# REPORTS

it provides further evidence of the conversion of these nanostructures to  $Mo^{\circ}$ . In contrast, as-deposited  $MoO_x$  composite nanowires were brittle and were subject to breaking when flexed by as little as  $5^{\circ}$ .

We conducted a survey of other metals and discovered that noble metals, including silver, platinum, and copper, do not nucleate with a sufficiently high linear density along step edges on graphite to form continuous nanowires, but instead form disconnected linear arrays of micrometer-scale metal particles. These three metals all exhibited facile electrodeposition kinetics at graphite surfaces. In contrast, several base metals, all of which exhibit slow heterogeneous electron transfer kinetics for deposition, behaved similarly to molybdenum. For example, we obtained nanowires of cadmium and nickelmolybdenum alloy by using deposition conditions analogous to those used in this study.

### References and Notes

- C. A. Foss, M. J. Tierney, C. R. Martin, J. Phys. Chem. 96, 9001 (1992); C. R. Martin et al., Adv. Mater. 11, 1021 (1999); S. A. Sapp, D. T. Mitchell, C. R. Martin, Chem. Mater. 11, 1183 (1999).

- C. K. Preston, M. Moskovits, J. Phys. Chem. 97, 8495 (1993); D. Routkevitch, T. Bigioni, M. Moskovits, J. M. Xu, J. Phys. Chem. 100, 14037 (1996); D. N. Davydov et al., Phys. Rev. B 57, 13550 (1998).

- L. Sun, P. C. Searson, C. L. Chien, *Phys. Rev. B* **61**, R6463 (2000); T. M. Whitney, J. S. Jiang, P. C. Searson, C. L. Chien, *Science* **261**, 1316 (1993); L. Sun, P. C. Searson, C. L. Chien, *Appl. Phys. Lett.* **74**, 2803 (1999).

- F. J. Himpsel et al., MRS Bull. 24, 20 (1999); T. Jung. R. Schlittler, J. K. Gimzewski, F. J. Himpsel, Appl. Phys. A 61, 467 (1995).

- D. Y. Petrovykh, F. J. Himpsel, T. Jung, Surf. Sci. 407, 189 (1998).

- M. Blanc, K. Kuhnke, V. Marsico, K. Kern, Surf. Sci. 414, L964 (1998); P. Gambardella, M. Blanc, H. Brune, K. Kuhnke, K. Kern, Phys. Rev. B 61, 2254 (2000).

- R. J. Nichols, D. M. Kolb, R. J. Behm, J. Electroanal. Chem. 313, 109 (1991); S. Morin, A. Lachenwitzer, O. M. Magnussen, R. J. Behm, Phys. Rev. Lett. 83, 5066 (1999).

- E. A. Abd El Meguid, P. Berenz, H. Baltruschat, J. Electroanal. Chem. 467, 50 (1999); J. Dekoster et al., Appl. Phys. Lett. 75, 938 (1999).

- 9. M. P. Zach, R. M. Penner, Adv. Mater. 12, 878 (2000).

- 10. Eq. 1 is readily derived from the expression for the deposition charge associated with the formation of a hemicylindrical solid,  $Q_{\rm dep} = (\pi r^2 n F \rho I/2 M)$ . For deposition with a constant current  $i_{\rm dep}$ ,  $Q_{\rm dep} = i_{\rm dep} t_{\rm dep}$ . Eq. 1 is then obtained by solving for r(t) in this equation.

- M. T. Reetz, W. Helbig, J. Am. Chem. Soc. 116, 7401 (1994); V. K. LaMer, R. H. Dinegar, J. Am. Chem. Soc. 72, 4847 (1950); T. Sugimoto, Adv. Colloid Interface Sci. 28, 65 (1987).

- A more extensive version of Fig. 3 is available at www.sciencemag.org/cgi/content/full/290/5499/ 2120/DC1.

- 13. The lattice parameter for body-centered cubic molybdenum metal is 3.1472 Å. Lattice parameters for monoclinic  $MoO_2$  are a=5.6096 Å, b=4.857 Å, and c=5.6259 Å, and  $\beta=120.912$ .

- 14. This work was funded by the NSF (grant DMR-9876479) and the Petroleum Research Fund of the American Chemical Society (grant 33751-AC5). We also gratefully acknowledge the financial support of the Camille and Henry Dreyfus Foundation. Finally, donations of graphite by A. Moore of Advanced Ceramics are gratefully acknowledged.

- 11 August 2000; accepted 13 October 2000

# High-Resolution Inkjet Printing of All-Polymer Transistor Circuits

H. Sirringhaus, 1\* T. Kawase, 1† R. H. Friend, 1\* T. Shimoda, 2 M. Inbasekaran, 3 W. Wu, 3 E. P. Woo<sup>3</sup>

Direct printing of functional electronic materials may provide a new route to low-cost fabrication of integrated circuits. However, to be useful it must allow continuous manufacturing of all circuit components by successive solution deposition and printing steps in the same environment. We demonstrate direct inkjet printing of complete transistor circuits, including via-hole interconnections based on solution-processed polymer conductors, insulators, and self-organizing semiconductors. We show that the use of substrate surface energy patterning to direct the flow of water-based conducting polymer inkjet droplets enables high-resolution definition of practical channel lengths of 5 micrometers. High mobilities of 0.02 square centimeters per volt second and on-off current switching ratios of 10<sup>5</sup> were achieved.

Semiconducting organic molecules (I) and polymers (2) can be self-assembled from solution into ordered structures with charge carrier mobilities close to that of inorganic thinfilm silicon. They may form the basis of a new thin-film electronic technology, in which integrated transistor circuits are manufactured by cheap solution processing and direct printing rather than vacuum deposition and photolithographic patterning (3-6). Howev-

er, this requires the development of printing techniques that provide accurate definition of all components of an integrated circuit but do not compromise the ability of the organic molecules to self-assemble. Inkjet printing (IJP) has emerged as an attractive patterning technique for conjugated polymers in lightemitting diodes (7, 8) and full-color highresolution displays (9). The technique has not been applied to organic transistors yet, because its resolution is limited to 20 to 50 µm by statistical variations of the flight direction of droplets and their spreading on the substrate. This is not sufficient for defining source-drain electrodes of practical thin-film transistors (TFTs) without accidental electrical shorts. Channel lengths of L = 5 to 10  $\mu$ m are required to achieve adequate drive current and switching speed.

Our approach for overcoming this prob-

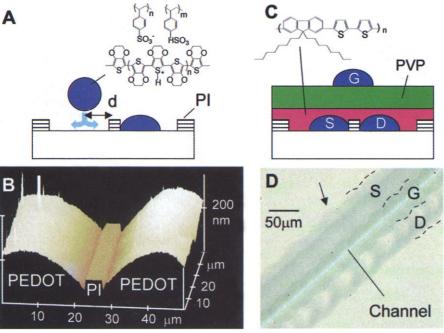

lem is to confine the spreading of waterbased conducting polymer ink droplets on a hydrophilic substrate with a pattern of narrow, repelling, hydrophobic surface regions that define the critical device dimensions (Fig. 1A). This surface free energy pattern on the Corning 7059 glass substrate is fabricated before TFT deposition by photolithography and O<sub>2</sub> plasma etching of a 500 Å polyimide film (9). After etching through the polyimide, the O2 plasma renders the source-drain regions on the bare glass hydrophilic, whereas the polyimide line defining the TFT channel is protected by photoresist and remains hydrophobic. The contact angle of water on hydrophilic glass and hydrophobic polyimide is 20° to 25° and 70° to 80°, respectively. For the source-drain and gate electrodes we use a water-based ink of the conducting polymer poly(3,4-ethylenedioxythiophene) doped with polystyrene sulfonic acid (PEDOT/PSS, Baytron P from Bayer, Krefeld, Germany). Our home-built, piezoelectric inkjet printer is equipped with an optical imaging system that allows coarse alignment (± 5 µm) of the inkjet nozzles with respect to the polyimide substrate pattern. A line of PEDOT droplets is deposited into the hydrophilic regions at a distance d from the polyimide line that is sufficiently small for the spreading droplets to reach the repelling line. The lateral distance between successive droplets (10 to 20 um) is smaller than the radius of sessile droplets (≈80 µm). Each droplet dries partially before the next droplet is deposited.

Atomic force microscopy (AFM) (Fig. 1B) shows that the inkjet-deposited PEDOT electrodes extend precisely up to the repelling polyimide line, whereas the second, unconfined boundary of the PEDOT line exhibits a typical roughness of  $\pm 10~\mu m$  (Fig. 1D). No PEDOT deposition occurs on top of the poly-

<sup>&</sup>lt;sup>1</sup>Cavendish Laboratory, University of Cambridge, Madingley Road, Cambridge CB3 OHE, UK. <sup>2</sup>Base Technology Research Center, Seiko-Epson Corporation, 3-5-3 Owa, Suwa-Shi, Nagano-Ken 392, Japan. <sup>3</sup>The Dow Chemical Company, Midland, MI 48674,

<sup>\*</sup>To whom correspondence should be addressed. E-mail: hs220@phy.cam.ac.uk

<sup>†</sup>Also at Epson Cambridge Laboratory, 8c King's Parade, Cambridge CB2 1SJ, UK.

imide. We have fabricated devices with channel lengths down to 5 µm, limited by the resolution of our photolithography setup. The AFM topographs suggest that fabrication of even shorter channels may be possible. The process is robust with respect to variations of the droplet volume or the distance *d*, which are caused by external perturbations of the droplet flight direction or changing ejection conditions at the nozzle. Device yields in our experiments, which were performed in a normal laboratory atmosphere, appear to be limited only by dust contamination. No evidence for accidental shorts between source and drain electrodes was found.

After IJP of source-drain electrodes, TFT devices are fabricated in a top-gate configuration (Fig. 1C) by spin-coating a continuous film (150 to 300 Å) of the active semiconducting polymer, poly(9,9-dioctylfluorene-co-bithiophene) (F8T2), from a xylene solution. Because of the low bulk conductivity of F8T2, no patterning of the semiconducting layer is required. A 400-to-500-nm-thick film of the gate dielectric polymer, polyvinylphenol (PVP), is spin-coated from isopropanol solution. Finally, a PEDOT/PSS gate electrode line overlapping the channel is inkjet printed in air.

The polyimide has a dual function. It not only provides accurate channel definition; when rubbed mechanically, it also acts as an

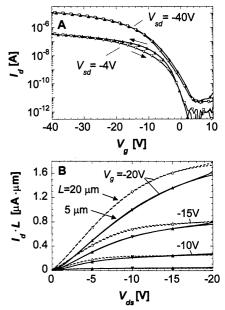

aligning template for the self-organization of the semiconducting polymer that is crucial for achieving high field-effect mobilities. F8T2 is a rigid-rod polymer with a nematic liquid-crystalline phase above 265°C and can be aligned into a monodomain on top of the rubbed polyimide line by bringing it into the liquid-crystalline phase and subsequently quenching it (10). To make best use of fast intrachain transport along the polymer backbone, the chains are aligned uniaxially parallel to the direction of current flow (Fig. 1D). The field-effect mobility  $\mu_{\text{FET}}$  extracted from the transfer characteristics (Fig. 2A) is  $\mu_{\text{FET}}$  = 0.01 to 0.02 cm<sup>2</sup>/V·s, which is only 1 to 2 orders of magnitude lower than that of conventionally processed amorphous silicon TFTs. The mobility of printed F8T2 TFTs is similar to that of devices with photolithographically defined gold electrodes (10). This shows that through careful choice of the sequence of solvents and polymers to avoid dissolution and swelling of underlying layers, our printing process maintains the critical integrity and abruptness required of the different polymer-polymer interfaces in a multilayer TFT device.

Another important attribute of F8T2 [as opposed to regioregular poly-3-hexylthiophene with even higher mobilities of 0.1 cm<sup>2</sup>/V · s (6)] is its relatively high stability against chemical doping by environmental oxygen or residual impurities such as mobile

sulphonic acid in the PEDOT/PSS ink. This enables devices with higher on-off current ratios exceeding  $10^5$  and with better operating stability than printed poly-3-hexylthiophene devices (11-13). The threshold voltage  $V_T \approx -10$  V, which is extracted from the x-axis intercept of the linear portion of the transfer characteristics ( $V_{\rm sd} = -4$  V), shifts by less than 1 V between subsequent gate voltage sweeps (Fig. 2A).

When comparing normalized drain currents  $I_d \cdot L$  of devices with different channel lengths, approximate scaling of the device characteristics with L is observed (Fig. 2B). This confirms the successful printing of devices with channel lengths of 5 µm, as already suggested by AFM (Fig. 1). The normalized current of  $L = 5 \mu m$  devices is only slightly lower than that of  $L = 20 \mu m$  devices. The 5-µm devices exhibit less pronounced current saturation and a nonlinearity in the output characteristics at small sourcedrain voltages. This is attributed to contact resistance effects at the source-drain contacts that limit the current flow in devices with short channels and high currents. To quantify this parasitic contact resistance, we consider the fraction  $V_c$  of the applied source-drain voltage V<sub>sd</sub> that drops across the source-

**Fig. 1.** (A) Schematic diagram of high-resolution IJP onto a prepatterned substrate. (B) AFM showing accurate alignment of inkjet-printed PEDOT/PSS source and drain electrodes separated by a repelling polyimide (PI) line with  $L=5~\mu m$ . (C) Schematic diagram of the top-gate IJP TFT configuration with an F8T2 semiconducting layer (S, source; D, drain; and G, gate). (D) Optical micrograph of an IJP TFT ( $L=5~\mu m$ ). The image was taken under crossed polarizers so that the TFT channel appears bright blue because of the uniaxial monodomain alignment of the F8T2 polymer on top of rubbed polyimide. Unpolarized background illumination is used to make the contrast in the remaining areas visible, where the F8T2 film is in an isotropic multidomain configuration. The arrow indicates pronounced roughness of the unconfined PEDOT boundary.

Fig. 2. (A) Transfer characteristics of an IJP TFT with F8T2 aligned uniaxially parallel to the current flow ( $L=5~\mu m$ ,  $W=3000~\mu m$ ) measured under an  $N_2$  atmosphere. Subsequent measurements with increasing (solid symbols) and decreasing (open symbols) gate voltage are shown. (B) Scaling of the output characteristics of IJP F8T2 TFTs normalized by multiplying the drain current by the channel length (dashed lines with open symbols,  $L=20~\mu m$ ; solid lines with solid symbols,  $L=5~\mu m$ ). Subsequent measurements with increasing (upward triangles) and decreasing (downward triangles) gate voltage are shown.

drain contacts. The remaining voltage drop across the TFT channel is proportional to L.  $V_c$  depends only on the current  $I_d$  flowing through the contacts and on the gate voltage  $V_g$ , but not explicitly on L (14). We consider the linear operation regime ( $V_{sd} \ll V_g$ ):

$$V_{\rm sd}(L) = V_{\rm c}(I_{\rm d}, V_{\rm g}) + \frac{I_{\rm d}}{\mu_{\rm FET} \cdot W \cdot C_{\rm i} \cdot (V_{\rm g} - V_{\rm T})} \cdot L \qquad (1)$$

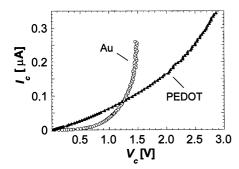

$C_i$  is the gate dielectric capacitance, and W is the channel width. By linear extrapolation of experimental  $V_{sd}(L)$  values for fixed  $I_t$  and  $V_g$  of devices fabricated on the same substrate, we extract the current-voltage characteristics  $I_{c}(V_{c})$ (Fig. 3) (15). The contact resistance characteristics of devices with PEDOT electrodes are slightly nonlinear at voltages below 2 V, indicating a small energy barrier for hole injection at the PEDOT-F8T2 interface. However, at higher voltages the characteristics can be approximated by a constant parasitic resistance of, typically, 3 to 5 megohm. This resistance is mainly attributed to the limited bulk conductivity of the PEDOT source-drain lines, which is measured to be 1 to 2 S/cm (20 to 50 kilohm/ square). Preliminary device modeling shows that a parasitic resistance of this order can consistently explain the deviations from ideal scaling behavior observed in Fig. 2B.

In comparison, devices fabricated with gold electrodes but with an otherwise identical configuration exhibit substantially more pronounced nonlinearities of the  $I_c(V_c)$  (and output) characteristics with strongly reduced currents for  $-V_{\rm sd}$  < 0.5 to 1 V (Fig. 3). At higher voltages, the characteristics rise more steeply, reflecting the higher conductivity of gold. The energy barrier for hole injection at the gold/F8T2 interface appears to be substantially higher than at the PEDOT/F8T2 interface, although PEDOT and gold have comparable workfunctions of about 5.1 eV (16). It is difficult to deduce quantitative information about injection barriers because of the complicated injection geometry and

**Fig. 3.** Current-voltage characteristics of the parasitic source-drain contact resistance for IJP PEDOT (solid triangles) and gold electrodes (open circles). The gold source-drain electrodes were cleaned carefully by exposure to  $O_2$  plasma before deposition of F8T2.

field configuration in the TFT, but similar observations have been reported for dark injection transient measurements on diode devices (17). We conclude that PEDOT/PSS provides more efficient hole injection into short-channel TFTs of rigid-rod conjugated polymers with high ionization potential ( $I_p = 5.5 \, \mathrm{eV}$  for F8T2) than do inorganic metals of comparable workfunction. However, for high-mobility devices with  $L < 5 \, \mu \mathrm{m}$ , higher bulk polymer conductivity is desirable.

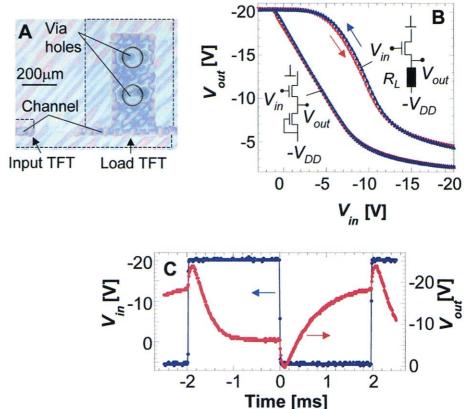

To fabricate complex integrated transistor circuits by IJP, circuit components other than TFTs need to be developed as well. Of particular importance are via-hole interconnects, which provide electrical connections between electrodes and/or interconnects in different layers (4). We have developed an IJP process for integrated via-hole fabrication based on the local dissolution of materials by inkjet deposition of a good solvent. To fabricate a via-hole through a layer of PVP, for example, a droplet of isopropanol is deposited locally. The PVP dissolves and upon drying of the solvent redeposits on the side walls of a craterlike intrusion. This is repeated several times until the surface

of the underlying layer, which also provides an automatic "etch stop," is exposed. Via-holes are filled by printing of PEDOT/PSS (Fig. 4A).

Via-holes are required for inverter devices: the basic building blocks of a logic circuit. Inverters can be implemented with two ptype transistors in either an enhancementload or a depletion-load configuration (18). The enhancement-load configuration, in which the drain and gate of the load transistor are connected together through a via-hole (Fig. 4B), is appropriate for transistors that are normally off such as inkjet-printed F8T2 devices ( $V_T \approx -10 \text{ V}$ , Fig. 2A). Alternatively, inverters with a printed resistor as the load element have been used. Resistors are fabricated by IJP of a line of PEDOT/PSS with a resistance value that can be adjusted over a wide range by varying the concentration of PSS. In both configurations, clean inverter action is observed for switching between logic "1" (-20 V) and logic "0" (0 V). The hysteresis of the characteristics is small, reflecting the stability of the transistor thresh-

old voltage. The voltage gain  $\frac{dV_{\text{out}}}{dV_{\text{in}}} \approx 2$  is

**Fig. 4.** (A) Optical micrograph of two via-holes connecting the drain and gate electrodes of the load TFT in an enhancement-load IJP inverter ( $L=5~\mu m$ ). Some reddish interference contrast is seen due to small spin-coating–induced thickness variations of the PVP dielectric. (B) Static characteristics of an enhancement-load inverter ( $L=5~\mu m$ ), width of the input switching transistor  $W_1=2150~\mu m$ , and width of the load transistor  $W_L=450~\mu m$ ) and of a resistance-load inverter ( $L=5~\mu m$ ,  $W_1=2150~\mu m$ , and  $R_L=47~m egohm$ ) measured with increasing (red) and decreasing (blue) input voltage  $V_{DD}=20~V$ ). (C) Dynamic switching characteristics of the resistance-load inverter in (B) ( $v_{in}=250~Hz$ ). The spikes of the output voltage after abrupt switching of the input voltage are induced by direct capacitive coupling on the TFT substrate between input and output electrodes.

# REPORTS

larger than 1, implying that these gates can be used to switch subsequent stages in more complex logic circuits. Higher gains of 5 to 7 have been obtained by increasing the load resistance.

Inkjet-printed inverters can be switched at frequencies up to a few hundred hertz, as shown in Fig. 4C for the resistor-load device of Fig. 4B. The fall time  $\tau_{1\rightarrow0}=350~\mu s$  is determined by the on current of the input transistor and by the load capacitance of our measurement setup  $(C_{\rm L} \approx 20 \text{ pF})$ . The rise time  $\tau_{1\to 0} = 750 \text{ }\mu\text{s}$ was designed to be comparable to the fall time by adjusting the load resistance ( $R_L = 47$ megohm). We estimate the total power consumption of an inverter stage, as in Fig. 4B, to be about 2 µW when switching five subsequent inverter stages (fanout = 5) at a frequency of 250 Hz (18). Further improvements are expected from increasing polymer mobility and PEDOT conductivity, and reducing channel length and source-drain-to-gate overlap capacitance ( $C_{\text{sd-g}} \approx 5 \text{ pF for } W = 2000 \text{ } \mu\text{m}$ ).

The performance of our inkjet-printed, all-polymer TFT circuits is believed to be adequate for applications such as active-matrix displays or identification tags. The TFT performance and the inverter switching speed are comparable to that of all-polymer TFT circuits reported by the Philips group who used a three-level photolithographic process to pattern electrodes and via-holes (4, 19). We believe that our IJP process will allow a similar degree of circuit complexity. IJP has advantageous attributes that will be required for continuous reel-to-reel processing of large-area circuits on plastic substrates. Because only a hydrophobic/hydrophilic surface energy contrast but no topographic profile is required for ink confinement, the photolithographic substrate prepatterning using polyimide can easily be replaced by soft lithography or photopatterning of a self-assembled monolayer (20), so that the entire circuit fabrication, including via-hole interconnections consists only of successive solution coating and printing steps. Particular advantages of IJP are as follows: (i) Different materials can be delivered simultaneously from multiple nozzles. (ii) IJP provides accurate registration over large areas, because the inkjet head can be aligned locally with respect to a previously deposited pattern. The local registration, which can be automated, is particularly important for flexible substrates, which inevitably exhibit distortions. (iii) Application- or even end-userspecific circuits can be defined by simple IJP of a network of interconnections and via-holes on a prefabricated array of transistor gates.

The physical mechanism underlying the precise self-alignment of inkjet-printed electrodes with the hydrophobic confinement structure is complex. It involves the simultaneous dynamic processes of droplet spreading and solidification, resulting in an increase of viscosity in the advancing front of the droplet (21).

Our dynamic, nonequilibrium droplet deposition technique overcomes inherent problems associated with forming high-resolution features by liquid-phase deposition onto patterned substrates. In static equilibrium, liquid patterns suffer from problems such as bulge formation (22), capillary breakup, or a sensitive dependence of film thickness on the shape and size of the pattern (23). None of these problems occurred in the IJP process, which allows precise local control of deposited droplet volume and drying time to form patterns with arbitrary shape and thickness. The submicrometer precise alignment observed in AFM topographs (Fig. 1A) suggests that our process can be extended to definition of even finer, possibly submicrometer features.

# References

- 1. H. E. Katz et al., Nature 404, 478 (2000).

- 2. H. Sirringhaus et al., Nature 401, 685 (1999).

- 3. R. F. Service, *Science* **278**, 383 (1997); F. Garnier, R. Hajlaoui, A. Yassar, P. Srivastava, *Science* **265**, 1684

- C. J. Drury, C. M. J. Mutsaers, C. M. Hart, M. Matters, D. M. de Leeuw, Appl. Phys. Lett. 73, 108 (1998).

- J. A. Rogers, Z. Bao, A. Makhija, P. Braun, Adv. Mater. 11, 741 (1999).

- H. Sirringhaus, N. Tessler, R. H. Friend, Science 280, 1741 (1998).

- T. R. Hebner, C. C. Wu, D. Marcy, M. H. Lu, J. C. Sturm, Appl. Phys. Lett. 72, 519 (1998).

- 8. Y. Yang, S.-C. Chang, J. Bharathan, J. Liu, J. Mater. Sci.: Mater. Electron. 11, 89 (2000).

- 9. T. Shimoda et al., Proc. Soc. Inf. Disp. 99, 376 (1999).

- 10. H. Sirringhaus et al., Appl. Phys. Lett. 77, 406 (2000).

- Z. Bao, Y. Feng, A. Dodabalapur, V. R. Raju, A. J. Lovinger, Chem. Mater. 9, 1299 (1997).

- W. S. Beh, I. T. Kim, D. Qin, Y. Xia, G. M. Whitesides, *Adv. Mat.* 11, 1038 (1999).

- J. A. Rogers, Z. Bao, V. R. Raju, Appl. Phys. Lett. 72, 2716 (1998).

- 14. S. Jain, Solid State Electron. 32, 77 (1989).

- 15. S. Luan, G. W. Neudeck, J. Appl. Phys. 72, 766 (1992).

- 16. T. M. Brown et al., Appl. Phys. Lett. 75, 1679 (1999).

- 17. A. J. Campbell et al., Appl. Phys. Lett. **76**, 1734 (2000).

- T. A. de Massa, Z. Ciccone, Digital Integrated Circuits (Wiley, New York, 1996).

- G. H. Gelinck, T. C. T. Geuns, D. M. de Leeuw, Appl. Phys. Lett. 77, 1487 (2000).

- H. Sugimura, K. Ushiyama, A. Hozumi, O. Takai, *Lang-muir* 16, 885 (2000).

- P. G. de Gennes in *Liquids at Interfaces*, J. Charvolin et al., Eds. (Elsevier Science, Amsterdam, 1989), vol. 48, pp. 273–291.

- H. Gau, S. Herminghaus, P. Lenz, R. Lipowsky, Science 283, 46 (1999).

- A. Darhuber, S. M. Troian, S. Miller, S. Wagner, J. Appl. Phys. 87, 7768 (2000).

- 13 September 2000; accepted 6 November 2000

# Ultrahigh-Density Nanowire Arrays Grown in Self-Assembled Diblock Copolymer Templates

T. Thurn-Albrecht, <sup>1</sup> J. Schotter, <sup>2</sup> G. A. Kästle, <sup>2</sup> N. Emley, <sup>2</sup> T. Shibauchi, <sup>3,4</sup> L. Krusin-Elbaum, <sup>3</sup> K. Guarini, <sup>3</sup> C. T. Black, <sup>3</sup> M. T. Tuominen, <sup>2\*</sup> T. P. Russell <sup>1\*</sup>

We show a simple, robust, chemical route to the fabrication of ultrahigh-density arrays of nanopores with high aspect ratios using the equilibrium self-assembled morphology of asymmetric diblock copolymers. The dimensions and lateral density of the array are determined by segmental interactions and the copolymer molecular weight. Through direct current electrodeposition, we fabricated vertical arrays of nanowires with densities in excess of  $1.9\times10^{11}$  wires per square centimeter. We found markedly enhanced coercivities with ferromagnetic cobalt nanowires that point toward a route to ultrahigh-density storage media. The copolymer approach described is practical, parallel, compatible with current lithographic processes, and amenable to multilayered device fabrication.

Continued advances in technologies such as magnetic storage and optoelectronics depend crucially on the ability to produce ultrahigh-

<sup>1</sup>Polymer Science and Engineering Department, <sup>2</sup>Physics Department, University of Massachusetts, Amherst, MA 01003, USA. <sup>3</sup>IBM T. J. Watson Research Center, Yorktown Heights, NY 10598, USA. <sup>4</sup>Los Alamos National Laboratory, Los Alamos, NM 87545, USA.

\*To whom correspondence should be addressed. E-mail: tuominen@physics.umass.edu (M.T.T.); russell@mail.pse.umass.edu (T.P.R.)

density arrays of nanometer-scale elements (I-II). As critical device dimensions shrink to the nanometer scale, the parallel fabrication of well-ordered arrays becomes increasingly difficult. We demonstrate a method to rapidly and reliably fabricate arrays with densities in excess of 1 terabit per square inch, based on the self-assembled morphology in diblock copolymer thin films. An ordered, nanoporous structure obtained from the copolymer film by chemical modification is