leagues, set out to measure the wind speed there. That's where SOHO came in. The team used SOHO's Ultraviolet Coronagraph Spectrometer (UVCS) as a kind of solar speedometer. The UVCS, explains its principal investigator, co-author John Kohl of CfA, collected light that is emitted by oxygen ions deep in the solar atmosphere, then scattered in all directions off other oxygen ions flowing outward in the solar wind. The faster the wind, the weaker the scattering, because the so-called Doppler shift lengthens the wavelengths seen by the fast-moving ions, making them unable to resonate with the light and scatter it.

The team correlated their speedometer readings with images of the magnetic arches and stalks made by another SOHO instrument, the Large Angle Spectroscopic Coronagraph. They also did a new search for scintillation by analyzing measurements of the Galileo communications signal. Strong radio scintillation, slow wind, and the stalks all turned up in the same places. "It's real exciting," says Steven Suess of NASA's Marshall Space Flight Center in Huntsville, Alabama. "I think 90% of their conclusions are absolutely accurate."

The other 10%, says Suess, concerns the fast wind. Although the fast wind is thought to originate in small regions near the poles, spacecraft far from the sun detect it at low latitudes. Solar physicists have explained this by assuming that field lines emerging from the polar coronal holes splay steeply outward, like the petals of a daisy, allowing the wind to spread out after it escapes. But to sustain high speeds even after it spreads out, the wind must get a tremendous boost from some unknown acceleration mechanism in the coronal holes.

The new UVCS measurements show, however, that the fast wind blows at a wide range of latitudes, even near the sun. What's more, radio scintillation combined with observations from Ulysses suggest that when gusts of plasma and other features rise from the sun's surface near the poles,

\_ELECTRONICS\_

## **Terribly Tiny Transistor Unveiled**

TOKYO—Circuit designers at NEC Corp. have probed what some thought was a lower limit on the size of microelectronics—and found some give. A transistor's gate—the narrow electrode that controls the flow of electrons through the device depending on whether it is "on" or "off"—can be made only so small. Too small, and electrons will manage to sneak through even when the device is

off. Some researchers had put this lower limit at 30 nanometers (billionths of a meter).

But at a recent conference\* in Japan, a group at NEC's Fundamental Research Laboratories in Tsukuba led by Hisao Kawaura announced that, by combining a novel design with high-precision techniques for carving semiconductors, it has developed an experi-

mental transistor with a gate just 14 nanometers across. That's 20 times smaller than in the transistors found on the densest commercially available chips. "Nobody has yet reported work at such small dimensions," says Sandip Tiwari, a small-device researcher at IBM's T. J. Watson Research Center in Yorktown Heights, New York. The device is mainly a proof of principle, however, as its design isn't suited to being packed in large numbers on a chip.

To create an ultrasmall gate that doesn't

leak electrons, the NEC group varied a common transistor design known as a metal-onoxide semiconductor field effect transistor, or MOSFET. In these devices, a central semiconducting channel lies between currentcarrying source and drain regions. These socalled n<sup>+</sup> regions are created by "doping" the base material with impurities that carry an excess of electrons. Above the channel is the

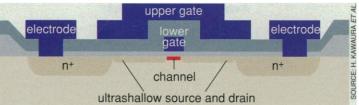

Hat trick. A hat-shaped upper gate electrode opened the way to shrinking the gate itself in this experimental transistor.

> gate electrode. The gate turns the transistor on or off by controlling the conductivity of the channel, either allowing electrons to flow from source to drain, or cutting off the current.

> The NEC team added a second gate, shaped something like a top hat, with the crown above the lower gate and brims above both sides of the channel. Ordinarily, the  $n^+$ regions abut the channel, but this second gate allowed the researchers to leave insulating gaps between the channel and the  $n^+$ regions. To create a route for current, a voltage applied to the upper gate attracts electrons to the surface of the base material, forming conductive ultrashallow source and

they don't expand much in latitude. That suggests, say Woo and Habbal, that the fast wind must originate not just near the poles, but from patches of open field lines all over the sun.

That's heresy to many solar physicists. Although some models have predicted the stray fields, says Randolph Levine, who did early work on the subject at CfA, researchers have tended to think of the sun's magnetic field as well anchored except in the polar regions. But the idea that the fast solar wind blows from all across the sun "simplifies our ideas about what's going on," says Habbal, because it would eliminate the need for some special boost in polar regions. What comes out, fast or slow, would depend only on the local magnetic topology.

The new evidence makes this idea "hard to dismiss," says Lockheed's Title. But he, like other solar physicists, isn't ready to follow that shift in the scientific winds just yet. –James Glanz

drain regions. These electrically induced regions are far shallower than anything that can be formed with present doping techniques; and the shallower source and drain confine the current so that a narrower gate can control it.

Microcircuit designers usually lay out such features by shining light through a stencillike mask. The light imprints the features onto a light-sensitive coating, or resist, on the semiconductor, establishing the pat-

> tern for later fabrication steps. To make their ultrasmall device, the NEC group replaced the light and mask with a tightly focused electron beam, says team member Toshitsugu Sakamoto. They also developed a new highresolution organic resist, which yielded even greater precision, much as a sharper pencil on finer grained paper yields more precise and consistent lines.

IBM's Tiwari says the new transistor "is very encouraging." But both Tiwari and the researchers themselves caution that it will take a lot more work to turn this strategy of electrically induced source and drain regions into a practical device. For one thing, the present double-gate design would make it difficult to pack these transistors densely. The device also takes a lot of power and doesn't switch on and off with the needed speed and consistency. But even if the new transistor won't make it out of the laboratory, says Sakamoto, "This is a good structure for testing the limits for gates."

-Dennis Normile

<sup>\*</sup> International Conference on Solid State Devices and Materials, Hamamatsu, 19 Sept.