# **PHILIPS**

# MICROPROCESSOR

2650 SERIES

Manufacturer reserves the right to make design and process changes and improvements,

#### **DESCRIPTION**

The 2650A, A-1, B and B-1 are additional members of the Signetics family of 8 bit, NMOS microprocessors.

The 2650A is a functional equivalent of the 2650 with a new mask design which provides improved device operating margins.

The 2650A-1 is a high speed version of the 2650A.

The 2650B is a variation of the 2650A microprocessor. Features have been added to the original 2650A to make the 2650B more powerful and easier to use.

The 2650B-1 is a high speed version of the 2650B.

#### **FEATURES**

- Static 8 bit parallel NMOS microproc-

- Single power supply of +5 volts

- TTL level single phase clock

- TLL compatible inputs and outputs

- Variable length instructions of 1, 2 or 3 bytes

- 32K byte addressing range

- Coding efficiency with multiple addressing modes

- Synchronous or asynchronous memory and I/O interface

- Interfaces directly with industry standard memories

- Single bit serial I/O path

- Seven 8 bit addressable general purpose registers

- Vectored interrupt

- Subroutine return address stack

# ORDERING CODE (All Device Types Operate Over 0°C to 70°C Temperature Range)

| PACKAGES    | CYCLE               | TIME            |

|-------------|---------------------|-----------------|

| FACRAGES    | 1.5 µs              | <b>2.4</b> μs   |

| eramic DIP  | 2650A-1I • 2650B-1I | 2650AI • 2650BI |

| Plastic DIP | 2650A-1N ● 2650B-1N | 2650AN ● 2650BN |

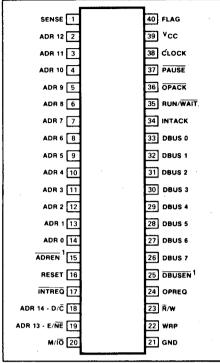

#### PIN CONFIGURATION

<sup>1.</sup> For 2650B and 2650B-1 pin 15 is BEN and pin 25 is

MICROPROCESSOR 2650 SERIES

# **PIN DESIGNATION**

| MNEMONIC         | NUMBER | NAME                                 | TYPE | FUNCTION                                                                                                                                                                                                                           |

|------------------|--------|--------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR0-ADR12       | 14-2   | Address lines                        | 0    | Low order memory address lines for instruction or operand fetch. ADR0 is the least significant bit and ADR12 is the most significant bit. ADR0 through ADR7 are also used as the I/O device address for extended I/O instructions. |

| ADR13-E/NE       | 19     | Address 13-<br>Extended/Non extended | 0    | Low order memory page address line during memory reference instructions. For I/O instructions this line discriminates between extended and non-extended I/O instructions.                                                          |

| ADR14-D/C        | 18     | Address 14-<br>Data / Control        | 0    | High order memory page address line during memory reference instructions. It also serves as the I/O device address for non-extended I/O instructions.                                                                              |

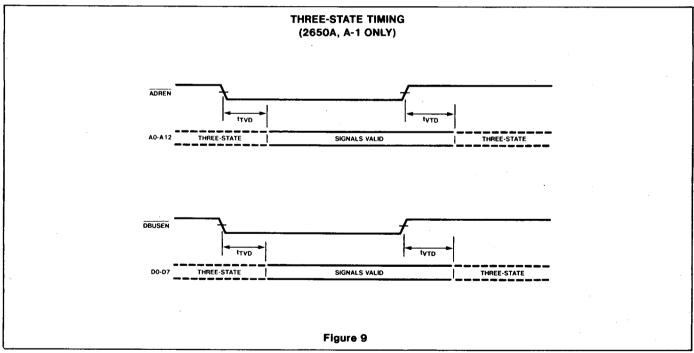

| ADREN            | 15     | Address enable<br>(2650A, 2650A-1)   | ı    | Active low input allowing 3-state control of the address bus ADR0-ADR12.                                                                                                                                                           |

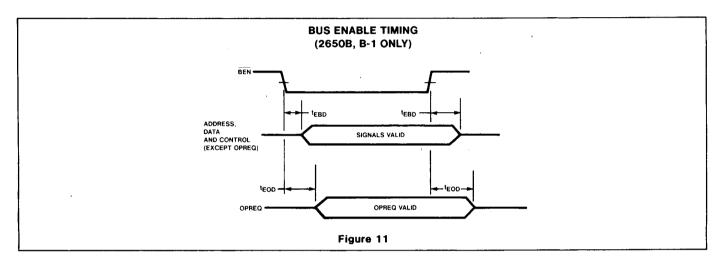

| BEN              | 15     | Bus enable<br>(2650B, 2650B-1)       | I    | Active low input allowing 3-state control of the address bus ADR0 through ADR14, data bus DBUS0 through DBUS7, WRP, $\overline{R}$ /W, M/ $\overline{IO}$ and OPREQ.                                                               |

| DBUSO-DBUS7      | 33-26  | Data bus                             | 1/0  | These lines provide communication between the CPU, Memory, and I/O devices for instruction and data transfers.                                                                                                                     |

| DBUSEN           | 25     | Data bus enable<br>(2650A, 265A-1)   | ı    | This active low input allows tri-state control of the data bus.                                                                                                                                                                    |

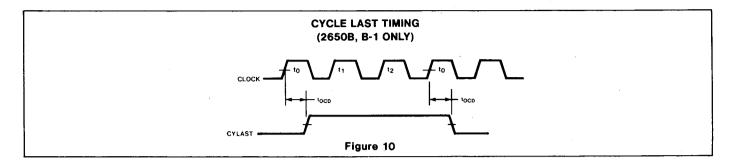

| CYLAST           | 25     | Cycle last (2650B, 2650B-1)          | 0    | Active high output indicates that the associated machine cycle is the last cycle of the instruction currently being executed.                                                                                                      |

| OPREQ            | 24     | Operation request                    | 0    | Indicates to external devices that all address, data and control information is valid.                                                                                                                                             |

| OPACK            | 36     | Operation acknowledge                | ı    | Active low input indicating completion of an external operation. This allows asynchronous functioning of external devices.                                                                                                         |

| M/ <del>IO</del> | 20     | Memory/input-output                  | 0    | Indicates whether the current operation references memory or I/O.                                                                                                                                                                  |

| <b>R</b> /W      | 23     | Read/Write                           | 0    | Indicates a read or a write operation.                                                                                                                                                                                             |

| WRP              | 22     | Write pulse                          | 0    | This is a timing signal from the 2650 that provides a positive-going pulse during each requested write operation (memory or I/O) and a high level during read operations.                                                          |

| SENSE            | 1      | Sense                                | 1    | The sense bit in the PSU reflects the logic state of the sense input to the processor at pin #1.                                                                                                                                   |

| FLAG             | 40     | Flag                                 | 0    | The flag bit in the PSU is tied to a latch that drives the flag output at pin #40.                                                                                                                                                 |

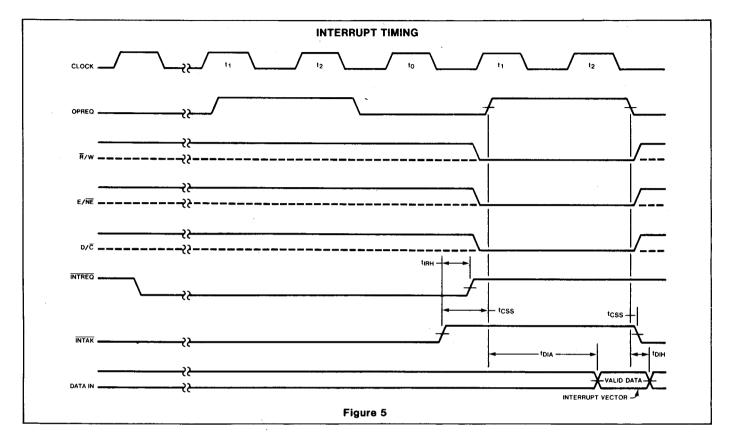

| INTREQ           | 17     | Interrupt request                    | 1    | This active low input line indicates to the processor that an external device is requesting service. The processor will recognize this signal at the end of the current instruction if the interrupt inhibit status bit is zero.   |

| INTACK           | 34     | Interrupt acknowledge                | 0    | This line indicates that the 2650 is ready to receive the interrupt vector (relative address byte) from the interrupting device.                                                                                                   |

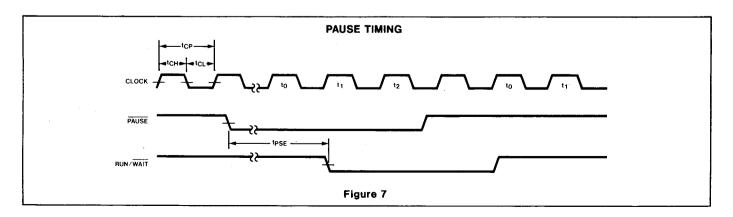

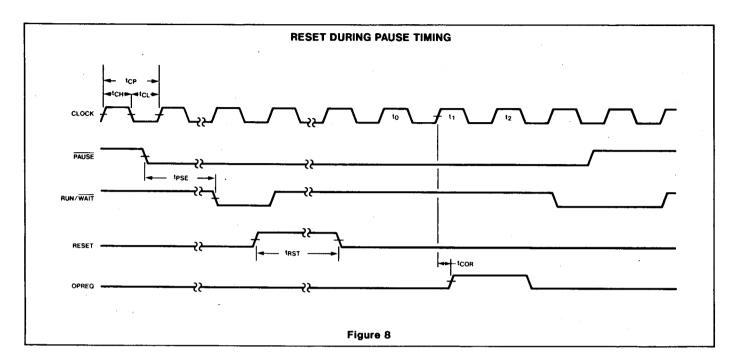

| PAUSE            | 37     | Pause                                | ١ -  | This active low input is used to suspend processor operation at the end of the current instruction.                                                                                                                                |

| RUN/WAIT         | 35     | Run/Wait                             | 0    | This output is a processor status indicator. During normal operation this line is high. If the processor is halted either by executing a half instruction or by a low input on the pause line, the run/wait line will go low.      |

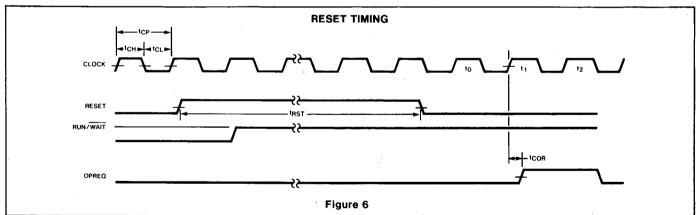

| RESET            | 16     | Reset                                | ı    | Resets the instruction address register to zero. Clears interrupt inhibit (2650A). Sets interrupt inhibit (2650B).                                                                                                                 |

| CLOCK            | 38     | Clock                                | ı    | A positive going pulse train that determines the instruction execution time.                                                                                                                                                       |

| VCC              | 39     | +5V                                  | 1    | +5V power                                                                                                                                                                                                                          |

| GND              | 21     | GND                                  | 1    | Ground                                                                                                                                                                                                                             |

#### **FUNCTIONAL DESCRIPTION**

The 2650 series processors are general purpose, single chip, fixed instruction set, parallel 8-bit binary processors. A general purpose processor can perform any data manipulations through execution of a stored sequence of machine instructions. The processor has been designed to closely resemble conventional binary computers, but executes variable length instructions of one to three bytes in length.

The 2650 series contains a total of seven general purpose registers, each eight bits long. They may be used as source or destination for arithmetic operations, as index registers, and for I/O transfers.

The processor can address up to 32,768 bytes of memory in four pages of 8,192 bytes each. The processor instructions are one, two, or three bytes long, depending on the instruction. Variable length instructions tend to conserve memory space since a one-or-two byte instruction may often be used rather than a three byte instruction. The first byte of each instruction always specifies the operation to be performed and the addressing mode to be used. Most instructions use six of the first eight bits for this purpose, with the remaining two bits forming the register field. Some instructions use the full eight bits as an operation code.

The data bus and address signals are tristate to provide convenience in system design. Memory and I/O interface signals are asynchronous so that direct memory access (DMA) and multiprocessor operations are easy to implement.

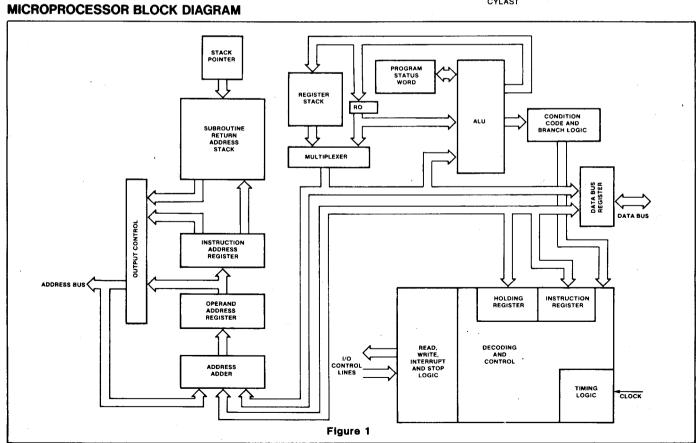

The block diagram for the 2650 series (figure 1) shows the major internal components and the data paths that interconnect them. In order for the processor to execute an instruction, it performs the following general steps:

- The instruction address register provides an address for memory.

- The first byte of an instruction is fetched from memory and stored in the instruction register.

- The instruction register (IR) is decoded to determine the type of instruction and the addressing mode.

- If an operand from memory is required, the operand address is resolved and loaded into the operand address register.

- 5. The operand is fetched from memory and the operation is executed.

- 6. The first byte of the next instruction is fetched

The instruction register holds the first byte of each instruction and directs the subsequent operations required to execute each

instruction. The IR contents are decoded and used in conjunction with the timing information to control the activation and sequencing of all the other elements on the chip. The holding register is used in some multiple-byte instructions to contain further instruction information and partial absolute addresses.

The arithmetic logic unit (ALU) is used to perform all of the data manipulation operations, including load, store, add, subtract, AND, inclusive OR, exclusive OR, compare, rotate, increment and decrement. It contains and controls the carry bit, the overflow bit, the interdigit carry and the condition code register.

The register stack contains six registers that are organized into two banks of three registers each. The register select bit picks one of the two banks to be accessed by instructions. In order to accommodate the register-to register instructions, register zero (R0) is outside the array. Thus, register zero is always available along with one set of three registers.

The address adder is used to increment the instruction address and to calculate relative and indexed addresses.

The instruction address register holds the address of the next instruction byte to be

accessed. The operand address register stores operand addresses and sometimes contains intermediate results during effective address calculations.

The return address stack (RAS) is a last in, first out (LIFO) storage which receives the return address whenever a branch-to-subroutine instruction is executed. When a return instruction is executed, the RAS provides the last return address for the processor's IAR. The stack contains eight levels of storage so that subroutines may be nested up to eight levels deep. The stack pointer is a three bit wraparound counter that indicates the next available level in the stack. It always points to the current address

#### PROGRAM STATUS WORD

The program status word (PSW) is a major feature of the 2650 which greatly increases its flexibility and processing power. The PSW is a special purpose register within the processor that contains status and control bits

It is divided into two bytes called the program status upper (PSU) and program status lower (PSL). The PSW bits may be tested, loaded, stored, preset, or cleared using the instructions which affect the PSW. The bits are utilized as shown in table 1.

#### Table 1 PROGRAM STATUS WORD

| PSU0,1,2 | SP     | Pointer for the return address stack.                                       | ı |

|----------|--------|-----------------------------------------------------------------------------|---|

| PSU3,4   | UF 1,2 | Setable testable user flags in 2650B, B-1. In 2650A, A-1, these bits are    | ĺ |

|          |        | always zero.                                                                |   |

| PSU5     | 11     | Used to inhibit recognition of additional Interrupts.                       | l |

| PSU6     | F      | Flag is a latch directly driving the flag output.                           |   |

| PSU7     | S      | Sense equals the state of the sense input.                                  | ĺ |

| PSLO     | C      | Carry stores any carry from the high-order bit of ALU.                      | ĺ |

| PSL1     | сом    | Compare determines if a logical or arithmetic comparison is to be           | ı |

|          |        | made.                                                                       | l |

| PSL2     | OVF    | Overflow is set if a two's complement overflow occurs.                      | l |

| PSL3     | wc     | With carry determines if the carry is used in arithmetic and rotate         | ĺ |

|          |        | instructions.                                                               | l |

| PSL4     | RS     | Register select identifies which bank of 3 GP registers is being used.      | l |

| PSL5     | IDC    | Inter digit carry stores the bit-3 to bit-4 carry in arithmetic operations. |   |

| PS167    | l cc   | Condition code is affected by compare, test and arithmetic instructions.    | ı |

### PSU

| 7 | 6 | 5   | 4   | 3   | 2   | 1   | 0   |

|---|---|-----|-----|-----|-----|-----|-----|

| s | F | -11 | UF1 | UF2 | SP2 | SP1 | SP0 |

- S Sense

- F Flag

- II Interrupt inhibit

- UF1 User flag 1

- UF2 User flag 2

- SP2 Stack pointer two

- SP1 Stack pointer one

- SPO Stack pointer zero

## PSL

| 7   | 6   | 5   | 4  | 3  | 2   | 1   | 0 |

|-----|-----|-----|----|----|-----|-----|---|

| CC1 | CCO | IDC | RS | wc | OVF | СОМ | С |

- CC1 Condition code one

- CCO Condition code zero

- IDC Interdigit carry

- RS Register bank select

- WC With/without carry

- **OVF** Overflow

- COM Logical arithmetic compare

- C 'Carry/borrow

MICROPROCESSOR 2650 SERIES

#### INPUT/OUTPUT INTERFACE

The 2650 series microprocessor has a set of versatile I/O instructions and can perform I/O operations in a variety of ways. One-and two-byte I/O instructions are provided, as well as a special single-bit I/O facility. The I/O modes provided by the 2650 are designated as data, control, and extended I/O.

Data or control I/O instructions, also called non-extended I/O instructions, are one byte long. Any general purpose register can be used as the source or destination. A special control line indicates if either a data or control instruction is being executed.

Extended I/O is a two-byte read or write instruction. Execution of an extended I/O instruction will cause an 8-bit address, taken from the second byte of the instruction, to be placed on the low order eight address lines. The data, which can originate or terminate with any general purpose register, is placed on the data bus. This type of I/O can be used to simultaneously select a device and send data to it

Memory reference instructions that address data outside of physical memory may also be used for I/O operations. When an instruction is executed, the address may be decoded by the I/O device rather than memory.

#### **MEMORY INTERFACE**

The memory interface consists of the address bus, the 8-bit data bus and several

signals that operate in an interlocked or handshaking mode.

The write pulse signal is designed to be used as a memory strobe signal for any memory type. It has been particularly optimized to be used as the chip enable or read/write signal.

# INTERRUPT HANDLING CAPABILITY

The 2650 series has a single level hardware vectored interrupt capability. When an interrupt occurs, the processor finishes the current instruction and sets the interrupt inhibit bit in the PSW. The processor then executes a branch to subroutine relative to location zero (ZBSR) instruction and sends out interrupt acknowledge and operation request signals. On receipt of the INTACK signal, the interrupting device inputs an 8-bit address, the interrupt vector, on the data bus. The relative and relative indirect addressing modes combined with this 8-bit address allow interrupt service routines to begin at any addressable memory location.

#### **INSTRUCTION SET**

It may be seen from examination of the 2650 instruction set that there are many powerful instructions which are all easily understood and are typical of larger computers. There are one-, two-, and three-byte instructions as a result of the multiplicity of addressing modes. See table 2 for a complete listing and figure 2 for instruction formats.

Automatic incrementing or decrementing of an index register is available in the arithmetic indexed instructions. All of the branch instructions except indexed branching can be conditional.

Register-to-register instructions are one byte; register-to-storage instructions are two or three bytes long. The two-byte register-to-memory instructions are either immediate or relative addressing types.

# SUMMARY OF DIFFERENCES BETWEEN 2650A/2650A-1 AND 2650B/2650B-1

- 1. Pin out: 2650B and 2650A differ in two pin functions. In the 2650B, pin 15 becomes bus enable and pin 25 becomes cycle last.

- 2. Program status word upper: PSU bits 3 and 4 are setable, testable user flags in the 2650B/B-1. These bits are always zero in the 2650A/A-1.

- 3. Instruction set: Two instructions have been added to the 2650B/B-1 to facilitate saving and restoring the program status lower during interrupt processing. These are: LDPL-Load program status lower from memory, and STPL-Store program status lower from memory.

- 4. Instruction execution time: Certain Z-format instructions in the 2650B/B-1 execute in 1 cycle rather than 2. These are: LODZ, SUBZ, COMZ, STRZ, IORZ, ANDZ, ADDZ and EORZ.

#### **Table 2 INSTRUCTION SET SUMMARY**

|                | MNE-           | DESCRIPTION OF OPERATION                             | Ľ        | _  | COD<br>r CC |            |    |     |   | BITS |    |   |   | -     |        |                   | NOTE      |

|----------------|----------------|------------------------------------------------------|----------|----|-------------|------------|----|-----|---|------|----|---|---|-------|--------|-------------------|-----------|

|                | MONIC          |                                                      | 3        | 2  | 1           | 0          | СС | IDC | С | OVF  | SP | П | F | BYTES | CYCLES | FORMAT (Figure 2) | NO.E      |

|                | (Z             | Load register zero                                   |          | 02 |             | _          | •  |     |   |      |    |   |   | 1     | 2      | Z                 | 1,12      |

| 삝              | LOD {          | Load immediate                                       |          | 06 |             | 04         | •  |     |   |      |    |   |   | 2     | 2      | I                 | 1         |

| []             | R              | Load relative                                        | 1        |    | 09          |            | •  |     |   |      |    |   |   | 2     | 3      | R                 | 1,6       |

| LOAD/STORE     | (A)            | Load absolute                                        |          |    | OD          |            | •  |     |   |      |    |   |   | 3     | 4      | A                 | 6         |

| 9              | (Z             | Store register zero                                  | 1        | C2 |             | _          | •  |     |   |      |    |   |   | 1     | 2      | Z                 | 1,12      |

| O              | STR R          | Store relative                                       |          |    | C9          |            | }  |     |   |      |    |   |   | 2     | 3      | R                 | 6         |

| -              | (A             | Store absolute                                       | CF       | CE | CD          | CC         |    |     |   |      |    |   |   | 3     | 4      | Α                 | -6        |

| П              | (Z             | Add to register zero w/wo carry                      | 1        |    | 81          |            | •  | •   | • | •    |    |   |   | 1     | 2      | Z                 | 1,12      |

| 11             | ADD            | Add immediate w/wo carry                             | 1        | 86 |             | 84         | •  | •   | • | •    |    |   |   | 2     | 2      | I                 | 1         |

|                | R              | Add chackets w/wo carry                              | 1        |    | 89          |            |    | •   | • | •    |    |   |   | 2     | 3      | R                 | 1,6       |

| 脂              |                | Add absolute w/wo carry                              | 1        |    | 8D          |            |    |     |   |      |    |   |   | 3     | 4      | Α                 | 1,6       |

| ARITHMETIC     | (z             | Subtract from register zero w/wo borrow              | АЗ       | A2 | A 1         | ΑO         | •  | •   | • | •    |    |   |   | 1     | 2      | Z                 | 1,12      |

| Ę              | SUB { I        | Subtract immediate w/wo borrow                       |          |    | Α5          |            | •  | •   | • | •    |    |   |   | 2     | 2      | 1                 | 1         |

| 4              | R              | Subtract relative w/wo borrow                        | i        |    | Α9          |            | •  | •   | • | •    |    |   |   | 2     | 3      | R                 | 1,6       |

| 1              | (A             | Subtract absolute w/wo borrow                        |          |    | ΑD          |            | •  | •   | • | •    |    |   |   | 3     | 4      | Α                 | 1,6       |

|                | DAR            | Decimal adjust register                              | 97       | 96 | 95          | 94         | •  |     |   |      |    |   |   | 1     | 3      | Z                 | 1,10      |

|                | ۲Z             | AND to register zero                                 | _        | 42 |             | _          | •  |     |   |      |    |   |   | 1     | 2      | Z                 | 1,12      |

| 1 1            | AND            | AND immediate                                        | 47       |    |             | 44         | •  |     |   |      |    |   |   | 2     | 2      | I                 | 1         |

| 1 1            | R              | AND relative AND absolute                            | 1        | 4A |             | 48         | •  |     |   |      |    |   |   | 2     | 3      | R                 | 1,6       |

|                | 1              |                                                      | 1        |    | 4D          |            |    |     |   |      |    |   |   | 3     | 4      | Α                 | 1,6       |

| 4              | (Z             | Inclusive-OR to register zero Inclusive-OR immediate |          | 62 |             | 60         |    |     |   |      |    |   |   | 1     | 2      | Z                 | 1,12      |

| 2              |                | Inclusive-OR relative                                | 67<br>60 | 6A |             | 64<br>68   |    |     |   |      |    |   |   | 2 2   | 2<br>3 | ı                 | 1         |

| LOGICAL        | (A)            | Inclusive-OR absolute                                | 1        |    | 6D          |            |    |     |   |      |    |   |   | 3     | 4      | R<br>A            | 1,6       |

|                | (Z             | Exclusive-OR to register zero                        | 23       |    |             | 20         |    |     |   |      |    |   |   | 1     | 2      | z                 | 1,6       |

| 1 1            | 17             | Exclusive-OR immediate                               | 1        | 26 |             | 24         |    |     |   | ,    |    |   |   | 2     | 2      | Z<br>I            | 1,12<br>1 |

|                | EOR R          | Exclusive-OR relative                                | 1        |    | 29          |            | •  |     |   |      |    |   |   | 2     | 3      | R                 | 1,6       |

|                | اما            | Exclusive-OR absolute                                | 1        |    | 2D          |            | •  |     |   |      |    |   |   | 3     | 4      | A                 | 1,6       |

| $\prod$        | (Z             | Compare to register zero                             | E3       | E2 | E1          | E0         | •  |     |   |      | •  |   | - | 1     | 2      | Z                 | 2,12      |

|                |                | arithmetic/logical                                   |          |    |             |            |    |     |   |      |    |   |   |       |        |                   |           |

| PAR            | сом {          | Compare immediate arithmetic/<br>logical             | E7       | E6 | <b>E</b> 5  | E4         | •  |     |   |      |    |   |   | 2     | 2      | Ì                 | 3         |

| NO.            | R              | Compare relative arithmetic/                         | ЕВ       | EΑ | <b>E</b> 9  | <b>E</b> 8 | •  |     |   |      | ,  |   |   | 2     | 3      | R                 | 3,6       |

| ROTATE/COMPARE | \ <sub>A</sub> | Compare absolute arithmetic/<br>logical              | EF       | EE | ED          | EC         | •  |     |   |      |    |   |   | 3     | 4      | A                 | 3,6       |

| ြဋ္ဌ           | RRR            | Rotate register w/wo carry                           | 53       | 52 | 51          | 50         | •  | •   | • |      |    |   |   | 1     | 2      | Z                 | 1         |

| -              | RRL            | Rotate register left w/wo carry                      | ł        |    | D1          |            | •  | •   | • |      |    |   |   | 1     | 2      | · Z               | 1         |

|                |                |                                                      |          |    |             |            |    |     |   |      | -  |   |   | '     | ~      | ~                 | '         |

- 1. Condition code (CC1, CC0): 01 if positive, 00 if zero, 10 if negative.

- 2. Condition code (CC1, CC0): 01 if R0 > r, 00 if R0 = r, 10 if R0 < r.

- 3. Condition code (CC1, CC0): 01 if r > V, 00 if r = V, 10 if r < V.

- 4. Condition code (CC1, CC0): 00 if all selected bits are 1s, 10 if not all the selected bits are 1s.

- 5. Index register must be register 3 or  $3^{\prime}$ .

- Requires two additional cycles if indirection is specified.

Requires two additional cycles if indirection is specified and branch is taken.

- 8. Specify CC = 11 for unconditional branch.

- 9. RS, WC and COM bits in PSW are also affected.

- 10. CC assumes number in register is a binary number.

- 11. 2650B, 2650B-1 only.

- 12. For 2650B, 2650B-1, execution requires one cycle.

Table 2 INSTRUCTION SET SUMMARY (Cont'd)

|                          | MNE  | _              | DESCRIPTION OF OREDATION                                                                           | •  |            | r CC       |            |    |     |   | BIT |    |    |   |       |        |                      |            |

|--------------------------|------|----------------|----------------------------------------------------------------------------------------------------|----|------------|------------|------------|----|-----|---|-----|----|----|---|-------|--------|----------------------|------------|

|                          | MONI | . 1            | DESCRIPTION OF OPERATION                                                                           | 3  | 2          | 1          | 0          | СС | IDC | С | OVF | SP | 11 | F | BYTES | CYCLES | FORMAT<br>(Figure 2) | NOTE       |

|                          | BCT. | {R<br>A        | Branch on condition true relative Branch on condition true absolute                                |    | 1A<br>1F   | 19<br>. 1D | 18<br>10   |    |     |   |     |    |    |   | 2     | 3<br>3 | R<br>B               | 7,8<br>7,8 |

|                          | BCF  | ĴŔ             | Branch on condition false relative                                                                 | 1  | -          | 99         |            |    |     |   |     |    |    |   | 2     | 3      | R                    | 7,0        |

|                          |      | LA             | Branch on condition false absolute                                                                 | 1  |            | 9D         |            |    |     |   |     |    |    |   | 3     | 3      | В                    | 7          |

| BRANCH                   | BRN  | R<br>A         | Branch on register non-zero relative Branch on register non-zero absolute                          |    |            | 59<br>5D   |            | -  |     |   |     |    |    |   | 3     | 3<br>3 | R<br>B               | 7          |

| 80                       | BIR  | {R<br>A        | Branch on incrementing register relative                                                           |    |            | D9         |            |    |     |   |     |    |    |   | 2     | 3      | R                    | 7          |

|                          |      |                | Branch on incrementing register absolute                                                           |    |            | DD         |            |    |     |   |     |    |    | ļ | 3     | 3      | В                    | 7          |

|                          | BDR  | {R<br>A        | Branch on decrementing register relative Branch on decrementing                                    |    |            | F9<br>FD   |            |    |     |   |     |    |    |   | 3     | 3      | R                    | 7          |

|                          |      | ^,             | register absolute                                                                                  | FF | re.        | FU         | FU         |    |     |   |     |    |    |   | 3     | 3      | В                    | ′          |

| 1                        | ZBRR |                | Zero branch relative, unconditional                                                                | 9B | -          | _          | .—         |    |     |   |     |    |    |   | 2     | 3      | ER                   | 6          |

| `                        | BXA  |                | Branch indexed absolute, unconditional                                                             | 9F | _          |            |            |    |     |   |     |    |    |   | 3     | 3      | EB                   | 5,6        |

|                          | BST  | (R             | Branch to subroutine on con-<br>dition true, relative                                              | зв | ЗА         | 39         | 38         |    |     |   |     | •  |    |   | 2     | 3      | R                    | 7,8        |

| _                        |      | (A             | Branch to subroutine on con-<br>dition true, absolute                                              | 3F | 3 <b>E</b> | 3D         | зС         |    |     |   |     | •  |    |   | 3     | 3      | В                    | 7,8        |

| SUBROUTINE BRANCH/RETURN | BSF  | ₽              | Branch to subroutine on con-<br>dition false, relative                                             | -  | ВА         | B9         | <b>B</b> 8 |    |     |   |     | •  |    |   | 2     | `3     | √ <b>R</b>           | 7          |

| H/RE                     |      | (A             | Branch to subroutine on con-<br>dition false, absolute                                             | -  | BE         | BD         | ВС         |    |     |   |     | •  |    |   | 3     | 3      | В                    | 7          |

| RANC                     | BSN  | { <sup>R</sup> | Branch to subroutine on non-<br>zero register, relative                                            |    |            | 79         |            |    |     |   |     | •  |    |   | 2     | 3      | R.                   | 7,8        |

| N N                      |      | (A             | Branch to subroutine on non-<br>zero register, absolute                                            | 7F | 7E         | 7D         | 7C         |    |     |   |     | •  |    |   | 3     | 3      | В                    | 7,8        |

| 50                       | ZBSR |                | Zero branch to subroutine relative, unconditional                                                  | ВВ | _          |            |            |    |     |   |     |    |    |   | 2     | 3      | ER                   | 6          |

| SUBI                     | BSXA |                | Branch to subroutine, indexed, absolute unconditional                                              | BF | _          | _          |            |    |     | į |     |    |    |   | 3     | 3      | EB                   | 5,6        |

|                          | RET  | {C<br>E        | Return from subroutine, conditional<br>Return from subroutine and<br>enable interrupt, conditional |    |            | 15<br>35   |            |    |     |   |     | •  | •  |   | 1 1   | 3<br>3 | Z<br>Z               | 8<br>8     |

- 1. Condition code (CC1, CC0): 01 if positive, 00 if zero, 10 if negative.

- 2. Condition code (CC1, CC0): 01 if R0 > r, 00 if R0 = r, 10 if R0 < r. 3. Condition code (CC1, CC0): 01 if r > V, 00 if r = V, 10 if r < V.

- 4. Condition code (CC1, CC0): 00 if all selected bits are 1s, 10 if not all the selected bits are 1s.

- 5. Index register must be register 3 or 3'.

- 6. Requires two additional cycles if indirection is specified.

- 7. Requires two additional cycles if indirection is specified and branch is taken.

- 8. Specify CC = 11 for unconditional branch.

- 9. RS, WC and COM bits in PSW are also affected.

- 10. CC assumes number in register is a binary number.

- 11. 2650B, 2650B-1 only.

- 12. For 2650B, 2650B-1, execution requires one cycle:

Table 2 INSTRUCTION SET SUMMARY (Cont'd)

|                | MNE-       | DESCRIPTION OF OPERATION              |     |            | CC |    |     |     |   | BITE |    |    |   |       |            |                   | NOTE   |

|----------------|------------|---------------------------------------|-----|------------|----|----|-----|-----|---|------|----|----|---|-------|------------|-------------------|--------|

|                | MONIC      |                                       | 3   | 2          | 1  | 0  | СС  | IDC | С | OVF  | SP | 11 | F | BYTES | CYCLES     | FORMAT (Figure 2) |        |

| E              | WRTD       | Write data                            | F3  | F2         | F1 | FO |     |     |   |      |    |    |   | 1     | 2          | Z                 |        |

| 12             | REDD       | Read data                             | 73  | 72         | 71 | 70 | •   |     |   |      |    |    |   | 1     | 2          | Z                 | 1.     |

| 15             | WRTC       | Write control                         | В3  | <b>B</b> 2 | В1 | BO |     |     |   |      |    |    | l | 1     | 2          | Z                 |        |

| 16             | REDC       | Read control                          | 33  | 32         | 31 | 30 | •   |     |   |      |    |    |   | 1     | 2          | Z                 | 1      |

| 15             | WRTE       | Write extended                        | D7` | D6         | D5 | D4 |     |     |   |      |    |    |   | 2     | 3 ·        | i                 |        |

| INPUT/OUTPUT   | REDE       | Read extended                         | 57  | 56         | 55 | 54 | •   |     |   |      |    |    |   | 2     | 3          | 1                 | 1      |

|                | HALT       | Halt, enter wait state                | _   | _          |    | 40 |     |     |   |      |    |    |   | 1     | 1          | E                 |        |

| MISC.          | NOP        | No operation                          | _   | _          | _  | CO |     | -   |   |      |    | ١. |   | 1     | 2          | E                 |        |

| Σ              | TMI        | Test under mask immediate             | F7  | F6         | F5 | F4 | •   |     |   |      |    |    |   | 2     | 3          | 1                 | 4      |

|                | LPS (U     | Load program status, upper            |     | 92         |    |    | ,   |     |   |      | •  | •  | • | 1     | 2          | E                 | 13     |

|                | · (L       | Load program status, lower            |     | 93         |    |    | •   | •   |   | •    |    |    |   | 1     | 2          | Ε                 | 9      |

| 1              | SPS {U     | Store program status, upper           |     | 12         |    |    | •   |     |   |      |    |    |   | 1     | 2          | E                 | 1 1    |

|                | ٠(١        | Store program status, lower           |     | 13         |    |    | •   |     |   |      |    |    | ĺ | 1     | 2          | E                 | 1      |

| Sn             | LDPL       | Load program status lower from memory |     | 10         |    |    | •   | •   | • | •    |    |    |   | 3     | 4          | С                 | 6,9,11 |

| PROGRAM STATUS | STPL       | Store program status lower in memory  |     | 11         |    |    |     |     |   |      |    |    |   | . 3   | 4          | C                 | 6,11   |

| ] ₹            | 000 (U     | Clear program status, upper, masked   |     | 74         |    |    |     |     |   |      | •  | •  | • | 2     | 3          | ΕI                | 13     |

| 12             | CPS {L     | Clear program status, lower, masked   |     | 75         |    |    | . • | •   | • | •    |    |    |   | 2     | 3          | ΕI                | 9      |

| PROG           | PPS (U     | Preset program status, upper, masked  |     | 76         |    |    |     |     |   |      | •  | •  | • | 2     | , <b>3</b> | Eł                | 13     |

|                | \<br> <br> | Preset program status, lower, masked  |     | 77         |    |    | •   | •   | • | •    |    |    |   | 2     | 3          | EI                | 9      |

|                | (U         | Test program status, upper, masked    |     | В4         |    |    | •   |     |   |      |    |    | 1 | 2     | 3          | El                | 4      |

|                | TPS {L     | Test program status, lower, masked    |     | <b>B</b> 5 |    |    | •   |     |   |      |    |    |   | 2     | 3          | EI                | 4      |

- 1. Condition code (CC1, CC0): 01 if positive, 00 if zero, 10 if negative.

- 2. Condition code (CC1, CC0): 01 if R0 > r, 00 if R0 = r, 10 if R0 < r. 3. Condition code (CC1, CC0): 01 if r > V, 00 if r = V, 10 if r < V.

- 4. Condition code (CC1, CC0): 00 if all selected bits are 1s, 10 if not all the selected bits

- 5. Index register must be register 3 or 3'.

- 6. Requires two additional cycles if indirection is specified.

- 7. Requires two additional cycles if indirection is specified and branch is taken.

- 8. Specify CC = 11 for unconditional branch.

- 9. RS, WC and COM bits in PSW are also affected.

- 10. CC assumes number in register is a binary number.

- 11. 2650B, 2650B-1 only.

- 12. For 2650B, 2650B-1, execution requires one cycle.

- 13. For 2650, 2650B-1, UFI and UF2 in PSU are also affected.

| ADDRESSING MODES AND II                                                      | NSTRUCTION FORMATS                                                                 |                                                                                                                     |

|------------------------------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| (Z) REGISTER ADDRESSING                                                      |                                                                                    | SYMBOLS R - Register number V - Value or condition X - Index register number I - Indirect bit                       |

| OPERATION CODE R  OPERATION CODE R/V                                         | DATA MASK OR BINARY VALUE  RELATIVE DISPLACEMENT  1 -64 \leq DISPLACEMENT \leq +63 | 3                                                                                                                   |

| (R) RELATIVE ADDRESSING OPERATION CODE R/X                                   | *INDEX HIGHER ORDER I CONTROL ADDRESS                                              | LOWER ORDER ADDRESS                                                                                                 |

| (A) ABSOLUTE ADDRESSING (NON-BRANCH INSTRUCTIONS)                            | HIGHER ORDER ADDRESS                                                               |                                                                                                                     |

| (B) ABSOLUTE ADDRESSING (BRANCH INSTRUCTION)  HIGHER ORDER ADDRESS           | PAGE                                                                               | LOWER ORDER ADDRESS                                                                                                 |

| (UNUSED) PAGE INDIRECT ADDRESSING                                            | LOWER ORDER ADDRESS                                                                | •                                                                                                                   |

| (E) MISCELLANEOUS INSTRUCTIONS                                               | HIGHER ORDER ADDRESS                                                               |                                                                                                                     |

| (C) ABSOLUTE ADDRESSING (PROGRAM STATUS LOWER MEMORY REFERENCE INSTRUCTIONS) | PAGE                                                                               | LOWER ORDER ADDRESS                                                                                                 |

|                                                                              |                                                                                    | *INDEX CONTROL 00 · Non-indexed 01 · Indexed with auto-increment 10 · Indexed with auto-decrement 11 · Indexed only |

| Figure                                                                       | 2                                                                                  |                                                                                                                     |

#### **ABSOLUTE MAXIMUM RATINGS**1

|         | PARAMETER                                 | RATING          |

|---------|-------------------------------------------|-----------------|

| $T_{A}$ | Operating temperature                     | 0°C to 70°C     |

| TSTG    | Storage temperature                       | -65°C to +150°C |

| PD      | Package power dissipation <sup>2</sup>    | 1.6W            |

|         | All input, output, and supply             | -0.5V to +6V    |

|         | voltages with respect to GND <sup>3</sup> |                 |

# DC ELECTRICAL CHARACTERISTICS $T_A = 0$ °C to 70°C, $V_{CC} = 5V \pm 5$ %.

|                                     |                                                                    |                                                                                                                             |             | LIMITS |                 |      |

|-------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------|--------|-----------------|------|

|                                     | PARAMETER                                                          | TEST CONDITIONS                                                                                                             | Min         | Тур    | Max             | UNIT |

| IIL<br>ILOH<br>ILOL                 | Current<br>Input load<br>Output high leakage<br>Output low leakage | V <sub>IN</sub> = 0 to 5.25V<br>ADREN, DBUSEN = 2.2V V <sub>OUT</sub> = 4V<br>ADREN, DBUSEN = 2.2V V <sub>OUT</sub> = 0.45V |             |        | 10<br>10<br>10  | μА   |

| V <sub>IH</sub><br>V <sub>IL</sub>  | Voltage levels<br>Input high<br>Input low                          |                                                                                                                             | 2.2<br>-0.5 |        | V <sub>CC</sub> | ٧    |

| V <sub>OH</sub><br>V <sub>OL</sub>  | Output high<br>Output low                                          | $I_{OH} = -100\mu A$<br>$I_{OL} = 1.6ma$                                                                                    | 2.4<br>0    |        | 0.45            |      |

| lcc                                 | Power supply current                                               | V <sub>CC</sub> = 5.25V T <sub>A</sub> = 0°C                                                                                |             |        | 150             | mA   |

| C <sub>IN</sub><br>C <sub>OUT</sub> | Capacitance<br>Input<br>Output                                     | V <sub>IN</sub> = 0V<br>V <sub>OUT</sub> = 0V                                                                               |             |        | 10<br>10        | pF   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operation sections of this specification is not implied.

For operating at elevated temperatures the device must be derated based on +150°C

maximum junction temperature and thermal resistance of 50°C/W junction to ambient (40

pin IW package).

This product includes circuitry specifically designed for the protection of its internal

devices from the damaging effects of excessive static charge. However, it is suggested

that conventional precautions be taken to avoid applying any voltages larger than the

rated maxima.

MCKOPHOLESSOR 2650 SERIES

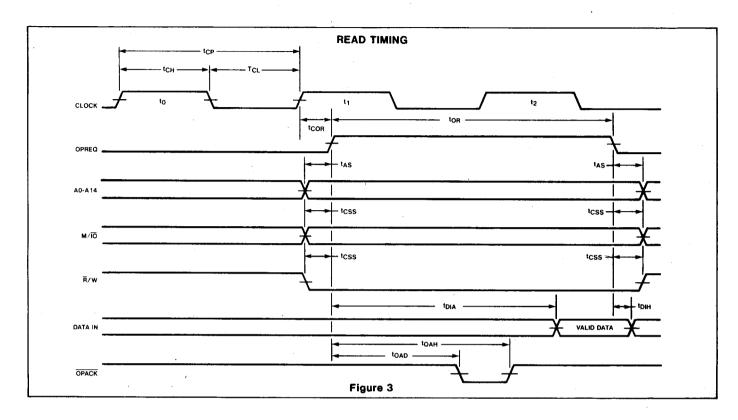

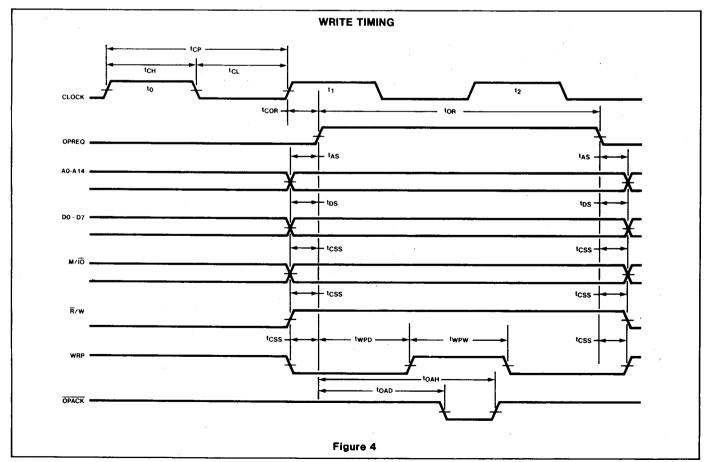

# AC CHARACTERISTICS $T_A = 0$ °C to +70°C, $V_{CC} = 5V \pm 5\%$

|                  | DIDINETED                                                      | LIM                                                                                | ITS                                            |      |

|------------------|----------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------------------|------|

|                  | PARAMETER                                                      | Min                                                                                | Max                                            | UNIT |

| tAS              | Address stable                                                 | 50                                                                                 |                                                | ns   |

| <sup>t</sup> TVD | 3-State enable delay time (2650A, A-1)                         |                                                                                    | 250                                            | ns   |

| tVTD             | 3-State disable delay time (2650A, A-1)                        |                                                                                    | 150                                            | ns   |

| <sup>t</sup> EBD | Enable to bus delay (2650B, B-1)                               |                                                                                    | 180                                            | ns   |

| t <sub>EOD</sub> | Enable to OPREQ <sup>7</sup> (2650B, B-1)                      |                                                                                    | 230                                            | ns   |

| tDS              | Data out stable                                                | 50                                                                                 |                                                | ns   |

| <sup>t</sup> DIH | Data in hold                                                   | 0                                                                                  |                                                | ns   |

| <sup>†</sup> DIA | Data in access time (2650A-1, B-1)<br>(2650A, B)               | t <sub>CP</sub> + t <sub>CL</sub> - 200<br>t <sub>CP</sub> + t <sub>CL</sub> - 300 |                                                | ns   |

| <sup>t</sup> CH  | Clock high phase (2650A-1, B-1)<br>(2650A, B)                  | 250<br>400                                                                         |                                                | ns   |

| tCL              | Clock low phase (2650A-1, B-1)<br>(2650A, B)                   | 250<br>400                                                                         |                                                | ns   |

| t <sub>CP</sub>  | Clock period (2650A-1, B-1)<br>(2650A, B)                      | 500<br>800                                                                         |                                                | ns   |

| tPC              | Processor cycle time <sup>6</sup> (2650A-1, B-1)<br>(2650A, B) | 1500<br>2400                                                                       |                                                | ns   |

| tOR              | OPREQ pulse width <sup>6</sup>                                 | t <sub>CP</sub> + t <sub>CL</sub> - 50                                             | t <sub>CP</sub> + t <sub>CL</sub> + 75         | ns   |

| <sup>t</sup> COR | Clock to OPREQ time (2650A-1, B-1)<br>(2650A, B)               | 50<br>50                                                                           | 200<br>300                                     | ns   |

| tOAD             | OPACK delay time (2650A-1, B-1)<br>(2650A, B)                  |                                                                                    | t <sub>CP</sub> - 250<br>t <sub>CP</sub> - 350 | ns   |

| <sup>t</sup> OAH | OPACK hold time                                                | · t <sub>CP</sub>                                                                  |                                                | ns   |

| tcss             | Control signal stable                                          | 50                                                                                 |                                                | ns   |

| tWPD             | Write pulse delay                                              | t <sub>CH</sub> - 50                                                               | t <sub>CH</sub> +100                           | ns   |

| twpw             | Write pulse width <sup>6</sup>                                 | t <sub>CL</sub> - 50                                                               | t <sub>CL</sub> + 75                           | ns   |

| tIRH .           | INTREQ hold time                                               | 0                                                                                  |                                                | ns   |

| <sup>t</sup> PSE | Pause delay                                                    |                                                                                    | t <sub>CP</sub>                                | ns   |

| <sup>t</sup> RST | Reset width                                                    | 3t <sub>CP</sub>                                                                   |                                                |      |

| tOCD             | to to CYLAST delay (2650B, B-1)                                | ,                                                                                  | 450                                            | ns   |

<sup>1.</sup> Input levels swing between 0.80 and 2.2 volts.

<sup>2.</sup> Input signal transition times are 20ns.

<sup>3.</sup> Timing reference level is 1.5 volts.

<sup>4.</sup> Output load is  $-100\mu\text{A}$  at 100pF and 1 TTL load.

<sup>5.</sup> Processor cycle time consists of three clock periods.

<sup>6.</sup> These values assume that OPACK is returned in time to not cause the processor to idle. Otherwise, the specified maximum will increase by an integral number of clock cycles. 7.  $t_{EOD}$  is bounded by  $t_{EBD}$  + 10ns  $\leq t_{EOD} \leq t_{EBD}$  + 50ns.

MICROPROCESSOR 2650 SERIES

Argentina: FAPESA I.y.C., Av. Crovara 2550, Tablada, Prov. de BUENOS AIRES, Tel. 652-7438/7478.

Australia: PHILIPS INDUSTRIES HOLDINGS LTD., Elcoma Division, 67 Mars Road, LANE COVE, 2066, N.S.W., Tel. 427 08 88.

Austria: ÖSTERREICHISCHE PHILIPS BAUELEMENTE Industrie G.m.b.H., Triester Str. 64, A-1101 WIEN, Tel. 62 91 11.

Belgium: M.B.L.E., 80, rue des Deux Gares, B-1070 BRUXELLES, Tel. 523 00 00.

Brazil: IBRAPE, Caixa Postal 7383, Av. Brigadeiro Fari Alima, 1735 SAO PAULO, SP, Tel. (011) 211-2600.

Canada: PHILIPS ELECTRONICS LTD., Electron Devices Div., 601 Milner Ave., SCARBOROUGH, Ontario, M1B 1M8, Tel. 292-5161.

Chile: PHILIPS CHILENA S.A., Av. Santa Maria 0760, SANTIAGO, Tel. 39-40 01.

Colombia: SADAPE S.A., P.O. Box 9805, Calle 13, No. 51 + 39, BOGOTA D.E. 1., Tel. 600 600. Denmark: MINIWATT A/S, Emdrupvej 115A, DK-2400 KØBENHAVN NV., Tel. (01) 69 16 22.

Finland: OY PHILIPS AB, Elcoma Division, Kaivokatu 8, SF-00100 HELSINKI 10, Tel. 1 72 71.

France: R.T.C. LA RADIOTECHNIQUE-COMPELEC, 130 Avenue Ledru Rollin, F-75540 PARIS 11, Tel. 355-44-99.

Germany: VALVO, UB Bauelemente der Philips G.m.b.H., Valvo Haus, Burchardstrasse 19, D-2 HAMBURG 1, Tel. (040) 3296-1.

Greece: PHILIPS S.A. HELLENIQUE, Elcoma Division, 52, Av. Syngrou, ATHENS, Tel. 915 311.

Hong Kong: PHILIPS HONG KONG LTD., Elcoma Div., 15/F Philips Ind. Bldg., 24-28 Kung Yip St., KWAI CHUNG, Tel. NT 24 51 21.

India: PHILIPS INDIA LTD., Elcoma Div., Band Box House, 254-D, Dr. Annie Besant Rd., Prabhadevi, BOMBAY-25-DD, Tel. 457 311-5.

Indonesia: P.T. PHILIPS-RALIN ELECTRONICS, Elcoma Division, 'Timah' Building, Jl. Jen. Gatot Subroto, P.O. Box 220, JAKARTA, Tel. 44 163.

Ireland: PHILIPS ELECTRICAL (IRELAND) LTD., Newstead, Clonskeagh, DUBLIN 14, Tel. 69 33 55.

Italy: PHILIPS S.p.A., Sezione Elcoma, Piazza IV Novembre 3, I-20124 MILANO, Tel. 2-6994.

Japan: NIHON PHILIPS CORP., Shuwa Shinagawa Bldg., 26-33 Takanawa 3-chome, Minato-ku, TOKYO (108), Tel. 448-5611.

(IC Products) SIGNETICS JAPAN, LTD., TOKYO, Tel. (03) 230-1521.

Korea: PHILIPS ELECTRONICS (KOREA) LTD., Elcoma Div., Philips House, 260-199 Itaewon-dong, Yongsan-ku, C.P.O. Box 3680, SEOUL, Tel. 794-4202.

Malaysia: PHILIPS MALAYSIA SDN. BERHAD, Lot 2, Jalan 222, Section 14, Petaling Jaya, P.O.B. 2163, KUALA LUMPUR, Selangor, Tel. 77 44 11.

Mexico: ELECTRONICA S.A. de C.V., Varsovia No. 36, MEXICO 6, D.F., Tel. 533-11-80.

Netherlands: PHILIPS NEDERLAND B.V., Afd. Elonco, Boschdijk 525, 5600 PD EINDHOVEN, Tel. (040) 79 33 33.

New Zealand: PHILIPS ELECTRICAL IND. LTD., Elcoma Division, 2 Wagener Place, St. Lukes, AUCKLAND, Tel. 867 119,

Norway: NORSK A/S PHILIPS, Electronica, Sørkedalsveien 6, OSLO 3, Tel. 46 38 90.

Peru: CADESA, Rocca de Vergallo 247, LIMA 17, Tel. 62 85 99.

Philippines: PHILIPS INDUSTRIAL DEV. INC., 2246 Pasong Tamo, P.O. Box 911, Makati Comm. Centre, MAKATI-RIZAL 3116, Tel. 86-89-51 to 59.

Portugal: PHILIPS PORTUGESA S.A.R.L., Av. Eng. Duhárte Pacheco 6, LISBOA 1, Tel. 68 31 21.

Singapore: PHILIPS PROJECT DEV. (Singapore) PTE LTD., Elcoma Div., P.O.B. 340, Toa Payoh CPO, Lorong 1, Toa Payoh, SINGAPORE 12, Tel. 53 88 11.

South Africa: EDAC (Pty.) Ltd., South Park Lane, New Doornfontein, JOHANNESBURG 2001, Tel. 24/6701.

Spain: COPRESA S.A., Balmes 22, BARCELONA 7, Tel. 301 63 12.

Sweden: A.B. ELCOMA, Lidingövägen 50, S-115 84 STOCKHOLM 27, Tel. 08/67 97 80.

Switzerland: PHILIPS A.G., Elcoma Dept., Allmendstrasse 140-142, CH-8027 ZÜRICH, Tel. 01/43 22 11.

Taiwan: PHILIPS TAIWAN LTD., 3rd Fl., San Min Building, 57-1, Chung Shan N. Rd, Section 2, P.O. Box 22978, TAIPEI, Tel. 5513101-5.

Thalland: PHILIPS ELECTRICAL CO. OF THAILAND LTD., 283 SIIOM Road, P.O. Box 961, BANGKOK, Tel. 233-6330-9.

Turkey: TÜRK PHILIPS TICARET A.S., EMET Department, Inonu Cad. No. 78-80, ISTANBUL, Tel. 43 59 10.

United Kingdom: MULLARD LTD., Mullard House, Torrington Place, LONDON WC1E 7HD, Tel. 01-580 6633.

United States: (Active devices & Materials) AMPEREX SALES CORP., Providence Pike, SLATERSVILLE, R.I. 02876, Tel. (401) 762-9000.

(Passive devices) MEPCO/ELECTRA INC., Columbia Rd., MORRISTOWN, N.J. 07960, Tel. (201) 539-2000.

(IC Products) SIGNETICS CORPORATION, 811 East Arques Avenue, SUNNYVALE, California 94086, Tel. (408) 739-7700.

Uruguay: LUZILECTRON S.A., Rondeau 1567, piso 5, MONTEVIDEO, Tel. 9 43 21.

Venezuela: IND. VENEZOLANAS PHILIPS S.A., Elcoma Dept., A. Ppal de los Ruices, Edif. Centro Colgate, CARACAS, Tel. 36 05 11.

i2 © 1979N.V. Philips' Gloeilampenfabrieken

This information is furnished for guidance, and with no guarantees as to its accuracy or completeness; its publication conveys no licence under any patent or other right, nor does the publisher assume liability for any consequence of its use; specifications and availability of goods mentioned in it are subject to change without notice; it is not to be reproduced in any way, in whole or in part, without the written consent of the publisher.