#### PRELIMINARY

#### **FEATURES**

- 4096-bit Serial Architecture

- -256 registers, 16 bits each

- -Nonvolatile data storage

- -Single 5V supply

- Versatile, Easy-to-Use Interface

- -READY/BUSY status signal

- -Automatic write cycle time-out

- -Software controlled write protection

- Advanced CMOS E<sup>2</sup>PROM Technology

- Low Power Consumption

- -3mA max. active

- -1mA max. standby, TTL

- -25µA max. standby CMOS

- Up to 10,000 Erase/Write Cycles Per Register

- 10 Year Data Retention

#### **OVERVIEW**

The XL90C41 is a 4096-bit, nonvolatile, serial E<sup>2</sup>PROM. It is fabricated using EXEL's advanced CMOS E<sup>2</sup>PROM technology. The XL90C41 provides external read/write memory arranged as 256 registers of 16 bits each. Five 8-bit instructions control the operation of the device, which include read, write, enable and status functions. The XL90C41 has been designed for applications requiring up to 10,000 erase/write cycles per register. In the standby mode, the XL90C41 reduces power consumption by more than 80%, compared to an NMOS counterpart.

# 4096-Bit Serial (5V) Electrically Erasable PROM

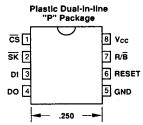

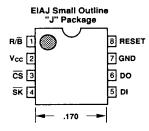

#### PIN CONFIGURATIONS

#### PIN NAMES

| CS    | Chip Select        |

|-------|--------------------|

| SK    | Serial Data Clock  |

| DI    | Serial Data Input  |

| DO    | Serial Data Output |

| GND   | Ground             |

| RESET | Reset Input        |

| R/B   | READY/BUSY Output  |

| Vcc   | Power Supply       |

|       |                    |

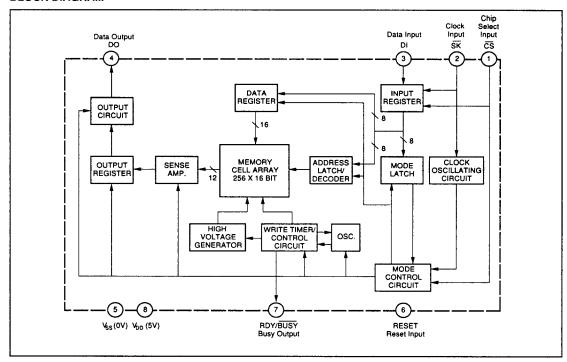

#### **BLOCK DIAGRAM**

#### **APPLICATIONS**

The XL90C41 is ideal for high volume applications requiring low density data storage. It uses a low cost, space saving 8-pin package, and readily interfaces with standard microprocessors and popular microcontrollers such as the 8048/49/51/96, the COP4XX series, the 6801/05, the TMS1000 and the Z8.

Candidate applications include alarm devices, appliances, computer terminals and smart cards, electronic locks, meters, robotics and telephone, to name just a few.

#### **ENDURANCE AND DATA RETENTION**

The XL90C41 is designed for applications requiring up to 10,000 write cycles per bit. It provides 10 years of secure data retention, with or without power applied.

# **DEVICE OPERATION**

The XL90C41 is a clocked serial port compatible E<sup>2</sup>PROM. Input data is latched on the rising edge of the clock, and data is output on the falling edge of the clock.

Data is grouped in 8-bit bytes. The beginning 8 bits specify the mode, the next 8 bits specify the address, and subsequent 16 bits specify the I/O data.

During the self-timed internal programming cycle that accompanies a write, the  $\overline{SK}$  clock is de-activated. It is needed only when instructions or data are being passed to or from the memory.

Any of the six modes (read, write, write enable, write disable, erase all and write all ) may be specified. The write time is set by internal timer, and determination of whether a write operation is in progress or not can be made from the status of the READY/BUSY pin. When the asynchronous RESET pin is taken HIGH, any ongoing operation is immediately halted.

Read (READ)

The read instruction is the only instruction that outputs serial data on the DO pin. After the read instruction and address have been decoded, data is transferred from the selected memory register into the output register. The output on DO changes during the HIGH to LOW transition of  $\overline{SK}$ .

Write (WRITE)

After a write instruction and its address have been decoded, the device expects 16 bits of data. These are to be transferred into the specific memory register which has previously been automatically erased. After the last data bit has been clocked into DI on the 32nd clock edge, the self-timed internal programming cycle is initiated. The write cycle status can be monitored by observing the READY/BUSY pin.

Write Enable/Disable (EWEN, EWDS) — When the XL90C41 is powered up, it comes up in the write disabled state. In order to be programmable, it must receive an enable instruction. The device remains programmable until a disable instruction is entered, or until it is powered down. The disable instruction provides protection against inadvertent writes. Read capability is not affected.

# Erase All (ERAL)

Full-chip erase is provided for ease in programming. Erasing the entire chip involves setting all bits in the entire memory array to a logical "1."

Write All (WRAL)

The write all command forces all registers in the memory array to an arbitrary 16-bit pattern. Like the standard write instruction, this instruction is followed by 16-bits of serial data on the DI pin. The erase all command should be entered before forcing write all command.

## INSTRUCTION SET

| Instruction                | Start<br>Bits | OP<br>Code | Address                        | Input<br>Data                   |

|----------------------------|---------------|------------|--------------------------------|---------------------------------|

| READ                       | 1010          | 1000       | A <sub>0</sub> -A <sub>7</sub> |                                 |

| WRITE                      | 1010          | 0100       | A0-A7                          | D <sub>0</sub> -D <sub>15</sub> |

| Erase/Write Enable (EWEN)  | 1010          | 0011       | xxxxxxx                        |                                 |

| Erase/Write Disable (EWDS) | 1010          | 0000       | xxxxxxxx                       |                                 |

| Erase All Registers (ERAL) | 1010          | 0010       | xxxxxxx                        |                                 |

| Write All Registers (WRAL) | 1010          | 0001       | xxxxxxx                        | D <sub>0</sub> -D <sub>15</sub> |

### **ABSOLUTE MAXIMUM RATINGS**

| Temperature under bias                                                                                                    | 40°C to +70°C                   |

|---------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Storage Temperature.                                                                                                      | 65°C to +150°C                  |

| Lead Soldering Temperature (less than 10 seconds)                                                                         | 300°C                           |

| Supply Voltage                                                                                                            | 0 to 6.5V                       |

| Supply Voltage                                                                                                            | 0.3 to Vcc + 0.3V               |

| ESD Řating NOTE: These are STRESS ratings only. Appropriate conditions for operating these devices are given elsewhere is | 2000V                           |

| NOTE: These are STRESS ratings only. Appropriate conditions for operating these devices are given elsewhere it            | in this specification. Stresses |

| beyond those listed here may permanently damage the part. Prolonged exposure to maximum ratings may affect d              | levice reliability.             |

DC ELECTRICAL CHARACTERISTICS TA =  $0^{\circ}$ C to  $+70^{\circ}$ C for the XLS90C41 or  $-40^{\circ}$ C to  $+85^{\circ}$ C for XLE90C41,  $V_{CC} = 5V \pm 10\%$

|        |                     | XLS                                      | XLS90C41 |         | XLE90C41 |         |       |

|--------|---------------------|------------------------------------------|----------|---------|----------|---------|-------|

| Symbol | Parameter           | Conditions                               | Min      | Max     | Min      | Max     | Units |

| Icc1   | Operating Current   | CS = VIH, SK = 1MHz<br>CMOS Input Levels |          | 3       |          | 3       | mA    |

| ICC2   | Operating Current   | CS = ViH, SK = 1MHz<br>TTL Input Levels  |          | 3       |          | 3       | mA    |

| ICC3   | Standby Current     | CS = 0V DI = SK = PE = Vcc               |          | 100, 3* |          | 100, 3* | μA    |

| tu     | Input Leakage       | Vin = 0V to Vcc, CS, SK, DI              |          | 2       |          | 2       | μA    |

| lıo    | Output Leakage      | Vout = 0V to Vcc                         |          | 2       |          | 2       | μA    |

| VIL    | Input Low Voltage   |                                          |          | 0.8     |          | 0.8     | ٧     |

| ViH    | Input High Voltage  |                                          | 2.0      |         | 2        |         | ٧     |

| Vol1   | Output Low Voltage  | IOL = 2.1mA TTL                          | 2.4      |         | 2.4      |         | ٧     |

| Vон1   | Output High Voltage | IOH = -400µA TTL                         |          | 0.4     |          | 0.4     | ٧     |

| Vol2   | Output Low Voltage  | IoL = 10μA CMOS                          |          | 0.2     |          | 0.2     | ٧     |

| Voн2   | Output High Voltage | IOH = -10µA CMOS                         | Vcc-0.2  |         | Vcc-0.2  |         | V     |

<sup>\*</sup>  $-A = 100\mu A$ ,  $-B = 3\mu A$

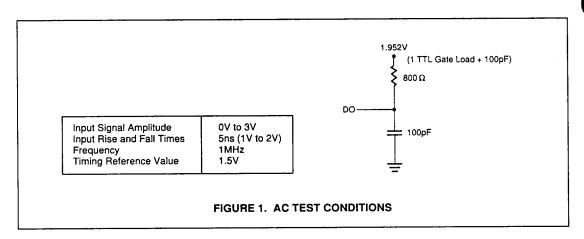

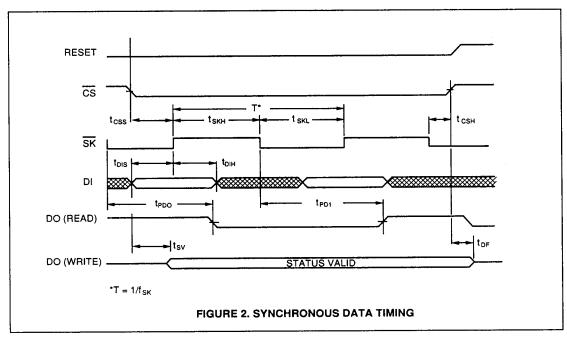

# AC ELECTRICAL CHARACTERISTICS

TA = 0°C to +70°C for the XLS90C41 or -40°C to +85°C for the XLE90C41,  $V_{CC} = 5V \pm 10\%$

|                  | 1                    |                   | XLS | XLS90C41 |     | XLE90C41 |     |

|------------------|----------------------|-------------------|-----|----------|-----|----------|-----|

| Symbol Parameter | Conditions           | Min               | Max | Min      | Max | Units    |     |

| fsĸ              | SK Clock Frequency   |                   |     | 1        |     | 1        | MHz |

| tskh             | SK HIGH Time         |                   | 450 |          | 450 |          | ns  |

| tskl             | SK LOW Time          |                   | 450 |          | 450 |          | ns  |

| tcs              | Minimum CS HIGH Time |                   | 1   |          | 1   |          | þs  |

| tcss             | CS Setup Time        | Relative to SK 7- | 200 |          | 200 |          | ns  |

| tois             | DI Setup Time        | Relative to SK ~L | 150 |          | 150 |          | ns  |

| tcsн             | CS Hold Time         | Relative to SK    | 0   |          | 0   |          | ns  |

| toih             | DI Hold Time         | Relative to SK ~_ | 150 |          | 150 |          | ns  |

| tPD1             | Output Delay to "1"  | AC Test           |     | 350      |     | 350      | ns  |

| tPD0             | Output Delay to "0"  | AC Test           |     | 350      |     | 350      | ns  |

| tsv              | CS to Status Valid   | AC Test           |     | 1        |     | 1        | μs  |

| tor              | CS to DO in 3-state  | CS = VIL          |     | 400      |     | 400      | ns  |

| te/w             | Write Cycle Time     |                   |     | 10       |     | 10       | ms  |

### CAPACITANCE

$T_A = 25^{\circ}C$ , f = 1MHz

| Symbol | Parameter          | Max | Units |

|--------|--------------------|-----|-------|

| Cin    | Input Capacitance  | 5   | pF    |

| Соит   | Output Capacitance | 5   | pF    |

2-275

| CS Itcs                  | t <sub>cs</sub>                                                                                   |

|--------------------------|---------------------------------------------------------------------------------------------------|

| DI101010                 | 0 0 (A0(A1)(A2)(A3)(A4)(A5)(A6)(A7)(X Data In - Don't Care)(5)(XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |

| sk xxx เป๋ เป๋เป๋เป๋เป๋เ | 1 7 8 8 10 11 12 13 14 15 16 17 18 19 20 21 xx 30 31 32                                           |

| DO HIGH Z                | Dummy<br>Bit (DD)(D1)(D2)(D3)(; )(D13)(D14)(D15) HIGH Z                                           |

| R/B = HIGH               |                                                                                                   |

|                          | FIGURE 3. READ CYCLE TIMING                                                                       |

| CS Itcs                                       |                                                          |

|-----------------------------------------------|----------------------------------------------------------|

| DI                                            | A4XA5XA6XA7X00X01X02X03X(;;)X012X013X014X015XXXXXXXXXXXX |

| sk <b>xxx บ</b> น่นั้นนั้นนั้นนั้นนั้นไม่นั้น | 3 14 15 16 17 18 19 20 xx 29 30 31 32<br>                |

| R/B HIGH (READY)                              | BUSY READY                                               |

| DO HIGH Z                                     |                                                          |

| FIGURE 4. WRIT                                | TE CYCLE TIMING                                          |

| CS Ttcs                           | tcs                                    |

|-----------------------------------|----------------------------------------|

| DI10110 0 01 1 \XXXXXXXXXXXXXXXX  | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |

| $\overline{sk}$ $\underline{xxx}$ | 14 15 16                               |

| R/B HIGH (READY)                  |                                        |

| DO HIGH Z                         |                                        |

| FIGURE 5. WRITE ENAB              | LE (EWEN) CYCLE TIMING                 |

| OS Itos            | t <sub>cs</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DI                 | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| sk xxxvivivivivivi | 11 12 13 14 15 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| R/B HIGH (READY)   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DO HIGH Z          | And the state of t |

SERIAL 2 P DCTS

| <del>cs</del> | t <sub>cs</sub> t <sub>cs</sub> t <sub>cs</sub>     |

|---------------|-----------------------------------------------------|

|               | TIOITO O OITO AXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |

| R/B           | HIGH (READY)  READY  HIGH Z                         |

| DO            | FIGURE 7. ERASE ALL (ERAL) CYCLE TIMING             |

| CS T <sub>CS</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| SK         XXXX         X | <i>"</i>            |

| R/B HIGH (READY)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BUŞY READY          |

| DO HIGH Z  FIGURE 8. WRITE ALL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | (WRAL) CYCLE TIMING |