# 4,096-Bit Serial Electrically Erasable PROM 2.7 to 5.5 Volt Operation

# FEATURES

- Low Power CMOS

- Active current less than 3mA

Standby current less than 5μA

- Hardware Write Protection

Write Control pin

- 2.7 to 5.5V Operation

- Extended Temperature Range: -40°C to +85°C

- Internally Organized as Two Banks

Each 256 x 8

- Two Wire Serial Interface (I<sup>2</sup>C<sup>™</sup>)

Bidirectional data transfer protocol

- Sixteen-Byte Page-Write Mode

Minimizes total write time per byte

- Automatic Word Address Incrementing

Sequential register read

- Self-Timed Write Cycle

- High Reliability

- Endurance: 100,000 write cycles

Data retention: 100 years

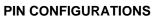

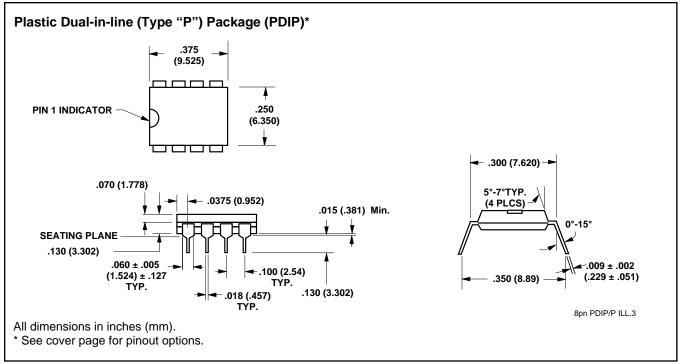

- 8-Pin PDIP or SOIC Packages

# OVERVIEW

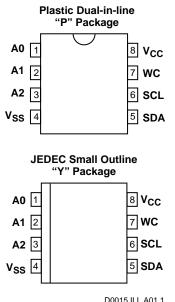

The XL24C04 is a cost-effective, 4,096-bit serial  $E^2$ PROM. It is fabricated using EXEL's advanced CMOS  $E^2$ PROM technology. This part operates from a single power supply over the range of 2.7 to 5.5 volts.

The XL24C04 is internally organized as two 256 x 8 memory banks. It features the  $I^2C$  serial interface and software protocol allowing operation on a simple two-wire bus. Up to four XL24C04s may be individually addressed on the two-wire bus by establishing their device address using the address input pins (A1 and A2).

# **PIN DESCRIPTIONS**

Serial Clock (SCL) - The SCL input is used to clock data into and out of the device. In the WRITE mode, data must remain stable while SCL is HIGH. In the READ mode, data is clocked out on the falling edge of SCL.

Serial Data (SDA) - The SDA pin is a bidirectional pin used to transfer data into and out of the device. Data may change only when SCL is LOW, except START and STOP

# PIN NAMES

| A0-A2 | Address Inputs      |

|-------|---------------------|

| SDA   | Serial Data I/O     |

| SCL   | Serial Clock Input  |

| WC    | Write Control Input |

| Vss   | Ground              |

| Vcc   | Supply Voltage      |

conditions. It is an open-drain output and may be wire-ORed with any number of open-drain or open-collector outputs.

Address (A0) - The A0 pin is not electrically connected internally. It can be connected to  $V_{SS}$  or left floating. It must not be connected to  $V_{CC}$ .

Address (A1, A2) - The address input pins are used to set the two-bit device address of the XL24C04 which will identify it on the two-wire bus. These inputs may be tied HIGH, LOW, or they may be actively driven. These inputs allow up to four XL24C04 devices to be distinguished on the bus.

Write Control (WC) - The Write Control input pin is used to disable the write circuitry to the memory. When HIGH, the write function is disabled, protecting previously written data; when LOW, the write function is enabled.

## **BLOCK DIAGRAM**

#### ENDURANCE AND DATA RETENTION

The XL24C04 is designed for applications requiring up to 100,000 write cycles and unlimited read cycles. It provides 100 years of secure data retention, with or without power applied, after the execution of 100,000 write cycles.

# **APPLICATIONS**

The XL24C04 is ideal for applications requiring low voltage and low power consumption. This device uses a cost effective, space-saving, 8-pin plastic package. Typical applications include, alarm devices, electronic locks, meters, keys, pagers and cellular phones.

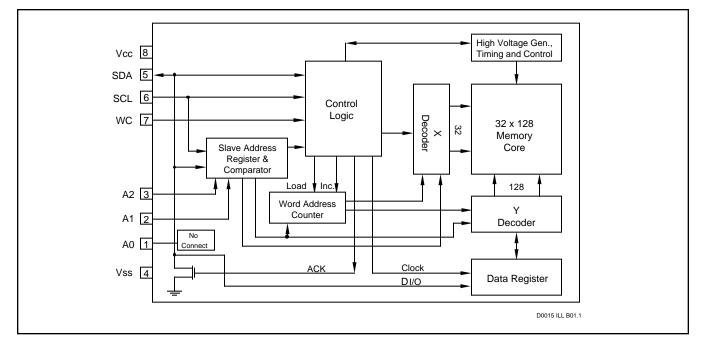

#### CHARACTERISTICS OF THE I<sup>2</sup>C BUS

#### **General Description**

The I<sup>2</sup>C bus was designed for two-way, two-line serial communication between different integrated circuits. The two lines are: a serial data line (SDA), and a serial clock line (SCL). The SDA line must be connected to a positive supply by a pull-up resistor, located somewhere on the bus (See Figure 1). Data transfer between devices may be initiated with a START condition only when SCL and SDA are HIGH (bus is not busy).

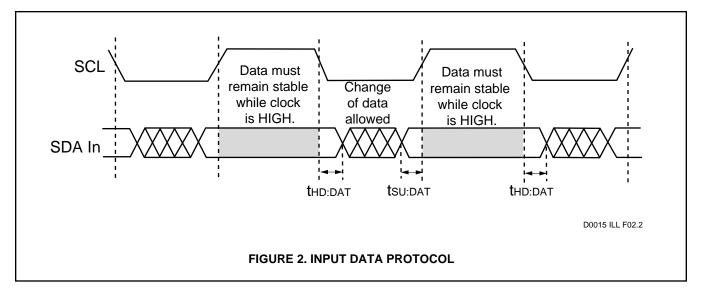

#### **Input Data Protocol**

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during clock HIGH time, because changes on the data line while SCL is HIGH will be interpreted as start or stop condition (See Figure 2.)

#### **START and STOP Conditions**

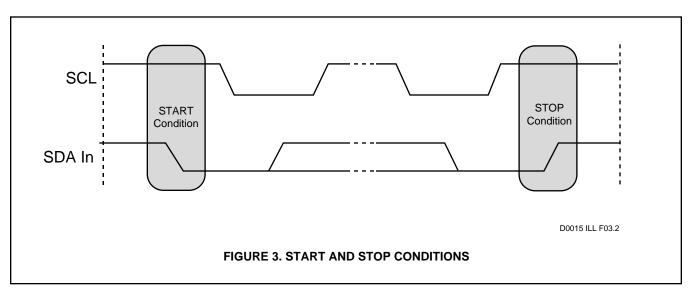

When both the data and clock lines are HIGH, the bus is said to be not busy. A HIGH-to-LOW transition on the data line, while the clock is HIGH, is defined as the "START" condition. A LOW-to-HIGH transition on the data line, while the clock is HIGH, is defined as the "STOP" condition (See Figure 3.)

#### **DEVICE OPERATION**

The XL24C04 is a 4,096-bit serial E<sup>2</sup>PROM. The device supports the I<sup>2</sup>C bidirectional data transmission protocol. The protocol defines any device that sends data onto the bus as a "transmitter" and any device which receives data as a "receiver." The device controlling data transmission is called the "master" and the controlled device is called the "slave." In all cases, the XL24C04 will be a "slave" device, since it never initiates any data transfers.

Up to four XL24C04s can be connected to the bus, selected by the A1 and A2 device addresses. A0 is not connected internally. A1 and A2 must be connected to either  $V_{CC}$ ,  $V_{SS}$ or they may be actively driven. A1 and A2 define the device address. Other devices may be connected to the bus, but need a different device identification code.

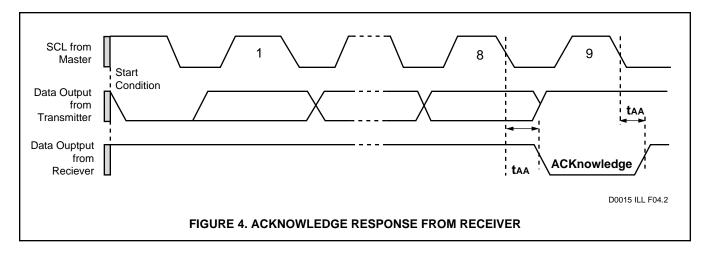

# Acknowledge (ACK)

Acknowledge is a software convention used to indicate successful data transfers. The transmitting device, either the master or the slave, will release the bus after transmitting eight bits. During the ninth clock cycle, the receiver will pull the SDA line LOW to ACKnowledge that it received the eight bits of data (See Figure 4.)

The XL24C04 will respond with an ACKnowledge after recognition of a START condition and its slave address byte. If both the device and a write operation are selected, the XL24C04 will respond with an ACKnowledge after the receipt of each subsequent 8-bit word.

In the READ mode, the XL24C04 transmits eight bits of data, then releases the SDA line, and monitors the line for an ACKnowledge signal. If an ACKnowledge is detected, and no STOP condition is generated by the master, the XL24C04 will continue to transmit data. If an ACKnowledge is not detected, the XL24C04 will terminate further data transmissions and awaits a STOP condition before returning to the standby power mode.

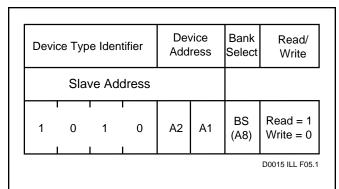

#### Slave Address Byte

Following a START condition, the master must output the device address of the slave to be accessed. The most significant four bits of the slave address are the "device type identifier." The XL24C04 address identifier is 1010 (See Figure 5.)

The next two bits are device address, addressing a particular device. Using this addressing scheme, a system may cascade up to four XL24C04 devices on the bus. The device address is defined by the state of the A1 and A2 input pins.

# Bank Select Bit

The next bit of the serial stream is the bank select bit. It is used by the host to toggle between the two 2K-bit banks of memory. It is, in effect, the most significant bit of the word address, or A8.

#### Read/Write Bit

The last bit of the data stream defines the operation to be performed. When set to "1," a read operation is selected; when set to "0," a write operation is selected.

#### FIGURE 5. SLAVE ADDRESS BYTE

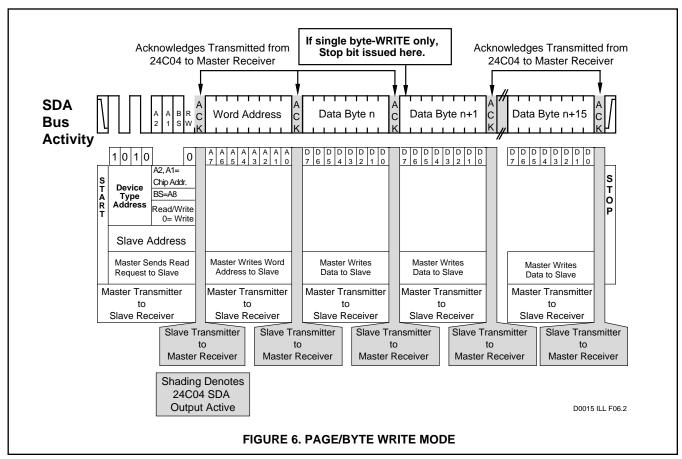

## WRITE OPERATIONS

The XL24C04 allows two types of write operations: byte write and page write. The byte write operation writes a single byte during the nonvolatile write period ( $t_{WR}$ ). The page write operation allows up to full 16-byte in the same page to be stored during  $t_{WR}$ .

#### Byte WRITE

After the slave address is sent (to identify the slave device, select the bank and specify a read or write operation), a second byte is transmitted which contains the word address of any one of the 256 words in the bankselected by the slave address byte.

Upon receipt of the word address, the XL24C04 responds with an ACKnowledge, and waits for the next byte of data, again responding with an ACKnowledge. The master then terminates the transfer by generating a STOP condition, at which time the XL24C04 begins the internal write cycle.

While the internal write cycle is in progress, the XL24C04 inputs are disabled, and the device will not respond to any requests from the master. Refer to Figure 6 for the address, ACKnowledge and data transfer sequence.

#### Page WRITE

The XL24C04 is capable of a 16-byte page write operation. It is initiated in the same manner as the byte-write operation, but instead of terminating the write cycle after the first data word, the master can transmit up to 15 more words of data. After the receipt of each word, the XL24C04 will respond with an ACKnowledge.

The XL24C04 automatically increments the address for subsequent data words. After the receipt of each word, the four low order address bits are internally incremented by one. The high order five bits of the address byte remain constant. Should the master transmit more than sixteen words, prior to generating the STOP condition, the address counter will "roll over," and the previously written data will be overwritten. As with the byte-write operation, all inputs are disabled during the internal write cycle. Refer to Figure 6 for the address, ACKnowledge and data transfer sequence.

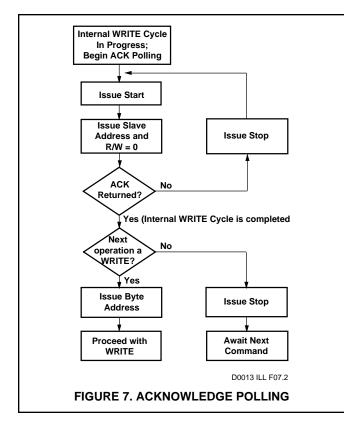

# Acknowledge Polling

When the XL24C04 is performing an internal WRITE operation, it will ignore any new START conditions. Since the device will only return an acknowledge after it accepts the START, the part can be continuously queried until an acknowledge is issued, indicating that the internal WRITE cycle is complete.

To poll the device, give it a START condition, followed by a slave address for a WRITE operation (See Figure 7).

### **READ OPERATIONS**

Read operations are initiated with the R/W bit of the identification field set to "1." There are four different read options:

- 1. Current Address Byte Read

- 2. Random Address Byte Read

- 3. Current Address Sequential Read

- 4. Random Address Sequential Read

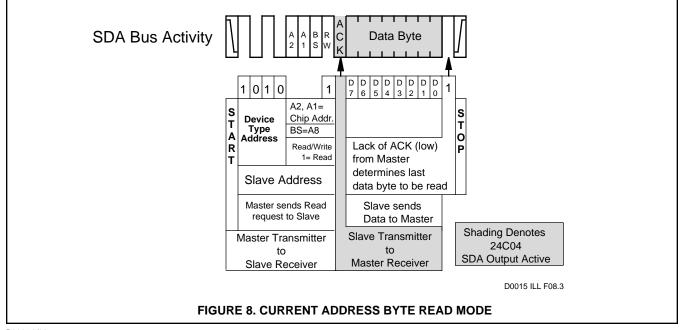

#### Current Address Byte Read

The XL24C04 contains an internal address counter which maintains the address of the last word accessed, incremented by one. If the last address accessed (either a read or write) was to address location n, the next read operation would access data from address location n+1 and increment the current address pointer. When the XL24C04 receives the slave address field with the R/W bit set to "1," it issues an acknowledge and transmits the 8-bit word stored at address location n+1.

The current read operation only accesses a single byte of data. The master does not acknowledge the transfer, but does generate a stop condition. At this point, the XL24C04 discontinues data transmission. See Figure 8 for the address acknowledge and data transfer sequence.

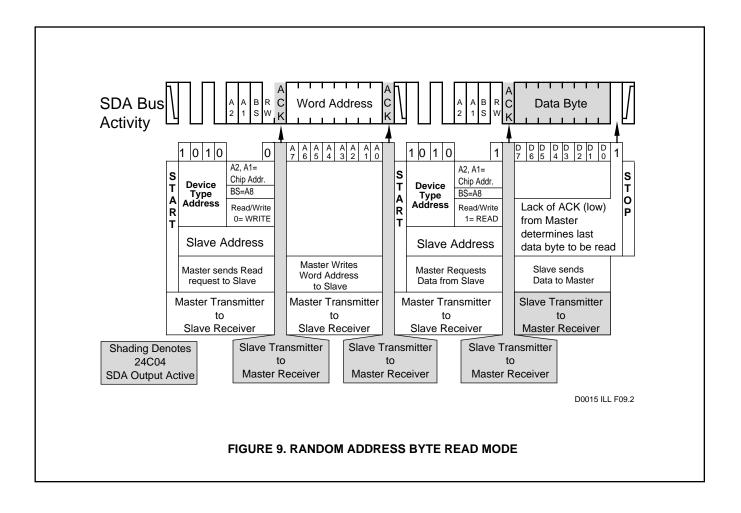

## **Random Address Byte Read**

Random address read operations allow the master to access any memory location in a random fashion. This operation involves a two-step process. First, the master issues a write command which includes the start condition and the slave address field (with the R/W bit set to WRITE) followed by the address of the word it is to read. This procedure sets the internal address counter of the XL24C04 to the desired address. After the word address acknowledge is received by the master, the master immediately reissues a start condition followed by another slave address field with the R/W bit set to READ. The XL24C04 will respond with an acknowledge and then transmit the 8-data bits stored at the addressed location. At this point, the master does not acknowledge the transmission but does generate the stop condition. The XL24C04 discontinues data transmission and reverts to its standby power mode. See Figure 9 for the address, acknowledge and data transfer sequence.

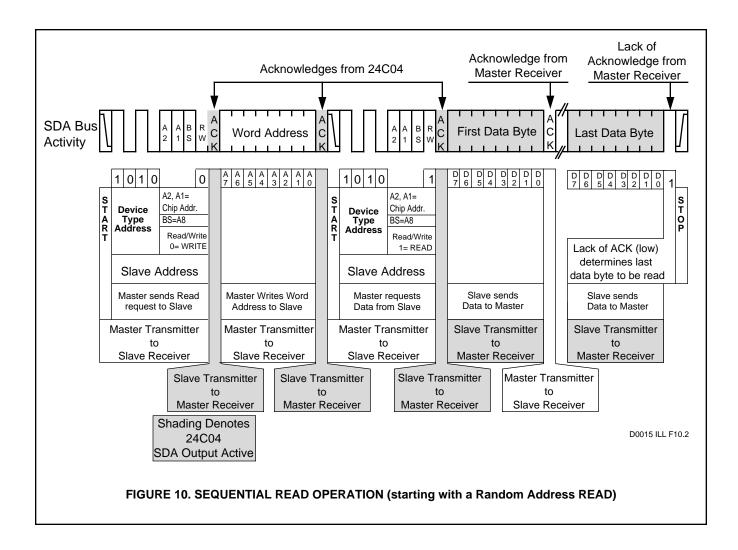

# Sequential READ

Sequential READs can be initiated as either a current address READ or random access READ. The first word is transmitted as with the other byte read modes (current address byte READ or random address byte READ); however, the master now responds with an ACKnowledge, indicating that it requires additional data from the XL24C04. The XL24C04 continues to output data for each ACKnowledge received. The master terminates the sequential READ operation by not responding with an ACKnowledge, and issues a STOP conditions. During a sequential read operation, the internal address counter is automatically incremented with each acknowledge signal. For read operations, all address bits are incremented, allowing the entire array to be read using a single read command. When the counter reaches the top of the array, it will "roll over" to the bottom of the array and continue to transmit data for each acknowledge bit it receives. See Figure 10 for the address, acknowledge and data transfer sequence.

# **ABSOLUTE MAXIMUM RATINGS**

| Temperature Under Bias:                      |           |

|----------------------------------------------|-----------|

| Storage Temperature                          |           |

| Soldering Temperature (less than 10 seconds) | 300°C     |

| Supply Voltage                               | 0 to 6.5V |

| Voltage on Any Pin                           |           |

| ESD Voltage (JEDEC method)                   |           |

| Output Current                               |           |

|                                              |           |

NOTE: These are STRESS ratings only. Appropriate conditions for operating these devices are given elsewhere in this specification. Stresses beyond those listed here may permanently damage the part. Prolonged exposure to maximum ratings may affect device reliability.

# DC ELECTRICAL CHARACTERISTICS

$T_A = -40^{\circ}C$  to  $85^{\circ}C$ ,  $V_{CC} = 2.7V$  to 5.5V

| Symbol          | Parameter              | Conditions                                                                                                            |              | Min     | Max     | Units |

|-----------------|------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------|---------|---------|-------|

| laa             | Supply Current (CMOS)  | SCL = CMOS Levels @ 100KHz $V_{CC} = 5V \pm 10\%$ SDA = OpenAll other inputs = GND or $V_{CC}$ $V_{CC} = 3V \pm 10\%$ |              | 3       | mA      |       |

| ICC             | Supply Current (CMOS)  |                                                                                                                       | Vcc = 3V±10% |         | 1       | mA    |

| I <sub>SB</sub> | Standby Current (CMOS) | SCL = SDA = V <sub>CC</sub><br>All other inputs = GND                                                                 |              |         | 5       | μΑ    |

| ILI             | Input Leakage          | V <sub>IN</sub> = 0 To V <sub>CC</sub>                                                                                |              |         | 10      | μA    |

| ILO             | Output Leakage         | V <sub>OUT</sub> = 0 To V <sub>CC</sub>                                                                               |              |         | 10      | μA    |

| VIL             | Input Low Voltage      | A0-A2, SCL, SDA                                                                                                       |              |         | 0.3xVcc | V     |

| VIH             | Input High Voltage     | A0-A2, SCL, SDA                                                                                                       |              | 0.7xVcc |         | V     |

| VOL             | Output Low Voltage     | I <sub>OL</sub> = 3mA                                                                                                 |              |         | 0.4     | V     |

D0015 PGM T01.1

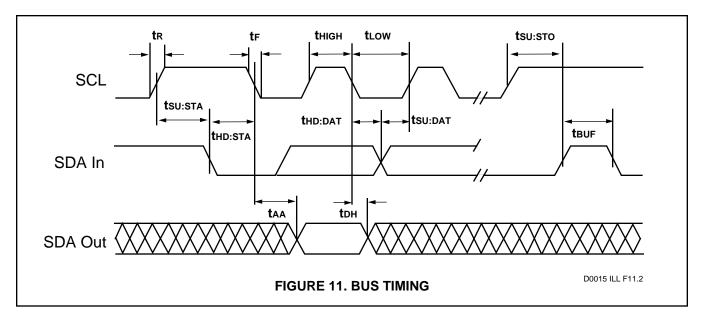

## AC ELECTRICAL CHARACTERISTICS

$T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 2.7V$  to 5.5V

| Symbol          | Parameter                  | Conditions                      | Min | Max  | Units |

|-----------------|----------------------------|---------------------------------|-----|------|-------|

| fscl            | SCL Clock Frequency        |                                 | 0   | 100  | KHz   |

| tLOW            | Clock Low Period           |                                 | 4.7 |      | μs    |

| thigh           | Clock High Period          |                                 | 4.0 |      | μs    |

| tBUF            | Bus Free Time              | Before New Transmission         | 4.7 |      | μs    |

| tsu:sta         | Start Condition Setup Time |                                 | 4.7 |      | μs    |

| thd:STA         | Start Condition Hold Time  |                                 | 4.0 |      | μs    |

| tsu:sto         | Stop Condition Setup Time  |                                 | 4.7 |      | μs    |

| t <sub>AA</sub> | Clock to Output            | SCL Low to SDA Data Out Valid   | 0.3 | 3.5  | μs    |

| tDH             | Data Out Hold Time         | SCL Low to SDA Data Out Change  | 0.3 |      | μs    |

| tR              | SCL and SDA Rise Time      |                                 |     | 1000 | ns    |

| tF              | SCL and SDA Fall Time      |                                 |     | 300  | ns    |

| tsu:dat         | Data In Setup Time         |                                 | 250 |      | ns    |

| thd:dat         | Data In Hold Time          |                                 | 0   |      | ns    |

| TI              | Noise Spike Width          | Time Constant @ SCL, SDA Inputs |     | 100  | ns    |

| two             | VCC = $5V\pm10\%$          | VCC = 5V±10%                    |     | 10   | ms    |

| twR             | Write Cycle Time           | VCC= 3V±10%                     |     | 25   | ms    |

# CAPACITANCE

TA = 25°C, f = 100KHz

| Symbol | Parameter          | Мах | Units |

|--------|--------------------|-----|-------|

| CIN    | Input Capacitance  | 5   | pF    |

| Соит   | Output Capacitance | 8   | pF    |

D0015 PGM T03.1

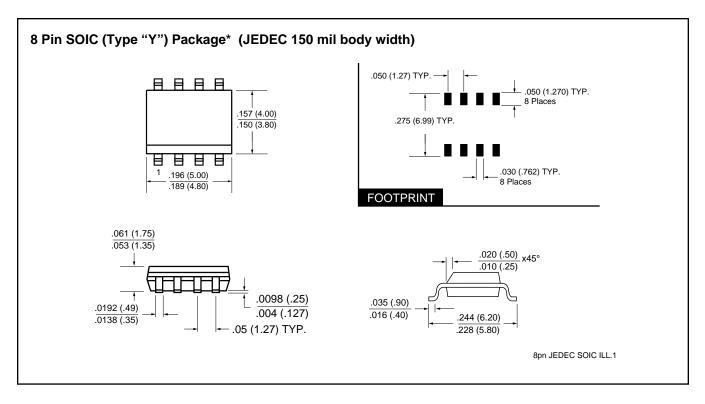

# PACKAGE DIAGRAMS

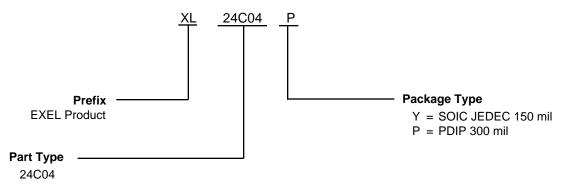

# ORDERING INFORMATION

| Prefix | Part<br>Number | Package<br>Type |

|--------|----------------|-----------------|

| XL     | 24C04          | Y, P            |

D0015 PGM T04.1

Part Numbers:

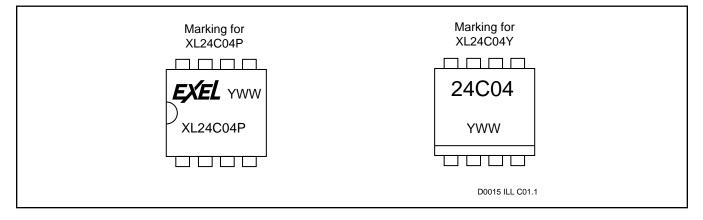

# MARKING INFORMATION

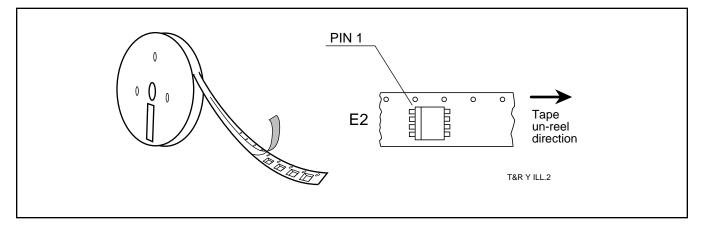

### TAPE AND REEL (EMBOSSED) INFORMATION

Surface mount devices, which are normally shipped in antistatic plastic tubes, are also available mounted on embossed tape for customers using automatic placement systems. The following diagram provides general information regarding the direction of the IC's. Tape "E2" shall be designated with PIN 1 at the trail direction.

# NOTICE

EXEL Microelectronics. Inc. reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXEL Microelectronics. Inc. assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained herein reflect representative operating parameters, and may vary depending upon a user's specific application. While the information in this publication has been carefully checked, EXEL Microelectronics. Inc. shall not be liable for any damages arising as a result of any error or omission.

EXEL Microelectronics. Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXEL Microelectronics. Inc. receives written assurances, to its satisfaction, that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; and (c) potential liability of EXEL Microelectronics. Inc. is adequately protected under the circumstances.

© Copyright 1996 EXEL Microelectronics. Inc.

I<sup>2</sup>C<sup>™</sup> is a trademark of Philips Corporation. Purchase of I<sup>2</sup>C components of Rohm Co. Ltd., or one of its sublicensed Associated Companies (EXEL Microelectronics, Inc.) conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.