# 3.3V, 2.7Gbps DUAL 2X2 CROSSPOINT SWITCH

SuperLite™ SY55859L FINAL

#### **FEATURES**

- Pin-for-pin, plug-in compatible to the MAX3840

- Supply voltage operation: +3.3V ±10%

- **■** Low jitter:

- · 2ps rms random jitter

- · 5ps pk-pk deterministic jitter

- Power saving output disable feature

- 15ps channel-to-channel skew

- Fast CML outputs: <100ps t<sub>r</sub>/t<sub>f</sub>

- Available in a small (5mm x 5mm) 32-pin EPAD-MLF package

#### **APPLICATIONS**

- SONET/SDH optical transport

- **■** High-speed backplane redundancy

- Add-drop multiplexers

#### **CROSS REFERENCE TABLE**

| Micrel Semiconductor | Maxim      |

|----------------------|------------|

| SY55859LMI           | MAX3840EGJ |

SuperLite™

#### **DESCRIPTION**

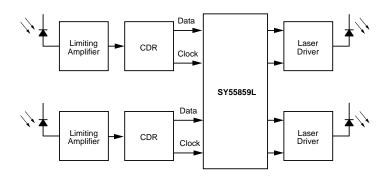

The SY55859L is a dual CML 2x2 crosspoint switch optimized for high-speed data and/or clock applications (up to 2.7Gbps or 2.7GHz) where low jitter and skew are critical. This device is pin-for-pin, plug-in compatible to the MAX3840. Each 2x2 of the SY55859L routes any input to any output, and thus can distribute or multiplex a clock or data stream. The I/O architecture is fully differential and CML compatible. Both inputs and outputs are optimized for  $50\Omega$  transmission lines. The inputs (DA 0-1 and DB 0-1) are internally terminated with  $50\Omega$ , thus eliminating external termination, and the outputs (QA0-1 and QB0-1) include  $50\Omega$  source termination. Furthermore, a power-saving output enable feature is provided which powers-down unused outputs.

The SY5859L operates from a  $+3.3V \pm 10\%$  supply, and is guaranteed over the industrial ( $-40^{\circ}$ C to  $+85^{\circ}$ C) temperature range. It is available in a 32-pin (5mm x 5mm) MLF package.

For applications that require either lower voltage operation or a more flexible input interface (for applications such as AC–coupled LVPECL inputs), consider the SY55858U.

#### TYPICAL APPLICATIONS CIRCUIT

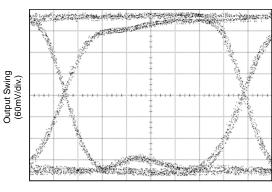

#### TYPICAL PERFORMANCE

TIME (50ps/div.)

2.7Gbps, 2<sup>23</sup> - 1 PRBS

SuperLite is a trademarks of Micrel, Inc. *Micro*LeadFrame and MLF are trademarks of Amkor Technology, Inc.

Rev.: B Amendment: /0 Issue Date: March 2003

### **PACKAGE/ORDERING INFORMATION**

### **Ordering Information**

| Part Number   | Package<br>Type | Operating<br>Range | Package<br>Marking |

|---------------|-----------------|--------------------|--------------------|

| SY55859LMI    | H32-1           | Industrial         | SY55859LMI         |

| SY55859LMITR* | H32-1           | Industrial         | SY55859LMI         |

<sup>\*</sup>Tape and Reel

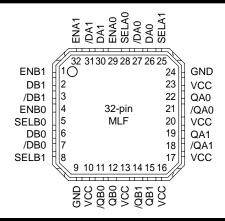

#### PIN DESCRIPTION

| Pin Number             | Pin Name    | Pin Function                                                                                                        |  |  |  |

|------------------------|-------------|---------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                      | ENB1        | TTL Input. Channel B1 Output Enable. Setting this pin inactive low powers down QB1 and /QB1. Do not leave floating. |  |  |  |

| 2                      | DB1         | CML Input. Channel B1 true input.                                                                                   |  |  |  |

| 3                      | /DB1        | CML Input. Channel B1 complement input.                                                                             |  |  |  |

| 4                      | ENB0        | TTL Input. Channel B0 Output Enable. Setting this pin inactive low powers down QB0 and /QB. Do not leave floating.  |  |  |  |

| 5                      | SELB0       | TTL Input. Channel B0 output select. Please refer to Table 2. Do not leave floating.                                |  |  |  |

| 6                      | DB0         | CML Input. Channel B0 true input.                                                                                   |  |  |  |

| 7                      | /DB0        | CML Input. Channel B0 complement input.                                                                             |  |  |  |

| 8                      | SELB1       | TTL Input. Channel B1 output select. Please refer to Table 2. Do not leave floating.                                |  |  |  |

| 9, 24                  | GND         | Supply ground. Most negative supply voltage.                                                                        |  |  |  |

| 10, 13, 16, 17, 20, 23 | VCC         | Positive supply.                                                                                                    |  |  |  |

| 11                     | /QB0        | CML Output. Channel B0 complement output.                                                                           |  |  |  |

| 12                     | QB0         | CML Output. Channel B0 true output.                                                                                 |  |  |  |

| 14                     | /QB1        | CML Output. Channel B1 complement output.                                                                           |  |  |  |

| 15                     | QB1         | CML Output. Channel B1 true output.                                                                                 |  |  |  |

| 18                     | /QA1        | CML Output. Channel A1 complement output.                                                                           |  |  |  |

| 19                     | QA1         | CML Output. Channel A1 true output.                                                                                 |  |  |  |

| 21                     | /QA0        | CML Output. Channel A0 complement output.                                                                           |  |  |  |

| 22                     | QA0         | CML Output. Channel A0 true output.                                                                                 |  |  |  |

| 25                     | SELA1       | TTL Input. Channel A1 output select. Please refer to Table 1. Do not leave floating.                                |  |  |  |

| 26                     | DA0         | CML Input. Channel A0 true input.                                                                                   |  |  |  |

| 27                     | /DA0        | CML Input. Channel A0 complement input.                                                                             |  |  |  |

| 28                     | SELA0       | TTL Input. Channel A0 output select. Please refer to Table 1. Do not leave floating.                                |  |  |  |

| 29                     | ENA0        | TTL Input. Channel A0 output enable. Setting this pin inactive low powers down QA0 and /QA0. Do not leave floating. |  |  |  |

| 30                     | DA1         | CML Input. Channel A1 true input.                                                                                   |  |  |  |

| 31                     | /DA1        | CML Input. Channel A1 complement input.                                                                             |  |  |  |

| 32                     | ENA1        | TTL Input. Channel A1 output enable. Setting this pin inactive low powers down QA1 and /QA1. Do not leave floating. |  |  |  |

| EP                     | Exposed Pad | Ground. This must be soldered to circuit board ground for proper electrical and thermal operation.                  |  |  |  |

## Absolute Maximum Ratings(Note 1)

####

## Operating Ratings(Note 2)

| Supply Voltage (V <sub>CC</sub> )      | +3.0V to +3.6V |

|----------------------------------------|----------------|

| Ambient Temperature (T <sub>A</sub> )  | 40°C to +85°C  |

| Junction Temperature (T <sub>J</sub> ) | 160°C          |

| Package Thermal Resistance             |                |

| MLF (θ <sub>JA</sub> )<br>still-air    |                |

| still-air                              | 28°C/W         |

| 500lfpm                                | 20°C/W         |

| MLF $(\theta_{JC})$                    | 4°C/W          |

- Note 1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods may affect device reliability.

- Note 2. The data sheet limits are not guaranteed if the device is operated beyond the operating ratings.

#### DC ELECTRICAL CHARACTERISTICS(1)

$T_A = -40^{\circ}C \text{ to } +85^{\circ}C$

| Symbol          | Parameter            | Condition                                            | Min | Тур | Max | Units |

|-----------------|----------------------|------------------------------------------------------|-----|-----|-----|-------|

| V <sub>CC</sub> | Power Supply Voltage |                                                      | 3.0 | 3.3 | 3.6 | V     |

| I <sub>cc</sub> | Power Supply Current | No Load, Over Supply Voltage;<br>All Outputs Enabled |     | 160 | 190 | mA    |

Note 1. Specification for packaged product only.

#### CML DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = 3.0V \text{ to } 3.6V; \text{ GND} = 0V; T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}^{\text{(Note 2)}}$

| Symbol            | Parameter Condition                  |                                         | Min                  | Тур                  | Max                  | Units |

|-------------------|--------------------------------------|-----------------------------------------|----------------------|----------------------|----------------------|-------|

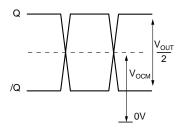

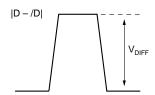

| V <sub>OUT</sub>  | CML Differential Output Swing        | $R_L = 50\Omega$ to $V_{CC}$ , Figure 3 |                      | 800                  | 1000                 | mVp-p |

| R <sub>OUT</sub>  | Differential Output Impedance        | Figure 2                                |                      | 100                  | 115                  | Ω     |

| V <sub>OCM</sub>  | CML Output Common Mode Voltage       | $R_L = 50\Omega$ to $V_{CC}$ , Figure 3 |                      | V <sub>CC</sub> -0.2 |                      | V     |

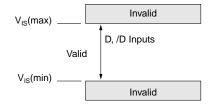

| V <sub>IS</sub>   | CML Input Voltage Range              | Figure 4                                | V <sub>CC</sub> -0.8 |                      | V <sub>CC</sub> +0.4 | V     |

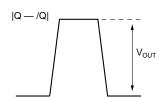

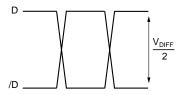

| V <sub>DIFF</sub> | CML Differential Input Voltage Swing | Figure 5                                | 300                  |                      | 1600                 | mVp-p |

|                   | CML Single-ended Input Impedance     | Figure 1                                | 42.5                 | 50                   | 57.5                 | Ω     |

- Note 1. Specification for packaged product only.

- Note 2. The device is guaranteed to meet the DC specifications, shown in the table above, after thermal equilibrium has been established. The device is tested in a socket such that transverse airflow of ≥500lfpm is maintained.

#### TTL CONTROL ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = 3.0V \text{ to } 3.6V; \text{ GND} = 0V; T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}^{\text{(Note 2)}}$

| Symbol          | Parameter              | Condition | Min | Тур | Max | Units |

|-----------------|------------------------|-----------|-----|-----|-----|-------|

| V <sub>IH</sub> | TTL Input HIGH Voltage |           | 2.0 |     |     | V     |

| $V_{\rm IL}$    | TTL Input LOW Voltage  |           |     |     | 0.8 | V     |

| I <sub>IH</sub> | TTL Input HIGH Current |           | -10 |     | +10 | μΑ    |

| I <sub>IL</sub> | TTL Input LOW Current  |           | -10 |     | +10 | μΑ    |

- Note 1. Specification for packaged product only.

- Note 2. The device is guaranteed to meet the DC specifications, shown in the table above, after thermal equilibrium has been established. The device is tested in a socket such that transverse airflow of ≥500lfpm is maintained.

### AC ELECTRICAL CHARACTERISTICS(1)

$V_{CC}$  = 3.0V to 3.6V; GND = 0V;  $T_A$  = -40°C to +85°C<sup>(Note 2)</sup>

| Symbol                         | Parameter                              | Condition                                     | Min | Тур | Max | Units     |

|--------------------------------|----------------------------------------|-----------------------------------------------|-----|-----|-----|-----------|

| $f_{MAX}$                      | Maximum NRZ Data Rate                  |                                               |     | 2.7 |     | Gbps      |

| $f_{MAX}$                      | Maximum Clock Rate                     |                                               |     | 2.7 |     | GHz       |

| t <sub>PD</sub>                | Propagation Delay from Input-to-Output |                                               |     | 275 |     | ps        |

| $R_J$                          | Random Jitter                          | Note 3                                        |     | 2   |     | ps(rms)   |

| $\overline{D_J}$               | Deterministic Jitter                   | Note 4                                        |     | 5   | 20  | ps(pk-pk) |

| t <sub>SKDIFF</sub>            | CML Output Differential Skew           | Any Differential Pair – Duty Cycle Distortion |     | 7   | 25  | ps        |

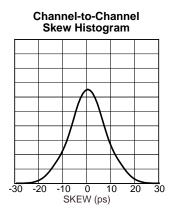

| t <sub>SKEW</sub>              | CML Output Channel-to-Channel          | Note 5, Any Two Outputs                       |     | 15  | 40  | ps        |

| t <sub>r</sub> ,t <sub>f</sub> | CML Output Rise/Fall Times             | (20% to 80%)                                  |     | 80  | 135 | ps        |

- Note 1. Specification for packaged product only.

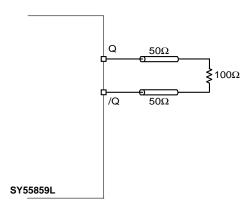

- Note 2. AC characteristics are guaranteed by design and characterization. Tested using environment of Figure 6, 50Ω equivalent load.

- **Note 3.** Measured with 100mVp-p noise ( $f \le 2MHz$ ) on the power supply.

- Note 4. Deterministic jitter (D<sub>.</sub>) is the arithmetic sum of pattern-dependent jitter and pulse width distortion.

- Note 5. This represents the skew on a QA and QB output with their inputs receiving the same signal.

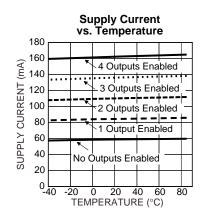

#### TYPICAL OPERATING CHARACTERISTICS

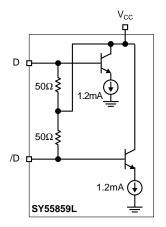

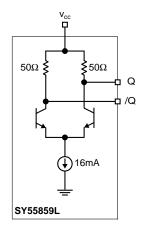

Figure 1. Input Structure

Figure 2. Output Structure

Figure 3a. Output Levels

Figure 3b. Output Levels

Figure 4. Input Range

Figure 5a. Input Levels

Figure 5b. Input Levels

Figure 6. Output Interface

### TYPICAL OPERATING CHARACTERISTICS

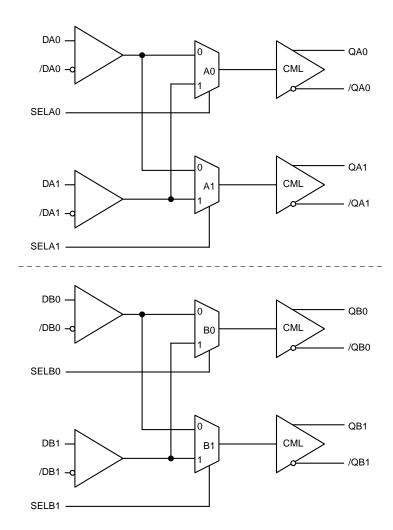

#### **FUNCTIONAL DESCRIPTION**

SY55859L is a dual cross point with excellent pin-to-pin and part-to-part skew matching. As shown in table 1, based on the logic value at TTL input SELA0, output QA0 replicates either input DA0 or DA1. TTL input SELA1 selects whether output QA1 replicates input DA0 or DA1. As shown in table 2, TTL inputs SELB0 and SELB1 perform similarly for outputs QB0 and QB1 respectively, choosing between inputs DB0 or DB1.

If the two control inputs are tied together, SY55859L behaves as a redundant distribution device. Depending on the state of the combined control inputs, QA0 and QA1 will both replicate either DA0 or DA1. If the two control inputs

are made the logical complement of each other, the SY55859L functions as a crosspoint, either sending DA0 to QA0 and DA1 to QA1, or sending DA0 to QA1 and DA1 to QA0. The same applies to channel B.

SY85859L's CML outputs are source terminated to  $50\Omega$  individually,  $100\Omega$  differentially. The CML inputs are parallel terminated, also to  $50\Omega$ . This improves signal integrity. With all terminations on chip, high-speed interfacing is greatly simplified, eliminating the need for external termination passive components. Figures 1 and 2 show the input and output structures.

| SELA0 | SELA1 | QA0      | QA1      | Function               |

|-------|-------|----------|----------|------------------------|

| 0     | 0     | DA0      | DA0      | Fanout Buffer          |

| 0     | 1     | DA0      | DA1      | Dual Buffer            |

| 1     | 0     | DA1      | DA0      | Dual Buffer            |

| 1     | 1     | DA1      | DA1      | Fanout Buffer          |

| CTL   | CTL   | Same     | Same     | Redundant Distribution |

| CTL   | /CTL  | Opposite | Opposite | Crosspoint             |

Table 1. Input to Output Connectivity, Crosspoint A

| SELB0 | SELB1 | QB0      | QB1      | Function               |

|-------|-------|----------|----------|------------------------|

| 0     | 0     | DA0      | DA0      | Fanout Buffer          |

| 0     | 1     | DA0      | DA1      | Dual Buffer            |

| 1     | 0     | DA1      | DA0      | Dual Buffer            |

| 1     | 1     | DA1      | DA1      | Fanout Buffer          |

| CTL   | CTL   | Same     | Same     | Redundant Distribution |

| CTL   | /CTL  | Opposite | Opposite | Crosspoint             |

Table 2. Input to Output Connectivity, Crosspoint B

### **FUNCTIONAL BLOCK DIAGRAM**

#### **APPLICATIONS INFORMATION**

The eight TTL compliant inputs to SY55859L are ENA0, ENA1, ENB0 ENB1, SELA0, SELA1, SELB0 and SELB1. These high impedance inputs do not default to a stable logic state when left unconnected. Therefore, these TTL compliant inputs cannot be left floating. Connect these inputs to a valid control signal, or hardwire to  $V_{CC}$  or GND.

The four enable TTL inputs, when driven low, disable the corresponding output stage. This reduces power consumption. Disabled output stages do not go into a high impedance state. Rather, each pin of a disabled output stage pair goes high through its respective  $50\Omega$  source termination.

The delay from a logic transition on an enable input to the corresponding effect on the CML output is not defined in the tables of this data sheet. This delay is 3ns typical, and 10ns maximum. Please note that, for cases where highly capacitive lines are being driven, the RC effects of the line may make this delay longer.

The delay from a logic transition on a select input to the corresponding CML output is also not defined in the tables. It is 300psec typical, 500psec maximum.

For best performance, use good high frequency layout techniques, filter  $V_{CC}$  supplies, and keep ground connections short. Use multiple vias where possible. Also, use controlled impedance transmission lines to interface with the SY55859L data inputs and outputs.

#### RELATED PRODUCT AND SUPPORT DOCUMENTATION

| Part Number | Function                | Data Sheet Link                                     |

|-------------|-------------------------|-----------------------------------------------------|

| SY55854U    | 2x2 CML Crosspoint      | www.micrel.com/product-info/products/sy55854u.shtml |

| SY55858U    | Dual 2x2 CML Crosspoint | www.micrel.com/product-info/products/sy55858u.shtml |

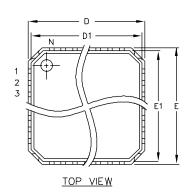

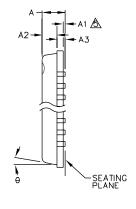

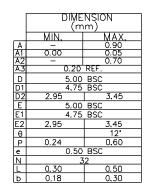

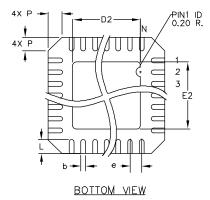

#### 32 LEAD *Micro* LEADFRAME™ (MLF-32)

- NOTE:

1. ALL DIMENSIONS ARE IN MILLIMETERS.

2. N IS THE NUMBER OF TERMINALS.

THE NUMBER OF TERMINALS PER SIDE IS N/4.

3. THE PIN#I IDENTIFIRE MUST BE EXISTED ON THE TOP SURFACE OF PACKAGE BY USING IDENTIFICATION MARK OR OTHER FEATURE OF PACKAGE BODY.

4. PACKAGE WARPAGE MAX 005mm.

- APPLIED FOR EXPOSED PAD AND TERMINALS.

Rev. 01

#### MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2003 Micrel, Incorporated.