## DUAL CML/PECL/LVPECL-to-LVDS TRANSLATOR

SuperLite™ SY55855V FINAL

### **FEATURES**

- Guaranteed f<sub>MAX</sub> >750MHz over temperature

- 1.5Gbps throughput capability

- 3.0V to 5.7V power supply

- Guaranteed <700ps propagation delay over temperature

- Guaranteed <50ps within-device skew over temperature

- **LVDS compatible outputs**

- Fully differential I/O architecture

- Wide operating temperature range: -40°C to +85°C

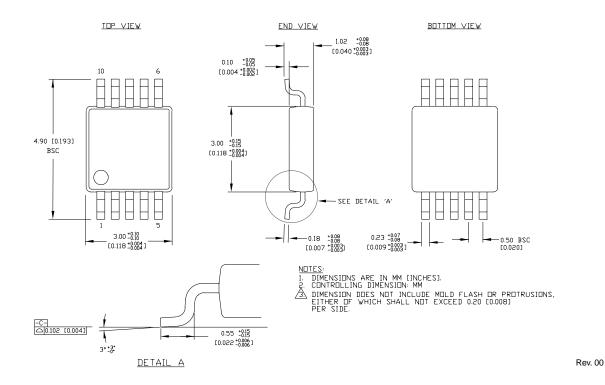

- Available in a tiny 10-pin MSOP package

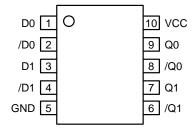

#### PIN CONFIGURATION

10-Pin MSOP

SuperLite™

#### DESCRIPTION

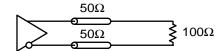

The SY55855V is a fully differential, CML/PECL/LVPECL-to-LVDS translator. It achieves LVDS signaling up to 1.5Gbps, depending on the distance and the characteristics of the media and noise coupling sources. LVDS is intended to drive  $50\Omega$  impedance transmission line media such as PCB traces, backplanes, or cables.

SY55855V inputs can be terminated with a single resistor between the true and the complement pins of a given input.

The SY55855V is a member of Micrel's new SuperLite<sup>™</sup> family of high-speed logic devices. This family features very small packaging, high signal integrity, and operation at many different supply voltages.

#### **APPLICATIONS**

- **■** High-speed logic

- Data communications systems

- Wireless communications systems

- **■** Telecom systems

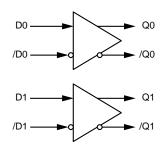

### **FUNCTIONAL BLOCK DIAGRAM**

#### **PIN NAMES**

| Pin             | Function                   |

|-----------------|----------------------------|

| D0, /D0         | CML/PECL/LVPECL Input Data |

| D1, /D1         | CML/PECL/LVPECL Input Data |

| Q0, /Q0         | LVDS Output Data           |

| Q1, /Q1         | LVDS Output Data           |

| GND             | Ground                     |

| V <sub>CC</sub> | V <sub>CC</sub>            |

SuperLite is a trademark of Micrel, Inc.

#### **PIN DESCRIPTIONS**

#### D0, /D0 - CML/PECL/LVPECL Input (Differential)

This is one of the inputs. It is converted to LVDS onto the Q0 and /Q0 outputs.

#### D1, /D1 – CML/PECL/LVPECL Input (Differential)

This is the other input. It is converted to LVDS onto the Q1 and /Q1 outputs.

#### Q0, /Q0 - LVDS Output (Differential)

This is one LVDS output. It buffers the CML input that appears at D0, /D0.

#### Q1, /Q1 - LVDS Output (Differential)

This is the other LVDS output. It buffers the CML input that appears at D1, /D1.

#### **FUNCTIONAL DESCRIPTION**

#### **Establishing Static Logic Inputs**

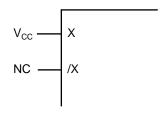

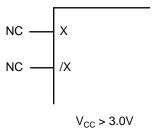

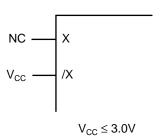

The true pin of an input pair is internally biased to ground through a  $75k\Omega$  resistor. The complement pin of an input pair is internally biased halfway between  $V_{CC}$  and ground by a voltage divider consisting of two  $75k\Omega$  resistors. In this way, unconnected inputs appear as logic zeros. To keep an input at static logic zero at  $V_{CC}>3.0V,$  leave both inputs

unconnected. For  $V_{CC} \leq 3.0V$ , connect the complement input to  $V_{CC}$  and leave the true input unconnected. To make an input static logic one, connect the true input to  $V_{CC}$ , leave the complement input unconnected. These are the only two safe ways to cause inputs to be at a static value. In particular, no input pin should be directly connected to ground. All NC (no connect) pins should be unconnected.

Figure 1. Hard Wiring a Logic "1" (1)

Note 1. X is either D0 or D1 input. /X is either /D0 or /D1 input.

Figure 2. Hard Wiring a Logic "0" (1)

Note 1. X is either D0 or D1 input. /X is either /D0 or /D1 input.

### **TRUTH TABLE**

| D0 | D1 | Q0 | /Q0 | Q1 | /Q1 |

|----|----|----|-----|----|-----|

| 0  | 0  | 0  | 1   | 0  | 1   |

| 0  | 1  | 0  | 1   | 1  | 0   |

| 1  | 0  | 1  | 0   | 0  | 1   |

| 1  | 1  | 1  | 0   | 1  | 0   |

### LVDS OUTPUTS

LVDS stands for Low Voltage Differential Swing. LVDS specifies a small swing of 350mV typical, on a nominal 1.25V common mode above ground. The common mode voltage has tight limits to permit large variations in ground

between an LVDS driver and receiver. Also, change in common mode voltage, as a function of data input, is also kept tight, to keep EMI low.

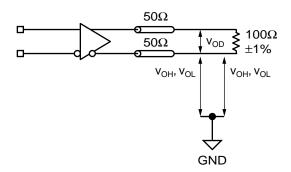

Figure 3. LVDS Differential Measurement

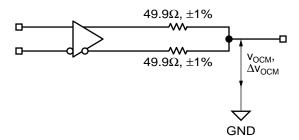

Figure 4. LVDS Common Mode Measurement

Figure 5. LVDS Output Termination

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol             | Rating                      | Value                        | Unit |

|--------------------|-----------------------------|------------------------------|------|

| V <sub>CC</sub>    | Power Supply Voltage        | -0.5 to +6.0                 | V    |

| V <sub>IN</sub>    | Input Voltage               | -0.5 to V <sub>CC</sub> +0.5 | V    |

| I <sub>OUT</sub>   | LVDS Output Current         | ±10%                         | mA   |

| T <sub>A</sub>     | Operating Temperature Range | -40 to +85                   | °C   |

| T <sub>store</sub> | Storage Temperature Range   | -65 to +150                  | °C   |

**Note 1.** Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC}$  = 3.0V to 5.7V; GND = 0V;  $T_A$  = -40°C to +85°C<sup>(2)</sup>

|                 |                                                               | T <sub>A</sub> = -40°C |          | T <sub>A</sub> = +25°C |         |          | T <sub>A</sub> = +85°C |          |      |

|-----------------|---------------------------------------------------------------|------------------------|----------|------------------------|---------|----------|------------------------|----------|------|

| Symbol          | Parameter                                                     | Min.                   | Max.     | Min.                   | Тур.    | Max.     | Min.                   | Max.     | Unit |

| V <sub>CC</sub> | Power Supply Voltage                                          | 3.0                    | 5.7      | 3.0                    |         | 5.7      | 3.0                    | 5.7      | V    |

| I <sub>CC</sub> | Power Supply Current $3.6V < V_{CC} < 5.7V$ $V_{CC} \le 3.6V$ | _<br>_                 | 80<br>50 | _<br>_                 | _<br>30 | 80<br>50 | —<br>—                 | 80<br>50 | mA   |

Note 1. Specification for packaged product only.

Note 2. Equilibrium temperature.

## CML DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = 3.0V \text{ to } 5.7V; \text{ GND} = 0V; T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}^{(2)}$

| Symbol          | Parameter                  | Min. | Тур. | Max.                  | Unit | Condition |

|-----------------|----------------------------|------|------|-----------------------|------|-----------|

| V <sub>ID</sub> | Differential Input Voltage | 100  |      |                       | mV   |           |

| V <sub>IH</sub> | Input HIGH Voltage         | 1.6  |      | V <sub>CC</sub>       | V    |           |

| $V_{IL}$        | Input LOW Voltage          | 1.5  |      | V <sub>CC</sub> – 0.1 | V    |           |

Note 1. Specification for packaged product only.

Note 2. Equilibrium temperature.

## LVDS DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = 3.0V \text{ to } 5.7V; \text{ GND} = 0V; T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}^{(2)}$

| Symbol           | Parameter                                       | Min.        | Тур. | Max.  | Unit | Condition                |

|------------------|-------------------------------------------------|-------------|------|-------|------|--------------------------|

| V <sub>OD</sub>  | Differential Output Voltage <sup>(4)</sup>      | 250         |      | 450   | mV   | 100Ω Termination         |

| V <sub>OCM</sub> | Output Common Mode Voltage <sup>(3)</sup>       | 1.125       |      | 1.375 | V    |                          |

| $\Delta V_{OCM}$ | Change in Common Mode<br>Voltage <sup>(3)</sup> | <b>–</b> 50 | _    | +50   | mV   |                          |

| V <sub>OH</sub>  | Output HIGH Voltage <sup>(4), (5)</sup>         |             |      | 1.474 | V    | I <sub>OH</sub> = -4.0mA |

| V <sub>OL</sub>  | Output LOW Voltage <sup>(4), (5)</sup>          | 0.925       | _    | _     | V    | I <sub>OL</sub> = 4.0mA  |

Note 1. Specification for packaged product only.

Note 2. Equilibrium temperature.

Note 3. Measured as per Figure 4.

Note 4. Measured as per Figure 3.

Note 5. Do not short output to GND.

# AC ELECTRICAL CHARACTERISTICS<sup>(1)</sup> $V_{CC} = 3.0V \text{ to } 5.7V; \text{ GND} = 0V; T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}^{(2)}$

| Symbol                               | Parameter                                                      | Min.   | Тур. | Max.      | Unit | Condition |

|--------------------------------------|----------------------------------------------------------------|--------|------|-----------|------|-----------|

| f <sub>MAX</sub>                     | Maximum Operating Frequency                                    | 750    | _    | _         | MHz  |           |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay<br>D0 to Q0, D1 to Q1                        | 300    | _    | 700       | ps   |           |

| t <sub>SKEW</sub>                    | Within-Device Skew <sup>(3)</sup><br>Part-to-Part Skew (Diff.) | _<br>_ | _    | 50<br>250 | ps   |           |

| t <sub>r</sub><br>t <sub>f</sub>     | LVDS Output Differential<br>Rise/Fall Times (20% to 80%)       | 100    | _    | 300       | ps   |           |

- Note 1. Specification for packaged product only.

- Note 2. Equilibrium temperature.

- Note 3. Worst case difference between Q0 and Q1 from either D0 or D1, when both outputs have the same transition.

## PRODUCT ORDERING CODE

| Ordering   | Package | Operating  | Package |

|------------|---------|------------|---------|

| Code       | Type    | Range      | Marking |

| SY55855VKI | K10-1   | Industrial | 855V    |

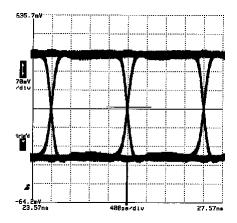

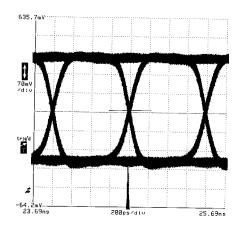

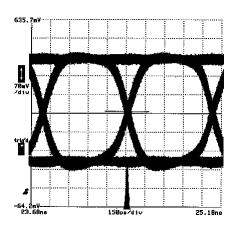

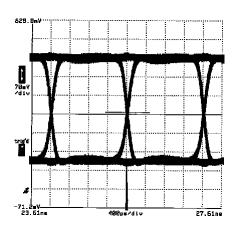

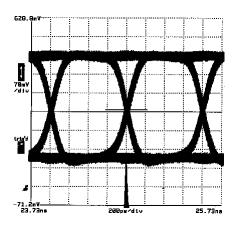

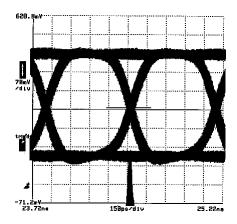

## EYE DIAGRAMS(1)

622Mbps 3.3V LVPECL-to-LVDS

1.25Gbps 3.3V LVPECL-to-LVDS

1.5Gbps 3.3V LVPECL-to-LVDS

622Mbps 3.3V CML-to-LVDS

1.25Gbps 3.3V CML-to-LVDS

1.5Gbps 3.3V CML-to-LVDS

**Note 1.** 2<sup>23</sup>–1 pattern.

## 10 LEAD MSOP (K10-1)

#### MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2003 Micrel, Incorporated