## D FLIP-FLOP

SuperLite™ SY55852U FINAL

# **FEATURES**

- 2.5GHz min. f<sub>MAX</sub>

- 2.3V to 5.7V power supply

- Single bit register memory

- Synchronizes 1 bit of data to a clock

- Optimized to work with SuperLite<sup>™</sup> family

- Fully differential

- Accepts CML, PECL, LVPECL input logic levels

- Source terminated CML outputs for fast edge rates

- Available in a tiny 10-pin MSOP

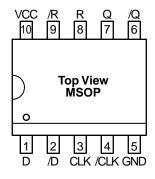

# **PIN CONFIGURATION**

SuperLite™

# **DESCRIPTION**

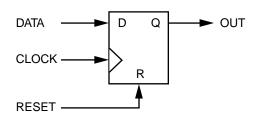

The SY55852U is a flip-flop used to synchronize data to a clock. Its differential output will reproduce and remember the value on its input at the rising edge of the clock. In addition, an asynchronous, level sensitive reset is provided. For a synchronous reset, the SY55851U AnyGate $^{\text{TM}}$  can be used.

SY55852U inputs can be terminated with a single resistor between the true and complement pins of a given input.

The SY55852U is a member of Micrel's SuperLite<sup>™</sup> family of high-speed CML logic. This family features very small packaging and 2.3V to 5.7V operation.

# **APPLICATIONS**

- High-speed logic

- OC-48 communication systems

## **FUNCTIONAL BLOCK DIAGRAM**

## **PIN NAMES**

| Pin             | Function                    |  |  |  |

|-----------------|-----------------------------|--|--|--|

| D, /D           | CML/PECL/LVPECL Data Input  |  |  |  |

| CLK, /CLK       | CML/PECL/LVPECL Clock Input |  |  |  |

| R, /R           | CML/PECL/LVPECL Reset Input |  |  |  |

| Q, /Q           | CML Data Output             |  |  |  |

| GND             | Ground                      |  |  |  |

| V <sub>CC</sub> | V <sub>CC</sub>             |  |  |  |

SuperLite is a trademark of Micrel, Inc.

Rev.: B Amendment: /0 Issue Date: March 2003

## **PIN DESCRIPTIONS**

#### D, /D - CML/PECL/LVPECL Input (Differential)

This is the single bit of data that gets clocked in and remembered.

#### CLK, /CLK - CML/PECL/LVPECL Input (Differential)

The rising edge of this signal is the clock signal that determines when the Boolean value at the data input gets stored.

#### R, /R - CML/PECL/LVPECL Input (Differential)

This is an asynchronous active high level reset, that forces the flip-flop into a known state, namely zero.

### Q, /Q - CML Output (Differential)

This is the output of the flip-flop.

## **FUNCTIONAL DESCRIPTION**

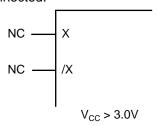

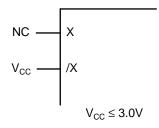

#### **Establishing Static Logic Inputs**

The true pin of an input pair is internally biased to ground through a  $75k\Omega$  resistor. The complement pin of an input pair is internally biased halfway between  $V_{CC}$  and ground by a voltage divider consisting of two  $75k\Omega$  resistors. To keep an input at static logic zero at  $V_{CC} > 3.0V$ , leave both

V<sub>CC</sub> — X NC — /X

Figure 1. Hard Wiring a Logic "1" (1)

Note 1. X is either D, CLK, R input. /X is either /D, /CLK, /R input.

inputs unconnected. For  $V_{CC} \leq 3.0 V_{,}$  connect the complement inputs to  $V_{CC}$  and leave the true inputs unconnected. To make an input static logic one, connect the true input to  $V_{CC},$  leave the complement input unconnected. These are the only safe ways to cause inputs to be at a static value. In particular, no input pin should be directly connected to ground. All NC (no connect) pins should be unconnected.

Figure 2. Hard Wiring a Logic "0" (1)

#### **TRUTH TABLE**

| D | CLK      | R | Q                                    | /Q                                     |

|---|----------|---|--------------------------------------|----------------------------------------|

| Х | Х        | 1 | 0                                    | 1                                      |

| Х | 0        | 0 | $Q_{N-1}$                            | /Q <sub>N-1</sub>                      |

| Х | 1        | 0 | Q <sub>N-1</sub><br>Q <sub>N-1</sub> | /Q <sub>N-1</sub><br>/Q <sub>N-1</sub> |

| 0 | <u>_</u> | 0 | 0                                    | 1                                      |

| 1 | <u>_</u> | 0 | 1                                    | 0                                      |

≶ 50Ω

≸100Ω

50Ω

100Ω

# ABSOLUTE MAXIMUM RATINGS(1)

| Symbol             | Rating                      | Value                                  | Unit |

|--------------------|-----------------------------|----------------------------------------|------|

| V <sub>CC</sub>    | Power Supply Voltage        | -0.5 to +6.0                           | V    |

| V <sub>IN</sub>    | Input Voltage               | –0.5 to V <sub>CC</sub> +0.5           | V    |

| V <sub>OUT</sub>   | CML Output Voltage          | $V_{\rm CC}$ –1.0 to $V_{\rm CC}$ +0.5 | V    |

| T <sub>A</sub>     | Operating Temperature Range | -40 to +85                             | °C   |

| T <sub>store</sub> | Storage Temperature Range   | -65 to +150                            | °C   |

Note 1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods may affect device reliability.

50Ω ≸

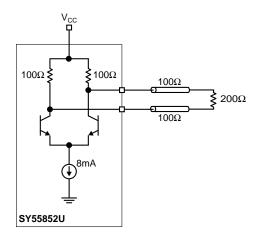

# **CML TERMINATION**

All inputs accept the output from any other member of this family. All outputs are source terminated  $100\Omega$  CML differential drivers as shown in Figures 3 and 4. SY55852U expects the inputs to be terminated, and that good high

speed design practices be adhered to. SY55852U inputs are designed to accept a termination resistor between the true and complement inputs of a differential pair. 0402 form factor chip resistors will fit with some trace fanout.

SY55852U

100Ω

$100\Omega$

50Ω

Figure 3a. Differentially Terminated (50 $\Omega$  Load CML Output)

Figure 3b. Individually Terminated  $(50\Omega \text{ Load CML Output})$

Figure 4.  $100\Omega$  Load CML Output

# DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC}$  = 2.3V to 5.7V; GND = 0V

|                 |                      | T <sub>A</sub> = -40°C |      | T <sub>A</sub> = 0°C |      | T <sub>A</sub> = +25°C |      | T <sub>A</sub> = +85°C |      |      |

|-----------------|----------------------|------------------------|------|----------------------|------|------------------------|------|------------------------|------|------|

| Symbol          | Parameter            | Min.                   | Max. | Min.                 | Max. | Min.                   | Max. | Min.                   | Max. | Unit |

| $V_{CC}$        | Power Supply Voltage | 2.3                    | 5.7  | 2.3                  | 5.7  | 2.3                    | 5.7  | 2.3                    | 5.7  | V    |

| I <sub>CC</sub> | Power Supply Current | _                      | 36   | _                    | 36   | _                      | 36   | _                      | 36   | mA   |

Note 1. Specification for packaged product only.

# CML DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = 2.3 \text{V to } 5.7 \text{V}; \text{ GND} = 0 \text{V}; T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}^{(2)}$

| Symbol             | Parameter                           | Min.                    | Тур.                    | Max.                    | Unit   | Condition                                                                |

|--------------------|-------------------------------------|-------------------------|-------------------------|-------------------------|--------|--------------------------------------------------------------------------|

| V <sub>ID</sub>    | Differential Input Voltage          | 100                     | _                       | _                       | mV     |                                                                          |

| V <sub>IH</sub>    | Input HIGH Voltage <sup>(6)</sup>   | 1.6                     | _                       | V <sub>CC</sub>         | V      |                                                                          |

| $V_{IL}$           | Input LOW Voltage <sup>(6)</sup>    | 1.5                     | _                       | V <sub>CC</sub> – 0.1   | V      |                                                                          |

| V <sub>OH</sub>    | Output HIGH Voltage                 | V <sub>CC</sub> - 0.020 | V <sub>CC</sub> – 0.010 | V <sub>cc</sub>         | V      | No Load                                                                  |

| V <sub>OL</sub>    | Output LOW Voltage                  | V <sub>CC</sub> – 0.97  | V <sub>CC</sub> – 0.825 | V <sub>CC</sub> - 0.660 | V      | No Load                                                                  |

| V <sub>os</sub>    | Output Voltage Swing <sup>(3)</sup> | 0.660                   | 0.800<br>0.400<br>0.200 | 0.950                   | \<br>\ | No Load $100\Omega$ Environment $^{(5)}$ $50\Omega$ Environment $^{(4)}$ |

| R <sub>DRIVE</sub> | Output Source Impedance             | 80                      | 100                     | 120                     | Ω      |                                                                          |

- **Note 1.** Specification for packaged product only.

- Note 2. Equilibrium temperature.

- **Note 3.** Actual voltage levels and differential swing will depend on customer termination scheme. Typically, a 400mV swing is available in the  $100\Omega$  environment and a 200mV swing in the  $50\Omega$  environment. Refer to the "CML Termination" diagram for more details.

- Note 4. See Figure 3a and 3b.

- Note 5. See Figure 4.

- Note 6. Inputs must be biased to logic LOW or HIGH when  $V_{CC}$  is less than 3.0V.

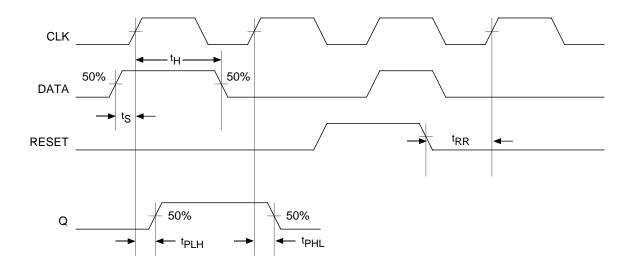

# AC ELECTRICAL CHARACTERISTICS(1)

$V_{CC}$  = 2.3V to 5.7V; GND = 0V;  $T_A$  = -40°C to +85°C

| Symbol                               | Parameter                                                         | Min.              | Тур.        | Max.        | Unit | Condition <sup>(2)</sup> |

|--------------------------------------|-------------------------------------------------------------------|-------------------|-------------|-------------|------|--------------------------|

| f <sub>MAX</sub>                     | Max. Operating Frequency                                          | 2.5               | _           | _           | GHz  |                          |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay, CLK to Q<br>R to Q                             |                   |             | 400<br>500  | ps   |                          |

| t <sub>S</sub>                       | Set-Up Time                                                       | 40                | _           | _           | ps   |                          |

| t <sub>H</sub>                       | Hold Time                                                         | 40                | _           | _           | ps   |                          |

| t <sub>RR</sub>                      | Reset Recovery                                                    | 400               | _           | _           | ps   |                          |

| t <sub>PW</sub>                      | Minimum Pulse Width CLK to Q $V_{CC} < 3V$ $V_{CC} \ge 3V$ R to Q | 160<br>140<br>250 | _<br>_<br>_ | _<br>_<br>_ | ps   |                          |

| t <sub>r</sub>                       | CML Output Rise/Fall Times (20% to 80%)                           | 35                | _           | 150         | ps   |                          |

- Note 1. Specification for packaged product only.

- Note 2. Tested using environment of Figure 3b,  $50\Omega$  load CML output.

# TIMING DIAGRAMS

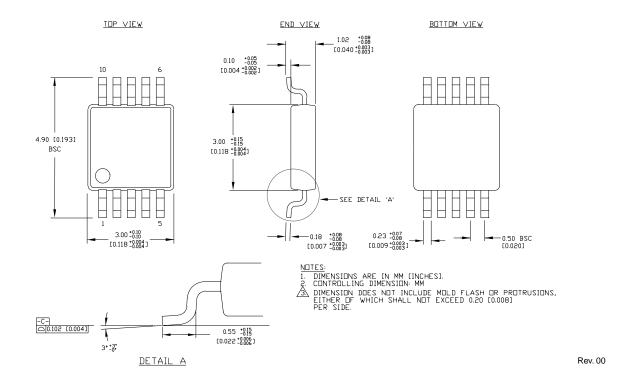

# PRODUCT ORDERING CODE

| Ordering   | Package | Operating  |

|------------|---------|------------|

| Code       | Type    | Range      |

| SY55852UKC | K10-1   | Commercial |

# 10 LEAD MSOP (K10-1)

#### MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2003 Micrel, Incorporated.