# 3.3V PECL/ECL DIFFERENTIAL PHASE-FREQUENCY DETECTOR

Precision Edge™ SY100EP140L FINAL

### **FEATURES**

■ >2GHz maximum frequency

■ < 220ps rise/fall time

■ Low-voltage: +3.3V ±10% operation

■ Wide operating temperature range: -40°C to +85°C

**■** Fully differential throughput architecture

■ Transfer gain:

1.0mV/degree at 1.4GHz 1.2mV/degree at 1.0GHz

■ Available in 8-Pin SOIC package

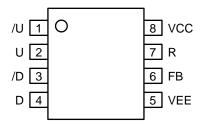

#### PIN CONFIGURATION

8-pin SOIC package

ECL Pro™

#### **DESCRIPTION**

The SY100EP140L is a high-speed, 2GHz phase-frequency detector optimized to control ultra-low noise VCXOs (voltage-controlled crystal oscillators) in telecom and datacom systems. The phase-frequency detector compares two input signals—a reference input and a feedback input. Any mismatches in the two input signal's phase or frequency will result in the output UP or DOWN pulse stream. When the difference between the UP and DOWN outputs are integrated, the resulting control signal speeds-up or slowsdown a VCO or acts as the error voltage for a precision VCXO.

The SY100EP140L I/O is 100K LVECL/LVPECL compatible. The device operates from a +3.0V to +3.6V (LVPECL) or -3.0V to -3.6V (LVECL) supply voltage. The output swing is 400mV with < 220ps rise/fall times, which enables the part to operate at a very high frequency. Operating temperature range is guaranteed over the  $-40^{\circ}$ C to +85°C industrial range.

#### **PIN NAMES**

| Pin             | Function                                                                                                                                 |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------|

| D, /D           | LVPECL/LVECL differential UP outputs. Terminate with $50\Omega$ to $V_{CC}$ -2V.                                                         |

| U, /U           | LVPECL/LVECL differential DOWN outputs. Terminate with $50\Omega$ to $V_{CC}$ –2V.                                                       |

| R               | LVPECL/LVECL reference input. Internal $75k\Omega$ pulldown to $V_{EE}$ . Default state is logic LOW when left floating.                 |

| FB              | LVPECL/LVECL feedback input. Internal 75k $\Omega$ pulldown resistor to V <sub>EE</sub> . Default state is logic LOW when left floating. |

| V <sub>CC</sub> | Positive supply. Bypass with 0.1μF//0.01μF low ESR capacitors.                                                                           |

| V <sub>EE</sub> | Negative power supply. For PECL operation, connect to GND.                                                                               |

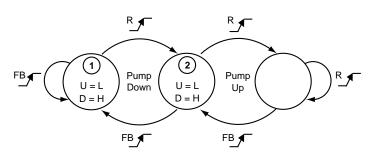

## PHASE DETECTOR LOGIC MODEL

## TRUTH TABLE

| Phase             | In | put | Out | tput |

|-------------------|----|-----|-----|------|

| Dector State      | R  | FB  | U   | D    |

| Pump Down (2-1-2) |    |     |     |      |

| 2                 | L  | L   | L   | L    |

| 2–1               | L  | Н   | L   | Н    |

| 1–2               | Н  | Χ   | L   | L    |

| 2                 | L  | L   | L   | L    |

| Pump Up (2-3-2)   |    |     |     |      |

| 2                 | L  | L   | L   | L    |

| 2–3               | Н  | L   | Н   | L    |

| 3–2               | Х  | Н   | L   | L    |

| 2                 | L  | L   | L   | L    |

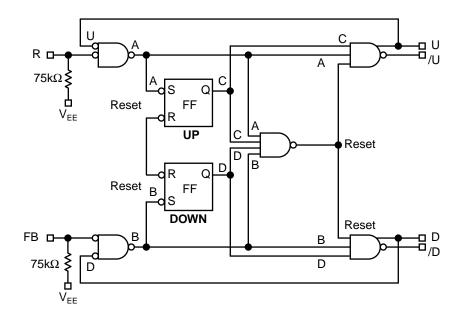

## LOGIC DIAGRAM

## ABSOLUTE MAXIMUM RATINGS(1)

| Symbol                            | Rating                                                                                                                   | Value                  | Unit             |             |      |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------|------------------|-------------|------|

| V <sub>CC</sub> — V <sub>EE</sub> | Power Supply Voltage                                                                                                     |                        |                  | 6V          | V    |

| V <sub>IN</sub>                   | Input Voltage ( $V_{CC} = 0V$ , $V_{IN}$ not more negligible Input Voltage ( $V_{EE} = 0V$ , $V_{IN}$ not more positive. | -6.0 to 0<br>+6.0 to 0 | V<br>V           |             |      |

| I <sub>OUT</sub>                  | Output Current                                                                                                           | –Continuou<br>–Surge   | S                | 50<br>100   | mA   |

| T <sub>A</sub>                    | Operating Temperature Range                                                                                              |                        |                  | -40 to +85  | °C   |

| T <sub>store</sub>                | Storage Temperature Range                                                                                                |                        |                  | -65 to +150 | °C   |

|                                   | Maximum Junction Temperature                                                                                             |                        |                  | 135         | °C   |

| $\theta_{JA}$                     | Package Thermal Resistance (Junction-to-Ambient)                                                                         | –Still-Air<br>–500lfpm | (SOIC)<br>(SOIC) | 160<br>109  | °C/W |

|                                   |                                                                                                                          | –Still-Air<br>–500lfpm | (MSOP)<br>(MSOP) | 206<br>155  | °C/W |

| θ <sub>JC</sub>                   | Package Thermal Resistance (Junction-to-Case)                                                                            |                        | (SOIC)<br>(MSOP) | 39<br>39    | °C/W |

Note 1. Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to ABSOLUTE MAXIMUM RATING conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS(1)

|                 |                          | T <sub>A</sub> = -40°C |      | T <sub>A</sub> = +25°C |      |      | T <sub>A</sub> = +85°C |      |      |      |      |                   |

|-----------------|--------------------------|------------------------|------|------------------------|------|------|------------------------|------|------|------|------|-------------------|

| Symbol          | Parameter                | Min.                   | Тур. | Max.                   | Min. | Тур. | Max.                   | Min. | Тур. | Max. | Unit | Condition         |

| V <sub>CC</sub> | Power Supply Voltage     |                        |      |                        |      |      |                        |      |      |      | V    |                   |

|                 | (LVPECL)                 | 3.0                    | —    | 3.6                    | 3.0  | _    | 3.6                    | 3.0  | _    | 3.6  |      |                   |

|                 | (LVECL)                  | -3.6                   | _    | -3.0                   | -3.6 | _    | -3.0                   | -3.6 |      | -3.0 |      |                   |

| I <sub>EE</sub> | Power Supply Current     | 55                     | 70   | 85                     | 60   | 74   | 90                     | 63   | 78   | 93   | mA   |                   |

| I <sub>IH</sub> | Input HIGH Current       |                        |      | 150                    | 1    |      | 150                    |      | ١    | 150  | μА   | $V_{IN} = V_{IH}$ |

| I <sub>IL</sub> | Input LOW Current R, FB  | 0.5                    |      |                        | 0.5  |      | _                      | 0.5  | ١    |      | μΑ   | $V_{IN} = V_{IL}$ |

| C <sub>IN</sub> | Input Capacitance (MSOP) |                        | _    | _                      |      | 0.75 |                        |      | _    |      | pF   |                   |

|                 | (SOIC)                   | _                      | _    | _                      | _    | 1.1  | _                      | _    | _    | _    | pF   |                   |

**Note 1.** 100KEP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and traverse airflow greater than 500lfpm is maintained.

### LVPECL DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = 3.3V \pm 10\%, V_{EE} = 0V$

|                 |                                      | T <sub>A</sub> = -40°C |      | T <sub>A</sub> = +25°C |      |      | T <sub>A</sub> = +85°C |      |      |      |      |                                    |

|-----------------|--------------------------------------|------------------------|------|------------------------|------|------|------------------------|------|------|------|------|------------------------------------|

| Symbol          | Parameter                            | Min.                   | Тур. | Max.                   | Min. | Тур. | Max.                   | Min. | Тур. | Max. | Unit | Condition                          |

| V <sub>IL</sub> | Input LOW Voltage<br>(Single-Ended)  | 1355                   |      | 1675                   | 1355 | _    | 1675                   | 1355 |      | 1675 | mV   |                                    |

| V <sub>IH</sub> | Input HIGH Voltage<br>(Single-Ended) | 2075                   | _    | 2420                   | 2075 | _    | 2420                   | 2075 | -    | 2420 | mV   |                                    |

| V <sub>OL</sub> | Output LOW Voltage                   | 1355                   | 1480 | 1605                   | 1355 | 1480 | 1605                   | 1355 | 1480 | 1605 | mV   | 50 $\Omega$ to V <sub>CC</sub> –2V |

| V <sub>OH</sub> | Output HIGH Voltage                  | 2155                   | 2280 | 2405                   | 2155 | 2280 | 2405                   | 2155 | 2280 | 2405 | mV   | 50 $\Omega$ to V <sub>CC</sub> –2V |

Note 1. 100KEP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and traverse airflow greater than 500lfpm is maintained. Input and output parameters are at V<sub>CC</sub> = 3.3V. They vary 1:1 with V<sub>CC</sub>.

## ECL DC ELECTRICAL CHARACTERISTICS(1)

$V_{CC} = 0V$ ,  $V_{EE} = -3.6V$  to -3.0V

|                 |                     | T <sub>A</sub> = -40°C |       | T <sub>A</sub> = +25°C |       |       | T <sub>A</sub> = +85°C |       |       |       |      |                                    |

|-----------------|---------------------|------------------------|-------|------------------------|-------|-------|------------------------|-------|-------|-------|------|------------------------------------|

| Symbol          | Parameter           | Min.                   | Тур.  | Max.                   | Min.  | Тур.  | Max.                   | Min.  | Тур.  | Max.  | Unit | Condition                          |

| $V_{IL}$        | Input LOW Voltage   | -1945                  |       | -1625                  | -1945 | _     | -1625                  | -1945 |       | -1625 | mV   |                                    |

| V <sub>IH</sub> | Input HIGH Voltage  | -1225                  |       | -880                   | -1225 | _     | -880                   | -1225 |       | -880  | mV   |                                    |

| V <sub>OL</sub> | Outuput LOW Voltage | -1545                  | -1420 | -1295                  | -1545 | -1420 | -1295                  | -1545 | -1420 | -1295 | mV   | $50\Omega$ to $V_{CC}$ –2V         |

| V <sub>OH</sub> | Output HIGH Voltage | -1145                  | -1020 | -895                   | -1145 | -1020 | -895                   | -1145 | -1020 | -895  | mV   | 50 $\Omega$ to V <sub>CC</sub> –2V |

Note 1. 100KEP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and traverse airflow greater than 500lfpm is maintained. Input and output parameters are at  $V_{CC} = 3.3V$ . They vary 1:1 with  $V_{CC}$ .

## AC ELECTRICAL CHARACTERISTICS(1)

LVPECL:  $V_{CC} = 3.3V \pm 10\%$ ,  $V_{EE} = 0V$ ; LVECL:  $V_{EE} = -3.3V \pm 10\%$ ,  $V_{CC} = 0V$

|                                      | 00 LL                                                                               |                        |            | •                      |            | 00         |                      |            |            |            |                   |           |

|--------------------------------------|-------------------------------------------------------------------------------------|------------------------|------------|------------------------|------------|------------|----------------------|------------|------------|------------|-------------------|-----------|

|                                      |                                                                                     | T <sub>A</sub> = -40°C |            | T <sub>A</sub> = +25°C |            |            | $T_A = +85^{\circ}C$ |            |            |            |                   |           |

| Symbol                               | Parameter                                                                           | Min.                   | Тур.       | Max.                   | Min.       | Тур.       | Max.                 | Min.       | Тур.       | Max.       | Unit              | Condition |

| f <sub>MAX</sub>                     | Maximum Frequency <sup>(1)</sup>                                                    | 1                      | >2         | _                      | _          | >2         |                      | 1          | >2         | _          | GHz               |           |

| t <sub>PLH</sub><br>t <sub>PHL</sub> | Propagation Delay to Output<br>(Differential)<br>R to U, FB to D<br>FB to U, R to D | 220<br>280             | 450<br>650 | 600<br>800             | 230<br>280 | 475<br>650 | 625<br>850           | 240<br>300 | 500<br>700 | 650<br>900 | ps<br>ps          |           |

| t <sub>JITTER</sub>                  | Cycle-to-Cycle Jitter (rms)                                                         |                        | 0.2        | < 1                    | _          | 0.2        | < 1                  | 1          | 0.2        | < 1        | ps <sub>rms</sub> |           |

| V <sub>PP</sub>                      | Input Voltage Swing                                                                 | 400                    | 800        | 1200                   | 400        | 800        | 1200                 | 400        | 800        | 1200       | mV                |           |

| t <sub>r</sub> , t <sub>f</sub>      | Output Rise/Fall Time Q, /Q (20% to 80%)                                            | 50                     | 90         | 180                    | 60         | 100        | 200                  | 70         | 120        | 220        | ps                |           |

**Note 1.** Measured with 750mV input signal, 50% duty cycle. All loading with a  $50\Omega$  to  $V_{CC}$ =2.0V.

#### PRODUCT ORDERING INFORMATION

| Ordering<br>Code                 | Package<br>Type | Operating<br>Range | Marking<br>Code |

|----------------------------------|-----------------|--------------------|-----------------|

| SY100EP140LZC                    | Z8-1            | Commercial         | XP140L          |

| SY100EP140LZCTR <sup>(1)</sup>   | Z8-1            | Commercial         | XP140L          |

| SY100EP140LZI <sup>(2)</sup>     | Z8-1            | Industrial         | XP140L          |

| SY100EP140LZITR <sup>(1,2)</sup> | Z8-1            | Industrial         | XP140L          |

Note 1. Tape and Reel

Note 2. Recommended for new designs.

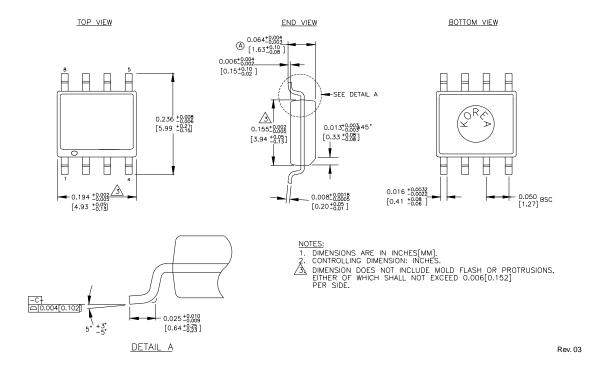

## **8 LEAD PLASTIC SOIC (Z8-1)**

#### MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2003 Micrel, Incorporated.