# 5V/3.3V ÷2, ÷4, ÷8 CLOCK GENERATION CHIP

Precision Edge™ SY10EL34/L SY100EL34/L FINAL

## **FEATURES**

- 3.3V and 5V power supply options

- 50ps output-to-output skew

- Synchronous enable/disable

- Master Reset for synchronization

- Internal 75K $\Omega$  input pull-down resistors

- Available in 16-pin SOIC package

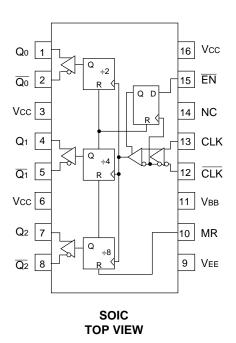

## PIN CONFIGURATION/BLOCK DIAGRAM

Precision Edge™

## **DESCRIPTION**

The SY10/100EL34/L are low skew  $\div 2$ ,  $\div 4$ ,  $\div 8$  clock generation chips designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the common output edges are all precisely aligned. The devices can be driven by either a differential or single-ended ECL or, if positive power supplies are used, PECL input signal. In addition, by using the VBB output, a sinusoidal source can be AC-coupled into the device. If a single-ended input is to be used, the VBB output should be connected to the  $\overline{\text{CLK}}$  input and bypassed to ground via a  $0.01\mu\text{F}$  capacitor. The VBB output is designed to act as the switching reference for the input of the EL34/L under single-ended input conditions. As a result, this pin can only source/sink up to 0.5mA of current.

The common enable  $(\overline{\text{EN}})$  is synchronous so that the internal dividers will only be enabled/disabled when the internal clock is already in the LOW state. This avoids any chance of generating a runt clock pulse on the internal clock when the device is enabled/disabled as can happen with an asynchronous control. An internal runt pulse could lead to losing synchronization between the internal divider stages. The internal enable flip-flop is clocked on the falling edge of the divider stages. The internal enable flip-flop is clocked on the falling edge of the input clock, therefore, all associated specification limits are referenced to the negative edge of the clock input.

Upon start-up, the internal flip-flops will attain a random state; the master reset (MR) input allows for the synchronization of the internal dividers, as well as for multiple EL34/Ls in a system.

## **PIN NAMES**

| Pin            | Function                  |

|----------------|---------------------------|

| CLK            | Differential Clock Inputs |

| ĒN             | Synchronous Enable        |

| MR             | Master Reset              |

| Vвв            | Reference Output          |

| Q <sub>0</sub> | Differential ÷2 Outputs   |

| Q1             | Differential ÷4 Outputs   |

| Q2             | Differential ÷8 Outputs   |

Precision Edge is a trademark of Micrel, Inc.

## TRUTH TABLE

| CLK | EN | MR | Function   |

|-----|----|----|------------|

| Z   | L  | L  | Divide     |

| ZZ  | Н  | L  | Hold Q0-2  |

| Х   | Х  | Н  | Reset Q0-2 |

#### NOTE:

Z = LOW-to-HIGH transition ZZ = HIGH-to-LOW transition

# DC ELECTRICAL CHARACTERISTICS(1)

VEE = VEE (Min.) to VEE (Max.); VCC = GND

|        |                                    | TA = -40°C     |      | TA = 0°C       |                | T    | TA = +25°C     |                | TA = +85°C |                |                |      |                |      |

|--------|------------------------------------|----------------|------|----------------|----------------|------|----------------|----------------|------------|----------------|----------------|------|----------------|------|

| Symbol | Parameter                          | Min.           | Тур. | Max.           | Min.           | Тур. | Max.           | Min.           | Тур.       | Max.           | Min.           | Тур. | Max.           | Unit |

| IEE    | Power Supply 10EL<br>Current 100EL | _              | _    | 49<br>49       | _              | _    | 49<br>49       | _              | _          | 49<br>49       |                |      | 49<br>54       | mA   |

| Vвв    |                                    | -1.43<br>-1.38 |      | -1.30<br>-1.26 | -1.38<br>-1.38 |      | -1.27<br>-1.26 | -1.35<br>-1.38 |            | -1.25<br>-1.26 | -1.31<br>-1.38 |      | -1.19<br>-1.26 | V    |

| IIН    | Input High Current                 | _              | _    | 150            | _              | _    | 150            |                | _          | 150            | _              | _    | 150            | μΑ   |

#### NOTE:

1. Parametric values specified at: 5 volt Power Supply Range 100EL34 Series: -4.2V to -5.5V.

10EL34 Series -4.75V to -5.5V.

3 volt Power Supply Range 10/100EL34L Series: -3.0V to -3.8V.

# **AC ELECTRICAL CHARACTERISTICS**(1)

VEE = VEE (Min.) to VEE (Max.); VCC = GND

|              |                                         | TA = -40°C |             | TA = 0°C     |            | TA = +25°C  |              | TA = +85°C |             |              |            |             |              |      |

|--------------|-----------------------------------------|------------|-------------|--------------|------------|-------------|--------------|------------|-------------|--------------|------------|-------------|--------------|------|

| Symbol       | Parameter                               | Min.       | Тур.        | Max.         | Unit |

| tPLH<br>tPHL | Propagation Delay to Output CLK MR      | 960<br>650 | 1100<br>800 | 1200<br>1010 | ps   |

| tskew        | Within-Device Skew <sup>(2)</sup>       | _          | _           | 50           | _          | _           | 50           | _          | _           | 50           | _          | _           | 50           | ps   |

| ts           | Set-up Time EN                          | 400        | _           | _            | 400        | _           | _            | 400        | _           |              | 400        | _           | _            | ps   |

| tH           | Hold Time EN                            | 200        | _           | _            | 200        | _           | _            | 200        | _           |              | 200        | _           | _            | ps   |

| VPP          | Minimum Input Swing <sup>(3)</sup>      | 250        | _           | _            | 250        | _           |              | 250        | _           | _            | 250        | _           | _            | mV   |

| VCMR         | Common Mode Range <sup>(4)</sup>        | -1.3       | _           | -0.4         | -1.4       | _           | -0.4         | -1.4       | _           | -0.4         | -1.4       | _           | -0.4         | V    |

| tr<br>tf     | Output Rise/Fall Times<br>Q (20% – 80%) | 275        | 400         | 525          | 275        | 400         | 525          | 275        | 400         | 525          | 275        | 400         | 525          | ps   |

#### **NOTES**

1. Parametric values specified at: 5 volt Power Supply Range 100EL34 Series: -4.2V to -5.5V.

10EL34 Series -4.75V to -5.5V.

3 volt Power Supply Range 10/100EL34L Series: -3.0V to -3.8V.

- 2. Skew is measured between outputs under identical transitions.

- 3. Minimum input swing for which AC parameters are guaranteed. The device will function reliably with differential inputs down to 100mV.

- 4. The CMR range is referenced to the most positive side of the differential input signal. Normal operation is obtained if the HIGH level falls within the specified range and the peak-to-peak voltage lies between VPP min. and 1V. The lower end of the CMR range varies 1:1 with VEE. The numbers in the spec table assume a nominal VEE = -3.3V. Note for PECL operation, the VCMR (min) will be fixed at 3.3V IVCMR (min)I.

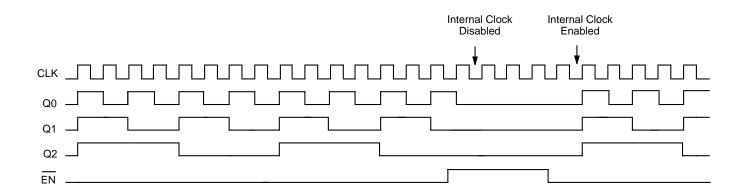

# TIMING DIAGRAM

The  $\overline{\text{EN}}$  signal will freeze the internal clocks to the flip-flops on the first falling edge of CLK after its assertion. The internal dividers will maintain their state during the internal clock freeze and will return to clocking once the internal clocks are unfrozen. The outputs will transition to their next states in the same manner, time and relationship as they would have had the  $\overline{\text{EN}}$  signal not been asserted.

# **PRODUCT ORDERING CODE**

| Ordering<br>Code | Package<br>Type | Operating<br>Range | Marking<br>Code |

|------------------|-----------------|--------------------|-----------------|

| SY10EL34LZC      | Z16-2           | Commercial         | HEL34L          |

| SY10EL34LZCTR*   | Z16-2           | Commercial         | HEL34L          |

| SY100EL34LZC     | Z16-2           | Commercial         | XEL34L          |

| SY100EL34LZCTR*  | Z16-2           | Commercial         | XEL34L          |

| Ordering<br>Code            | Package<br>Type | Operating<br>Range | Marking<br>Code |

|-----------------------------|-----------------|--------------------|-----------------|

| SY10EL34LZI <sup>(1)</sup>  | Z16-2           | Industrial         | HEL34L          |

| SY10EL34LZITR*(1)           | Z16-2           | Industrial         | HEL34L          |

| SY100EL34LZI <sup>(1)</sup> | Z16-2           | Industrial         | XEL34L          |

| SY100EL34LZITR*(1)          | Z16-2           | Industrial         | XEL34L          |

Note 1. Recommended for new designs.

<sup>\*</sup>Tape and Reel

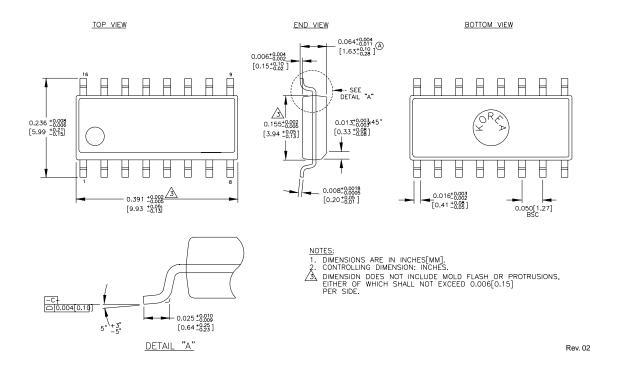

# 16 LEAD SOIC .150" WIDE (Z16-2)

## MICREL, INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2003 Micrel, Incorporated.