# **ICs for Communications**

PMB 2408 V1.1 Wideband-Receiver

#### **Contents**

| 0 | Revisi  | on History                                                              | 3  |

|---|---------|-------------------------------------------------------------------------|----|

| 1 | Genera  | al Overview                                                             | 4  |

|   | 1.1     | Features                                                                | 4  |

|   | 1.2     | Applications                                                            | 4  |

|   | 1.3     | Functional Description                                                  | 4  |

| 2 | Pinnin  | ng                                                                      | 5  |

|   | 2.1     | Pin Description                                                         | 5  |

|   | 2.2     | Pin Configuration                                                       | 6  |

|   | 2.3     | Package Outline                                                         | 6  |

| 3 | Functi  | onal Block Diagram                                                      | 7  |

| 4 | Circui  | t Description                                                           | 8  |

| 5 | Interna | al Input/Output circuits                                                | 12 |

| 6 | Electri | ical Characteristics                                                    | 14 |

|   | 6.1     | Absolut Maximum Ratings                                                 | 14 |

|   | 6.2     | Operational Range                                                       | 15 |

|   | 6.3     | AC/DC Characteristics                                                   | 16 |

| 7 | Test C  | Circuits                                                                | 25 |

|   | 7.1     | Test Circuit 1                                                          | 25 |

|   | 7.2     | Test Circuit 1.1                                                        | 26 |

|   | 7.3     | Test Circuit 1.2                                                        | 26 |

|   | 7.4     | Test Circuit 2                                                          | 27 |

|   | 7.5     | Test Board                                                              | 28 |

| 8 | Design  | n Hints                                                                 |    |

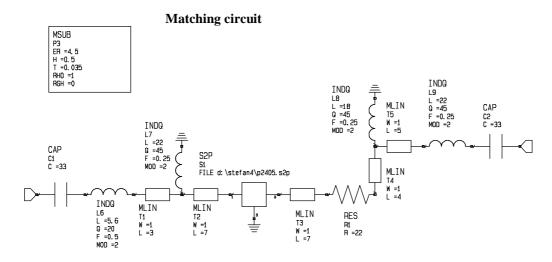

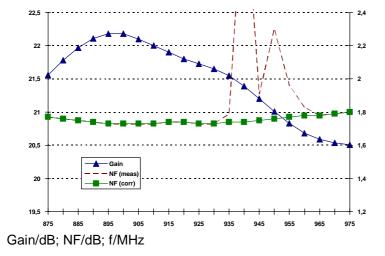

|   | 8.1     | LNA Matching for 925 MHz                                                | 35 |

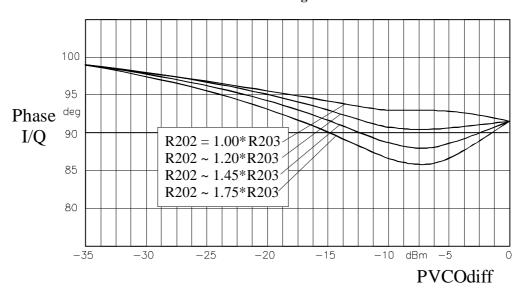

|   | 8.2     | VCO: Possibility of I/Q phase error correction                          | 36 |

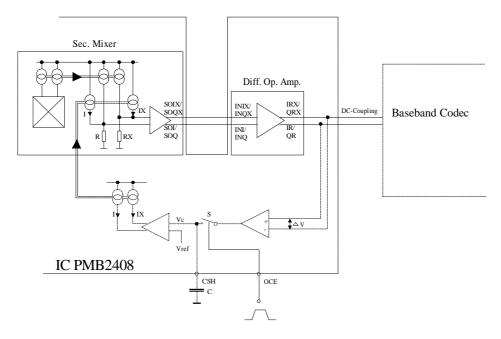

|   | 8.3     | Sample and Hold: Offset compensation diagram for smallband applications | 37 |

|   | 8.4     | Sample and Hold: Offset compensation diagram for wideband applications  | 38 |

| 9 | Diagra  | ams                                                                     | 39 |

#### 0 Revision History

|   |         | Data sh | eet 5/99 | Data sh | eet  |        |  |

|---|---------|---------|----------|---------|------|--------|--|

| # | Subjekt | Page    | Item     | Page    | Item | Change |  |

|   |         |         |          |         |      |        |  |

|   |         |         |          |         |      |        |  |

|   |         |         |          |         |      |        |  |

|   |         |         |          |         |      |        |  |

|   |         |         |          |         |      |        |  |

|   |         |         |          |         |      |        |  |

|   |         |         |          |         |      |        |  |

#### 1 General Overview

#### 1.1 Features

- Heterodyne receiver with demodulator

- On-chip low noise amplifier (LNA), gain switchable

- Switchable (on / off) reference voltage for biasing either the internal LNA or an external LNA

- Demodulation and generation of I/Q components

- Low mixer noise 9dB (SSB)

- High input intercept point +2dB

- Integrated phase shifter

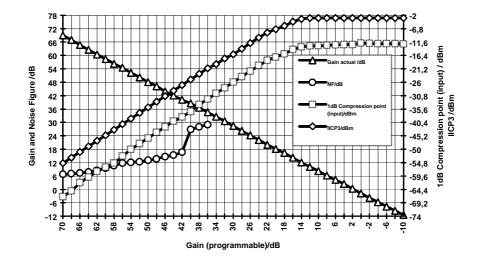

- IF amplifier with 80dB programmable gain control (PGC) in steps of 2dB

- Active part of a local-oscillator (LO2) with external tuning circuit or possibility to use it as amplifier

- Two differential operational amplifiers for use as base-band amplifier in smallband applications

- Low power consumption due to highly flexible power down capability

- Wide input frequency range up to 2.5 GHz

- Wide IF range from 40 MHz to 460 MHz

- Channel bandwidth (baseband bandwidth) up to 5 MHz (VS = 2.7V)

- Low Supply Voltage down to 2.7V

- P-TQFP-48 package

- Temperature range -40° to 85°C

#### 1.2 Applications

- Vector modulated digital mobile cellular systems as WLAN etc.

- Various demodulation schemes, such as PM, PSK, FSK, QAM, QPSK, GMSK

- Space and power saving optimisations of existing discrete demodulator circuits

#### 1.3 Functional Description

The PMB 2408 is a single-chip double-conversion heterodyne receiver with LO-phase shifting circuitry for the I/Q-Phase demodulation on chip. It also includes a low noise amplifier with switchable gain, a switchable reference voltage for biasing either the internal or an external LNA, the second local oscillator with a VCO output buffer, a programmable gain controlled IF amplifier, two differential operational amplifiers for base band purposes in smallband applications, and a power down circuitry.

The PMB 2408 is designed for vector modulated digital systems like WLAN with larger channel bandwidth.

#### 2 Pinning

#### 2.1 Pin Description

| Pin No.          | Symbol | Function                                                    |

|------------------|--------|-------------------------------------------------------------|

| 1                | VS2    | Supply voltage 2                                            |

|                  |        | (IF circuit part, Op. Amp, 3-wire bus, offset compensation) |

| 2                | DIV1/3 | Divider-logic input                                         |

| 3, 6, 16, 22, 30 | GND    | Ground                                                      |

| 4                | CSH1   | Sample and hold capacitance 1                               |

| 5                | CSH2   | Sample and hold capacitance 2                               |

| 7                | OCE    | Sample and hold input                                       |

| 8                | IFI    | Non-inverting IF input                                      |

| 9                | IFIX   | Inverting IF input                                          |

| 10               | SYGCDT | Data input ( 3 wire bus of PGC )                            |

| 11               | SYGCCL | Clock input ( 3 wire bus of PGC )                           |

| 12               | PGCSTR | Enable input ( 3 wire bus of PGC )                          |

| 13               | SIX    | Inverted signal input of first mixer                        |

| 14               | SI     | Non-inverted signal input of first mixer                    |

| 15               | RXON1  | Power down input 1 ( RF )                                   |

| 17               | LO1X   | Inverting input for first local oscillator                  |

| 18               | LO1    | Non-inverting input for first local oscillator              |

| 19               | VS1    | Supply voltage 1 ( First mixer, bias for LNA )              |

| 20               | MO     | Non-inverted output of first mixer                          |

| 21               | MOX    | Inverted output of first mixer                              |

| 23               | LO2OX  | Inverted Output of Inst Inixer  Inverted VCO output buffer  |

| 24               | LO2O   | Non-inverted VCO output buffer                              |

| 25               | GND3   | Ground3 ( LNA ground )                                      |

| 26               | AO     | LNA output                                                  |

| 27               | VS3    | Supply voltage 3 (LNA)                                      |

| 28               | AREF   | LNA reference input                                         |

| 29               | AI     | LNA input                                                   |

| 31               | PUPLO2 | Power up input for VCO and VCO output buffer                |

| 32               | LO2X   | Base inverting input for second local oscillator            |

| 33               | LO2EX  | Emitter inverting input for second local oscillator         |

| 34               | LO2E   | Emitter inverting input for second local oscillator         |

| 35               | LO2    | Base non-inverting input for second local oscillator        |

| 36               | RXON2  | Power down input 2 for the IF-part and Op. Amp.'s           |

| 37               | SOQX   | Inverting quadratur demodulator signal output               |

| 38               | FBQ    | Feedback tap for "fixed-gain" OpAmp.'s (Q)                  |

| 39               | QRX    | Inverting op. amp. signal output (Q)                        |

|                  |        |                                                             |

| 40               | QR     | Non-inverting op. amp. signal output (Q)                    |

| 41               | FBQX   | Feedback tap for "fixed-gain" OpAmp.'s (Q)                  |

| 42               | SOQ    | Non-inverting quadratur demodulator signal output           |

| 43               | SOIX   | Inverting in-phase demodulator signal output                |

| 44               | FBI    | Feedback tap for "fixed-gain" OpAmp.'s (I)                  |

| 45               | IRX    | Inverting op. amp. signal output (I)                        |

| 46               | IR     | Non-inverting op. amp. signal output (I)                    |

| 47               | FBIX   | Feedback tap for "fixed-gain" OpAmp.'s (I)                  |

| 48               | SOI    | Non-inverting in-phase demodulator signal output            |

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

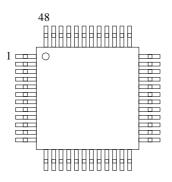

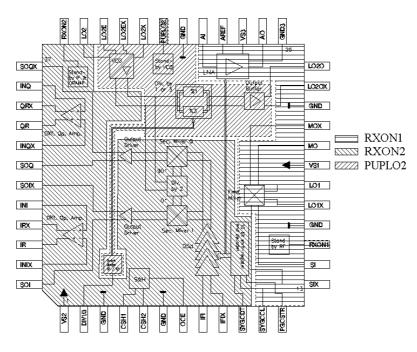

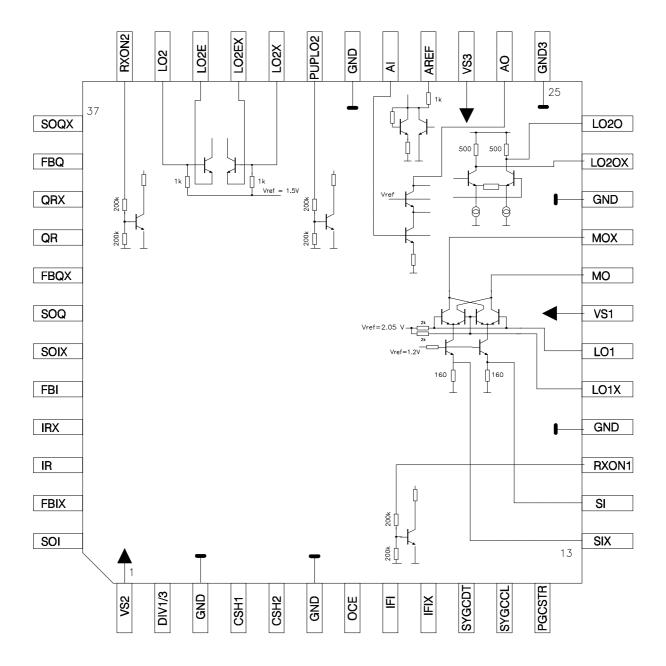

#### **2.2 Pin Configuration** (top view)

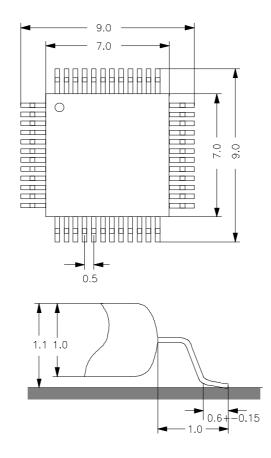

#### 2.3 Package Outline

Quad Flat package P-TQFP-48

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

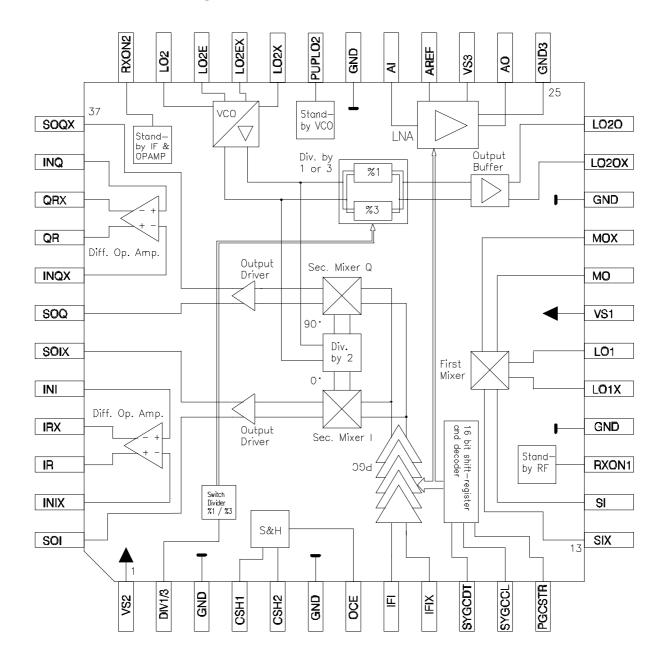

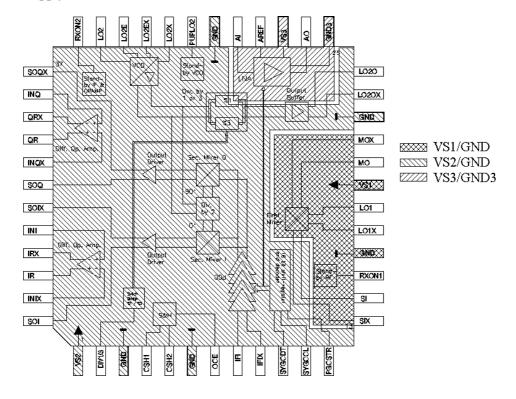

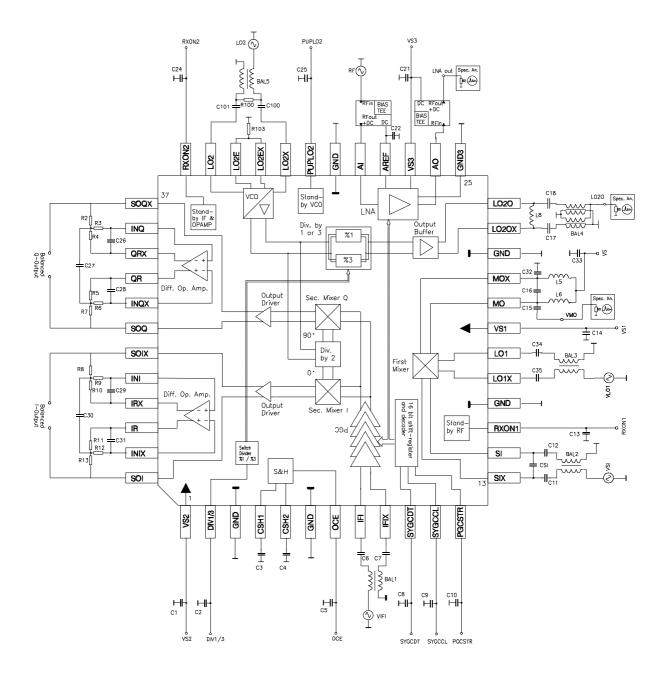

#### 3 Functional Block Diagram

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### 4 Circuit Description

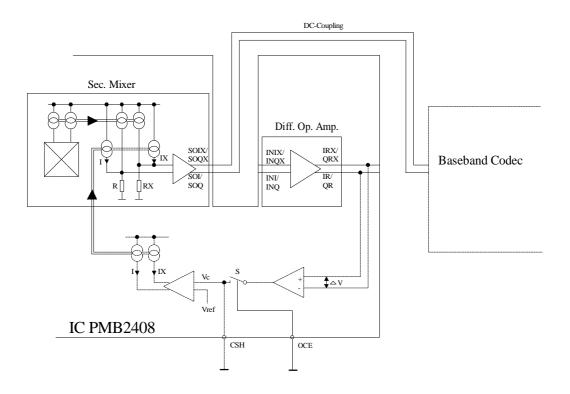

The input signal is amplified by the internal or an external LNA and filtered in an external Filter (LNA programming see table3). The filtered signal SI/SIX and the first local oscillator signal LO1/LO1X are mixed down to an intermediate frequency (IF). The open collector output of the mixer generates a differential current at pins MO/MOX which is filtered by an external LC tank circuit. An external SAW filter following this LC circuit is used for channel selection.

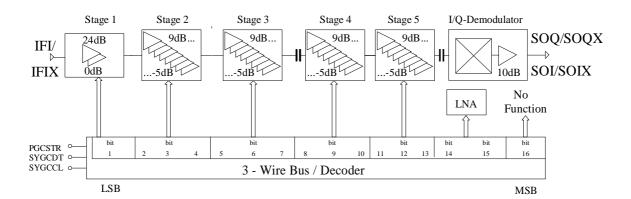

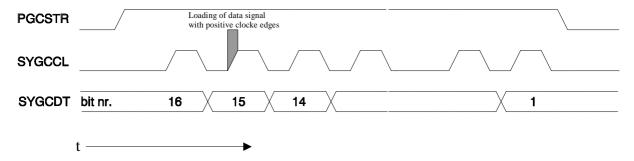

The amplification of the IF signal is performed by a digitally programmable gain-controlled amplifier. Gain programming is done by loading a 16 bit control word into a register via the 3 - wire bus (see Fig. 1 and 3 and also table 3 and 4). Serial data is clocked out from MSB to LSB. After power-down the information in the register is lost.

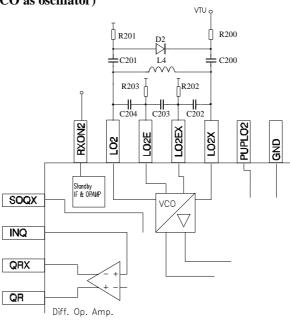

The second local oscillator signal LO2 is generated either by the active part of an on-chip oscillator (with external tuning circuit) or by an external VCO.

Depending on the logic level at pin DIV1/3 (see table 2), the internal LO2 signal is fed directly to the buffered output (DIV1/3: L) or to a divider by 3 (DIV1/3: H) and then to a buffered output and also to a divider, which generates orthogonal signals at half the VCO frequency. The filtered IF signal re-enters the chip at the IFI/IFIX input, where it is amplified and converted to the final output frequency with each of the orthogonal signals. The resulting in-phase and quadrature signals pass through differential output drivers and appear at SOI/SOIX and SOQ/SOQX outputs, respectively.

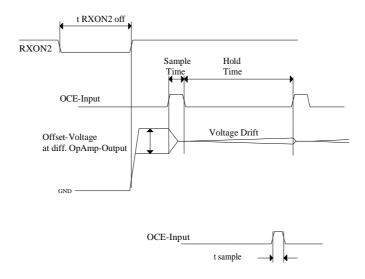

Two differential operational amplifiers with the input signals INI/INIX (INQ/INQX) and the output signals IR/IRX (QR/QRX) can be used as baseband amplifiers or active baseband filters in smallband applications (see design hint 8.3 page 37). At both outputs IR/IRX (QR/QRX) the differential offset is sensed via the sample and hold circuitry. A feedback loop corrects the remaining offset error below the tolerable input value of the baseband A/D converter. For wideband applications please refer to design hint 8.4 page 38.

Differential signals and symmetrical circuitry are used throughout. Bias drivers generate internal temperatureand supply voltage compensated reference voltages required by various circuit blocks. Switching the power down inputs RXON1,RXON2 and PUPLO2 from HIGH to LOW (see table 1 and Fig. 2.1) sets the circuit from its normal operating mode into a mode with reduced supply current. Fig. 2.2 shows the supply function.

There are three supply voltages: VS1 supplies the first mixer and the standby RF circuit, VS2 supplies the complete IF part and VS3 supplies the LNA. The LNA has an own ground pin GND3, the rest of the circuits are grounded by GND.

Figure 1: Block Diagram of PGC and 3 - wire bus

Figure 2: Power Down- and Supply-Function

**Figure 2.1: Power Down Function**

**Figure 2.2: Supply Function**

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

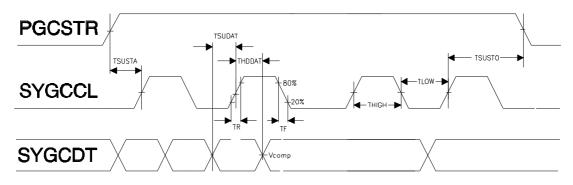

Figure 3: Three-wire bus timing diagram

**Table 1: Power Down Function**

| RXON1 | RF Part |

|-------|---------|

| L     | Off     |

| Н     | On      |

| RXON2 | IF Part & Op.Amp.'s |

|-------|---------------------|

| L     | Off                 |

| Н     | On                  |

| PUPLO2 | VCO/Buffer<br>Div. by 1 or 3 |

|--------|------------------------------|

| L      | Off                          |

| Н      | On                           |

The PGC adjustment is not stored during power down of RXON2.

Table 2: Divider DIV1/3: switch logic

| DIV 1/3 | Divider |

|---------|---------|

| L       | %1      |

| Н       | %3      |

Table 3: LNA gain control:

| general           |              |                  |             |  |  |  |  |  |  |  |

|-------------------|--------------|------------------|-------------|--|--|--|--|--|--|--|

| Reference Voltage | Gain Control | bit 14           | bit 15      |  |  |  |  |  |  |  |

|                   |              | reference switch | gain switch |  |  |  |  |  |  |  |

| Aref = on         | H-gain       | 1                | 1           |  |  |  |  |  |  |  |

| Aref = on         | L-gain       | 1                | 0           |  |  |  |  |  |  |  |

| Aref = off        |              | 0                | X           |  |  |  |  |  |  |  |

| as LNA |        |       |  |  |  |  |  |  |

|--------|--------|-------|--|--|--|--|--|--|

|        | bit 14 | bit15 |  |  |  |  |  |  |

| H-gain | 1      | 1     |  |  |  |  |  |  |

| L-gain | 1      | 0     |  |  |  |  |  |  |

| as switch     |   |   |  |  |  |  |  |  |  |

|---------------|---|---|--|--|--|--|--|--|--|

| bit 14 bit 15 |   |   |  |  |  |  |  |  |  |

| Aref=on       | 1 | 1 |  |  |  |  |  |  |  |

| Aref=off      | 0 | 1 |  |  |  |  |  |  |  |

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

**Table 4: Table of PGC-, LNA-Gain Control**

|          | bit   |   |         |   |   |         |   |   |         |    |    |         |    |      |      |               |

|----------|-------|---|---------|---|---|---------|---|---|---------|----|----|---------|----|------|------|---------------|

|          |       |   |         |   |   | PGC     |   |   |         |    |    |         |    | LNA  |      | no            |

| G/dB     | st. 1 |   | stage 2 | 2 |   | stage 3 | 3 |   | stage 4 | 1  |    | stage 5 | 5  | Aref | gain | func-<br>tion |

| PGC      | 1     | 2 | 3       | 4 | 5 | 6       | 7 | 8 | 9       | 10 | 11 | 12      | 13 | 14   | 15   | 16            |

| 70       | 1     | 1 | 1       | 1 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 68       | 1     | 1 | 1       | 0 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 66       | 1     | 1 | 0       | 1 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 64       | 1     | 1 | 0       | 0 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 62       | 1     | 0 | 1       | 1 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 60       | 1     | 0 | 1       | 0 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 58       | 1     | 0 | 0       | 1 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 56       | 1     | 0 | 0       | 0 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 54       | 1     | 0 | 0       | 0 | 1 | 1       | 0 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 52       | 1     | 0 | 0       | 0 | 1 | 0       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 50       | 1     | 0 | 0       | 0 | 1 | 0       | 0 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 48<br>46 | 1     | 0 | 0       | 0 | 0 | 1 1     | 0 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 44       | 1     | 0 | 0       | 0 | 0 | 0       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 42       | 1     | 0 | 0       | 0 | 0 | 0       | 0 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 40       | 0     | 1 | 0       | 0 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 38       | 0     | 0 | 1       | 1 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 36       | 0     | 0 | 1       | 0 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 34       | 0     | 0 | 0       | 1 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 32       | 0     | 0 | 0       | 0 | 1 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 30       | 0     | 0 | 0       | 0 | 1 | 1       | 0 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 28       | 0     | 0 | 0       | 0 | 1 | 0       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 26       | 0     | 0 | 0       | 0 | 1 | 0       | 0 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 24       | 0     | 0 | 0       | 0 | 0 | 1       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 22       | 0     | 0 | 0       | 0 | 0 | 1       | 0 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 20       | 0     | 0 | 0       | 0 | 0 | 0       | 1 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 18       | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 1 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 16<br>14 | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 1 | 0       | 0  | 1  | 1       | 1  | X    | X    | X             |

| 12       | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 1 | 0       | 0  | 1  | 1       | 1  | X    | X    | X             |

| 10       | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 1       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 8        | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 1       | 0  | 1  | 1       | 1  | X    | X    | X             |

| 6        | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 1  | 1  | 1       | 1  | X    | X    | X             |

| 4        | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 0  | 1  | 1       | 1  | X    | X    | X             |

| 2        | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 0  | 1  | 1       | 0  | X    | X    | X             |

| 0        | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 0  | 1  | 0       | 1  | X    | X    | X             |

| -2       | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 0  | 1  | 0       | 0  | X    | X    | X             |

| -4       | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 0  | 0  | 1       | 1  | X    | X    | X             |

| -6       | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 0  | 0  | 1       | 0  | X    | X    | X             |

| -8       | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 0  | 0  | 0       | 1  | X    | X    | X             |

| -10      | 0     | 0 | 0       | 0 | 0 | 0       | 0 | 0 | 0       | 0  | 0  | 0       | 0  | X    | X    | X             |

| G/dB     |       |   |         |   |   |         |   | b | it      |    |    |         |    |      |      |               |

| LNA      | 1     | 2 | 3       | 4 | 5 | 6       | 7 | 8 | 9       | 10 | 11 | 12      | 13 | 14   | 15   | 16            |

| 15       | X     | X | X       | X | X | X       | X | X | X       | X  | X  | X       | X  | 1    | 1    | X             |

| -5       | X     | X | X       | X | X | X       | X | X | X       | X  | X  | X       | X  | 1    | 0    | X             |

1 = High, 0 = Low, X = don't care

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

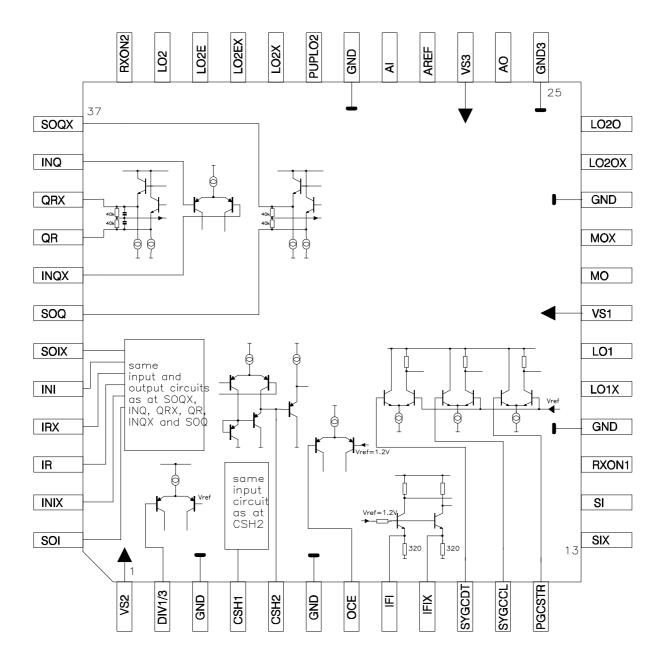

#### 5 Internal Input/Output Circuits

Internal I/O Circuits from Pin 1 to 12 and 37 to 48

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### Internal I/O Circuits from Pin 13 to 36

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### **6** Electrical Characteristics

#### 6.1 Absolute Maximum Ratings

The maximum ratings may not be exceeded under any circumstances, not even momentarily and individually, as permanent damage to the IC will result.

Ambient temperature  $T_A = -40^{\circ}$  to  $85^{\circ}C$

| #  | Parameter                                | Symbol            | Limit | t Values | Unit | Remarks                               |

|----|------------------------------------------|-------------------|-------|----------|------|---------------------------------------|

|    |                                          |                   | min.  | max.     |      |                                       |

| 1  | Supply Voltage                           | $v_{S}$           | -0.3  | 5.5      | V    |                                       |

| 2  | Input/Output Voltage                     | $v_{IO}$          | -0.3  | VS + 0.3 | V    | Except LNA                            |

|    | Output Voltage Aref                      |                   | 0     | 2.5      |      |                                       |

| 3  | Open Collector Output                    | V <sub>OC</sub>   |       |          | V    |                                       |

|    | Voltage MO,MOX                           |                   | 1.7   | VS + 0.3 |      |                                       |

|    | AO                                       |                   | 1.0   | VS + 0.3 |      |                                       |

| 4  | LNA Input Voltage                        | $v_{AI}$          | -3    |          | V    | RXON1=L                               |

| 5  | LNA Input Current                        | I <sub>AI</sub>   |       | 10       | mA   | RXON1=L                               |

| 6  | Differential Input Voltage               | $v_{I}$           |       | 2        | Vpp  |                                       |

|    | (any differential Input)                 |                   |       |          |      |                                       |

|    |                                          |                   |       |          |      |                                       |

| 7  | Junction Temperature                     | Tj                |       | 125      | °C   |                                       |

| 8  | Storage Temperature                      | $T_{\mathbf{S}}$  | -55   | 125      | °C   |                                       |

| 9  | Thermal Resistance (junction to ambient) | R <sub>thJA</sub> |       | 165      | K/W  |                                       |

|    | (                                        |                   |       |          |      |                                       |

| 10 | ESD-integrity                            | V <sub>ESD</sub>  | 1000  | 1000     | V    | according MIL-Std 883D, method 3015.7 |

The RF pins 20, 21, 26, 29, 32, 33, 34 and 35 are not protected against voltage stress > 300V (versus VS or GND).

The high frequency performance prohibits the use of adequate protective structures.

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### 6.2 Operational Range

Within the operational range the IC operates as described in the circuit description. The AC/DC characteristics limits are not guaranteed.

Supply voltage  $V_S = 2.7V$  to 4.5V; ambient temperature  $T_A = -40$  to 85°C; refer to test circuit 1.

| #    | Parameter                                                          | Symbol            | Limit | Values | Unit | Remarks                                                        |

|------|--------------------------------------------------------------------|-------------------|-------|--------|------|----------------------------------------------------------------|

|      |                                                                    |                   | min.  | max.   |      |                                                                |

| LN   | A                                                                  |                   |       |        |      |                                                                |

| 1    | AI Input Frequency                                                 | f <sub>SI</sub>   |       | 2500   | MHz  |                                                                |

| Firs | st mixer                                                           |                   |       |        |      |                                                                |

| 2    | SI/SIX Input Level                                                 | $P_{SI}$          |       | -11    | dBm  |                                                                |

| 3    | SI/SIX Input Frequency                                             | f <sub>SI</sub>   |       | 2500   | MHz  |                                                                |

| 4    | LO1/LO1X Input Level                                               | P <sub>LO1</sub>  | -11   | 3      | dBm  |                                                                |

| 5    | LO1/LO1X Input<br>Frequency                                        | fLO1              |       | 2500   | MHz  |                                                                |

| IF a | amplifier (PGC)                                                    |                   |       |        |      |                                                                |

| 6    | Intermediate Frequency                                             | IF                | 40    | 460    | MHz  |                                                                |

| 7    | IFI/IFIX Input Level                                               | $P_{IFI}$         |       | -12    | dBm  |                                                                |

| 8    | IFI/IFIX Input Frequency                                           | $f_{ m IFI}$      | 40    | 460    | MHz  |                                                                |

| VC   | O (second local oscillator)                                        |                   |       |        |      |                                                                |

| 9    | LO2 Input Level                                                    | P <sub>LO2</sub>  | -35   | 0      | dBm  |                                                                |

| 10   | LO2 Input Frequency                                                | f <sub>LO2</sub>  | 80    | 920    | MHz  | VCO as Amplifier                                               |

| 11   | VCO Frequency Range                                                | fvCO              | 80    | 920    | MHz  |                                                                |

| 12   | LO2O Output Level                                                  | P <sub>LO2O</sub> |       | 4      | dBm  | tuned for reso-nance,<br>measured with high<br>impedance probe |

| 13   | LO2O Output Frequency                                              | fLO2O             | 80    | 920    | MHz  | DIV1/3: L                                                      |

|      |                                                                    |                   | 26.7  | 307    | MHz  | DIV1/3: H                                                      |

| Der  | nodulator outputs                                                  |                   |       |        |      |                                                                |

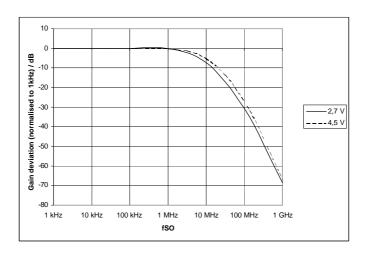

| 14   | IR/X,QR/X Outp. Bandw.                                             | B <sub>Out</sub>  | 0     | 9.5    | MHz  | 3dB roll off, see<br>AC/DC characteristics<br>page 21          |

| Pov  | ver down and logic inputs                                          |                   |       |        |      |                                                                |

| 15   | SYGCDT/SYGCCL/PGCSTR/<br>RXON1/RXON2/PUPLO2/OCE<br>Input Voltage-L | $v_{\rm L}$       | 0     | 0.5    | V    |                                                                |

| 16   | SYGCDT/SYGCCL/PGCSTR/<br>RXON1/RXON2/PUPLO2/OCE<br>Input Voltage-H | $v_{\mathrm{H}}$  | 2.0   | VS     | V    |                                                                |

| 17   | Input Capacitance                                                  | $c_{I}$           |       | 2      | pF   |                                                                |

Note:

Power levels are referred to impedance of 50 Ohms

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### 6.3 AC/DC Characteristics

AC/DC characteristics involve the spread of values guaranteed within the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

Supply voltage  $V_S = 2.7V$  to 4.5V; ambient temperature  $T_A = 25$ °C

| #   | Parameter      | Symbol           | L    | imit Valu | es    | Unit | Test Condition                  | Test    |

|-----|----------------|------------------|------|-----------|-------|------|---------------------------------|---------|

|     |                |                  | min. | typ.      | max.  |      |                                 | Circuit |

| Sup | ply currents   |                  |      |           |       |      |                                 |         |

| 1   | Supply current | $I_{\mathbf{S}}$ |      |           | 10    | μΑ   | RXON1/RXON2/PUPLO2<br>L / L / L |         |

|     |                |                  | 7.8  | 10.5      | 13.13 | mA   | H/L/L                           |         |

|     |                |                  | 8.4  | 11.3      | 14.1  | mA   | L/L/H                           |         |

|     |                |                  | 16   | 20        | 24    | mA   | L/H/L                           |         |

|     |                |                  | 32.5 | 42        | 51.3  | mA   | H/H/H                           |         |

#### LNA

Input signal AI

| шр  | ut signai Ai              |                 |          |            |          |      |                                    |    |

|-----|---------------------------|-----------------|----------|------------|----------|------|------------------------------------|----|

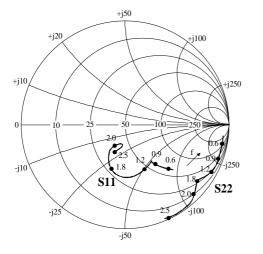

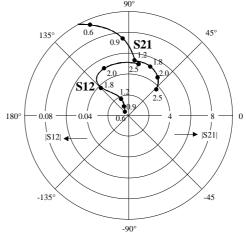

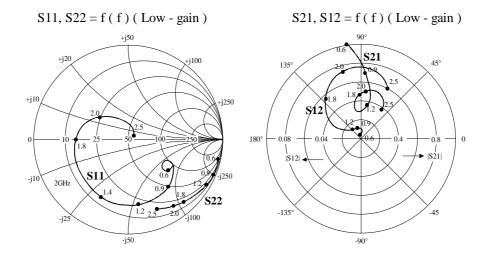

| 2   | Input Impedance           |                 | see dia  | grams 9.1  | and 9.2, |      |                                    | 2b |

|     |                           |                 | I        | pages 42-4 | 4        |      |                                    |    |

| 3   | Max. Input Level          | P <sub>AI</sub> |          |            |          | dBm  | 1dB Compr. at AO,                  | 1  |

|     |                           |                 | -23      | -20        |          |      | H, L gain 900MHz                   |    |

|     |                           |                 | -16      | -13        |          |      | H, L gain 1.8/1.9GHz               |    |

| 4   | Input Intercept Point     | IPIP3           | -7/-5/-5 | -4/-2/-2   | -        | dBm  | H gain, 0.9/1.8/1.9GHz             | 1  |

|     |                           |                 | -7/-5/-5 | -4/-2/-2   | 1/+1/+1  |      | L gain, 0.9/1.8/1.9GHz             |    |

|     |                           |                 |          |            | -        |      |                                    |    |

|     |                           |                 |          |            | 1/+1/+1  |      |                                    |    |

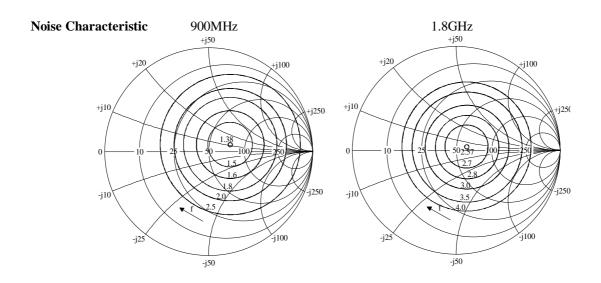

| 5   | Noise Figure              | $N_{AI}$        |          | 1.5        | 2.5      | dB   | f <sub>RF</sub> =900MHz;H gain     | 1  |

|     | (Values with              | $N_{AI}$        |          | 3          | 3.5      | dB   | f <sub>RF</sub> =1.8/1.9GHz;H gain |    |

|     | matching for 900          | $N_{AI}$        |          | 8          | 9        | dB   | f <sub>RF</sub> =900MHz;L gain     |    |

|     | MHz see design hints 9.1, | $N_{AI}$        |          | 9          | 10       | dB   | f <sub>RF</sub> =1.8/1.9GHz;L gain |    |

|     | page 39)                  |                 |          |            |          |      |                                    |    |

| 5.1 | Temp. coefficient         | T <sub>C</sub>  |          | 0.006      |          | dB/K | see appl. circuit page 35          |    |

**Output signal AO**

| 6   | Output Impedance  |                  | see dia | grams 9.1  | and 9.2, |      |                              | 2b |

|-----|-------------------|------------------|---------|------------|----------|------|------------------------------|----|

|     |                   |                  | Ī       | pages 42-4 | 4        |      |                              |    |

| 7   | Output collector  | I <sub>AO</sub>  |         | 5          |          | mA   | H gain                       |    |

|     | current           |                  |         | 0.5        |          | mA   | L gain                       |    |

| 8   | Gain from Signal  | G <sub>LNA</sub> |         |            |          |      | f <sub>RF</sub> =900MHz,     | 1  |

|     | Input             |                  | 15      | 17         | 19       | dB   | H gain                       |    |

|     | Without matching. |                  | -5      | -3         | -1       | dB   | L gain                       |    |

|     |                   |                  |         |            |          |      | f <sub>RF</sub> =1.8/1.9GHz, |    |

|     |                   |                  | 10.5    | 13.5       | 16.5     | dB   | H gain                       |    |

|     |                   |                  | -9.5    | -6.5       | -3.5     | dB   | L gain                       |    |

| 8.1 | Temp. coefficient | T <sub>C</sub>   |         | -0.01      |          | dB/K | see appl. circuit page 35    |    |

| 9   | Gain step         | ΔG               | 19      | 20         | 21       | dB   |                              |    |

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

Supply voltage  $V_{\mbox{\scriptsize S}}=2.7\mbox{\scriptsize V}$  to 4.5V; ambient temperature  $T_{\mbox{\scriptsize A}}=25\mbox{\scriptsize ^{\circ}C}$

| # | Parameter | Symbol | Limit Values |      |      | Unit | <b>Test Condition</b> | Test    |

|---|-----------|--------|--------------|------|------|------|-----------------------|---------|

|   |           |        | min.         | typ. | max. |      |                       | Circuit |

#### First mixer

Input SI/SIX

| Inp  | nput SI/SIX                |                   |         |                        |         |      |                                       |    |  |  |  |  |  |

|------|----------------------------|-------------------|---------|------------------------|---------|------|---------------------------------------|----|--|--|--|--|--|

| 10   | Input Impedance            |                   | see dia | gram 9.3, <sub>1</sub> | page 45 |      |                                       | 2a |  |  |  |  |  |

| 11   | Max. Input Level           | P <sub>SI</sub>   |         |                        |         | dBm  | 1dB Compr. at MO/X                    | 1  |  |  |  |  |  |

|      |                            |                   | -14     | -11                    |         |      | f <sub>SI</sub> =900MHz               |    |  |  |  |  |  |

|      |                            |                   | -10     | -7                     |         |      | f <sub>SI</sub> =1.8/1.9GHz           |    |  |  |  |  |  |

| 12   | Input Intercept Point      | P <sub>IPI3</sub> | 2       |                        |         | dBm  | f <sub>SI</sub> =900MHz               | 1  |  |  |  |  |  |

|      | 3rd order                  |                   | -3      |                        |         |      | f <sub>SI</sub> =1.8/1.9GHz           |    |  |  |  |  |  |

| 13   | Blocking Level             | PB                |         |                        |         | dBm  | 3dB Attenuation of                    | 1  |  |  |  |  |  |

|      | $\Delta f = 3 \text{ MHz}$ |                   |         |                        |         |      | wanted Signal at<br>MO/MOX            |    |  |  |  |  |  |

|      |                            |                   |         |                        |         |      |                                       |    |  |  |  |  |  |

|      |                            |                   | -11     | -8                     |         |      | f <sub>SI</sub> =900MHz               |    |  |  |  |  |  |

|      |                            |                   | -7      | -4                     |         |      | f <sub>SI</sub> =1.8/1.9GHz           |    |  |  |  |  |  |

| 14   | Input Frequency            | f <sub>SI</sub>   |         |                        | 2500    | MHz  |                                       | 1  |  |  |  |  |  |

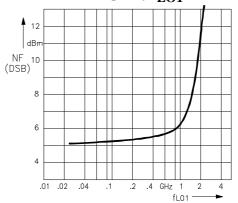

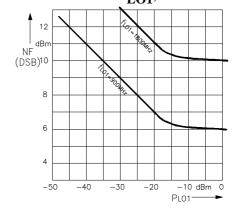

| 15   | Noise Figure               |                   |         |                        |         |      | IF = 246/336 MHz                      | 1  |  |  |  |  |  |

|      |                            | $N_{SI}$          |         |                        | 6/6.5   | dB   | DSB Noise, f <sub>c</sub> =900MHz     |    |  |  |  |  |  |

|      |                            |                   |         |                        | 10/10.5 | dB   | DSB Noise,                            |    |  |  |  |  |  |

|      |                            | $N_{SI}$          |         |                        |         |      | f <sub>c</sub> =1.8/1.9GHz            |    |  |  |  |  |  |

|      |                            | 51                |         |                        | 9/9.5   | dB   | SSB Noise, f <sub>c</sub> =900MHz     |    |  |  |  |  |  |

|      |                            |                   |         |                        | 13/13.5 | dB   | SSB Noise, f <sub>c</sub> =1.8/1.9GHz |    |  |  |  |  |  |

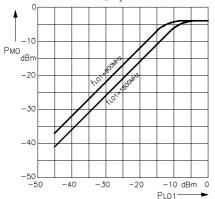

|      |                            |                   |         |                        |         |      | see diagrams 2, 4, page 39            |    |  |  |  |  |  |

| 15.1 | Temp. coefficient          | $T_{\mathbf{C}}$  |         | 0.01                   |         | dB/K |                                       |    |  |  |  |  |  |

Output MO/MOX (open collector)

| 16   | Output Impedance                  |                     | see dia | gram 9.5, <sub>I</sub> | page 47 |      |                                                                                                                 | 2c |

|------|-----------------------------------|---------------------|---------|------------------------|---------|------|-----------------------------------------------------------------------------------------------------------------|----|

| 17   | Total Output Collector<br>Current | $I_{\text{MO+MOX}}$ |         | 4                      |         | mA   |                                                                                                                 | 1  |

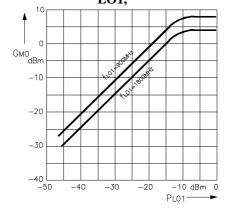

| 18   | Power Gain from<br>Signal Input   | G <sub>MO</sub>     | 11      | 14                     | 17      | dB   | f <sub>MO</sub> =40MHz,<br>f <sub>RF</sub> =900MHz                                                              |    |

|      |                                   |                     | 7       | 10                     | 13      | dB   | $\begin{array}{c} f_{\hbox{MO}}\!\!=\!\!40 \hbox{MHz}, \\ f_{\hbox{RF}}\!\!=\!\!1.8/1.9 \hbox{GHz} \end{array}$ |    |

|      |                                   |                     | 5       | 8                      | 11      | dB   | f <sub>MO</sub> =246MHz,<br>f <sub>SI</sub> =900MHz, *                                                          | 1  |

|      |                                   |                     | 2       | 4                      | 6       | dB   | f <sub>MO</sub> =246MHz,<br>f <sub>SI</sub> =1.8/1.9GHz, *                                                      |    |

|      |                                   |                     |         |                        |         |      | see diagram 3, page 39                                                                                          | 1  |

| 18.1 | Temp. coefficient                 | T <sub>C</sub>      |         | -0.015                 |         | dB/K |                                                                                                                 |    |

| 19   | Output Frequency IF               | $f_{ m IF}$         | 40      | 246                    | 460     | MHz  |                                                                                                                 | 1  |

<sup>\*</sup> tank circuit at MO/MOX matched to output / tuned for resonance

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

Supply voltage  $V_{\mbox{\scriptsize S}}=2.7\mbox{\scriptsize V}$  to 4.5V; ambient temperature  $T_{\mbox{\scriptsize A}}=25\mbox{\scriptsize ^{\circ}C}$

| #    | Parameter              | Symbol              | I          | Limit Valu | es      | Unit | Test Condition                                      | Test    |

|------|------------------------|---------------------|------------|------------|---------|------|-----------------------------------------------------|---------|

|      |                        |                     | min.       | typ.       | max.    |      |                                                     | Circuit |

| Inp  | out LO1/LO1X (first m  | ixer local os       | scillator) |            |         |      |                                                     |         |

| 20   | Input Impedance        |                     | see dia    | ngram 9.4, | page 46 |      |                                                     | 2a      |

| 21   | Input Level            | P <sub>LO1</sub>    | -11        |            | 3       | dBm  | see diagram 1, page                                 | 1       |

|      |                        | $v_{LO1}$           | 177        |            | 890     | mVpp | 39                                                  | 1       |

| 22   | Input Frequency        | f <sub>LO1</sub>    |            |            | 2500    | MHz  |                                                     | 1       |

| Isol | ation of first mixer   |                     |            |            |         |      |                                                     |         |

| 23   | From SI to MO          | A <sub>SI-MO</sub>  |            | 30         |         | dB   | f <sub>SI</sub> =945MHz; f <sub>LO1</sub> =900MHz   | 1       |

| 24   | SI to LO1              | A <sub>SI-LO1</sub> |            | 60         |         | dB   | п                                                   | 1       |

| 25   | LO1 to MO              | A <sub>LO1-MO</sub> |            | 50         |         | dB   | "                                                   | 1       |

| 26   | LO1 to SI              | A <sub>LO1-SI</sub> |            | 60         |         | dB   | "                                                   | 1       |

| 27   | MO to SI               | A <sub>MO-SI</sub>  |            | 50         |         | dB   | "                                                   | 1       |

| 28   | MO to LO1              | A <sub>MO-LO1</sub> |            | 65         |         | dB   | "                                                   | 1       |

| 29   | From SI to MO          | A <sub>SI-MO</sub>  |            | 24         |         | dB   | f <sub>SI</sub> =1.845GHz; f <sub>LO1</sub> =1.8GHz | 1       |

| 30   | SI to LO1              | A <sub>SI-LO1</sub> |            | 54         |         | dB   | п                                                   | 1       |

| 31   | LO1 to MO              | A <sub>LO1-MO</sub> |            | 44         |         | dB   | "                                                   | 1       |

| 32   | LO1 to SI              | A <sub>LO1-SI</sub> |            | 54         |         | dB   | "                                                   | 1       |

| 33   | MO to SI               | A <sub>MO-SI</sub>  |            | 44         |         | dB   | п                                                   | 1       |

| 34   | MO to LO1              | A <sub>MO-LO1</sub> |            | 59         |         | dB   | "                                                   | 1       |

| Isol | ation between first Mi | xer Output          | to IF Inp  | ut         |         |      |                                                     |         |

| 35   | From MO to IFI         | A <sub>MO-IFI</sub> | 60         |            |         | dB   | IF = 40 460 MHz                                     | 1       |

| Isol | ation between LNA O    | utput to firs       | t Mixer I  | nput       |         |      |                                                     |         |

| 36   | From AO to SI          | A <sub>AO-SI</sub>  |            | 45         |         | dB   | f <sub>RF</sub> =900 MHz                            | 1       |

| 37   | From AO to SI          | A <sub>AO-SI</sub>  |            | 45         |         | dB   | f <sub>RF</sub> =1.8/1.9GHz                         | 1       |

|      |                        |                     |            | •          | •       | •    | •                                                   | •       |

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

Supply voltage  $V_S = 2.7V$  to 4.5V; ambient temperature  $T_A = 25$ °C

| # | Parameter | Symbol | L    | imit Valu | es   | Unit | Test Condition | Test    |

|---|-----------|--------|------|-----------|------|------|----------------|---------|

|   |           |        | min. | typ.      | max. |      |                | Circuit |

#### IF amplifier (PGC) input IFI/IFIX

| 38 | Input Impedance       |                  | see dia | gram 9.6, j | page 48 |      |                  | 2a |

|----|-----------------------|------------------|---------|-------------|---------|------|------------------|----|

|    |                       |                  |         |             |         |      |                  |    |

| 39 | Max. Input Level      | $P_{IFI}$        |         | -12         |         | dBm  | 1dB Compr.       | 1  |

|    |                       | $v_{IFI}$        |         | 155         |         | mVpp | PGC Gain: -10dB  | 1  |

|    |                       |                  |         |             |         |      | see diagram 5.1, |    |

|    |                       |                  |         |             |         |      | page 39          |    |

| 40 | Input Intercept Point | P <sub>IPI</sub> | see dia | gram 5.1, j | page 39 |      |                  | 1  |

| 41 | Input Frequency       | $f_{SI}$         | 40      | 246         | 460     | MHz  |                  | 1  |

| 42 | Noise Figure          | N <sub>SI</sub>  |         | 6           | 7       | dB   | PGC Gain: 70dB   | 1  |

|    |                       |                  |         |             |         |      | see diagram 5.1, |    |

|    |                       |                  |         |             |         |      | page 39          |    |

#### VCO (second local oscillator LO2)

#### Input LO2/LO2X (when used as amplifier for an external VCO)

| 43 | Input Impedance |                  | see dia | see diagram 9.7, page 49 |     |      |                  | 2b |

|----|-----------------|------------------|---------|--------------------------|-----|------|------------------|----|

|    |                 |                  |         |                          |     |      |                  |    |

| 44 | Input Level     | P <sub>LO2</sub> | -20     |                          | 0   | dBm  | into 50 Ohms     | 1  |

|    |                 | $v_{LO2}$        | 63      |                          | 630 | mVpp | application hint | 1  |

| 45 | Input Frequency | f <sub>LO2</sub> | 80      |                          | 920 | MHz  |                  | 1  |

#### Voltage controlled oscillator VCO (LO2)

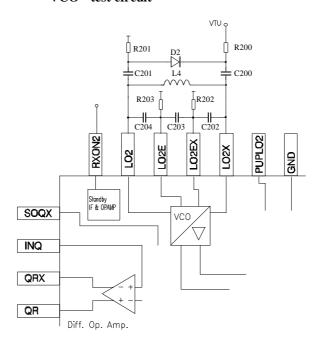

| 46 | VCO Frequency range | f <sub>VCO</sub> | 80 | 492 | 920 | MHz | *                | 1.1 |

|----|---------------------|------------------|----|-----|-----|-----|------------------|-----|

| 47 | VCO tuning range    | $\Delta f_{VCO}$ |    | 32  |     | MHz | Vt = 0.6 2.3V ** | 1.1 |

<sup>\*</sup> depending on external tuning circuit

<sup>\*\*</sup> Test circuit 1.1 (f<sub>VCO</sub>= 492MHz), page 26 and page 36

Supply voltage  $V_{\mbox{\scriptsize S}}=2.7\mbox{\scriptsize V}$  to 4.5V; ambient temperature  $T_{\mbox{\scriptsize A}}=25\mbox{\scriptsize ^{\circ}C}$

| # | Parameter | Symbol | Limit Values |      |      | Unit | Test Condition | Test    |

|---|-----------|--------|--------------|------|------|------|----------------|---------|

|   |           |        | min.         | typ. | max. |      |                | Circuit |

#### Output LO2O/LO2OX

| 48 | Output Resistance (diff.)  | R <sub>LO2O</sub> |      | 1   |      | kOhms  |                                                                  |     |

|----|----------------------------|-------------------|------|-----|------|--------|------------------------------------------------------------------|-----|

| 49 | Output Capacitance (diff.) | C <sub>LO2O</sub> |      | 1   |      | pF     | Parallel to R <sub>LO2O</sub>                                    |     |

| 50 | Output Level               | P <sub>LO2O</sub> |      | -15 |      | dBm    | tuned for resonance                                              | 1   |

| 51 | Output Level               | P <sub>LO2O</sub> |      | 4   |      | dBm    | tuned for resonance,                                             |     |

|    |                            |                   |      |     |      |        | measured with high<br>impedance probe<br>(differential)          |     |

| 52 | Output Frequency           | f <sub>LO2O</sub> | 80   | 492 | 920  | MHz    | DIV1/3: L                                                        |     |

| 53 | Output Frequency           | fLO2O             | 26.7 | 164 | 307  | MHz    | DIV1/3: H                                                        |     |

| 54 | SSB noise referenced       | L(fm)             |      |     | -121 | dBc/Hz | fm=600 kHz                                                       | 1.1 |

|    |                            |                   |      |     | -126 |        | fm=1.8 MHz                                                       |     |

|    |                            |                   |      |     | -131 |        | fm=6 MHz;                                                        |     |

|    |                            |                   |      |     |      |        | using high Q coil,<br>Q=60-70 for oscillator<br>tank circuit. ** |     |

| 55 | power on delay             | t <sub>po</sub>   |      | 0.3 |      | μs     |                                                                  |     |

<sup>\*\*</sup> Test circuit 1.1 ( $f_{VCO}$ = 492MHz), page 26 and page 36

Supply voltage  $V_{\mbox{\scriptsize S}}=2.7\mbox{\scriptsize V}$  to 4.5V; ambient temperature  $T_{\mbox{\scriptsize A}}=25\mbox{\scriptsize ^{\circ}C}$

| # | Parameter | Symbol | Limit Values |      |      | Unit | Test Condition | Test    |

|---|-----------|--------|--------------|------|------|------|----------------|---------|

|   |           |        | min.         | typ. | max. |      |                | Circuit |

#### IF and BB chain: PGC==>Demodulator

Outputs SOI/SOIX, SOQ/SOQX

| 56 | Output Resistance                  | R <sub>OUT</sub>   |     | 75   |      | Ohms |                                                                                          |   |

|----|------------------------------------|--------------------|-----|------|------|------|------------------------------------------------------------------------------------------|---|

|    | (diff.)                            |                    |     |      |      |      |                                                                                          |   |

| 57 | Output Capacitance                 | C <sub>OUT</sub>   |     | 1    |      | pF   |                                                                                          |   |

|    | (diff.)                            |                    |     |      |      |      |                                                                                          |   |

| 58 | Frequency roll off                 | fout               | 3.0 | 5.0  | 7.0  | MHz  | VCC = 2.7V                                                                               |   |

|    |                                    |                    | 3.6 | 6.0  | 8.4  | MHz  | VCC = 3.6V                                                                               |   |

|    |                                    |                    | 4.1 | 6.8  | 9.5  | MHz  | VCC = 4.5V                                                                               |   |

|    |                                    |                    |     |      |      |      | see diagram 6 page 41<br>and design hint 9.4<br>page 38                                  |   |

| 59 | DC Output Level                    | V <sub>OUTDC</sub> |     | 0.95 |      | V    |                                                                                          | 1 |

| 60 | Diff. Output Offset                | V <sub>SO/X</sub>  |     | ±30  | ±100 | mV   | without offset comp.                                                                     | 1 |

|    | Voltage                            |                    |     |      |      |      | OCE = Low                                                                                |   |

| 61 | AC Voltage Swing (diff.)           | V <sub>OUTAC</sub> |     |      | 2.5  | Vpp  | differential                                                                             | 1 |

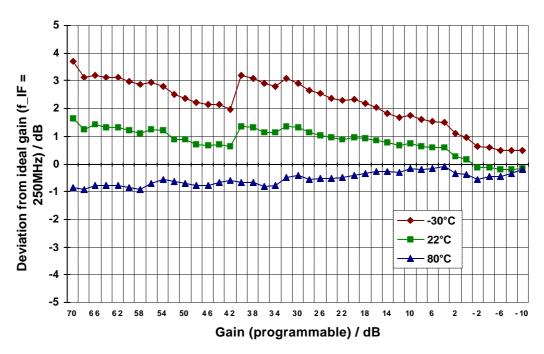

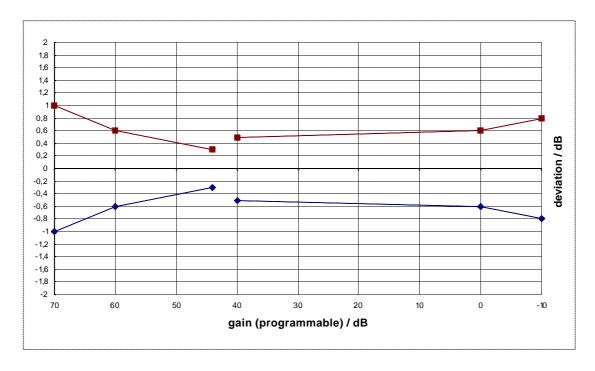

| 62 | Voltage Gain from IF to I/Q-       | G <sub>OUT</sub>   | 67  | 70   | 73   | dB   | Gmax; IF = 246MHz                                                                        | 1 |

|    | BB Output<br>(IF: 225 / 246MHz)    |                    | 64  | 67   | 70   | dB   | Gmax; IF = 336MHz                                                                        | 1 |

|    | gPGC+Demodulator                   |                    | 59  | 62   | 65   | dB   | Gmax; IF = 435MHz                                                                        |   |

|    | SPGC+Demodulator                   |                    | -13 | -10  | -7   | dB   | Gmin; IF = 246MHz                                                                        |   |

|    |                                    |                    | -16 | -13  | -10  | dB   | Gmin; IF = 336MHz                                                                        |   |

|    |                                    |                    | -21 | -18  | -15  | dB   | Gmin; IF = 435MHz                                                                        |   |

|    |                                    |                    |     |      |      |      |                                                                                          |   |

|    |                                    |                    |     |      |      |      | PGC: see table 4 page 11 and<br>diagram 5.1, page 39<br>PGC controlled via 3 wire<br>bus |   |

| 63 | PGC Gain step                      | Gstep              |     | 2    |      | dB   |                                                                                          | 1 |

| 64 | I - Q Phase deviation              | ΔφΙQ               |     |      | ±3   | deg  | see                                                                                      | 1 |

|    |                                    |                    |     |      |      |      | design hint 8.2, page 36                                                                 |   |

|    |                                    |                    |     |      |      |      | design hint 8.4, page 38                                                                 |   |

| 65 | Amplitude mismatch $\Delta V(I/Q)$ | ΔVI/Q              |     |      | 1.7  | dB   |                                                                                          | 1 |

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

$0v \le V_{in} \le VS$

1

1/1.2

1/1.2

1/1.2

#### AC/DC Characteristics (cont'd)

69 Input Current

70 Clock frequency

Supply voltage  $V_S = 2.7V$  to 4.5V; ambient temperature  $T_A = 25$ °C

| #   | Parameter           | Symbol      | Limit Values |      |      | Unit | Test Condition | Test    |

|-----|---------------------|-------------|--------------|------|------|------|----------------|---------|

|     |                     |             | min.         | typ. | max. |      |                | Circuit |

| 3 W | re bus inputs SYGCD | T/SYGCC     | L/PGCST      | 'R   |      |      |                |         |

| 66  | Input Voltage L     | $v_{L}$     | 0            |      | 0.5  | V    |                | 1       |

| 67  | Input Voltage H     | $v_{\rm H}$ | 2.0          |      | VS   | V    |                | 1       |

| 68  | Reference Voltage   | Vcomp       |              | 1.75 |      | V    |                | 1/1.2   |

μΑ

MHz

ns

ns

# 71 Set - up time (start) TSUSTA 30 72 H pulse width (clock) THIGH 20 73 L pulse width (clock) TLOW 20

-I<sub>in</sub>

fSYGCCL

# 73 L pulse width (clock) TLOW 20 ns 1/1.2 74 Set - up time (data transfer) TSUDAT 20 ns 1/1.2 75 Hold time (data transfer) THDDAT 20 ns 1/1.2

3.25

13

#### TR20 40 1/1.2 76 Rise time ns TF 1/1.2 77 Fall time 20 35 ns TSUSTO 1/1.2 Set - up time (stop) 30 ns Setting Time 200 Setting of gain after 1 ns t<sub>set</sub> programming Start time 1 80 200 Programming start $t_{start}$ ns time after power up

#### Power-down and control inputs RXON1, RXON2, PUPLO2,OCE

| 81 | Input Voltage L   | $v_{\rm L}$     | 0   | 0.5 | V  |                            | 1 |

|----|-------------------|-----------------|-----|-----|----|----------------------------|---|

| 82 | Input Voltage H   | $v_{H}$         | 2.0 | VS  | V  |                            | 1 |

| 83 | Input Current L   | $I_{L}$         |     | 2.5 | μΑ | 0<=V <sub>PDL</sub> <=0.5V | 1 |

| 84 | Input Current H   | I <sub>H</sub>  |     | 25  | μΑ | $2.0V \le V_{PDH} \le VS$  | 1 |

| 85 | Input capacitance | C <sub>in</sub> |     | 2   | pF |                            |   |

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

Supply voltage  $V_S$  = 2.7V to 4.5V; ambient temperature  $T_A$  = 25°C

| #  | Parameter                               | Symbol             | L         | imit Valu | es   | Unit  | Test Condition                                                             | Test    |

|----|-----------------------------------------|--------------------|-----------|-----------|------|-------|----------------------------------------------------------------------------|---------|

|    |                                         |                    | min.      | typ.      | max. |       |                                                                            | Circuit |

|    | Differential Operation                  | nal Amplif         | ier (open | loop)     |      |       |                                                                            |         |

| 86 | Slew Rate                               | SR                 |           | 2.6       |      | V/µs  |                                                                            |         |

| 87 | Gain-Bandwidth Prod.                    | GBW                |           | 12        |      | MHz   |                                                                            |         |

| 88 | Voltage Gain                            | A <sub>Vo</sub>    |           | 60        |      | dB    |                                                                            |         |

| 89 | Phase margin                            |                    |           | 60        |      | degr. |                                                                            |         |

| 90 | Gain margin                             | $A_{\mathbf{R}}$   |           | 14        |      | dB    |                                                                            |         |

| 91 | Common-Mode<br>Rejection                | CMR                |           | 70        |      | dB    |                                                                            |         |

| 92 | Offset Voltage                          | V <sub>OFF</sub>   |           | 1         |      | mV    | at input INQ/X,INI/X                                                       |         |

| 93 | Output Voltage<br>(IR/X,QR/X)           | V <sub>OUT</sub>   |           |           | 2.5  | Vpp   | differential                                                               |         |

| 94 | Diff. Output Offset<br>Volt.(IR/X,QR/X) | V <sub>OUT/X</sub> |           |           | 1    | mV/ms | with offset<br>compensation ( S&H )<br>over the whole<br>temperature range | 1       |

| 95 | DC Output Level (IR/X,QR/X)             | V <sub>outDC</sub> |           | 0.95      |      | V     | depends on SO-DC<br>output level                                           | 1       |

| 96 | Output Resistor                         | R(out/outx)        |           | 250       |      | Ω     | differential                                                               |         |

Note: The operational amplifiers do not offer wideband capability (see also design hint 8.3 page 37 and design hint 8.4 page 38).

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

Supply voltage  $V_S$  = 2.7V to 4.5V; ambient temperature  $T_A$  = 25°C

| Parameter            | Symbol                       | Limit Values                         |                                             | Unit                                            | Test Condition                                                    | Test                                                          |                                                          |  |  |  |

|----------------------|------------------------------|--------------------------------------|---------------------------------------------|-------------------------------------------------|-------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------------|--|--|--|

|                      |                              | min.                                 | typ.                                        | max.                                            |                                                                   |                                                               | Circuit                                                  |  |  |  |

| Sample and Hold      |                              |                                      |                                             |                                                 |                                                                   |                                                               |                                                          |  |  |  |

| Voltage drift        | V <sub>dritt</sub>           |                                      |                                             | 1                                               | mV/ms                                                             | (CSH1/2 = 47nF)                                               | 1                                                        |  |  |  |

| at output IR/X, QR/X |                              |                                      |                                             |                                                 |                                                                   | during hold time,                                             |                                                          |  |  |  |

|                      | nple and Hold  Voltage drift | nple and Hold  Voltage drift  Vdritt | min.  Pople and Hold  Voltage drift  Vdritt | min. typ.  nple and Hold  Voltage drift  Vdritt | min. typ. max.  nple and Hold  Voltage drift V <sub>dritt</sub> 1 | min. typ. max.  pple and Hold  Voltage drift  Vdritt  1 mV/ms | $\begin{tabular}{ c c c c c c c c c c c c c c c c c c c$ |  |  |  |

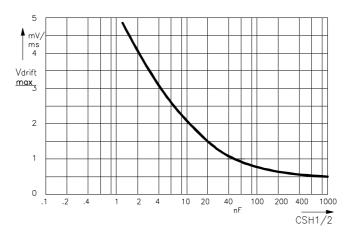

| 97  | Voltage drift                             | V <sub>dritt</sub>  |    | 1   | mV/ms | (CSH1/2 = 47nF)                                                                    | 1             |

|-----|-------------------------------------------|---------------------|----|-----|-------|------------------------------------------------------------------------------------|---------------|

|     | at output IR/X, QR/X                      |                     |    |     |       | during hold time,                                                                  |               |

|     |                                           |                     |    |     |       | dep. of capac. C, for<br>the whole temperature<br>range, see diagram 7,<br>page 41 |               |

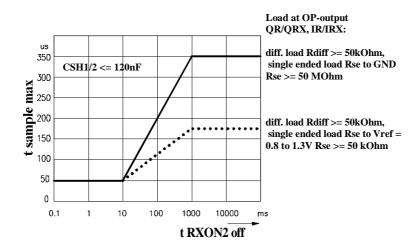

| 98  | Min. Sample time                          | t <sub>sample</sub> |    | 50  | μs    | CSH1/2 ≤ 120nF                                                                     | 1             |

|     |                                           |                     |    |     |       | t PD2 off ≤ 10ms                                                                   |               |

|     |                                           |                     |    | 350 | μs    | CSH1/2 ≤ 120nF                                                                     |               |

|     |                                           |                     |    |     |       | t PD2 off ≥ 10ms                                                                   |               |

|     |                                           |                     |    |     |       | see diagram 8, page 41                                                             |               |

| 99  | Diff. Output Offset<br>Volt. at OP-output | V <sub>OPdiff</sub> |    | 5   | mV    | during sample time<br>and the beginning of<br>hold time                            | 1             |

| 100 | Diff. load at Op-out                      | Rl <sub>diff</sub>  | 10 |     | kΩ    |                                                                                    | see           |

|     | Single ended load to GND                  | Rl <sub>se</sub>    | 50 |     | ΜΩ    |                                                                                    | diagram<br>8, |

|     | Single ended load to $V_{ref}$            | Rl <sub>se</sub>    | 50 |     | kΩ    | $0.8V \le V_{\text{ref}} \le 1.3V$                                                 | page 41       |

Note: The operational amplifiers do not offer wideband capability. In wideband applications,the Sample and Hold therefore must be deactivated by setting the OCE input to L (see also design hint 8.4 page 38).

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### 7 Test Circuits

#### 7.1 Test Circuit 1

Note:

Resistors R2 - R7, R8 - R13 and capacitors C27 - C31 are not necessary in a wideband application (see also design hint 8.4).

However, the test board offers the possibility to mount these components (e.g. for a low pass filter in small band applications).

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### 7.2 Test Circuit 1.1 (VCO as oscillator)

#### 7.3 Test Circuit 1.2 (3-wire-bus timing)

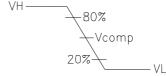

TSUSTA Set - up time ( start )

THIGH H pulse width ( clock )

TLOW L pulse width ( clock )

TSUDAT Set - up time ( data transfer )

THDDAT Hold time (data transfer )

TR Rise time TF Fall time

TSUSTO Set - up time ( stop )

Rise and Fall time to 20% and 80% values All other times referenced to Vcomp

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

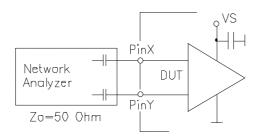

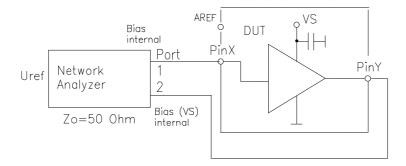

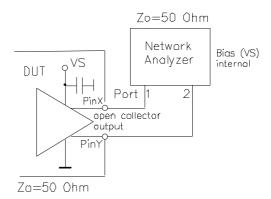

#### 7.4 Test Circuit 2

#### 7.4.1 Test Circuit 2a

#### 7.4.2 Test circuit 2b

#### 7.4.3 Test Circuit 2c

The S parameters are tested at the indicated frequency and the equivalent parallel or series circuit can be calculated on this base.

| Test point          | Test Circuit | Test Frequency / MHz | Pin X | Pin Y |

|---------------------|--------------|----------------------|-------|-------|

| LO1-Input Impedance | 2a           | 2002000              | 17    | 18    |

| SI-Input Impedance  | 2a           | 2002000              | 13    | 14    |

| MO-Output Impedance | 2c           | 10600                | 20    | 21    |

| IFI-Input Impedance | 2a           | 10600                | 8     | 9     |

| LO2-Input impedance | 2a           | 10 1000              | 32    | 35    |

| LNA-I/O impedance   | 2b           | 200 2000             | 29    | 26    |

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

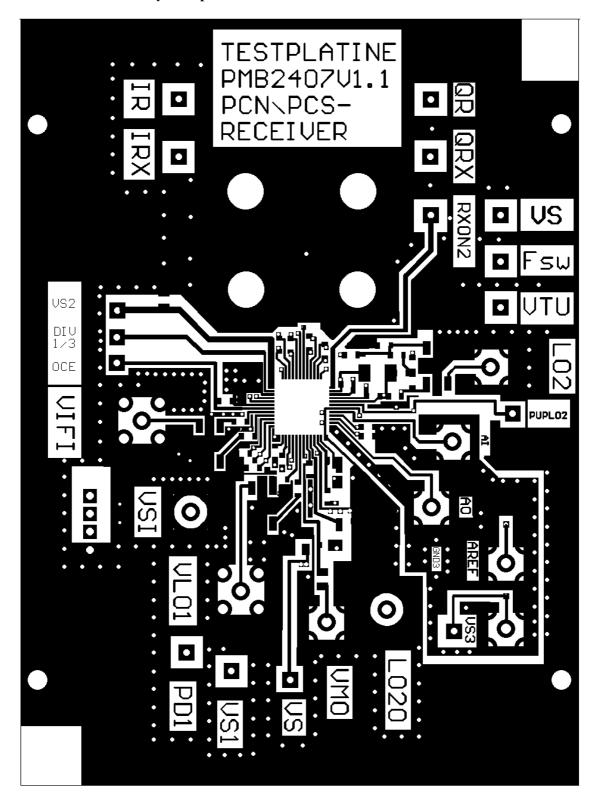

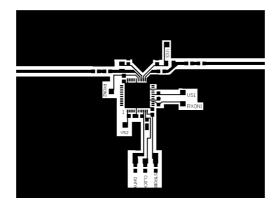

- 7.5 Test Board (Test boards PMB2407 V1.1 are available on request, also usable for PMB2408 V1.1)

- 7.5.1 Test Board: Layout Top

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

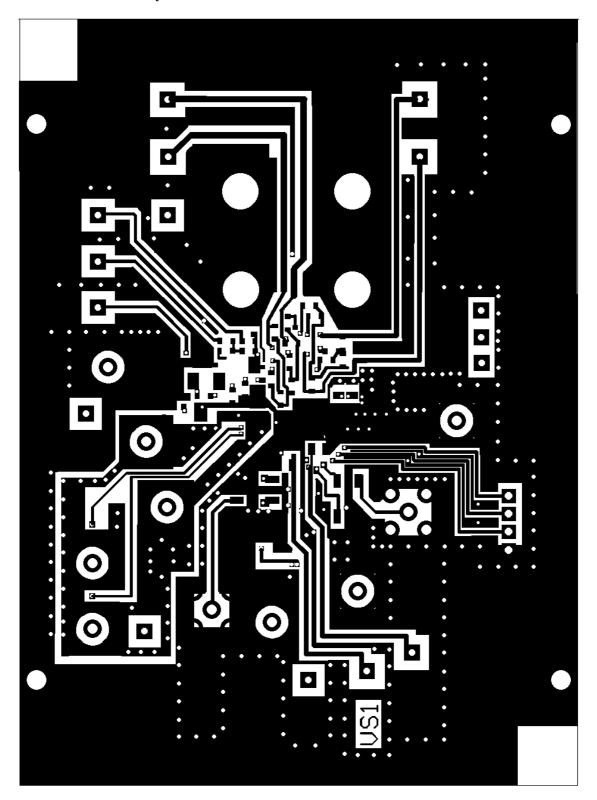

7.5.2 Test Board: Layout Bottom

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

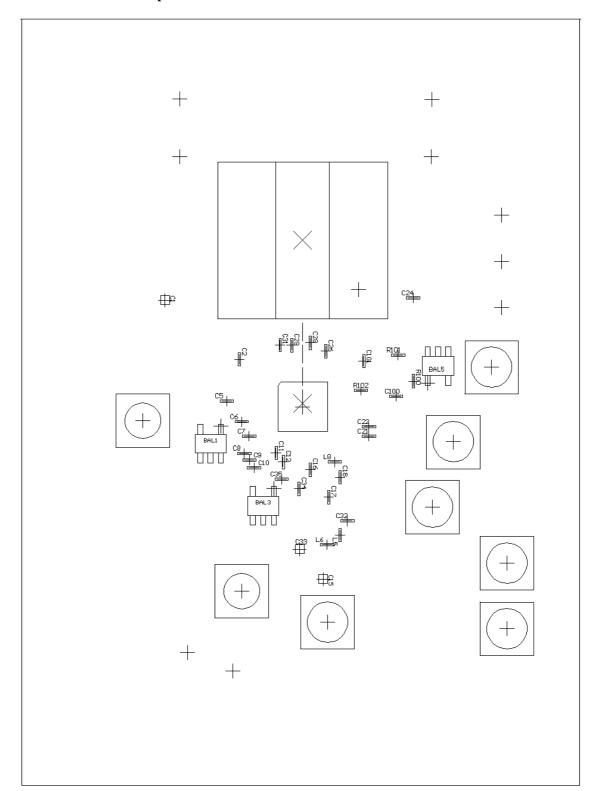

#### 7.5.3 Test Board: Top Place for Test Circuit 1

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

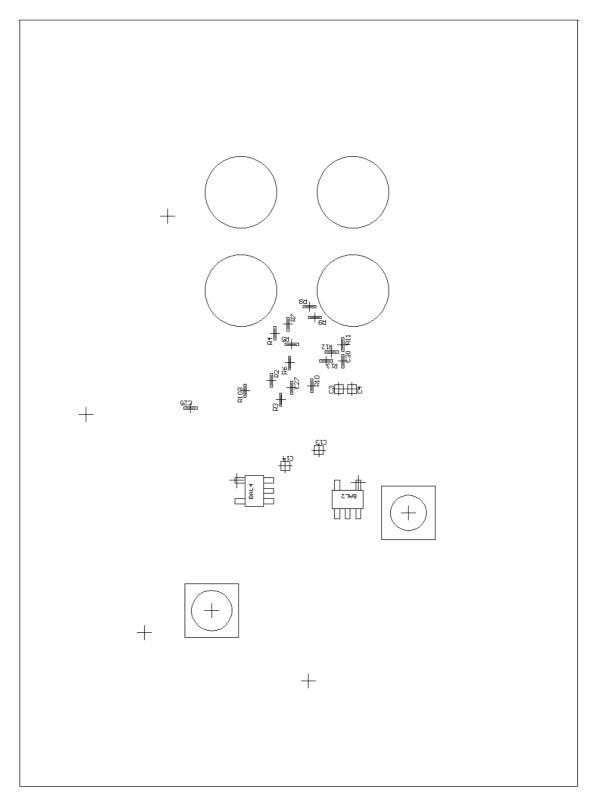

#### 7.5.4 Test Board: Bottom Place for Test Circuit 1

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### 7.5.5 Test Board: Top Place for Test Circuit 1.1

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### 7.5.6 Test Board: Bottom Place for Test Circuit 1.1

The reproduction, transmission or use of this document is not permitted without expresswritten authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved

#### 7.5.7 **Test Circuit 1 List of Components:**

#### **Component values**