# Wireless Components

Transmitter PLL (Up-Conversion Loop Modulator) PMB 2251 Version 1.3

Specification August 1999

preliminary

| Revision History: Current Version: 08.99 |                                 |                                              |  |

|------------------------------------------|---------------------------------|----------------------------------------------|--|

| Previous Vers                            | ion:Data Sheet                  |                                              |  |

| Page<br>(in previous<br>Version)         | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |  |

|                                          |                                 |                                              |  |

|                                          |                                 |                                              |  |

ABM<sup>®</sup>, AOP<sup>®</sup>, ARCOFI<sup>®</sup>, ARCOFI<sup>®</sup>-BA, ARCOFI<sup>®</sup>-SP, DigiTape<sup>®</sup>, EPIC<sup>®</sup>-1, EPIC<sup>®</sup>-S, ELIC<sup>®</sup>, FALC<sup>®</sup>54, FALC<sup>®</sup>56, FALC<sup>®</sup>-E1, FALC<sup>®</sup>-LH, IDEC<sup>®</sup>, IOM<sup>®</sup>, IOM<sup>®</sup>-1, IOM<sup>®</sup>-2, IPAT<sup>®</sup>-2, ISAC<sup>®</sup>-P, ISAC<sup>®</sup>-S, ISAC<sup>®</sup>-S TE, ISAC<sup>®</sup>-P TE, ITAC<sup>®</sup>, IWE<sup>®</sup>, MUSAC<sup>®</sup>-A, OCTAT<sup>®</sup>-P, QUAT<sup>®</sup>-S, SICOFI<sup>®</sup>, SICOFI<sup>®</sup>-2, SICOFI<sup>®</sup>-4, SICOFI<sup>®</sup>-4, SICOFI<sup>®</sup> are registered trademarks of Infineon Technologies AG.

ACE<sup>™</sup>, ASM<sup>™</sup>, ASP<sup>™</sup>, POTSWIRE<sup>™</sup>, QuadFALC<sup>™</sup>, SCOUT<sup>™</sup> are trademarks of Infineon Technologies AG.

Edition 03.99 Published by Infineon Technologies AG i. Gr., SC

#### Balanstraße 73,

81541 München

© Infineon Technologies AG i. Gr. 10.08.99. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that lifesupport device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

# **Product Info**

| General Description | The PMB 2251 is a transmitter PLL containing a modulator, a mixer, two programmable counters and a phase detector. The device is programmed via a three-wire bus.                                                                                                                                                                                                                                                                                                          | Package                                                                                                                                                                                                                                                                                                                          |  |  |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Features            | <ul> <li>Vector modulator operating from<br/>80 to 450MHz</li> <li>Integrated generation of<br/>orthogonal carriers</li> <li>Typ. 40dB carrier rejection,<br/>40dB SSB rejection,<br/>54dB IM3 supression</li> </ul>                                                                                                                                                                                                                                                       | TATATATAT                                                                                                                                                                                                                                                                                                                        |  |  |

|                     | <ul> <li>Double balanced Gilbert cell mixer         <ul> <li>single ended inputs and outputs</li> <li>LO- and RF input frequency<br/>range: 800MHz to 2GHz</li> <li>Output frequency range: DC to<br/>450MHz</li> </ul> </li> <li>Integrated modulation PLL         <ul> <li>Input Counters programmable<br/>from 1 to 8</li> <li>Charge pump with programmable<br/>current up to 4mA</li> <li>Separate charge pump suppy<br/>voltage (2.7 to 5.5V)</li> </ul> </li> </ul> | <ul> <li>-Phase/Frequency-sensitive phase detector <ul> <li>Operation at up to 150MHz</li> <li>-Linear transfer characteristi (no dead zone)</li> </ul> </li> <li>Serial data transfer via three-wire bus (Power-down modes programmable)</li> <li>Supply voltage 2.7 to 4.5V</li> <li>Temperature range -30° to 85°C</li> </ul> |  |  |

| Application         | <ul> <li>The PMB 2251 is intended for use in an up-conversion loop.</li> <li>The device has a wide frequency range and is suitable for mobile communication systems requiring a high modulation bandwidth and a low phase error.</li> </ul>                                                                                                                                                                                                                                | The device is part of the Infineon-<br>chipset for single- and multiband<br>mobile communication systems,<br>such as GSM, PCN and PCS.                                                                                                                                                                                           |  |  |

#### **Ordering Information**

| Туре          | Ordering Code | Package    |  |  |

|---------------|---------------|------------|--|--|

| PMB 2251 V1.3 |               | P-TSSOP-28 |  |  |

# Table of Contents

| 2Product Description2-2.1General Description2-2.2Application2-2.3Features2-2.4Package Outlines2-3Functional Description3-3.1Pin Configuration3-3.2Pin Definition and Function3-3.3Block Diagram3-                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.2       Application       2-         2.3       Features       2-         2.4       Package Outlines       2-         3       Functional Description       3-         3.1       Pin Configuration       3-         3.2       Pin Definition and Function       3-         3.3       Block Diagram       3- |

| 2.3       Features       2-         2.4       Package Outlines       2-         3       Functional Description       3-         3.1       Pin Configuration       3-         3.2       Pin Definition and Function       3-         3.3       Block Diagram       3-                                        |

| 2.4    Package Outlines    2-      3    Functional Description    3-      3.1    Pin Configuration    3-      3.2    Pin Definition and Function    3-      3.3    Block Diagram    3-                                                                                                                      |

| 3       Functional Description       3-         3.1       Pin Configuration       3-         3.2       Pin Definition and Function       3-         3.3       Block Diagram       3-                                                                                                                        |

| 3.1Pin Configuration3-3.2Pin Definition and Function3-3.3Block Diagram3-                                                                                                                                                                                                                                    |

| 3.2    Pin Definition and Function                                                                                                                                                                                                                                                                          |

| 3.3 Block Diagram                                                                                                                                                                                                                                                                                           |

| 5                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                                                             |

| 3.4 Circuit Description                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                             |

| 4 Applications                                                                                                                                                                                                                                                                                              |

| 4.1 Circuit Principle                                                                                                                                                                                                                                                                                       |

| 4.2 Intermediate Frequency                                                                                                                                                                                                                                                                                  |

| 4.3 Supply and Ground Pins                                                                                                                                                                                                                                                                                  |

| 4.4 Coupling Circuitry                                                                                                                                                                                                                                                                                      |

| 4.5 Loop Filter                                                                                                                                                                                                                                                                                             |

| 4.6 Other Filters                                                                                                                                                                                                                                                                                           |

| 4.7 Modulation Inputs                                                                                                                                                                                                                                                                                       |

| 4.8 Charge Pump                                                                                                                                                                                                                                                                                             |

| 4.9 Input/Output Impedances                                                                                                                                                                                                                                                                                 |

| <b>5 Reference</b>                                                                                                                                                                                                                                                                                          |

| 5.1 Electrical Data                                                                                                                                                                                                                                                                                         |

| 5.1.1 Absolute Maximum Ratings5-                                                                                                                                                                                                                                                                            |

| 5.1.2 Operating Range5-                                                                                                                                                                                                                                                                                     |

| 5.1.3 AC/DC Characteristics                                                                                                                                                                                                                                                                                 |

| 5.2 Bus Timing                                                                                                                                                                                                                                                                                              |

| 5.3 Programming Tables                                                                                                                                                                                                                                                                                      |

| 5.4 Typical Temperature Dependencies5-                                                                                                                                                                                                                                                                      |

| 5.5 Test Circuit 1                                                                                                                                                                                                                                                                                          |

#### Contents of this Chapter

| 2.1 | General Description | . 2-2 |

|-----|---------------------|-------|

| 2.2 | Application         | . 2-2 |

| 2.3 | Features            | . 2-2 |

| 2.4 | Package Outlines    | . 2-3 |

#### 2.1 General Description

The PMB 2251 is a transmitter PLL containing a modulator, a mixer, two programmable counters and a phase detector. The device is programmed via a three-wire bus.

# 2.2 Application

- The PMB 2251 is intended for use in an up-conversion loop.

- The device has a wide frequency range and is suitable for mobile communication systems requiring a high modulation bandwidth and a low phase error.

- The device is part of the Infineon chipset for single- and multiband mobile communication systems, such as GSM, PCN and PCS.

#### 2.3 Features

- Vector modulator operating from 80 to 450MHz

Integrated generation of orthogonal carriers

Typ. 40dB carrier rejection, 40dB SSB rejection, 54dB IM3 supression

- Double balanced Gilbert cell mixer

- single ended inputs and outputs

- LO- and RF input frequency range: 800MHz to 2GHz

- Output frequency range: DC to 450MHz

- Integrated modulation PLL

- -Input Counters programmable from 1 to 8

- -Charge pump with programmable current up to 4mA

- -Separate charge pump suppy voltage (2.7 to 5.5V)

- -Phase/Frequency-sensitive phase detector

- -Operation at up to 150MHz

- -Linear transfer characteristic (no dead zone)

- Serial data transfer via three-wire bus (Power-down modes programmable)

- Supply voltage 2.7 to 4.5V

- Temperature range -30° to 85°C

- P-TSSOP-28 package

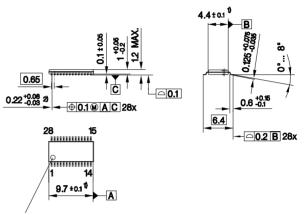

# 2.4 Package Outlines

P-TSSOP-28

Index Marking

1) Does not include plastic or metal protrusion of 0.15 max. per side 2) Does not include dambar protrusion

# **3** Functional Description

#### Contents of this Chapter

| 3.1 | Pin Configuration           | . 3-2 |

|-----|-----------------------------|-------|

| 3.2 | Pin Definition and Function | . 3-2 |

| 3.3 | Block Diagram               | . 3-5 |

| 3.4 | Circuit Description         | . 3-6 |

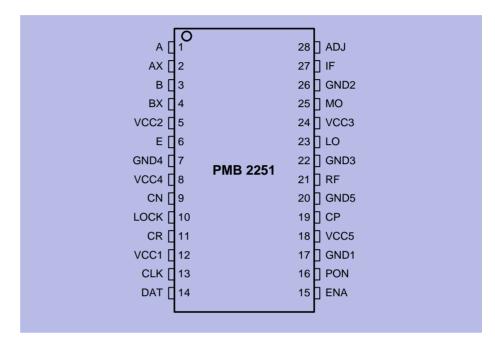

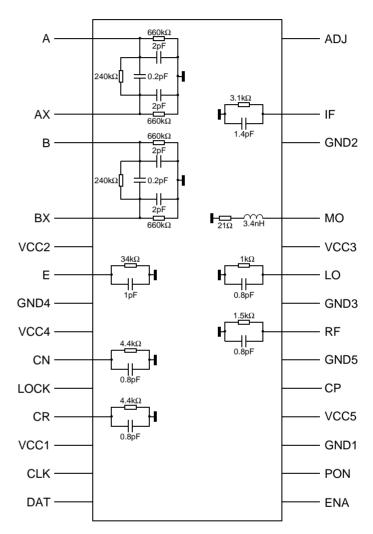

# 3.1 Pin Configuration

Pin\_config.wmf

# 3.2 Pin Definition and Function

| Table 3-1 Pin Definition and Function |        |                                   |                                  |  |  |

|---------------------------------------|--------|-----------------------------------|----------------------------------|--|--|

| Pin No.                               | Symbol | Equivalent I/O-Schematic          | Function                         |  |  |

| 1                                     | А      |                                   | Modulation input (non-inverting) |  |  |

| 2                                     | AX     | $A \xrightarrow{4k\Omega}{0.5pF}$ | Modulation input (inverting)     |  |  |

#### **Functional Description**

| 3  | В    |                                            | Modulation input (non-inverting)          |

|----|------|--------------------------------------------|-------------------------------------------|

|    |      | B6.5pF                                     |                                           |

|    |      | -∽ <sup>t</sup> t⊖-                        |                                           |

| 4  | вх   | ∽∽┸⊖−                                      | Modulation input (inverting)              |

|    |      | BX —H∎<br><sup>4kΩ</sup> <sub>0.5p</sub> F |                                           |

| 5  | VCC2 |                                            | Modulator supply voltage                  |

| 6  | E    |                                            | Modulator output                          |

| 0  | L    |                                            |                                           |

|    |      |                                            |                                           |

|    |      | E ────┬ <sup>‡</sup> ⊙-                    |                                           |

| 7  | GND4 |                                            | Counter and phase detector ground         |

| 8  | VCC4 |                                            | Counter and phase detector supply voltage |

| 9  | CN   |                                            | N-counter input                           |

|    |      | ₽ <sup>V</sup> cc−0.7V                     |                                           |

|    |      | 2kΩ []2.5kΩ<br>ή h.                        |                                           |

|    |      |                                            |                                           |

|    |      | ↓ ± <sup>5pF</sup>                         |                                           |

| 10 | LOCK |                                            | Control input for charge pump current     |

| 10 | LOOK |                                            | (also test output)                        |

|    |      |                                            |                                           |

|    |      | ₽                                          |                                           |

| 11 | CR   |                                            | R-counter input                           |

|    |      | ₽ <sup>V</sup> cc−0.7V                     |                                           |

|    |      | 2kΩ []2.5kΩ                                |                                           |

|    |      |                                            |                                           |

|    |      | $\bigcirc$ $\mathbf{T}_{22}$               |                                           |

| 12 | VCC1 |                                            | Bus supply voltage                        |

| 13 | CLK  |                                            | Clock input                               |

|    |      |                                            |                                           |

|    |      |                                            |                                           |

|    |      | Ψ                                          |                                           |

| 14 | DAT  |                                            | Data input                                |

|    |      |                                            |                                           |

|    |      |                                            |                                           |

|    |      | , , , , , , , , , , , , , , , , , , ,      |                                           |

| 15 | ENA  |                                            | Enable input                              |

|    |      |                                            |                                           |

|    |      | φ                                          |                                           |

|    |      |                                            |                                           |

**Functional Description**

| 16 | PON  |                                                                       | Power-on input               |  |

|----|------|-----------------------------------------------------------------------|------------------------------|--|

|    |      |                                                                       |                              |  |

| 17 | GND1 |                                                                       | Bus ground                   |  |

| 18 | VCC5 |                                                                       | Charge pump supply voltage   |  |

|    |      | CP<br>ICP<br>VCC5                                                     |                              |  |

|    |      | H= <sub>Y</sub> → YCC5                                                | -                            |  |

| 19 | CP   |                                                                       | Charge pump output           |  |

| 20 | GND5 |                                                                       | Charge pump ground           |  |

| 21 | RF   |                                                                       | Linear mixer input           |  |

|    |      | $V_{CC}$ -0.8V $A_{k\Omega}$ $4k\Omega$ $2k\Omega$                    |                              |  |

|    |      |                                                                       |                              |  |

|    |      |                                                                       |                              |  |

|    |      | -φφ                                                                   |                              |  |

| 22 | GND3 |                                                                       | Mixer ground                 |  |

| 23 | LO   |                                                                       | Switching mixer input        |  |

|    |      | V <sub>CC</sub> -0.7V o                                               |                              |  |

|    |      | $\frac{3.5k\Omega \prod_{2k\Omega}}{2k\Omega \prod_{j=1}^{2k\Omega}}$ |                              |  |

|    |      |                                                                       |                              |  |

|    |      | $\rightarrow$                                                         |                              |  |

| 24 | VCC3 |                                                                       | Mixer supply voltage         |  |

| 25 | МО   |                                                                       | Mixer output                 |  |

|    |      | <u>_</u>                                                              |                              |  |

|    |      | MO                                                                    |                              |  |

|    |      | 4mA ()                                                                |                              |  |

| 26 | GND2 |                                                                       | Modulator ground             |  |

| 27 | IF   |                                                                       | Modulator carrier input      |  |

|    |      | V <sub>CC</sub> -0.7V<br>P                                            |                              |  |

|    |      | 3.33kΩ <mark>↓</mark> 2kΩ                                             |                              |  |

|    |      |                                                                       |                              |  |

|    |      |                                                                       |                              |  |

| 28 | ADJ  |                                                                       | Modulator phase adjust input |  |

|    |      | <u>ل</u>                                                              |                              |  |

|    |      | –Γ.<br>200m∨ <u>1</u> ==−−−−−− ADJ                                    |                              |  |

|    |      | 2.5kΩ                                                                 |                              |  |

|    |      | _                                                                     |                              |  |

PMB 2251 preliminary Functional Description

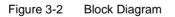

## 3.3 Block Diagram

# 3.4 Circuit Description

The modulator implements a single-sideband modulation. The signal at the IF input is split into two orthogonal carriers, which are multiplied by the signals at the modulation inputs A/AX and B/BX. The multiplication products are added and fed to the E output. The phase adjust input ADJ can optionally be used to maximise the single-sideband suppression of the modulator (see chapter 4).

The mixer multiplies the signals at the RF and LO inputs; the result appears at the MO output. The LO input is operated in switched mode, whereas the RF input is linear, which makes it suitable for a modulated signal.

The counters divide the frequency of the signals at the CN and CR inputs by the programmed factors N and R respectively, and feed the resulting signals FN and FR to the phase detector, which drives the charge pump. The counter outputs switch on the rising edge of the inputs. A test mode can be programmed in which either FN or FR is fed to the LOCK pin.

At the CP output, the charge pump generates current pulses of width equal to the time interval between the negative edges of FN and FR. The height and polarity of the pulses are programmable. In the intervals between pulses, the output is in a high-impedance state. The polarity of the pulses depends on which input has the higher frequency, or, if both inputs have the same frequency, which input leads. The charge pump can be operated at a higher supply voltage than the rest of the circuit, to allow a larger tuning voltage range. When a logic HIGH is applied to the LOCK input, the charge pump current has the value programmed via the bus. Applying a logic LOW at the LOCK input switches the charge pump current to its maximum value of 4mA.

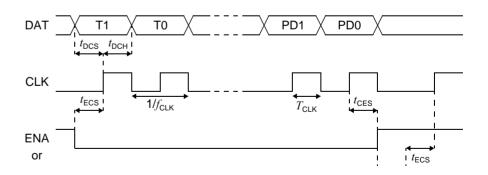

The device is programmed by shifting in a 14-bit control word at the DAT input. Each bit is transferred on the rising edge of the CLK input, starting with the most significant bit. The control word becomes valid on the rising edge of the ENA input, when it is loaded into a latch. The programming allows the modulator, the mixer and the phase detector block (including counters and charge pump) to be powered down individually. In the programmable power-down modes, the bus is ready to receive new data, and the control word remains latched. In the hardware power-down mode, activated by a logic LOW at the PON input, the entire chip is powered down and the control word is lost. After a hardware power-on, the modulator and phase detector blocks are initially powered down, whereas the mixer is powered up with PON to prevent LO-VCO pulling.

#### Contents of this Chapter

| 4.1 | Circuit Principle         |

|-----|---------------------------|

| 4.2 | Intermediate Frequency4-2 |

| 4.3 | Supply and Ground Pins4-2 |

| 4.4 | Coupling Circuitry        |

| 4.5 | Loop Filter               |

| 4.6 | Other Filters             |

| 4.7 | Modulation Inputs         |

| 4.8 | Charge Pump               |

| 4.9 | Input/Output Impedances   |

# 4.1 Circuit Principle

In the application circuit, the PMB 2251 is configured to form an up-conversion loop with external VCO and filters. In the feedback path of the loop, the mixer converts the transmit signal TX\_OUT at the VCO output down to an intermediate frequency, where it is filtered and fed to the carrier input IF of the modulator. The modulator performs a single-sideband modulation of the baseband input signals at A\_IN, AX\_IN, B\_IN, BX\_IN on to the carrier. The modulator output at E is filtered and fed to the R-counter. A constant reference frequency at CR\_IN is applied to the R-counter. In the steady state of the loop, the VCO output is modulated so as to cancel the modulation in the modulator, so that the modulator output is a constant, unmodulated frequency.

The direct and indirect conversion methods require a highly selective bandpass filter to suppress the wideband noise of the modulator and mixer. In the up-conversion loop, the wideband noise is suppressed by the loop filter, which is a simple RC low-pass filter. Compared to other modulation methods, the upconversion loop has the advantages of a better noise performance with lower filter costs and lower superimposed residual AM. As a result, the system can be operated with a higher efficiency in the power amplifier and a lower insertion loss in the antenna switch, both of which reduce the power consumption.

### 4.2 Intermediate Frequency

The mixer output MO, the carrier input IF and output E of the modulator and the N-counter input CN all operate at the intermediate frequency. In the Operational Range, the maximum intermediate frequency is specified at 400MHz, but the AC/DC characteristics are guaranteed only up to 350MHz. The functionality of mixer, modulator and N-counter in the range 300 to 400MHz is intended to allow the loop to lock for an initial VCO frequency deviation of up to 100MHz from its final value. In the locked state of the loop, the intermediate frequency may not exceed 300MHz. Note that the frequency sensitivity of the phase detector is guaranteed only up to 150MHz.

# 4.3 Supply and Ground Pins

On the circuit board, the ground pins GND1 to GND5 must all be connected by the shortest possible route to a common, low-impedance ground plane, and the supply pins VCC1 to VCC4 must all be connected to the same supply rail. It is permissible to connect VCC5 to a separate, higher supply voltage in order to increase the tuning voltage range. Each supply pin must be separately decoupled to the corresponding ground pin. The decoupling capacitor should be as close as possible to the pin and have its self-resonant frequency, and hence its minimum impedance, at the RF signal frequency in the block supplied by the pin.

# 4.4 Coupling Circuitry

The inputs CN, CR, RF, LO, IF are high-impedance inputs with internal resistors to a DC bias voltage (see Internal Input/Output Circuits). The signals at these inputs must be AC-coupled using an external capacitor. The optimum coupling is obtained when the self-resonant frequency of the capacitor is equal to the signal frequency. Note, however, that the power-up settling time depends on the time required to charge the coupling capacitors (see AC/DC Characteristics). There should be no external DC path to ground or supply at these pins, which means that any termination resistor must be placed on the other side of the coupling capacitor (e.g.  $R_3$  and  $R_{10}$  in the application circuit).

The attenuation between TX\_OUT and RF must be sufficient to ensure that the mixer is operated at least 3dB below its 1dB compression point. Because of the finite isolation of RF from LO (see AC/DC characteristics), the reverse attenuation must be sufficient to ensure that, in the signal spectrum at TX\_OUT, the component at the LO frequency is within the system specification.

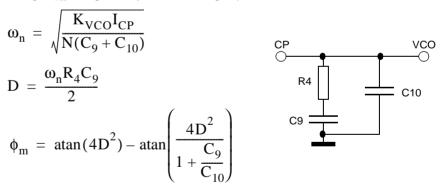

# 4.5 Loop Filter

In designing the loop filter, the same principles can be used as for a synthesizer PLL. The natural resonant frequency  $\omega_n$ , the damping factor *D* and the phase margin  $\phi_m$  are given by the following equations:

where  $K_{VCO}$  is the VCO gain in Hz V<sup>-1</sup> (<u>not</u> rad s<sup>-1</sup> V<sup>-1</sup>),  $I_{CP}$  the programmed value of the charge pump current and *N* the division ratio of the N-counter. A phase margin of about 60° is recommended. The choice of values for  $\omega_n$  and *D* involves a trade-off between phase accuracy and suppression of wideband noise. Provided the modulation frequency is less than  $1/(2\pi R_4 C_9)$ , the phase error depends only on  $\omega_n$  and is a decreasing function of  $\omega_n$ . The phase noise at a frequency offset much greater than  $\omega_n$  is an increasing function of  $\omega_n$  if *D* and  $\phi_m$  are held constant, and a decreasing function of *D* (up to the point where the noise of  $R_4$  begins to dominate) if  $\omega_n$  and  $\phi_m$  are held constant.

Wireless Components

### 4.6 Other Filters

The low-pass filter between MO and IF suppresses the image frequency and any residual components at the RF and LO frequencies. To avoid excessive intermodulation, the current swing at the MO output should not exceed 2mA peak, which means a minimum load impedance of  $50\Omega$  for an output level of - 10dBm.

E is a high-impedance, open-collector output, and requires a DC path to the supply voltage. The band-pass filter between E and CN suppresses the modulation product associated with the third harmonic of the carrier (see AC/DC Characteristics), which would cause in-band spurious in the VCO output spectrum due to intermodulation in the phase detector block. At the CN input, a suppression of at least 65dB relative to the wanted signal is recommended. Note that the third-harmonic suppression of the modulator improves with increasing frequency, therefore a high intermediate frequency is advisable. The voltage divider formed by  $R_1$  and  $R_2$  allows CN to be driven with a low impedance, which reduces cross-talk from E, without excessively damping the resonant circuit in the filter. The bandwidth of the filter must be wide enough to allow the loop to lock for maximum and minimum values of the initial VCO frequency.

### 4.7 Modulation Inputs

The modulator generates the upper sideband if A lags B by 90° and the lower sideband if A leads B by 90°. In the loop, the VCO is modulated so as to cancel the modulation in the modulator, so A should lead B if the upper sideband is required, and A should lag B if the lower sideband is required.

The allowed range of the DC level at the modulation inputs depends on the the voltage swing, the supply voltage and whether the drive is single-ended or balanced. The DC level and swing must be such that the instantaneous voltage at each input pin is at least 0.75V away from the ground and supply rails at all times (see Operational Range).

The single-sideband suppression of the modulator can be maximised by connecting a resistor to ground at the ADJ pin. The required value of the resistor depends on the IF frequency, and varies from  $R_{ADJ\_80MHz}$  (t.b.d.) at 80MHz to  $R_{ADJ\_350MHz}$  (t.b.d.) at 350MHz. If ADJ is not shorted to ground, a decoupling capacitor is recommended.

Offset voltages at the modulation inputs affect the carrier suppression. For an ideal modulator with external offsets  $V_{oa}$  and  $V_{ob}$  at the A and B inputs, the carrier suppression in dB is given by

$$a_{c} = 20 \log_{10} \left( \frac{V_{m}}{2 \sqrt{V_{oa}^{2} + V_{ob}^{2}}} \right)$$

where  $V_m$  is the peak-to-peak swing at the modulation inputs. The real modulator contains internal offsets, which are added to the external offsets. To obtain the best possible carrier suppression, it is advisable to use the maximum input swing of  $1V_{pp}$  (see Operational Range), which means  $500mV_{pp}$  at each pin for balanced operation.

Amplitude and phase errors in the modulation input signals affect the singlesideband suppression. For an ideal modulator with external amplitude error  $\alpha$  (amplitude ratio – 1) and phase error  $\phi$  (phase difference – 90°), the single-sideband suppression in dB is

$$a_{SSB} = 20 \log_{10} \sqrt{\frac{1 + \left(\frac{\alpha}{\alpha + 2}\right)^2 \tan^2\left(\frac{\phi}{2}\right)}{\left(\frac{\alpha}{\alpha + 2}\right)^2 + \tan^2\left(\frac{\phi}{2}\right)}}$$

The real modulator has an internal amplitude mismatch and phase error, which are added to the external ones.

#### 4.8 Charge Pump

The required charge pump polarity, which is set by the CPP bit in the control word (see Circuit Description), depends on the VCO characteristic. If the VCO frequency is an increasing function of the tuning voltage, CPP should be set to 1; if the VCO frequency is a decreasing function of the tuning voltage, CPP should be set to 0.

As the noise bandwidth is not important during capture, it is possible to reduce the capture time by increasing the charge pump current to its maximum value. This is done by switching the LOCK input to LOW (see Circuit Description). Once the loop is locked, LOCK is switched to HIGH, and the charge pump current has its lower, programmed value and a correspondingly lower supply current. The loop filter must be such that an adequate phase margin is maintained for both values of charge pump current. If the LOCK input is not needed, it can be connected to the supply voltage.

# 4.9 Input/Output Impedances

The AC equivalent circuits given below represent a best-fit approximation to the simulated small-signal impedances over the operational frequency range.

#### Contents of this Chapter

| 5.1.1 | Electrical Data                  |

|-------|----------------------------------|

|       | Operating Range                  |

| 5.2   | Bus Timing                       |

| 5.3   | Programming Tables               |

| 5.4   | Typical Temperature Dependencies |

| 5.5   | Test Circuit 1                   |

## 5.1 Electrical Data

#### 5.1.1 Absolute Maximum Ratings

#### WARNING

The maximum ratings may not be exceeded under any circumstances, not even momentarily and individually, as permanent damage to the IC will result.

| Table 5-1 Absolute Maximum Ratings       |                          |       |                       |      |                             |      |

|------------------------------------------|--------------------------|-------|-----------------------|------|-----------------------------|------|

| Parameter                                | Symbol                   | Limit | Values                | Unit | Remarks                     | Item |

|                                          |                          | min   | max                   |      |                             |      |

|                                          |                          |       |                       |      |                             |      |

| Supply voltage                           | V <sub>CC1,2,3,4</sub>   | -0.5  | 5.0                   | V    |                             | 1    |

|                                          | V <sub>CC5</sub>         | -0.5  | 6.0                   | V    |                             |      |

| Voltage at any input or output except CP | V <sub>IO</sub>          | -0.5  | V <sub>cc</sub> +0.5  | V    | $V_{\rm CC} \le 4.5 { m V}$ | 2    |

|                                          |                          |       | 5.0                   | V    | $V_{\rm CC} > 4.5 V$        |      |

| Voltage at CP                            | V <sub>CP</sub>          | -0.5  | V <sub>CC5</sub> +0.5 | V    | $V_{\rm CC5} \le 5 \rm V$   | 3    |

|                                          |                          |       | 5.5                   | V    | $V_{\rm CC5} > 5V$          |      |

| Differential input voltage               | $V_{\rm I} - V_{\rm IX}$ | -2    | 2                     | V    |                             | 4    |

| Output current                           | Ι <sub>Ο</sub>           |       | 10                    | mA   |                             | 5    |

| Storage temperature                      | Ts                       | -55   | 125                   | °C   |                             | 6    |

| Thermal Resistance                       | R <sub>thJA</sub>        |       | 152                   | K/W  |                             | 7    |

| (junction to ambient)                    |                          |       |                       |      |                             |      |

| ESD integrity                            | $V_{ESD}$                | -1000 | +1000                 | V    |                             | 8    |

| Pins 21, 23: reduced                     |                          |       |                       |      |                             |      |

| ESD-integrity > +/-500V                  |                          |       |                       |      |                             |      |

| due to HF-performance                    |                          |       |                       |      |                             |      |

#### 5.1.2 Operating Range

Within the operational range the IC operates as described in the circuit description. The AC/DC characteristic limits are not guaranteed.

| Table 5-2 Operating Range                 |                                                                 |                    |                           |                    |                   |      |

|-------------------------------------------|-----------------------------------------------------------------|--------------------|---------------------------|--------------------|-------------------|------|

| Parameter                                 | Symbol                                                          | Limit \            | /alues                    | Unit               | Test Conditions L | ltem |

|                                           |                                                                 | min                | max                       |                    |                   |      |

| Ambient temperature                       | $T_{A}$                                                         | -30                | 85                        | °C                 |                   | 1    |

| Supply voltage                            | $\begin{array}{c} V_{\rm CC1,2,3,4} \\ V_{\rm CC5} \end{array}$ | 2.7<br>2.7         | 4.5<br>5.5                | V<br>V             |                   | 2    |

| IF input frequency                        | $f_{IF}$                                                        | 80                 | 450 <sup>(1;6)</sup>      | MHz                |                   | 3    |

| IF input level                            | $P_{IF}$                                                        | -19 <sup>(6)</sup> | 0                         | dBm <sup>(2)</sup> |                   | 4    |

| A, AX, B, BX input voltage <sup>(2)</sup> | $V_{A}, V_{B}$                                                  | 0.75               | V <sub>cc</sub> –<br>0.75 | V                  |                   | 5    |

| A, AX, B, BX input frequency              | $f_{\sf m}$                                                     | 0                  | 10                        | MHz                |                   | 6    |

| A/AX, B/BX input level <sup>(3)</sup>     | $V_{\sf m}$                                                     |                    | 1                         | V <sub>pp</sub>    |                   | 7    |

| LO input frequency                        | ſlo                                                             | 800                | 2000                      | MHz                |                   | 8    |

| LO input level                            | $P_{LO}$                                                        |                    | 0                         | dBm <sup>(2)</sup> |                   | 9    |

| RF input frequency                        | $f_{\sf RF}$                                                    | 800                | 2000                      | MHz                |                   | 10   |

| RF input level                            | $P_{RF}$                                                        |                    | 0                         | dBm <sup>(2)</sup> |                   | 11   |

| MO output frequency                       | f <sub>мо</sub>                                                 | 0                  | 450 <sup>(1)</sup>        | MHz                |                   | 12   |

| CN input frequency                        | f <sub>cn</sub>                                                 | 80                 | 450 <sup>(1;7)</sup>      | MHz                |                   | 13   |

| CN input level                            | P <sub>CN</sub>                                                 | -18 <sup>(7)</sup> | 0                         | dBm <sup>(2)</sup> |                   | 14   |

| CR input frequency                        | fcr                                                             | 80                 | 650                       | MHz                |                   | 15   |

| CR input level                            | $P_{CR}$                                                        | -15                | 0                         | dBm <sup>(2)</sup> |                   | 16   |

| LOCK output frequency                     | flock                                                           | 0                  | 150                       | MHz                | test mode         | 17   |

| CP output voltage                         | V <sub>CP</sub>                                                 | 0.5                | V <sub>CC5</sub> -<br>0.8 | V                  |                   | 18   |

| CP output frequency                       | $f_{\sf CP}$                                                    | 10                 | 150                       | MHz                |                   | 19   |

| LOW input voltage <sup>(4)</sup>          | $V_{IL}$                                                        | 0                  | 0.8                       | V                  |                   | 20   |

| HIGH input voltage <sup>(4)</sup>         | $V_{IH}$                                                        | 2.1                | V <sub>CC</sub>           | V                  |                   | 21   |

| Clock frequency                           | f <sub>clk</sub>                                                |                    | 10                        | MHz                |                   | 22   |

| Clock pulse width                         | $T_{CLK}$                                                       | 60                 |                           | ns                 |                   | 23   |

| Enable pulse width                        | $T_{ENA}$                                                       | 60                 |                           | ns                 |                   | 24   |

| Data-to-clock set-up time                 | t <sub>DCS</sub>                                                | 20                 |                           | ns                 |                   | 25   |

| Data-to-clock hold time                   | t <sub>DCH</sub>                                                | 10                 |                           | ns                 |                   | 26   |

| Clock-to-enable set-up time               | t <sub>CES</sub>                                                | 20                 |                           | ns                 |                   | 27   |

| Enable-to-clock set-up time               | t <sub>ECS</sub>                                                | 20                 |                           | ns                 |                   | 28   |

- (1) In the locked state of the loop,  $f_{MO}$ ,  $f_{IF}$  and  $f_{CN}$  may not exceed 350MHz. Frequencies between 350 and 450MHz may only occur during capture (see chapter 4).

- (2) Power levels are referred to  $50\Omega$ .

- (3) The limits apply to the instantaneous voltage at A, AX, B, BX relative to ground.

- (4) The limit applies to the differential voltage between A and AX or between B and BX.

- (5) For LOCK, CLK, DAT, ENA and PON

- (6) In the locked state of the loop, the IF input level may not be lower than -15 dBm. Levels down to -17 dBm may only occur during capture. The specified Min. value of -17 dBm is guaranteed only up to 400 MHz. This reduces to -15dBm at 450 MHz.

- (7) The specified Min. value of -18 dBm is guaranteed only up to 400 MHz. See also 5.4

#### 5.1.3 AC/DC Characteristics

AC/DC characteristics involve the spread of values guaranteed within the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

| Table 5-3 AC/DC Characteris | stics with V <sub>V</sub>   | CC1,2,3,4 <sup>=</sup>     | = 2.7 to 4                  | .5 V, V <sub>VC</sub>       | <sub>C5</sub> = 2.7 to | o 5.5 V, T <sub>A</sub> = 25 °C                          |   |      |

|-----------------------------|-----------------------------|----------------------------|-----------------------------|-----------------------------|------------------------|----------------------------------------------------------|---|------|

|                             | Symbol                      | Li                         | Limit Values                |                             |                        | Test Conditions                                          | L | Item |

|                             |                             | min                        | typ                         | max                         |                        |                                                          |   |      |

| Supply current              |                             |                            |                             |                             |                        |                                                          |   |      |

| Bus                         | I <sub>CC1</sub>            | 0.46                       | 0.62                        | 0.78                        | mA                     |                                                          |   | 1    |

| Modulator                   | $I_{\rm CC2}$ + $I_{\rm E}$ | 12.7                       | 17                          | 21.3                        | mA                     |                                                          |   | 2    |

| Mixer                       | I <sub>CC3</sub>            | 6.0                        | 8.5                         | 11                          | mA                     |                                                          |   | 3    |

| Phase detector and counters | I <sub>CC4</sub>            | 9.6                        | 12.8                        | 16.0                        | mA                     | T1=0                                                     |   | 4    |

| Charge pump <sup>(1)</sup>  | I <sub>CC5</sub>            | 4.5<br>7.7<br>11.0<br>14.2 | 6.0<br>10.3<br>14.6<br>18.9 | 7.5<br>12.9<br>18.2<br>23.6 | mA<br>mA<br>mA<br>mA   | CP=00 (1mA)<br>CP=01 (2mA)<br>CP=10 (3mA)<br>CP=11 (4mA) |   | 5    |

| Power down                  | $\Sigma I_{\rm CC}$         | 0                          |                             | 10                          | μA                     | V <sub>PON</sub> =0.8V                                   |   | 6    |

#### Logic inputs LOCK<sup>(2)</sup>, DATA, CLK and ENA

| LOW input current  | I <sub>IL</sub> | -1 | 0   | 1   | μA | V <sub>IL</sub> =0.8V | 7 |

|--------------------|-----------------|----|-----|-----|----|-----------------------|---|

| HIGH input current | I <sub>IH</sub> | 0  | 1.4 | 2.8 | μA | V <sub>IH</sub> =2.1V | 8 |

|                    |                 |    |     |     |    |                       |   |

| Table 5-3 AC/DC Characteristics with $V_{VCC1,2,3,4}$ = 2.7 to 4.5 V, $V_{VCC5}$ = 2.7 to 5.5 V, $T_A$ = 25 °C (continued) |                  |              |     |      |      |                        |   |      |

|----------------------------------------------------------------------------------------------------------------------------|------------------|--------------|-----|------|------|------------------------|---|------|

|                                                                                                                            | Symbol           | Limit Values |     |      | Unit | Test Conditions        | L | ltem |

|                                                                                                                            |                  | min          | typ | max  |      |                        |   |      |

| Power-on input                                                                                                             |                  |              |     |      |      |                        |   |      |

| LOW input current                                                                                                          | $I_{PONL}$       | 1            | 2   | 4    | μA   | V <sub>PON</sub> =0.8V |   | 9    |

| HIGH input current                                                                                                         | $I_{PONH}$       | 3.3          | 6.6 | 13.2 | μA   | V <sub>PON</sub> =2.1V |   | 10   |

| Power-on delay <sup>(3),(6)</sup>                                                                                          | t <sub>PON</sub> |              | 350 |      | ns   |                        |   | 11   |

#### Modulator

$f_{IF}$ =180 and 330 MHz,  $P_{IF}$ =-8dBm;  $V_{A}$ = $V_{B}$ =1.35 $V_{DC}$ ,  $V_{m}$ =1 $V_{pp}$  (sine),  $f_{m}$ =10MHz, A lags B by 90°

| DC voltage at IF                                                     | $V_{IF}$               | V <sub>cc</sub> –<br>0.75      | V <sub>cc</sub> –<br>0.65     | V <sub>CC</sub> -<br>0.55  | V                                                    |                                                                               | 12 |

|----------------------------------------------------------------------|------------------------|--------------------------------|-------------------------------|----------------------------|------------------------------------------------------|-------------------------------------------------------------------------------|----|

| DC current at A, AX, B, BX                                           | $I_{\rm A}, I_{\rm B}$ | 2.5                            | 5                             | 10                         | μA                                                   |                                                                               | 13 |

| DC offset current at A/AX, B/BX <sup>(4)</sup>                       | I <sub>OS</sub>        | -1.5                           |                               | +1.5                       | μA                                                   |                                                                               | 14 |

| DC voltage at ADJ                                                    | $V_{ADJ}$              | 200                            | 240                           | 280                        | mV                                                   |                                                                               | 15 |

| DC current at E                                                      | IE                     | 3.0                            | 4.0                           | 5.0                        | mA                                                   |                                                                               | 16 |

| Settling time <sup>(5),(6)</sup>                                     | t <sub>MOD</sub>       |                                | 1.5                           |                            | μs                                                   | 100pF at IF and ADJ                                                           | 17 |

| Output level (at $f_{\rm IF}$ + $f_{\rm m}$ ) <sup>(12)</sup>        | i <sub>E</sub>         | 0.85<br>-14.4<br>0.74<br>-15.6 | 1.2<br>-11.4<br>1.05<br>-12.6 | 1.7<br>-8.4<br>1.5<br>-9.6 | mA <sub>rms</sub><br>dBm<br>mA <sub>rms</sub><br>dBm | @ 180 MHz<br>@ 330 MHz                                                        | 18 |

| Carrier suppression (at $f_{IF}$ )                                   | a <sub>CE</sub>        | 32                             | 40                            |                            | dB                                                   |                                                                               | 19 |

| Single-sideband suppression (at $f_{IF}-f_m$ )                       | a <sub>ssb</sub>       | 35<br>35                       | 40<br>40                      |                            | dB<br>dB                                             | $f_{\rm IF}$ =180MHz,<br>$f_{\rm IF}$ =330MHz,<br>(R <sub>ADJ</sub> = t.b.d.) | 20 |

| Suppression of 3rd-order intermodulation (at $f_{IF}$ -3 $f_m$ )     | a <sub>IM3</sub>       | 44<br>46                       | 54<br>56                      |                            | dB<br>dB                                             | f <sub>IF</sub> =180MHz<br>f <sub>IF</sub> =330MHz                            | 21 |

| Third-harmonic<br>suppression (at 3f <sub>IF</sub> -f <sub>m</sub> ) | a <sub>H3</sub>        | 12<br>32                       | 17<br>40                      |                            | dB                                                   | <i>f</i> <sub>IF</sub> =180MHz<br><i>f</i> <sub>IF</sub> =330MHz              | 22 |

| Phase noise <sup>(6),(7)</sup>                                       | $P_{\sf NE}$           |                                | 126                           |                            | dBc/<br>Hz                                           | at <i>f</i> <sub>IF</sub> + <i>f</i> <sub>m</sub> ± 400kHz                    | 23 |

#### Mixer

1.)  $f_{\rm RF} = 900$  MHz,  $f_{\rm LO} = 1230$  MHz 2.)  $f_{\rm RF} = 1.9$  GHz,  $f_{\rm LO} = 1.72$  GHz  $P_{\rm LO} = -10$  dBm,  $P_{\rm RF} = -12$  dBm,

| DC voltage at RF                 | $V_{RF}$         | V <sub>CC</sub> -<br>0.9  | V <sub>cc</sub> −<br>0.75 | V <sub>cc</sub> -<br>0.6  | V  |                    | 24 |

|----------------------------------|------------------|---------------------------|---------------------------|---------------------------|----|--------------------|----|

| DC voltage at LO                 | V <sub>LO</sub>  | V <sub>cc</sub> −<br>0.75 | V <sub>CC</sub> -<br>0.65 | V <sub>cc</sub> -<br>0.55 | V  |                    | 25 |

| DC voltage at MO                 | $V_{\rm MO}$     | V <sub>cc</sub> −<br>1.7  | V <sub>cc</sub> −<br>1.5  | V <sub>cc</sub> −<br>1.3  | V  |                    | 26 |

| Settling time <sup>(5),(6)</sup> | t <sub>MIX</sub> |                           | 1.5                       |                           | μs | 100pF at RF and LO | 27 |

#### preliminary

#### Reference

| Table 5-3 AC/DC Characteris                            | stics with V <sub>V</sub> | CC1,2,3,4 <sup>=</sup>    | = 2.7 to 4               | .5 V, V <sub>VC</sub>     | <sub>C5</sub> = 2.7 to | o 5.5 V, T <sub>A</sub> = 25 °C (cor             | ntinu | ied) |

|--------------------------------------------------------|---------------------------|---------------------------|--------------------------|---------------------------|------------------------|--------------------------------------------------|-------|------|

|                                                        | Symbol                    | Li                        | Limit Values             |                           | Unit                   | Test Conditions                                  | L     | Item |

|                                                        |                           | min                       | typ                      | max                       |                        |                                                  |       |      |

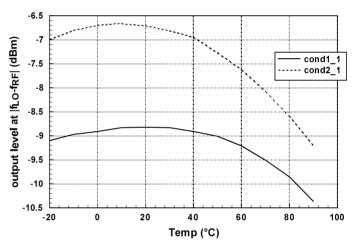

| Output power into $50\Omega^{(11)}$                    | P <sub>MO</sub>           | -12<br>-10                | -9<br>-7                 | -6<br>-4                  | dBm<br>dBm             | condition1<br>condition2<br>at $f_{RF} = f_{LO}$ |       | 28   |

| Carrier suppression                                    | a <sub>CMO</sub>          |                           | 20                       |                           | dB                     | at $f_{\rm LO}$                                  |       | 29   |

| 1dB compression point                                  | $P_{RF1dB}$               | -15<br>-18                | -12<br>-15               | -9<br>-12                 | dBm<br>dBm             | condition1<br>condition2                         |       | 30   |

| Phase noise <sup>(6),(7)</sup>                         | P <sub>NMO</sub>          |                           | 126                      |                           | dBc/<br>Hz             | at f <sub>RF</sub> –f <sub>LO</sub> ± 400kHz     |       | 31   |

| Isolation of RF input from LO input <sup>(6),(7)</sup> | a <sub>RF</sub>           | 30                        |                          |                           | dB                     |                                                  |       | 32   |

| Phase detector block <sup>(8)</sup>                    |                           |                           |                          |                           |                        |                                                  |       |      |

| DC voltage at CN, CR                                   | $V_{\rm CN},V_{\rm CR}$   | V <sub>cc</sub> -<br>0.86 | <sup>V</sup> cc−<br>0.76 | V <sub>CC</sub> -<br>0.66 | V                      |                                                  |       | 33   |

| HIGH output current at LOCK                            | I                         | 0.0                       | 12                       | 15                        | m۸                     | T-10 N-001                                       |       | 34   |

|                                                                     |                  | 0.86                     | 0.76                     | 0.66                     |                      |                                                        |    |

|---------------------------------------------------------------------|------------------|--------------------------|--------------------------|--------------------------|----------------------|--------------------------------------------------------|----|

| HIGH output current at LOCK (test mode)                             | $I_{LOCKH}$      | 0.9                      | 1.2                      | 1.5                      | mA                   | T=10, N=001,<br>V <sub>CN</sub> =V <sub>CC</sub>       | 34 |

| LOW output current at LOCK (test mode)                              | $I_{\rm LOCKL}$  | 2.3                      | 3.15                     | 4.0                      | mA                   | T=10, N=001,<br>V <sub>CN</sub> =V <sub>CC</sub> -1.4V | 35 |

| Output current at CP in high-impedance state                        | I <sub>CPZ</sub> |                          |                          | 100                      | nA                   | V <sub>CP</sub> =V <sub>CC</sub> /2<br>CP=11           | 36 |

| Output current in active<br>(source and sink) states <sup>(9)</sup> | I <sub>CPA</sub> | 0.8<br>1.6<br>2.4<br>3.2 | 1.0<br>2.0<br>3.0<br>4.0 | 1.2<br>2.4<br>3.6<br>4.8 | mA<br>mA<br>mA<br>mA | $V_{CP}=V_{CC}/2$<br>CP=00<br>CP=01<br>CP=10<br>CP=11  | 37 |

| Variation of output current with voltage <sup>(9)</sup>             | a <sub>CPV</sub> |                          |                          | 5                        | %                    | V <sub>CP</sub> over operational range                 | 38 |

| Variation of output<br>current with temperature <sup>(6),(9)</sup>  | a <sub>CPT</sub> |                          |                          | 5                        | %                    | $T_{A}$ over operational                               | 39 |

| Source/sink mismatch                                                | a <sub>CPM</sub> |                          |                          | 8                        | %                    | $V_{\rm CP} = V_{\rm CC}/2$                            | 41 |

| Output ripple at $f_{CP}$ when loop is locked <sup>(6),(10)</sup>   | i <sub>CP</sub>  |                          | 70                       |                          | μАр                  | CP=11<br><i>f</i> <sub>CP</sub> =150MHz                | 42 |

| Settling time <sup>(5),(6)</sup>                                    | t <sub>PD</sub>  |                          | 1.5                      |                          | μs                   | 100pF at CN and CR                                     | 43 |

| Propagation delay from CN to $CP^{(6)}$                             | t <sub>CP</sub>  |                          | 1.4                      |                          | ns                   |                                                        | 44 |

This value is only guaranteed in lab.

- (1) The supply current of the charge pump is the same in the active and high-impedance states.

- (2) T1=0.

- (3) The bus is ready to receive data a time  $t_{PON}$  after the positive edge of PON.

- (4) The offset current is the difference between the A and AX (or B and BX) input currents.

- (5) The settling time of a block after a software power-up is the time interval between the positive edge of ENA and the point where the parameters of the block are within the specified range. Note that the settling time depends on the time required to charge the external capacitors.

- (6) Not measured in production testing.

- (7) Test circuit for lab measurement to be defined.

- (8) The dynamic testing of the phase detector block is explained in Test Circuit 1.

- (9) The total variation of the output current (i.e. including production spread and dependence on temperature, supply voltage and output voltage) is  $\leq \pm 25\%$ .

- (10) The output ripple is proportional to the programmed charge pump current.

- (11) Mixer output power vs. temperature see 5.4.1

- (12) Modulator output power vs. temperature see 5.4.2

#### 5.2 Bus Timing

# 5.3 Programming Tables

| Table | 5-4                                                   |    |          |    |           |    |    |             |     |     |     |     |    |

|-------|-------------------------------------------------------|----|----------|----|-----------|----|----|-------------|-----|-----|-----|-----|----|

| MSB   | MSB bit assignment in control word *) reserved bit LS |    |          |    |           |    |    |             | LSB |     |     |     |    |

| te    | st                                                    | F  | R-counte | er | N-counter |    |    | charge pump |     |     | ро  | wn  |    |

| T1    | Т0                                                    | R2 | R1       | R0 | N2        | N1 | N0 | СРР         | CP1 | CP0 | PD2 | PD1 | *) |

| Table 5-5 |    |                  |

|-----------|----|------------------|

| T1        | ТО | test mode        |

| 0         | Х  | normal operation |

| 1         | 0  | FN fed to LOCK   |

| 1         | 1  | FR fed to LOCK   |

| Table 5-6 |         |         |                                |

|-----------|---------|---------|--------------------------------|

| N2 (R2)   | N1 (R1) | N0 (R0) | frequency division ratio N (R) |

| 0         | 0       | 0       | 8                              |

| 0         | 0       | 1       | 1                              |

| 0         | 1       | 0       | 2                              |

| 0         | 1       | 1       | 3                              |

| 1         | 0       | 0       | 4                              |

| 1         | 0       | 1       | 5                              |

| 1         | 1       | 0       | 6                              |

| 1         | 1       | 1       | 7                              |

| Table 5-7 |                                                        |

|-----------|--------------------------------------------------------|

| CPP       | polarity of charge pump output current                 |

| 0         | current sourced if FN has higher frequency or FN leads |

| 1         | current sunk if FN has higher frequency or FN leads    |

| Table 5-8 |     |                            |  |  |  |

|-----------|-----|----------------------------|--|--|--|

| CP1       | CP0 | charge pump output current |  |  |  |

| 0         | 0   | 1mA                        |  |  |  |

| 0         | 1   | 2mA                        |  |  |  |

| 1         | 0   | 3mA                        |  |  |  |

| 1         | 1   | 4mA                        |  |  |  |

Reference

| Table 5-9 |     |     |     |                                                   |  |  |

|-----------|-----|-----|-----|---------------------------------------------------|--|--|

| PON       | PD0 | PD1 | PD2 | active blocks                                     |  |  |

| 0         | х   | х   | х   | Power down                                        |  |  |

| 1         | х   | 0   | 0   | bus + mixer                                       |  |  |

| 1         | х   | 1   | 0   | bus + mixer + modulator                           |  |  |

| 1         | х   | 1   | 1   | bus + mixer + modulator +<br>phase detector block |  |  |

# 5.4 Typical Temperature Dependencies

condition 1: f<sub>RF</sub>=900MHz, f<sub>LO</sub>=1230MHz, P<sub>LO</sub>=-10dBm, P<sub>RF</sub>=-12dBm condition 2: f<sub>RF</sub>=1.9GHz, f<sub>LO</sub>=1.72GHz, P<sub>LO</sub>=-10dBm, P<sub>RF</sub>=-12dBm

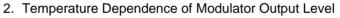

Output power of modulator vs IF frequency at -30°C, 30°C, 85°C from top  $P_{IF}$ =-9dBm,  $V_A$ = $V_B$ =1.8VDC,  $V_m$ =1 $V_{pp}$ ,  $f_m$ =100kHz,  $V_{CC}$ =3.6V,  $R_{ADJ}$ =47kOhm

PMB 2251

preliminary

Reference

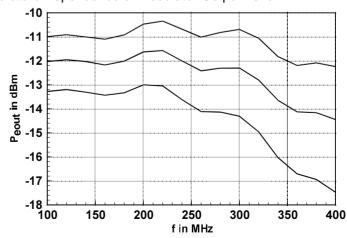

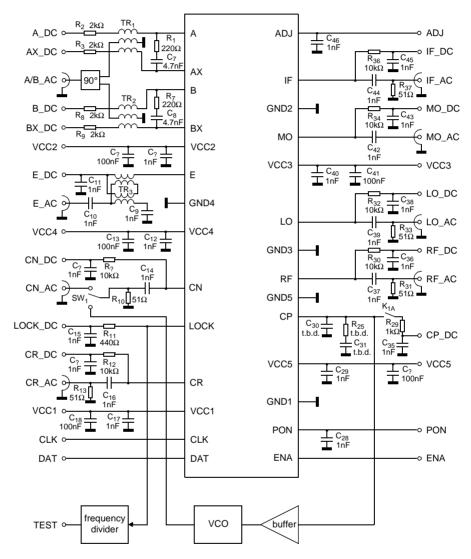

#### 5.5 Test Circuit 1

Infineon

Note: The dynamic testing of the phase detector block is performed by feeding the output of the VCO to the CN input, so as to form a closed phase-locked loop, and measuring the output frequency of the N-counter (in test mode).