## 4M-BIT [512K x8/256K x16] CMOS EPROM WITH PAGE MODE

### **FEATURES**

- With Page Mode function, 8-word/16-byte page

- 512K x 8 or 256K x 16 organization

- +12.5V programming voltage

- Fast access time: 90/100/120/150 ns

- Page mode access time 50/60/75 ns

- Totally static operation

- Completely TTL compatible

- Operating current: 60mAStandby current: 100uA

- Package type:

- 40 pin plastic DIP

- 40 pin SOP

#### **GENERAL DESCRIPTION**

The MX27C4111 is a 4M-bit, ultraviolet Erasable Programmable Read Only Memory with page mode. It is organized as 512K x 8 or 256K x 16, operates from a single + 5 volt supply, has a static standby mode, and features fast single address location programming. All programming signals are TTL levels, requiring a single pulse. For programming outside from the system, existing EPROM programmers may be used. The MX27C4111 supports a intelligent fast programming algorithm which can result in programming time of less than two minutes.

MX27C4111 provides Page Read Access Mode which can greatly reduce the read access time. Normal read access time and Page Mode read access time is as fast as 90/50ns. It is designed to be compatible with all microprocessors and similar applications in which high perofmrance, large bit storage and simple interfacing are important design considerations.

This EPROM is packaged in industry standard 40 pin dual-in-line packages and 40 pin SOP packages.

# PIN CONFIGURATIONS PDIP/SOP

| A17 🗆 1  |              | 40 🗆 A8      |

|----------|--------------|--------------|

| _        |              |              |

| A7 🗆 2   |              | 39 A9        |

| A6 □ 3   |              | 38 🗖 A10     |

| A5 🖂 4   |              | 37 🔁 A11     |

| A4 🖂 5   |              | 36 🗖 A12     |

| A3 □ 6   |              | 35 🗖 A13     |

| A2 🗖 7   | _            | 34 🗖 A14     |

| A1 🗆 8   | <del>-</del> | 33 🗖 A15     |

| A0 □ 9   | 4            | 32 🗖 A16     |

| CE 🗆 10  | MX27C4111    | 31 BYTE/VPP  |

| GND ☐ 11 | 9            | 30 🗀 GND     |

| ŌE □ 12  | ŝ            | 29 🗖 Q15/A-1 |

| Q0 🗖 13  | _            | 28 🗖 Q7      |

| Q8 🗆 14  |              | 27 🗖 Q14     |

| Q1 🗖 15  |              | 26 🗖 Q6      |

| Q9 🗖 16  |              | 25 🗖 Q13     |

| Q2 🖂 17  |              | 24 🗖 Q5      |

| Q10 🗖 18 |              | 23 🗖 Q12     |

| Q3 🗆 19  |              | 22 🗅 Q4      |

| Q11 🗆 20 |              | 21 🗅 VCC     |

|          |              |              |

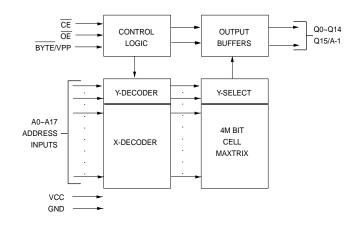

#### **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

| -        |                                            |

|----------|--------------------------------------------|

| SYMBOL   | PIN NAME                                   |

| A0~A17   | Address Input                              |

| Q0~Q14   | Data Input/Output                          |

| CE       | Chip Enable Input                          |

| ŌĒ       | Output Enable Input                        |

| BYTE/VPP | Word/Byte Selection/Program Supply Voltage |

| Q15/A-1  | Q15(Word mode)/LSB addr. (Byte mode)       |

| VCC      | Power Supply Pin (+5V)                     |

| GND      | Ground Pin                                 |

## TRUTH TABLE OF BYTE FUNCTION

## BYTE $MODE(\overline{BYTE} = GND)$

| CE | ŌĒ | Q15/A-1   | MODE         | Q0-Q7  | SUPPLY CURRENT  |  |

|----|----|-----------|--------------|--------|-----------------|--|

| Н  | Х  | X         | Non selected | High Z | Standby(ICC2)   |  |

| L  | Н  | X         | Non selected | High Z | Operating(ICC1) |  |

| L  | L  | A-1 input | Selected     | DOUT   | Operating(ICC1) |  |

## WORD MODE( $\overline{BYTE} = VCC$ )

| CE | ŌĒ | Q15/A-1 | MODE         | Q0-Q14 | SUPPLY CURRENT  |  |

|----|----|---------|--------------|--------|-----------------|--|

| Н  | Х  | High Z  | Non selected | High Z | Standby(ICC2)   |  |

| L  | Н  | High Z  | Non selected | High Z | Operating(ICC1) |  |

| L  | L  | DOUT    | Selected     | DOUT   | Operating(ICC1) |  |

NOTE: X = H or L

#### **FUNCTIONAL DESCRIPTION**

#### THE PROGRAMMING OF THE MX27C4111

When the MX27C4111 is delivered, or it is erased, the chip has all 4M bits in the "ONE" or HIGH state. "ZEROs" are loaded into the MX27C4111 through the procedure of programming.

For programming, the data to be programmed is applied with 16 bits in parallel to the data pins.

VCC must be applied simultaneously or before VPP, and removed simultaneously or after VPP. When programming an MXIC EPROM, a 0.1uF capacitor is required across VPP and ground to suppress spurious voltage transients which may damage the device.

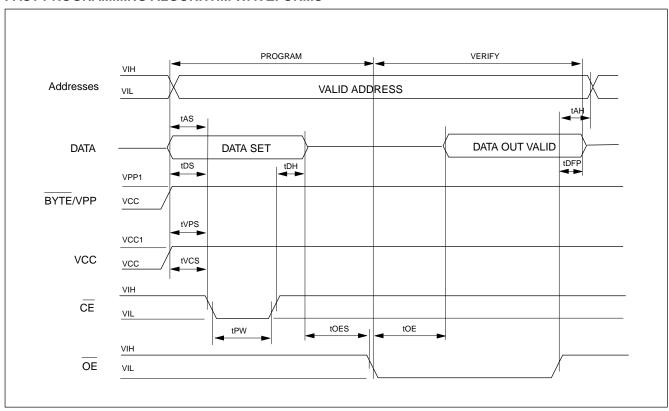

#### **FAST PROGRAMMING**

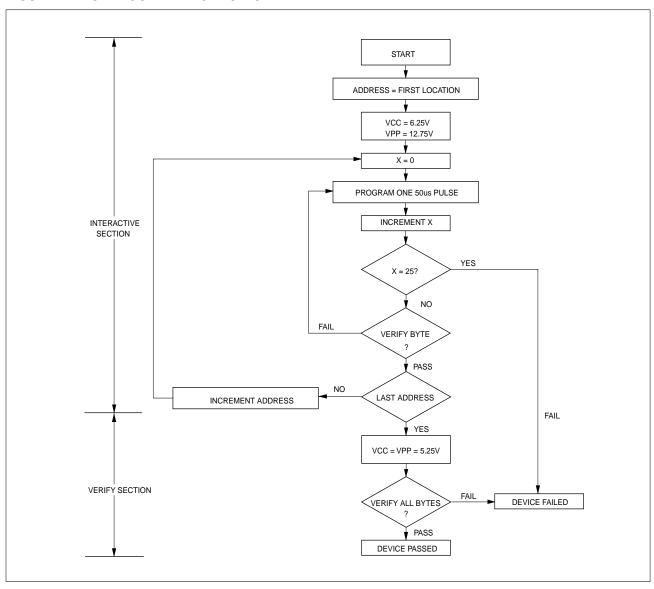

The device is set up in the fast programming mode when the programming voltage VPP = 12.75V is applied, with VCC = 6.25 V and  $\overline{OE}$  = VIH (Algorithm is shown in Figure 1). The programming is achieved by applying a single TTL low level 100us pulse to the  $\overline{CE}$  input after addresses and data line are stable. If the data is not verified, an additional pulse is applied for a maximum of 25 pulses. This process is repeated while sequencing through each address of the device. When the programming mode is completed, the data in all address is verified at VCC = VPP =  $5V \pm 10\%$ .

#### **PROGRAM INHIBIT MODE**

Programming of multiple MX27C4111's in parallel with different data is also easily accomplished by using the Program Inhibit Mode. Except for  $\overline{CE}$  and  $\overline{OE}$ , all like inputs of the parallel MX27C4111 may be common. A  $\overline{TTL}$  low-level program pulse applied to an MX27C4111  $\overline{CE}$  input with  $\overline{VPP} = 12.5 \pm 0.5 \text{ V}$  will program the MX27C4111. A high-level  $\overline{CE}$  input inhibits the other MX27C4111s from being programmed.

#### PROGRAM VERIFY MODE

Verification should be performed on the programmed bits to determine that they were correctly <u>programmed</u>. The verification should be performed with OE at VIL, CE at VIH, and VPP at its programming voltage.

#### **AUTO IDENTIFY MODE**

The auto identify mode allows the reading out of a binary code from an EPROM that will identify its manufacturer and device type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the  $25\,^{\circ}\text{C}$   $\pm$   $5\,^{\circ}\text{C}$  ambient temperature range that is required when programming the MX27C4111.

To activate this mode, the programming equipment must force  $12.0 \pm 0.5 \, \text{V}$  on address line A9 of the device. Two identifier bytes may then be sequenced from the device outputs by toggling address line A0 from VIL to VIH. All other address lines must be held at VIL during auto identify mode.

Byte 0 (A0 = VIL) represents the manufacturer code, and byte 1 (A0 = VIH), the device identifier code. For the MX27C4111, these two identifier bytes are given in the Mode Select Table. All identifiers for manufacturer and device codes will possess odd parity, with the MSB (Q15) defined as the parity bit.

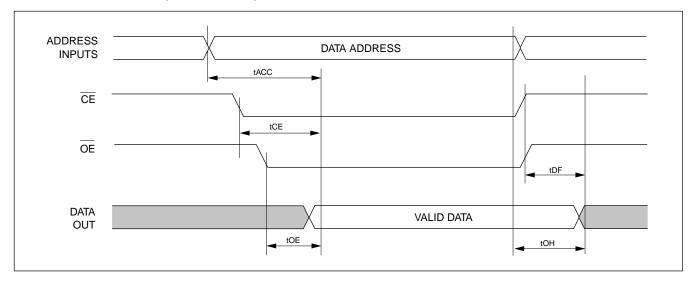

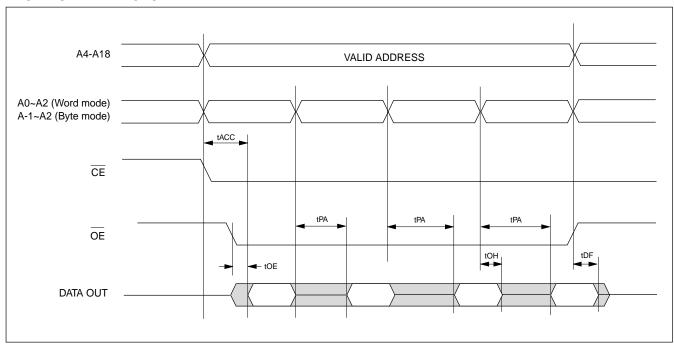

#### **READ MODE**

The MX27C4111 provides page mode with 8 words/16 bytes per page. In order to get the benefit of fast page read, the user should keep chip enable  $(\overline{CE})$  low and toggle address A0~A2 in word mode or A-1~A2 in byte mode. Page Read access time(tPA) is equal to the delay from address stable to data output. It is twice as fast as normal tACC and is highly recommended.

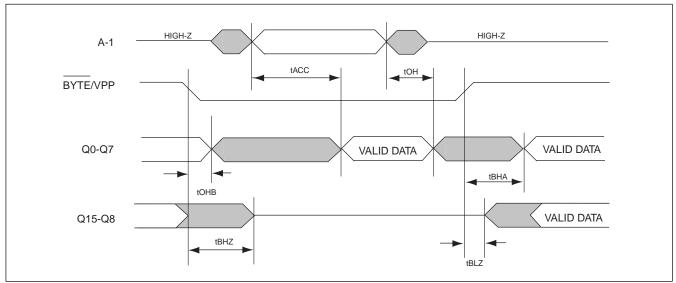

#### **WORD-WIDE MODE**

With  $\overline{\text{BYTE}}/\text{VPP}$  at VCC  $\pm$  0.2V outputs Q0-7 present data Q0-7 and outputs Q8-15 present data Q8-15, after  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  are appropriately enabled.

#### **BYTE-WIDE MODE**

With BYTE/VPP at GND  $\pm$  0.2V, outputs Q8-15 are tristated. If Q15/A-1 = VIH, outputs Q0-7 present data bits Q8-15. If Q15/A-1 = VIL, outputs Q0-7 present data bits Q0-7.

#### STANDBY MODE

The MX27C4111 has a CMOS standby mode which reduces the maximum VCC current to 100 uA. It is placed in CMOS standby when CE is at VCC  $\pm$  0.3 V. The MX27C4111 also has a TTL-standby mode which reduces the maximum VCC current to 1.5 mA. It is placed in TTL-standby when  $\overline{\text{CE}}$  is at VIH. When in standby mode, the outputs are in a high-impedance state, independent of the  $\overline{\text{OE}}$  input.

#### TWO-LINE OUTPUT CONTROL FUNCTION

To accommodate multiple memory connections, a twoline control function is provided to allow for:

- 1. Low memory power dissipation,

- 2. Assurance that output bus contention will not occur.

It is recommended that CE be decoded and used as the primary device-selecting function, while OE be made a common connection to all devices in the array and

connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low-power standby mode and that the output pins are only active when data is desired from a particular memory device.

#### SYSTEM CONSIDERATIONS

During the switch between active and standby conditions, transient current peaks are produced on the rising and falling edges of Chip Enable. The magnitude of these transient current peaks is dependent on the output capacitance loading of the device. At a minimum, a 0.1 uF ceramic capacitor (high frequency, low inherent inductance) should be used on each device between Vcc and GND to minimize transient effects. In addition, to overcome the voltage drop caused by the inductive effects of the printed circuit board traces on EPROM arrays, a 4.7 uF bulk electrolytic capacitor should be used between VCC and GND for each eight devices. The location of the capacitor should be close to where the power supply is connected to the array.

#### MODE SELECT TABLE

|                      |     |     |    |     |         | BYTE/  |           |           |

|----------------------|-----|-----|----|-----|---------|--------|-----------|-----------|

| MODE                 | CE  | OE  | A9 | Α0  | Q15/A-1 | VPP(5) | Q8-14     | Q0-7      |

| Read (Word)          | VIL | VIL | Х  | Х   | Q15 Out | VCC    | Q8-14 Out | Q0-7 Out  |

| Read (Upper Byte)    | VIL | VIL | Х  | Х   | VIH     | GND    | High Z    | Q8-15 Out |

| Read (Lower Byte)    | VIL | VIL | Х  | Х   | VIL     | GND    | High Z    | Q0-7 Out  |

| Output Disable       | VIL | VIH | Х  | Х   | High Z  | Х      | High Z    | High Z    |

| Standby              | VIH | Х   | Х  | Х   | High Z  | Х      | High Z    | High Z    |

| Program              | VIL | VIH | Х  | Х   | Q15 In  | VPP    | Q8-14 In  | Q0-7 In   |

| Program Verify       | VIH | VIL | Х  | Х   | Q5 Out  | VPP    | Q8-14 Out | Q0-7 Out  |

| Program Inhibit      | VIH | VIH | Х  | Х   | High Z  | VPP    | High Z    | High Z    |

| Manufacturer Code(3) | VIL | VIL | VH | VIL | 0B      | VCC    | 00H       | C2H       |

| Device Code(3)       | VIL | VIL | VH | VIH | 1B      | VCC    | 38H       | 00H       |

**NOTES:** 1. VH =  $12.0V \pm 0.5V$

2. X = Either VIH or VIL

3. A1 - A8, A10 - A17 = VIL (For auto select)

- 4. See DC Programming Characteristics for VPP voltages.

- 5. BYTE/VPP is intended for operation under DC Voltage conditions only.

- 6. Manufacture code = 00C2H Device code = B800H

#### FIGURE 1. FAST PROGRAMMING FLOW CHART

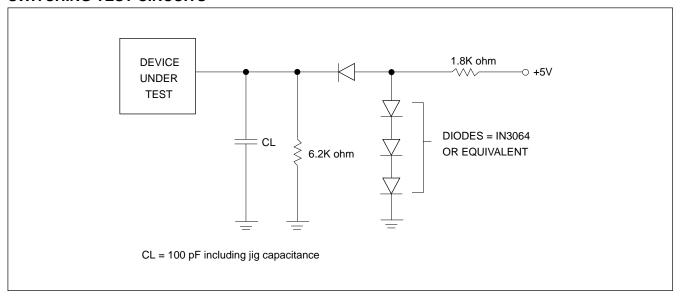

#### **SWITCHING TEST CIRCUITS**

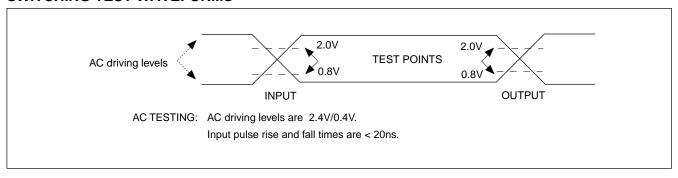

## **SWITCHING TEST WAVEFORMS**

#### **ABSOLUTE MAXIMUM RATINGS**

| RATING                        | VALUE               |

|-------------------------------|---------------------|

| Ambient Operating Temperature | 0°C to 70°C         |

| Storage Temperature           | -65°C to 125°C      |

| Applied Input Voltage         | -0.5V to 7.0V       |

| Applied Output Voltage        | -0.5V to VCC + 0.5V |

| VCC to Ground Potential       | -0.5V to 7.0V       |

| A9 & VPP                      | -0.5V to 13.5V      |

#### NOTICE

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended period may affect reliability.

#### NOTICE:

Specifications contained within the following tables are subject to change.

#### **DC/AC Operating Condition for Read OPeration**

|                       |            | MX27C4111 |           |           |           |  |  |  |  |  |

|-----------------------|------------|-----------|-----------|-----------|-----------|--|--|--|--|--|

|                       |            | -90       | -10       | -12       | -15       |  |  |  |  |  |

| Operating Temperature | Commercial | 0℃ to 70℃ | 0℃ to 70℃ | 0℃ to 70℃ | 0℃ to 70℃ |  |  |  |  |  |

| Vcc POwer Supply      |            | 5V ± 5%   | 5V ± 10%  | 5V ± 10%  | 5V ± 10%  |  |  |  |  |  |

#### **DC CHARACTERISTICS**

| SYMBOL | PARAMETER               | MIN. | MAX.      | UNIT | CONDITIONS                                                                             |

|--------|-------------------------|------|-----------|------|----------------------------------------------------------------------------------------|

| VOH    | Output High Voltage     | 2.4  |           | V    | IOH = -0.4mA                                                                           |

| VOL    | Output Low Voltage      |      | 0.4       | V    | IOL = 2.1mA                                                                            |

| VIH    | Input High Voltage      | 2.0  | VCC + 0.5 | V    |                                                                                        |

| VIL    | Input Low Voltage       | -0.3 | 0.8       | V    |                                                                                        |

| ILI    | Input Leakage Current   | -10  | 10        | uA   | VIN = 0 to 5.5V                                                                        |

| ILO    | Output Leakage Current  | -10  | 10        | uA   | VOUT = 0 to 5.5V                                                                       |

| ICC3   | VCC Power-Down Current  |      | 100       | uA   | CE = VCC ± 0.3V                                                                        |

| ICC2   | VCC Standby Current     |      | 1.5       | mA   | CE = VIH                                                                               |

| ICC1   | VCC Active Current      |      | 60        | mA   | CE = VIL, f=5MHz, lout = 0mA                                                           |

| IPP    | VPP Supply Current Read |      | 10        | uA   | $\overline{\text{CE}} = \overline{\text{OE}} = \text{VIL}, \text{ VPP} = 5.5 \text{V}$ |

## **CAPACITANCE** TA = 25°C, f = 1.0 MHz (Sampled only)

| SYMBOL | PARAMETER          | TYP. | MAX. | UNIT | CONDITIONS |  |

|--------|--------------------|------|------|------|------------|--|

| CIN    | Input Capacitance  | 8    | 12   | pF   | VIN = 0V   |  |

| COUT   | Output Capacitance | 8    | 12   | pF   | VOUT = 0V  |  |

| CVPP   | VPP Capacitance    | 18   | 25   | pF   | VPP = 0V   |  |

#### **AC CHARACTERISTICS**

|        |                                    | 27C  | <u>4111-90</u> | 27C411 | <u>11-10</u> | 27C41 | 11-12 | 27C411 | <u>1-15</u> |      |                                       |

|--------|------------------------------------|------|----------------|--------|--------------|-------|-------|--------|-------------|------|---------------------------------------|

| SYMBOL | PARAMETER                          | MIN. | MAX.           | MIN.   | MAX.         | MIN.  | MAX.  | MIN.   | MAX.        | UNIT | CONDITIONS                            |

| tACC   | Address to Output Delay            |      | 90             |        | 100          |       | 120   |        | 150         | ns   | $\overline{CE} = \overline{OE} = VIL$ |

| tCE    | Chip Enable to Output Delay        |      | 90             |        | 100          |       | 120   |        | 150         | ns   | OE = VIL                              |

| tPA    | Page Address to Output Delay       |      | 50             |        | 50           |       | 60    |        | 75          | ns   | CE = OE =VIL                          |

| tOE    | Output Enable to Output Delay      |      | 45             |        | 45           |       | 50    |        | 65          | ns   | CE = VIL                              |

| tDF    | OE High to Output Float,           | 0    | 30             | 0      | 30           | 0     | 35    | 0      | 50          | ns   |                                       |

|        | or CE High to Output Float         |      |                |        |              |       |       |        |             |      |                                       |

| tOH    | Output Hold from Address,          | 0    | 0              | 0      |              | 0     |       | 0      |             | ns   |                                       |

|        | CE or OE which ever occurred first | st   |                |        |              |       |       |        |             |      |                                       |

## AC CHARACTERISTICS(Continued)

|        |                        | 27C41 | 11-90 | 27C4 | 1111-10 | 27C41 | 111-12 | 27C41 | <u>11-15</u> |      |

|--------|------------------------|-------|-------|------|---------|-------|--------|-------|--------------|------|

| SYMBOL | PARAMETER              | MIN.  | MAX.  | MIN. | MAX.    | MIN.  | MAX.   | MIN.  | MAX.         | UNIT |

| tBHA   | BYTE Access Time       |       | 90    |      | 100     |       | 120    |       | 150          | ns   |

| tOHB   | BYTE Output Hold Time  | 0     |       | 0    |         | 0     |        | 0     |              | ns   |

| tBHZ   | BYTE Output Delay Time |       | 70    |      | 70      |       | 70     |       | 70           | ns   |

| tBLZ   | BYTE Output Set Time   | 10    |       | 10   |         | 10    |        | 10    |              | ns   |

## **DC PROGRAMMING CHARACTERISTICS** $TA = 25^{\circ}C \pm 5^{\circ}C$

| SYMBOL | PARAMETER                             | MIN. | MAX.      | UNIT | CONDITIONS         |

|--------|---------------------------------------|------|-----------|------|--------------------|

| VOH    | Output High Voltage                   | 2.4  |           | V    | IOH = -0.40mA      |

| VOL    | Output Low Voltage                    |      | 0.4       | V    | IOL = 2.1mA        |

| VIH    | Input High Voltage                    | 2.0  | VCC + 0.5 | V    |                    |

| VIL    | Input Low Voltage                     | -0.3 | 0.8       | V    |                    |

| ILI    | Input Leakage Current                 | -10  | 10        | uA   | VIN = 0 to 5.5V    |

| VH     | A9 Auto Select Voltage                | 11.5 | 12.5      | V    |                    |

| ICC3   | VCC Supply Current (Program & Verify) |      | 50        | mA   |                    |

| IPP2   | VPP Supply Current(Program)           |      | 30        | mA   | CE = VIL, OE = VIH |

| VCC1   | Fast Programming Supply Voltage       | 6.00 | 6.50      | V    |                    |

| VPP1   | Fast Programming Voltage              | 12.5 | 13.0      | V    |                    |

|        |                                       |      |           |      |                    |

## AC PROGRAMMING CHARACTERISTICS TA = 25°C ± 5°C

| SYMBOL | PARAMETER                         | MIN. | MAX. | UNIT | CONDITIONS |

|--------|-----------------------------------|------|------|------|------------|

| tAS    | Address Setup Time                | 2.0  |      | us   |            |

| tOES   | OE Setup Time                     | 2.0  |      | us   |            |

| tDS    | Data Setup Time                   | 2.0  |      | us   |            |

| tAH    | Address Hold Time                 | 0    |      | us   |            |

| tDH    | Data Hold Time                    | 2.0  |      | us   |            |

| tDFP   | Chip Enable to Output Float Delay | 0    | 130  | ns   |            |

| tVPS   | BYTE/VPP Setup Time               | 2.0  |      | us   |            |

| tPW    | CE initial Program Pulse Width    | 95   | 105  | us   |            |

| tVCS   | VCC Setup Time                    | 2.0  |      | us   |            |

| tOE    | Data valid from OE                |      | 150  | ns   |            |

## WAVEFORMS NORMAL READ CYCLE(WORD MODE)

#### **PAGE MODE READ CYCLE**

# WAVEFORMS NORMAL READ CYCLE(BYTE MODE)

#### **FAST PROGRAMMING ALGORITHM WAVEFORMS**

## **ORDERING INFORMATION**

## PLASTIC PACKAGE

| PART NO.       | ACCESS TIME | OPERATING CURRENT | STANDBY CURRENT | PACKAGE                  |

|----------------|-------------|-------------------|-----------------|--------------------------|

|                | (ns)        | MAX.(mA)          | MAX.(uA)        |                          |

| MX27C4111MC-90 | 90          | 60                | 100             | 40 Pin SOP(ROM pin out)  |

| MX27C4111MC-10 | 100         | 60                | 100             | 40 Pin SOP(ROM pin out)  |

| MX27C4111MC-12 | 120         | 60                | 100             | 40 Pin SOP(ROM pin out)  |

| MX27C4111MC-15 | 150         | 60                | 100             | 40 Pin SOP(ROM pin out)  |

| MX27C4111PC-90 | 90          | 60                | 100             | 40 Pin PDIP(ROM pin out) |

| MX27C4111PC-10 | 100         | 60                | 100             | 40 Pin PDIP(ROM pin out) |

| MX27C4111PC-12 | 120         | 60                | 100             | 40 Pin PDIP(ROM pin out) |

| MX27C4111PC-15 | 150         | 60                | 100             | 40 Pin PDIP(ROM pin out) |

|                |             |                   |                 |                          |

#### **PACKAGE INFORMATION**

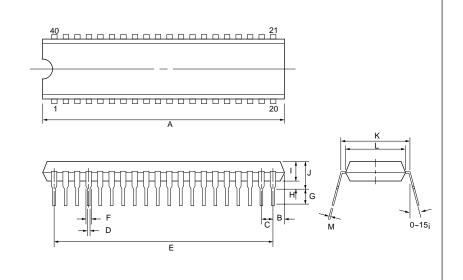

#### 40-PIN PLASTIC DIP(600 mil)

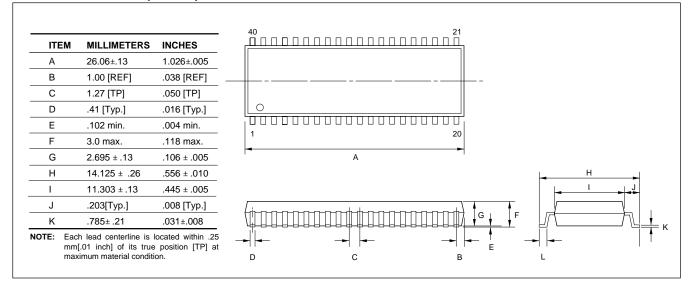

| ITEM | MILLIMETERS | INCHES      |

|------|-------------|-------------|

| Α    | 52.54 max.  | 2.070 max.  |

| В    | 2.03 [REF]  | .080 [REF]  |

| С    | 2.54 [TP]   | .100 [TP]   |

| D    | .46 [Typ.]  | .018 [Typ.] |

| Е    | 48.22       | 1.900       |

| F    | 1.52 [Typ.] | .060 [Typ.] |

| G    | 3.30 ± .25  | .130 ± .010 |

| Н    | .51 [REF]   | .020 [REF]  |

| ı    | 3.94 ± .25  | .155 ± .010 |

| J    | 5.33 max.   | .210 max.   |

| K    | 15.22 ± .25 | .600 ± .010 |

| L    | 13.97 ± .25 | .550 ± .010 |

| М    | .25 [Typ.]  | .010 [Typ.] |

NOTE: Each lead centerline is located within .25 mm[.01 inch] of its true position [TP] at maximum material condition.

#### 40-PIN PLASTIC SOP(450 mil)

## **Revision History**

| Revision | No. Description                                         | Page       | Date        |

|----------|---------------------------------------------------------|------------|-------------|

| 2.0      | Eliminate Interactive Programming Mode                  |            | 6/14/1997   |

|          | 2) 40-CDIP package quartz lens, change to square shape. |            |             |

| 2.1      | IPP 100uA> 10uA                                         |            | 8/07/1997   |

| 2.2      | Add 100ns speed grade.                                  |            | 1/31/1998   |

| 2.3      | Add 90ns speed grade.                                   |            | 4/07/1998   |

| 2.4      | 90ns speed grade VCC=5V±10%> VCC=5V±5%                  |            | 5/06/1998   |

| 2.5      | Cancel ceramic DIP package type                         | P1,3,12,13 | MAR/02/2000 |

## MACRONIX INTERNATIONAL CO., LTD.

#### **HEADQUARTERS:**

TEL:+886-3-578-6688 FAX:+886-3-563-2888

#### **EUROPE OFFICE:**

TEL:+32-2-456-8020 FAX:+32-2-456-8021

#### JAPAN OFFICE:

TEL:+81-44-246-9100 FAX:+81-44-246-9105

#### SINGAPORE OFFICE:

TEL:+65-348-8385 FAX:+65-348-8096

#### TAIPEI OFFICE:

TEL:+886-2-509-3300 FAX:+886-2-509-2200

## MACRONIX AMERICA, INC.

TEL:+1-408-453-8088 FAX:+1-408-453-8488

#### **CHICAGO OFFICE:**

TEL:+1-847-963-1900 FAX:+1-847-963-1909

http://www.macronix.com