# MN83951

### **TFT LCD Panel Controller**

#### Overview

The MN83951 is a timing controller for displaying an analog video signal on a TFT color liquid crystal display panel in such applications as LCD television sets and video cameras.

#### Features

- Support for both composite color sync input and separate color sync input

- Horizontal and vertical position adjustment functions

- Horizontal: 4 bits (range: approximately 4 µs)

- Vertical: 3 bits (range: 7 H)

- Wide panel support

- · Three side blackout modes

- Simple ZOOM mode (Support for both normal and reverse scans)

- Applications

- LCD television sets and video cameras

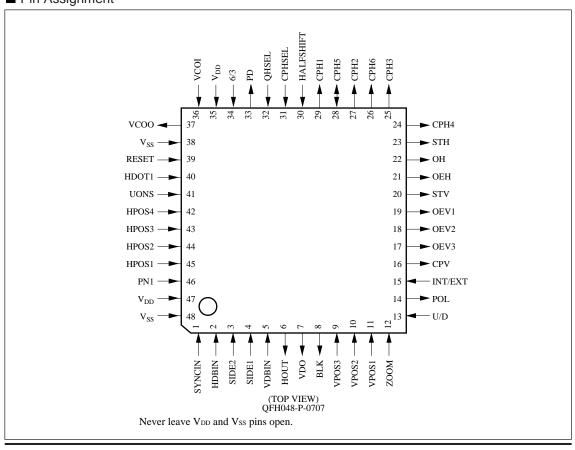

- Pin Assignment

- Support for both single- and two-sided source driver configurations

- Support for both PAL and NTSC systems (decimation mode only for PAL)

- Support for underside on screen display(UONS)

- ON/OFF function for shifting output timing by half a pixel clock cycle

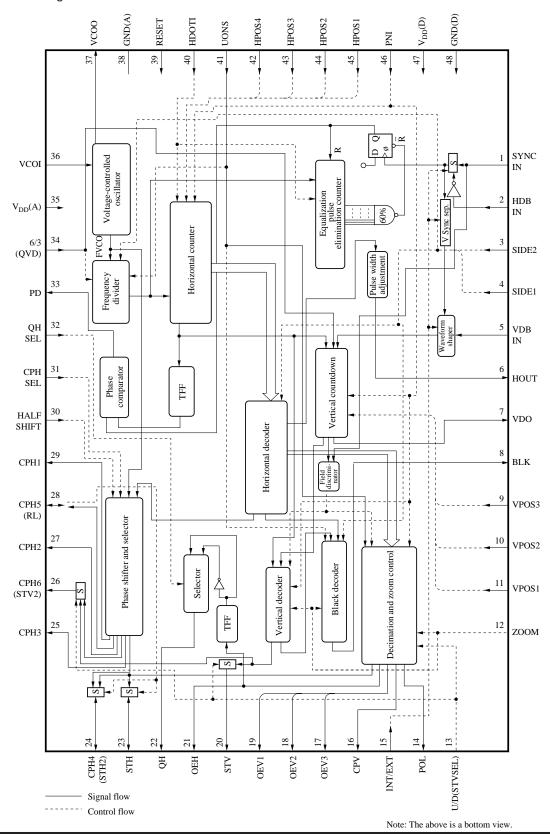

#### ■ Block Diagram

# ■ Pin Descriptions

| Pin No. | Internal<br>Resistor | Symbol  | Pin Name                                                      | I/O | Function Description                                                                                                                                                     |

|---------|----------------------|---------|---------------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | None                 | SYNC IN | Composite color sync input                                    | I   | Composite color sync signal (Sync "H" level)                                                                                                                             |

| 2       | None                 | HDBIN   | Horizontal sync input                                         | I   | • (Sync "L" level)                                                                                                                                                       |

| 3       | PD                   | SIDE2   | Side blackout SIDE2 0 1 0 1                                   | I   |                                                                                                                                                                          |

| 4       | PD                   | SIDE1   | control pins   SIDE1   0   0   1   1       Normal (1) (2) (3) | I   | SIDE ① Double-edged blackout  4:3  On-screen display or single-edge blackout  SIDE ③ SIDE ③ SIDE ③                                                                       |

| 5       | None                 | VDB IN  | Vertical sync input                                           | I   | • (Sync "L" level)                                                                                                                                                       |

| 6       | _                    | HOUT    | Horizontal sync output                                        | 0   | This pin provides the horizontal sync signal obtained by removing the equalization and the cut pulses for vertical synchronization from the composite color sync signal. |

| 7       |                      | VDO     | Vertical sync output                                          | 0   | The pulse from this pin falls with<br>the horizontal sync pulse of pin 6<br>following a falling edge of pin 5<br>pulse and rises after 3-H pulse width.                  |

| 8       | _                    | BLK     | Black signal output                                           | О   | In the side blackout and underside<br>on screen (UONS) modes, this pin<br>provides "H" level pulses<br>synchronized with the black and on-<br>screen timing.             |

| 9       | PD                   | VPOS3   | Vertical display position selection                           | I   | These pins control the position of the STV                                                                                                                               |

| 10      | PD                   | VPOS2   | (These change the STV position.)                              | I   | rising edge after the VDO falling edge.                                                                                                                                  |

| 11      | PD                   | VPOS1   |                                                               | I   | NTSC  • 12H+(7-VPOS1-2 × VPOS2-4 × VPOS3)H  In the ZOOM mode, the interval is 31 H.  PAL  • 24H+(7-VPOS1-2 × VPOS2-4 × VPOS3)H  In the ZOOM mode, the interval is 35 H.  |

| 12      | PD                   | ZOOM    | Zoom control ("H" level selects ZOOM mode.)                   | I   | NTSC  • The controller selects two scan lines every 3H.  PAL  • The controller deactivates decimation and simultaneously selects two scan lines at (6n+1) H.             |

| 13      | PU                   | U/D     | Scan direction control ("H" level selects normal scan.)       | I   | <ul> <li>In the ZOOM mode, the controller switches pulses of OEV1 - OEV3.</li> <li>When HALFSHIFT is at "H" level, this pin functions as STVSEL.</li> </ul>              |

## ■ Pin Descriptions (continued)

| Pin No. | Internal<br>Resistor | Symbol  | Pin Name                                                  | I/O | Function Description                                                                                                                                                                                                                                                                                                     |

|---------|----------------------|---------|-----------------------------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14      | _                    | POL     | Pulses switching image polarity and opposing voltage      | 0   | Pulses sent to chroma IC for<br>controlling image polarity and<br>opposing electrode. The level<br>changes at the rising edge of OEH.                                                                                                                                                                                    |

| 15      | PU                   | INT/EXT | Internal/external synchronization selection               | I   | "H" level selects composite color sync mode     "L" level, separate color sync mode.                                                                                                                                                                                                                                     |

| 16      | _                    | CPV     | Gate driver clock pulses                                  | 0   | Clock pulses for shift registers<br>inside gate driver ICs                                                                                                                                                                                                                                                               |

| 17      | _                    | OEV3    | Gate driver output stage enable pulses                    | 0   | "H" level output from these pins                                                                                                                                                                                                                                                                                         |

| 18      |                      | OEV2    | (Selective stage output:                                  | 0   | forces the gate driver IC output                                                                                                                                                                                                                                                                                         |

| 19      | _                    | OEV1    | "H" level for VgL; "L" level for VgH)                     | 0   | buffers to VgL.  • These pins are used during PAL                                                                                                                                                                                                                                                                        |

|         |                      |         |                                                           |     | decimation and in the ZOOM mode  "L" level input from pin 39  (RESET) forces all three pins to  "H" level.                                                                                                                                                                                                               |

| 20      |                      | STV     | Gate driver scan start pulses                             | 0   | These pulses start the shift registers inside the gate driver ICs. They are 1 H wide and change levels at the falling edge of CPV.                                                                                                                                                                                       |

| 21      | _                    | ОЕН     | Source driver output stage enable pulses                  | О   | • These pulses determine the timing with which the source drivers write image data to the LCD panel. The period is 1 H; the pulse width, 8 µs.                                                                                                                                                                           |

| 22      | _                    | QH      | Color data switching pulses to source drivers             | О   | This pin controls switching of color data to source driver ICs. Pin 32 controls the order.                                                                                                                                                                                                                               |

| 23      | _                    | STH     | Source driver start pulses                                | О   | These pulses start the shift registers inside the<br>source driver ICs. They are 1 CPH wide and<br>change levels at the falling edge of CPH1.                                                                                                                                                                            |

| 24      | _                    | СРН4    | Source driver clock pulses 4/Source driver start pulses 2 | О   | (1) When pins 30 and pins 3 are both "L" level, the controller delivers clock pulses only to CPH1 - CPH3 and drives CPH4 - CPH6 at "L" level.  (2) When pins 30 and pins 3 are both "H" level, the controller alternates the CPH1 - CPH3 outputs between the CPH1 - CPH3 and CPH4 - CPH6 phase clock patterns every 1 H. |

| 25      |                      | СРН3    | Source driver clock pulses 3                              | О   |                                                                                                                                                                                                                                                                                                                          |

| 26      |                      | СРН6    | Source driver clock pulses 6/Source driver start pulses 2 | О   |                                                                                                                                                                                                                                                                                                                          |

| 27      |                      | CPH2    | Source driver clock pulses 2                              | 0   |                                                                                                                                                                                                                                                                                                                          |

| 28      |                      | CPH5    | Source driver clock pulses 5/STH switching signal         | I/O |                                                                                                                                                                                                                                                                                                                          |

| 29      | _                    | CPH1    | Source driver clock pulses 1                              | 0   |                                                                                                                                                                                                                                                                                                                          |

# ■ Pin Descriptions (continued)

| Pin No. | Internal<br>Resistor | Symbol              | Pin Name                                                                           | I/O | Function Description                                                                                                                                                                                                                                                                                                                    |

|---------|----------------------|---------------------|------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 30      | PD                   | HALF<br>SHIFT       | Controlling timing shift of half a pixel clock cycle ("H" level selects shifting.) | Ι   | The pin provides a means of shift output<br>timing for alternate lines by half a pixel<br>clock cycle to drive a delta panel layou                                                                                                                                                                                                      |

| 31      | PD                   | CPH SEL             | CPH pulse phase switching                                                          | I   | When the frequency divider is six—that is,<br>pin 34 is at "H" level—this pin switches<br>between the CPH1 - CPH3 and<br>CPH4 - CPH6 phase clock patterns.                                                                                                                                                                              |

| 32      | PD                   | QH SEL              | QH output switching                                                                | I   | This pin determines the order in which<br>the color data switching pulses (QH<br>from pin 22) to the source driver ICs.                                                                                                                                                                                                                 |

| 33      | _                    | PD                  | Phase comparator output                                                            | О   | This pin provides output from the phase comparator using an edge trigger.                                                                                                                                                                                                                                                               |

| 34      | None                 | 6/3 (QVD)           | Frequency divider doubler ("H" level input doubles the divider ratio from 3 to 6.) | I   | <ul> <li>This pin determines the frequency divider ratio to CPH from FVCO, the fundamental frequency for the voltage-controlled oscillator: 6 for "H" level input and 3 for "L" level input.</li> <li>When pin 30 is at "H" level, this pins serves as the QVD input pin.</li> </ul>                                                    |

| 35      | _                    | V <sub>DD (A)</sub> | Power supply for analog circuits: 3 V                                              |     | This is the power supply for the voltage-<br>controlled oscillator, clock frequency<br>divider, and CPH generator.                                                                                                                                                                                                                      |

| 36      | _                    | VCO I               | VCO input                                                                          | I   | Oscillator signal input for VCO                                                                                                                                                                                                                                                                                                         |

| 37      | _                    | VCO O               | VCO output                                                                         | 0   | Oscillator signal output for VCO                                                                                                                                                                                                                                                                                                        |

| 38      | _                    | GND (A)             | Ground for analog circuits                                                         | _   | This is the ground for the voltage-<br>controlled oscillator, clock frequency<br>divider, and CPH generator.                                                                                                                                                                                                                            |

| 39      | PU                   | RESET               | Reset ("L" level input selects RESET mode.)                                        | Ι   | • This signal resets internal counters, flip-flops, and other components. The pull-up resistance is between 50 k $\Omega$ and 500 k $\Omega$ .                                                                                                                                                                                          |

| 40      | PU                   | HDOTI               | Switching number of panel dots in the horizontal direction                         | I   | <ul> <li>In combination with pins 30 and 34, this pin controls the horizontal frequency divider ratio to match the number of panel dots in the horizontal direction.</li> <li>For delta layouts, dot counts of 480, 600, 960 and 1200 are supported.</li> <li>For striped layouts, dot counts of 960 and 1200 are supported.</li> </ul> |

| 41      | PD                   | UONS                | Controlling underside on<br>screen (UONS) mode ("H" level<br>selects UONS mode.)   | Ι   | This mode switches the bottom 30 lines to an on-screen display mode.                                                                                                                                                                                                                                                                    |

## ■ Pin Descriptions (continued)

| Pin No.        | Internal<br>Resistor | Symbol               | Pin Name                                       | I/O | Function Description                                                                                                                                                                                                                                                                                            |

|----------------|----------------------|----------------------|------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42<br>to<br>45 | PD                   | HPOS4<br>to<br>HPOS1 | Horizontal pixel position (STH position)       | I   | These pins determine the lag between the rising edge of the SYNC IN signal and the STH rising edge: (assuming that the synchronization separation delay is 1.1 μs)  • NTSC:  7.3μs+(15-HPOS1-2 × HPOS2  -4 × HPOS3-3 × HPOS4) ×  0.3125μs  • PAL:  8.0μs+(15-HPOS1-2 × HPOS2  -4 × HPOS3-3 × HPOS4) ×  0.3125μs |

| 46             | PD                   | PN1                  | PAL/NTSC switch ("L" level selects NTSC mode.) | I   | • "H" level input selects PAL mode with decimation at the rate of one line in eight. 1st: (8n+2) H, 2nd: (8n+5) H                                                                                                                                                                                               |

| 47             | _                    | $V_{DD}$             | Power supply for digital circuits: 3 V         | _   | Power supply for digital circuits                                                                                                                                                                                                                                                                               |

| 48             | _                    | GND                  | Ground for digital circuits                    | _   | Ground for digital circuits                                                                                                                                                                                                                                                                                     |

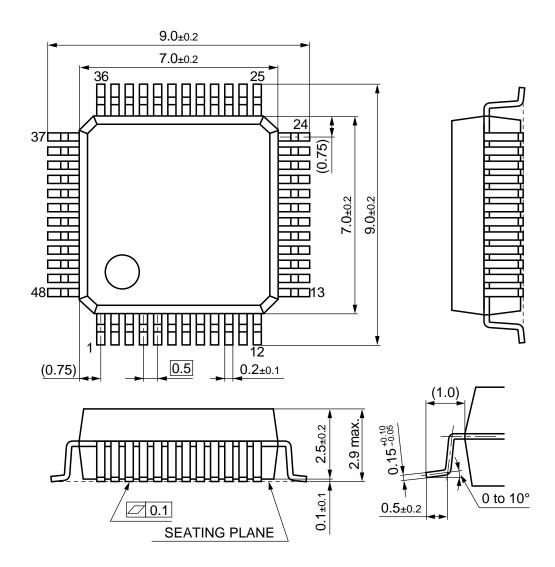

# ■ Package Dimensions (Unit:mm)

QFH048-P-0707