# **MN5571** Gray Scale Font Engine

## Overview

The MN5571 is a high-speed rasterizer that generates bitmapped gray scale font data (bit-mapped font data with gray scale data for each bit) from outline font data (data describing the character outline).

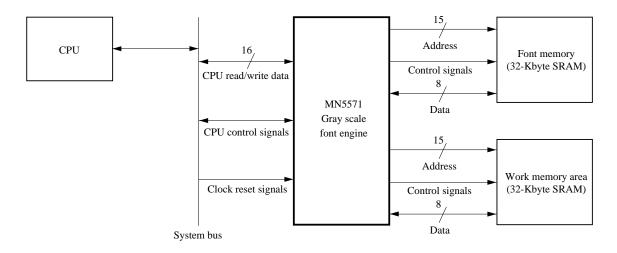

The MN5571 uses two external SRAM devices: one is for a storage area holding the outline data; the other, for a work area holding intermediate results.

The MN5571 achieves its high processing speed with parallel processing of intermediate data generation, gray scale bit map generation, and transfer of the completed bit map data to external devices.

## Features

| ٠ | Gray scale support:     | Choice of 2, 4, 8, or 16 levels                                                                               |

|---|-------------------------|---------------------------------------------------------------------------------------------------------------|

| • | Character sizes:        | Max. $1024 \times 1024$ dots                                                                                  |

|   |                         | The character height and width need not be the same.                                                          |

| • | Throughput:             | Approximately 1000 charac-<br>ters per second<br>(matrix of $16 \times 16$ dots for<br>typical Japanese text) |

| • | Affine transformations: | Slanting, rotation, mirror image, parallelogram                                                               |

| • | Energy-saving modes:    | SLEEP and STOP modes                                                                                          |

| • | Operating power supply  | voltage:                                                                                                      |

ower supply voltage: 3.3 V ± 0.3 V (5 volt input also supported)

## Applications

- Television displays: Internet terminals Set-top boxes

- Game computers Karaoke equipment

- CRT displays: Personal computers

- Word processors

- Liquid crystal displays:

- Portable information terminals Mobile communications terminals Car navigation systems

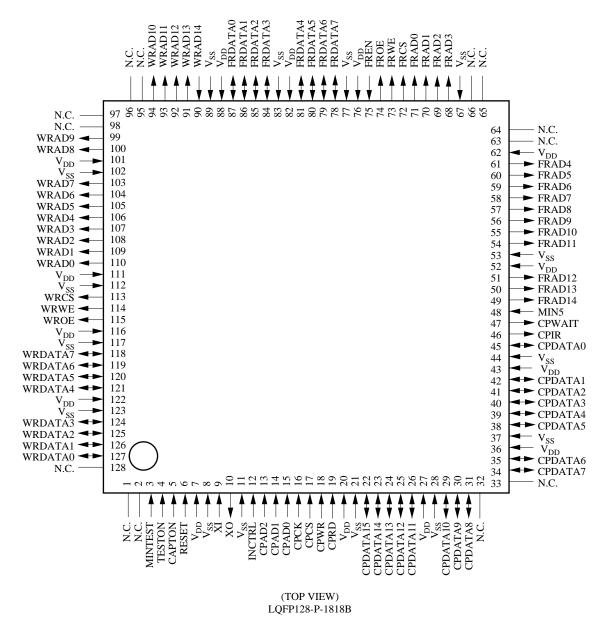

## Pin Assignment

Note: Never leave  $V_{DD}$  and  $V_{SS}$  pins open.

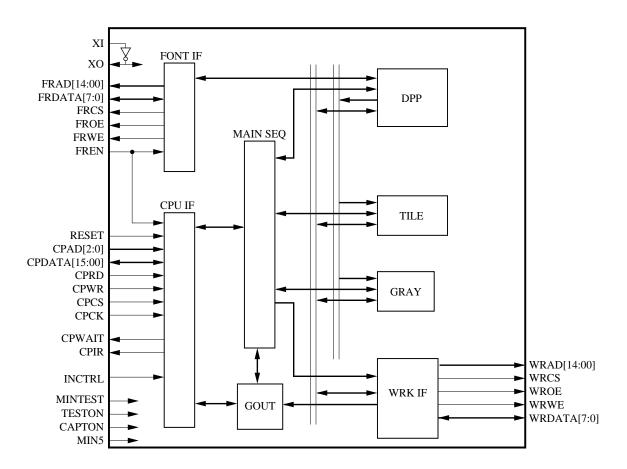

# Block Diagram

## **Block Descriptions**

# Pin Descriptions

| Pin No.              | Symbol          | I/O | Function Description                                        |

|----------------------|-----------------|-----|-------------------------------------------------------------|

| 9                    | XI              | Ι   | Oscillator-cell input (system clock)                        |

| 10                   | XO              | 0   | Oscillator-cell output (system clock)                       |

| 6                    | RESET           | Ι   | System reset signal (negative logic)                        |

| 13 to 15             | CPAD[2:0]       | Ι   | Address signals from host                                   |

| 22 to 26,29 to 31,   | CPDATA[15:00]   | I/O | Data I/O signals to and from host                           |

| 34,35,               |                 |     |                                                             |

| 38 to 42,45          |                 |     |                                                             |

| 47                   | CPWAIT          | 0   | Wait signal to host                                         |

| 46                   | CPIR            | 0   | Interrupt request signal to host                            |

| 19                   | CPRD            | Ι   | Read signal from host (negative logic)                      |

| 18                   | CPWR            | Ι   | Write signal from host (negative logic)                     |

| 17                   | CPCS            | Ι   | Chip select signal from host (negative logic)               |

| 16                   | СРСК            | Ι   | Clock signal from host                                      |

| 12                   | INCTRL          | Ι   | Signal switching to STOP mode                               |

| 49 to 51,54 to 61,   | FRAD[14:00]     | 0   | Address output signals to font RAM                          |

| 68 to 71             |                 |     |                                                             |

| 78 to 81 ,84 to 87   | FRDATA[7:0]     | I/O | Data I/O signals to and from font RAM                       |

| 72                   | FRCS            | 0   | Read enable signal to font RAM (negative logic)             |

| 74                   | FROE            | 0   | Chip select signal to font RAM (negative logic)             |

| 73                   | FRWE            | 0   | Write enable signal to font RAM (negative logic)            |

| 75                   | FREN            | Ι   | Signal indicating presence of font RAM (negative logic)     |

| 90 to 94,99,100,     | WRAD[14:00]     | 0   | Address output signals to work RAM                          |

| 103 to 110           |                 |     |                                                             |

| 118 to 121,          | WRDATA[7:0]     | I/O | Data I/O signals to and from work RAM                       |

| 124 to 127           |                 |     |                                                             |

| 113                  | WRCS            | 0   | Chip select signal to work RAM (negative logic)             |

| 115                  | WROE            | 0   | Read enable signal to work RAM (negative logic)             |

| 114                  | WRWE            | 0   | Write enable signal to work RAM (negative logic)            |

| 3                    | MINTEST         | Ι   | Test signal input (Normally keep this at "L" level.)        |

| 4                    | TESTON          | Ι   | Test signal input (Normally keep this at "L" level.)        |

| 5                    | CAPTON          | Ι   | Test signal input (Normally keep this at "L" level.)        |

| 48                   | MIN5            | Ι   | 5 volt reference (If 5 volt input is not used, this pin has |

|                      |                 |     | same voltage of $V_{DD}$ .)                                 |

| 7 ,20 ,27 ,36 ,43 ,  | V <sub>DD</sub> | Ι   | Power supply pins $(3.3 \text{ V} \pm 0.3 \text{ V})$       |

| 52 ,62 ,76 ,82 ,88 , |                 |     |                                                             |

| 101 ,111 ,116 ,122   |                 |     |                                                             |

| 8 ,11 ,21 ,28 ,      | V <sub>SS</sub> | Ι   | Ground pins (0 V)                                           |

| 37 ,44 ,53 ,67 ,     |                 |     |                                                             |

| 77 ,83 ,89 ,102 ,    |                 |     |                                                             |

| 112 ,117 ,123        |                 |     |                                                             |

This section describes MN5571 functions concretely.

## • Registers

The CPU controls the MN5571 operation by the following registers.

## 1. Address map

CPAD[2:0]:

| (2) | (1) | (0) | Symbol | Contents                  | R/W |

|-----|-----|-----|--------|---------------------------|-----|

| 0   | 0   | 0   | STAT   | Status register           | R   |

| 0   | 0   | 1   | MASK   | Interrupt register        | R/W |

| 0   | 1   | 0   | COMM   | Command register          | R/W |

| 0   | 1   | 1   | DATA   | Data register             | R/W |

| 1   | 0   | 0   | INCNT  | Font memory free register | R   |

| 1   | 0   | 1   |        | Not used                  |     |

| 1   | 1   | 0   |        | Not used                  |     |

| 1   | 1   | 1   | SYCNT  | System control register   | W   |

## 2. Register bits

The following describes the meaning of the bits in the above registers.

#### • STAT register

This register indicates the MN5571's operating status. It is read-only. After reading, it sets all the set bits to "0" and resets the CPIR output pin.

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4  | 3  | 2 | 1  | 0  |

|-----|----|----|----|----|----|----|---|---|----|---|---|----|----|---|----|----|

|     | _  | _  | —  | _  | _  | EM | _ | _ | GO | _ | _ | ER | GE | _ | FE | IN |

IN: The completion of work area initialization sets this bit to "1". Read/write access to the work area is prohibited during initialization.

- FE: The presence of the font memory RAM sets this bit to "1".

- GE: The generation of output data sets this bit to "1".

- ER: An invalid command error occurrence sets this bit to "1".

- GO: Reading gray scale data when the gray scale data buffer is empty sets this bit to "1".

- EM: When the font memory is empty, this bit is set to "1".

- -: Unused

Bit 10 (EM) is set to "1" after a hardware or software reset, the program should always read the STAT register to clear it.

Undefined

#### MASK register

This register controls interrupt signals from the MN5571. It is a read/write register.

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4  | 3  | 2 | 1 | 0  |

|-----|----|----|----|----|----|----|---|---|----|---|---|----|----|---|---|----|

|     | 0  | 0  | 0  | 0  | 0  | EM | 0 | 0 | GO | 0 | 0 | ER | GE | 0 | 0 | IN |

IN: Setting this bit to "1" produces an interrupt when the work memory has been initialized.

GE: Setting this bit to "1" produces an interrupt when output data has been generated.

- ER: Setting this bit to "1" produces an interrupt when the chip encounters an invalid command.

- GO: Setting this bit to "1" produces an interrupt when there is an attempt to read gray scale data from an empty gray scale data buffer.

- EM: Setting this bit to "1" produces an interrupt when the font memory is empty.

- 0: Unused

Reading the status register automatically clears the interrupt. The software's interrupt handler must always read the status register to clear the interrupt source. Always set unused bits to "0."

#### COMM register

This register specifies the MN5571's operating mode. It is a read/write register.

This register accepts the following commands.

| Hex    | Command | Contents               |

|--------|---------|------------------------|

| 0x0001 | TCLR    | Clear work memory area |

| 0x0007 | SRST    | Software reset         |

| 0x8000 | FTIN    | Start font generation  |

The status is shown as NOP (0x0000) right after hardware or software reset while CPU reading the register, and is shown as 0x8001 (EXEC) in generating fonts while CPU reading the register.

#### • DATA register

Writes

The MN5571 uses this register for data I/O. It is a read/write register.

Font data write

Register function depends on the contents of the COMM register.

| Bit | 15    | 14  | 13 | 12 | 11 | 10      | 9       | 8        | 7      | 6 | 5 | 4 | 3    | 2       | 1 | 0 |  |

|-----|-------|-----|----|----|----|---------|---------|----------|--------|---|---|---|------|---------|---|---|--|

|     |       |     |    |    |    |         | Re      | ad/write | e data |   |   |   |      |         |   |   |  |

|     |       |     |    |    |    |         |         |          |        |   |   |   |      |         |   |   |  |

|     |       | COM | 1M |    |    |         |         |          |        |   |   |   |      |         |   |   |  |

| R/W |       |     |    |    |    | EXE     | C(0x8   | 001)     |        |   |   |   | Othe | er valu | е |   |  |

|     | Reads | 5   |    |    | G  | ray sca | ale dat | a read   |        |   |   |   | Unc  | lefined |   |   |  |

#### INCNT register

This register indicates the amount of free font-memory. It is read only.

| Bit | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----|----|----|----|----|----|----|---|----|----|---|---|---|---|---|---|---|

|     | _  |    |    |    |    |    |   | FR | EE |   |   |   |   |   |   |   |

The field FREE indicates the number of words (16 bits) available for storing font data.

• System control register (SYCNT)

This register controls the MN5571's power-saving mode. It is write only.

This register accepts the following commands.

Reading this register leads to unpredictable operation (not guaranteed).

| Hex      | Command | Contents                                               |  |

|----------|---------|--------------------------------------------------------|--|

| 0xAAAA   | CKSP    | Switches into SLEEP mode (stopping internal clock)     |  |

| 0x0000   | CKST    | Switches out of SLEEP mode (restarting internal clock) |  |

| (0xAAAA) |         |                                                        |  |

Always wait ten clock cycles when switching into or out of SLEEP mode.

- Data Formats for Input Font Data and Output Gray Scale Data

- 1. Data Format for Input Font Data

The MN5571 expects input font data in the following format.

## 2. Data Formats for Output Gray Scale Data

The MN5571 delivers gray scale data in the following formats.

| Ora | ly SC |      | ata 1 | orme | 101 | 4, 0, | 01 10 |   | 1015 |      |       |   |     |      |       |   |        |

|-----|-------|------|-------|------|-----|-------|-------|---|------|------|-------|---|-----|------|-------|---|--------|

|     | 15    | 14   | 13    | 12   | 11  | 10    | 9     | 8 | 7    | 6    | 5     | 4 | 3   | 2    | 1     | 0 |        |

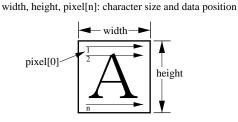

| 0   | mo    | ode  | -     |      |     | wi    | dth   |   |      | _    |       |   | hei | ight |       |   |        |

| 1   |       | pixe | el[0] |      |     | pixe  | el[1] |   |      | pixe | el[2] |   |     | pixe | el[3] |   |        |

| 2   |       | pixe | el[4] |      |     | pixe  | el[5] |   |      | pixe | el[6] |   |     | pixe | el[7] |   | Line ( |

| 3   |       | pixe | el[8] |      |     | pixe  | el[9] |   |      | pixe | l[10] |   | _   | _    | _     | - | V      |

| 4   |       | pixe | 1[11] |      |     | pixe  | 1[12] |   |      | pixe | l[13] |   |     | pixe | l[14] |   | Line 1 |

|     |       |      |       |      |     |       |       |   |      |      |       |   |     |      |       |   | V      |

#### Gray Scale Data Format for 4, 8, or 16 Levels

Gray Scale Data Format for 2 Levels

|   | 15 | 14     | 13    | 12    | 11    | 10  | 9     | 8      | 7      | 6      | 5 | 4 | 3   | 2   | 1 | 0 |

|---|----|--------|-------|-------|-------|-----|-------|--------|--------|--------|---|---|-----|-----|---|---|

| 0 | mo | ode    | _     |       |       | wie | dth   |        |        | _      |   |   | hei | ght |   |   |

| 1 |    |        |       |       |       | I   | oixel | [0] to | o pixe | el[15] |   |   |     |     |   |   |

| 2 | p  | ixel[  | 16] t | o pix | el[21 | ]   | _     | _      | -      | -      | _ | - | _   | _   | _ | _ |

| 3 |    |        |       |       |       | р   | ixel[ | 22] t  | o pix  | el[37  | ] |   |     | -   |   |   |

| 4 | p  | oixel[ | 38] t | o pix | el[43 | 5]  | _     | _      | _      | _      | _ | _ | _   | _   | _ | _ |

|   |    |        |       |       |       |     |       |        |        |        |   |   |     |     |   |   |

Description of Gray Scale Data Format

#### mode: gray scale

- 3: 2 levels 2: 4 levels 1: 8 levels

- 0: 16 levels

#### • Power-saving standby modes

Two power-saving standby modes are supported: SLEEP and STOP. The SLEEP mode conserves power by turning off the internal clock signal CLK. The STOP mode produces a complete stop by shutting down the oscillator circuit. It also cuts off the input pins to the host to prevent leakage current due to input penetration current.

# Operating Procedure

# • Overview

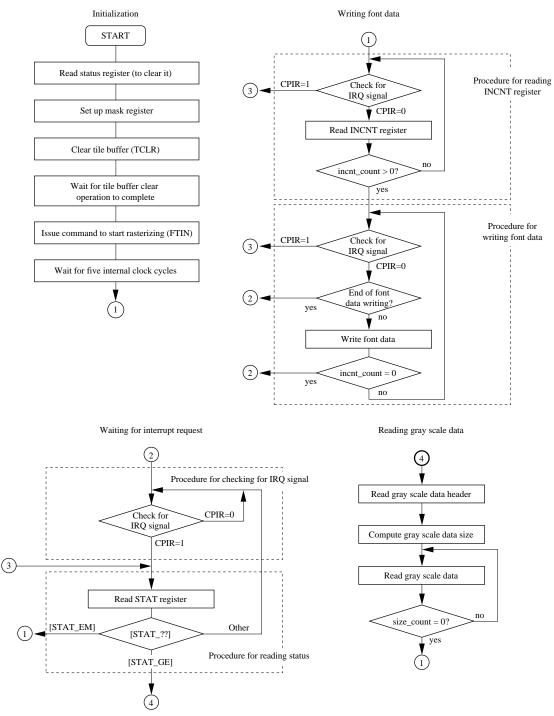

The procedure for operating the MN5571 is divided into four main steps.

• Initialization

This step, which is performed only once after a hardware or software reset, consists of clearing the MN5571's internal registers and the memory and giving the MN5571 the command to start rasterizing.

• Writing font data

The font data for the characters to be rasterized are transferred to the MN5571.

• Waiting for interrupt request

This step waits for the MN5571 to indicate that it is ready for output.

• Reading gray scale data

This step outputs the gray scale data that the MN5571 has generated.

#### Operational flow

## • Examples of Operation

This section gives two examples in different procedures.

## 1. With Font Memory RAM

This example shows the general procedure for using the rasterizer together with an external RAM for font data. Driving the FREN pin at "L" level configures the MN5571 for this mode of operation. The following flowchart assumes software control of the MN5571.

#### Description for flowchart

The following is a detailed description of the flowchart.

#### (1) Initialization

This step is performed only once after a hardware or software reset.

If there is a font memory RAM attached, the FREN pin must be at "L" level before the hardware reset.

• Read status register

A font memory RAM attached is confirmed.

$STAT_FE = "1"$

The status register is read and that the FE bit is "1" is checked.

After a hardware or software reset, always the STAT register is read to initialize it.

• Set up mask register

The mask register is set up to enable the desired interrupts.

$MASK \leftarrow 16'b0000\_0100\_1000\_1001;$ (STAT\_EM, STAT\_GO, STAT\_GE, STAT\_IN)

• Clear tile buffer

The TCLR instruction code is written to the COMM register to initiate clearing of the tile buffer.

$\text{COMM} \gets \text{TCLR}$

• Wait for tile buffer clear operation to complete

The IN bit in the STAT register indicates the completion of a tile buffer clear operation.

$STAT_IN = "1"$

This example sets the IN bit in the MASK register and waits for the corresponding interrupt request.

When accepting the interrupt request, always the status register is read to clear the interrupt request.

Do not access the command register while the chip is clearing the tile buffer.

• Issue command to start rasterizing

The FTIN instruction code is written to the COMM register to start rasterizing.

$\text{COMM} \gets \text{FTIN}$

• Wait for five internal clock cycles

To ensure circuit stability, do not access the MN5571 command register within 5 internal clock cycles after writing the FTIN instruction code.

#### (2) Writing font data

The following is the procedure for writing font data to the MN5571.

(a) Procedure for reading INCNT register

• Check for IRQ signal

IRQ signal is checked. If the CPIR bit is "1," the status register is read.

• Read INCNT register

The number of words available for storing font data is read from the INCNT register.

$<\!\!<\!\!\text{incnt\_count} >\!\!> \leftarrow \text{INCNT}$

This number indicates how much space is available for font data in the font memory.

• INCNT contents check

If the INCNT register is "0," the register contents are read again.

#### (b) Procedure for writing font data

- Check for IRQ signal

- Interrupt requests are checked. If the CPIR bit is "1," the status register is read.

- Check word count for font data to be written

When the count reaches zero, the state is switched to waiting for a change in the IRQ signal.

• Write font data

One word of font data is written to the DATA register.

$\text{DATA} \leftarrow << \text{font data} >>$

<< incnt\_count  $>> \leftarrow <<$  incnt\_count >> - 1

• INCNT check

When the count reaches zero, the state is switched to waiting for a change in the IRQ signal.

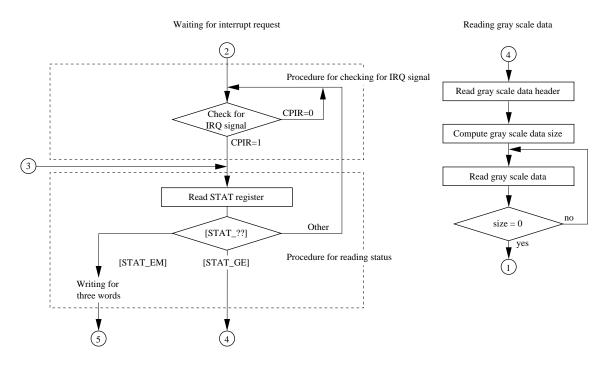

- (3) Waiting for IRQ signal change

- Checking for IRQ signal

Wait for a change in the IRQ signal generated in the status register.

• Read STAT register

STAT register is read.

• Branch by status register bit

If the STAT\_EM bit is "1," the state goes to read the contents of the INCNT register. If the STAT\_GM bit is "1," it goes to read the gray scale data.

Otherwise, it returns to waiting for a change in the IRQ signal.

#### (4) Reading gray scale data

This step reads the gray scale data from the MN5571.

• Read gray scale data header

The ghead, the gray scale data header is read from the DATA register.

<< ghead  $>> \leftarrow$  DATA

• Compute gray scale data size

Compute the size of the gray scale data set using the following procedure.

```

mode = ghead[15:14];

width = ghead[12:7];

height = ghead[5:0];

if(mode=3{

size = (width/4+((width%4)!=0))*height;

}else{

size = (width/16+((width%16)!=0))*height;

}

```

• Read gray scale data

Numbers of data expressed by contents of "size" are read from DATA register.

```

<< gray_scale_data >> \leftarrow DATA

```

```

<< size_count >> \leftarrow << size_count >> - 1

```

Check size

When all the gray scale data has been read, the contents of the INCNT register are read.

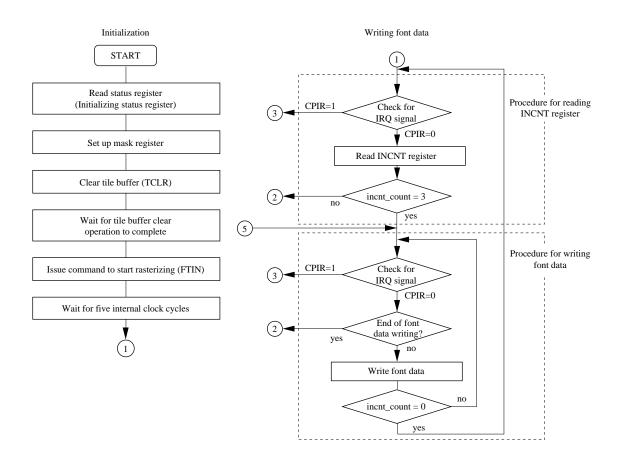

## 2. Chip without Font Memory RAM

This example shows the general procedure for using the rasterizer without an external RAM for font data. Driving the FREN pin at "H" level configures the MN5571 for this mode of operation. The following flow-chart assumes software control of the MN5571.

Description for flowchart

The following is a detailed description of the flowchart.

(1) Initialization

This step is performed only once after a hardware or software reset.

If there is no font memory RAM attached, the FREN pin must be at "H" level before the hardware reset.

• Read status register

No font memory RAM attached is confirmed.

$STAT_FE = "0"$

The status register is read and the state that the FE bit is "0" is checked.

After a hardware or software reset, the STAT register is always read to initialize it.

• Set up mask register

The mask register is set up to enable the desired interrupts.

$MASK \leftarrow 16'b0000\_0100\_1000\_1001;$ (STAT\_EM, STAT\_GO, STAT\_GE, STAT\_IN)

• Clear tile buffer

The TCLR instruction code is written to the COMM register to initiate clearing of the tile buffer. COMM ← TCLR

• Wait for tile buffer clear operation to complete

The IN bit in the STAT register indicates the completion of a tile buffer clear operation.

$STAT_IN = "1"$

This example sets the IN bit in the MASK register and waits for the corresponding interrupt request. When accepting the interrupt request, the status register is always read to clear the interrupt request. Do not access the command register while the chip is clearing the tile buffer. • Issue command to start rasterizing

The FTIN instruction code is written to the COMM register to start rasterizing.

$\text{COMM} \leftarrow \text{FTIN}$

• Wait for five internal clock cycles

To ensure circuit stability, do not access the MN5571 command register within 5 internal clock cycles after writing the FTIN instruction code.

(2) Writing font data

The following is the procedure for writing font data to the MN5571.

- (a) Procedure for reading INCNT register

- Check for IRQ signal

Interrupt request is checked. If the CPIR bit is "1," the status register is read.

• Read INCNT register

The number of words available for storing font data is read from the INCNT register.

$<\!\!<\!\!\text{incnt\_count} \!>\!\!> \leftarrow \text{INCNT}$

This number indicates how much space is available for font data (max. 3).

• INCNT check

If the INCNT register contains a number other than three, the state goes to wait for a change in the IRQ signal.

#### (b) Procedure for writing font data

• Check for IRQ signal

Interrupt requests are checked. If the CPIR bit is "1," the status register is read.

• Check word count for font data to be written

When the count reaches zero, the state is switched to waiting for a change in the IRQ signal.

• Write font data

One word of font data to the DATA register is written.

```

DATA \leftarrow << font \ data >>

```

$<\!\!<\!\!\text{incnt\_count}>\!\!> \leftarrow <\!\!<\!\!\text{incnt\_count}>\!\!> - 1$

• INCNT check

When the count reaches zero, the state returns to reading the contents of the INCNT register.

#### (3) Waiting for interrupt request

Checking for IRQ signal

The state waits for a change in the IRQ signal generated by a change in the status register.

• Read STAT register

STAT register is read.

• Branch by status register bit

If the STAT\_EM bit is "1," there is room to write three words of font data, so the state is switched to writing font data. If the STAT\_GE bit is "1," the state goes to read the gray scale data.

Otherwise, it returns to waiting for a change in the IRQ signal.

(4) Reading gray scale data

This step reads the gray scale data from the MN5571.

- Read gray scale data header

- The ghead, the gray scale data header is read from the DATA register.

$<< \texttt{ghead} >> \leftarrow \mathsf{DATA}$

• Compute gray scale data size

Compute the size of the gray scale data set using the following procedure.

```

mode = ghead[15:14];

width = ghead[12:7];

height = ghead[5:0];

if(mode<3{

size = (width/4+((width%4)!=0))*height;

}else{

size = (width/16+((width%16)!=0))*height;

}

```

• Read gray scale data

Numbers of data expressed by contents of "size" are read from DATA register.

```

<<gray_scale_data>> \leftarrow DATA

```

<<size\_count>>  $\leftarrow$  <<size\_count>> -1

Check size

When all the gray scale data has been read, the contents of the INCNT register are read.

#### Additional Notes

• The most efficient timing for writing font data is once every 400 ns\* (8 internal clock cycles).

• The most efficient timing for reading gray scale data is once every 750 ns\* (15 internal clock cycles).

Note: \* At a system clock frequency of 20 MHz (an internal clock cycle time of 50 ns).

## External Interface Specifications

The following are the I/O timing specifications for the chip's external interfaces.

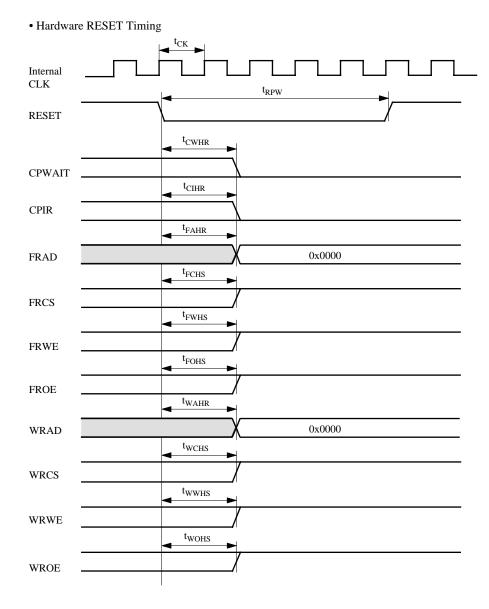

#### 1. Hardware reset

## (a) Timing chart

The RESET signal is not synchronized with the internal clock.

# (b) AC characteristics

| Parameter                    | Symbol            | min               | max | Unit |

|------------------------------|-------------------|-------------------|-----|------|

| Internal clock cycle         | t <sub>CK</sub>   | 40                | _   | ns   |

| RESET pulse width            | t <sub>RPW</sub>  | $t_{CK} \times 1$ |     | ns   |

| CPWAIT reset validation time | t <sub>CWHR</sub> | _                 | 40  | ns   |

| CPIR reset validation time   | t <sub>CIHR</sub> | _                 | 40  | ns   |

| FRAD reset validation time   | t <sub>FAHR</sub> | _                 | 40  | ns   |

| FRCS set validation time     | t <sub>FCHS</sub> | —                 | 40  | ns   |

| FRWE set validation time     | t <sub>FWHS</sub> | _                 | 40  | ns   |

| FROE set validation time     | t <sub>FOHS</sub> | _                 | 40  | ns   |

| WRAD reset validation time   | t <sub>WAHR</sub> | _                 | 40  | ns   |

| WRCS set validation time     | t <sub>WCHS</sub> | _                 | 40  | ns   |

| WRWE set validation time     | t <sub>WWHS</sub> |                   | 40  | ns   |

| WROE set validation time     | t <sub>WOHS</sub> | _                 | 40  | ns   |

Note: The load capacity for the host interface is 30 pF; for the SRAM interface, 20 pF.

# 2. Host interface

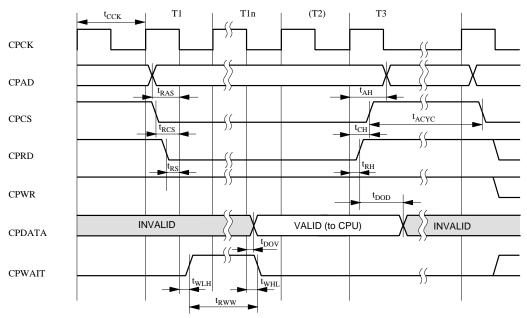

## (a) Timing charts

CPU Read Timing

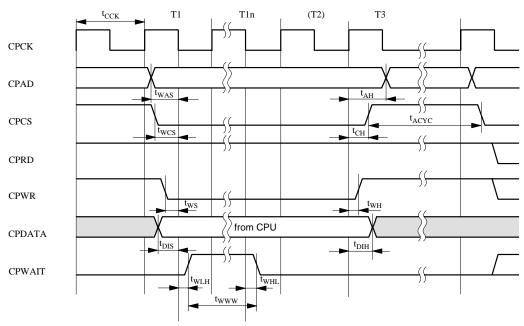

• CPU Write Timing

# (b) AC characteristics

• Read cycle

| Parameter                                               | Symbol            | min                | max | Unit |

|---------------------------------------------------------|-------------------|--------------------|-----|------|

| CPU clock cycle                                         | t <sub>CCK</sub>  | 40                 |     | ns   |

| Internal clock cycle                                    | t <sub>CK</sub>   | 40                 |     | ns   |

| CPAD setup time relative to falling edge of CPCK        | t <sub>RAS</sub>  | 10                 |     | ns   |

| CPCS setup time relative to falling edge of CPCK        | t <sub>RCS</sub>  | 10                 |     | ns   |

| CPRD setup time relative to falling edge of CPCK        | t <sub>RS</sub>   | 10                 |     | ns   |

| CPWAIT rise time relative to falling edge of CPCK       | t <sub>WLH</sub>  | —                  | 22  | ns   |

| CPAD hold time relative to rising edge of CPCK          | t <sub>AH</sub>   | 0                  |     | ns   |

| CPCS hold time relative to rising edge of CPCK          | t <sub>CH</sub>   | 0                  |     | ns   |

| CPRD hold time relative to rising edge of CPCK          | t <sub>RH</sub>   | 0                  |     | ns   |

| CPDATA validation time relative to falling edge of CPCK | t <sub>DOV</sub>  |                    | 0   | ns   |

| CPDATA delay time relative to rising edge of CPRD       | t <sub>DOD</sub>  | 0                  |     | ns   |

| CPWAIT fall time relative to falling edge of CPCK       | t <sub>WHL</sub>  | _                  | 22  | ns   |

| CPCS fall time relative to rising edge of CPCS          | t <sub>ACYC</sub> | $t_{CK} \times 2$  |     | ns   |

| Width of read cycle CPWAIT "H" pulse                    | t <sub>RWW</sub>  | $t_{CCK} \times 3$ | _   | ns   |

Note: The load capacity for the host interface is 30 pF.

#### • Write cycle

| Parameter                                          | Symbol            | min                | max | Unit |

|----------------------------------------------------|-------------------|--------------------|-----|------|

| CPU clock cycle                                    | t <sub>CCK</sub>  | 40                 |     | ns   |

| Internal clock cycle                               | t <sub>CK</sub>   | 40                 |     | ns   |

| CPAD setup time relative to falling edge of CPCK   | t <sub>WAS</sub>  | 10                 |     | ns   |

| CPCS setup time relative to falling edge of CPCK   | t <sub>WCS</sub>  | 10                 |     | ns   |

| CPWR setup time relative to falling edge of CPCK   | t <sub>ws</sub>   | 10                 |     | ns   |

| CPDATA setup time relative to falling edge of CPCK | t <sub>DIS</sub>  | 10                 |     |      |

| CPWAIT rise time relative to rising edge of CPCK   | t <sub>WLH</sub>  | _                  | 22  | ns   |

| CPAD hold time relative to rising edge of CPCK     | t <sub>AH</sub>   | 0                  |     | ns   |

| CPCS hold time relative to rising edge of CPCK     | t <sub>CH</sub>   | 0                  |     | ns   |

| CPWR hold time relative to rising edge of CPCK     | t <sub>WH</sub>   | 0                  |     | ns   |

| CPDATA hold time relative to rising edge of CPCK   | t <sub>DIH</sub>  | _                  | 0   | ns   |

| CPWAIT fall time relative to falling edge of CPCK  | t <sub>WHL</sub>  | _                  | 22  | ns   |

| CPCS fall time relative to rising edge of CPCS     | t <sub>ACYC</sub> | $t_{CK} \times 2$  |     | ns   |

| Width of write cycle CPWAIT "H" pulse              | t <sub>WWW</sub>  | $t_{CCK} \times 2$ |     | ns   |

Note: The load capacity for the host interface is 30 pF.

## 3. Font memory interface

#### (a) Timing charts

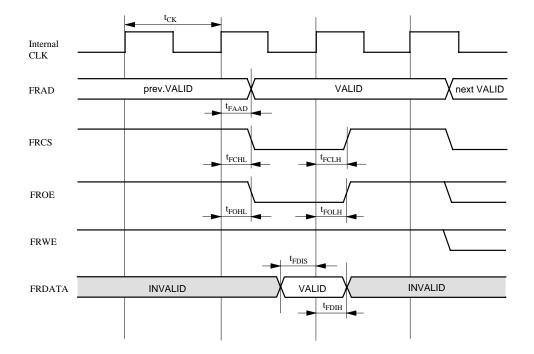

• FONT MEMORY Read Timing

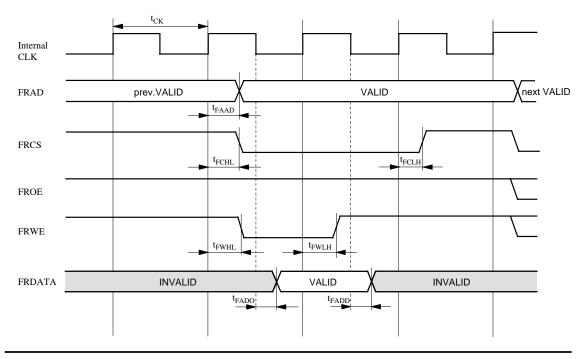

#### • FONT MEMORY Write Timing

## Panasonic

#### (b) AC characteristics

#### Read cycle

| Parameter                                        | Symbol            | min | max          | Unit |

|--------------------------------------------------|-------------------|-----|--------------|------|

| Internal clock cycle                             | t <sub>CK</sub>   | 40  |              | ns   |

| FRAD delay time relative to rising edge of CLK   | t <sub>FADD</sub> | _   | 20           | ns   |

| FRCS fall time relative to rising edge of CLK    | t <sub>FCHL</sub> | _   | 13           | ns   |

| FROE fall time relative to rising edge of CLK    | t <sub>FOHL</sub> | _   | 13           | ns   |

| FRCS rise time relative to rising edge of CLK    | t <sub>FCLH</sub> | _   | $6 + \alpha$ | ns   |

| FROE rise time relative to rising edge of CLK    | t <sub>FOLH</sub> | _   | 13           | ns   |

| FRDATA setup time relative to rising edge of CLK | t <sub>FDIS</sub> | 6   |              | ns   |

| FRDATA hold time relative to rising edge of CLK  | t <sub>FDIH</sub> | 12  |              | ns   |

• Write cycle

| Parameter                                              | Symbol            | min | max          | Unit |

|--------------------------------------------------------|-------------------|-----|--------------|------|

| Internal clock cycle                                   | t <sub>CK</sub>   | 40  |              | ns   |

| FRAD delay time relative to rising edge of CLK         | t <sub>FADD</sub> |     | 20           | ns   |

| FRCS fall time relative to rising edge of CLK          | t <sub>FCHL</sub> |     | 13           | ns   |

| FRWE fall time relative to rising edge of CLK          | t <sub>FWHL</sub> |     | 13           | ns   |

| FRCS rise time relative to rising edge of CLK          | t <sub>FCLH</sub> |     | $6 + \alpha$ | ns   |

| FRWE rise time relative to rising edge of CLK          | t <sub>FWLH</sub> |     | 14           | ns   |

| FRDATA validation time relative to falling edge of CLK | t <sub>FADO</sub> | _   | 12           | ns   |

| FRDATA delay time relative to falling edge of CLK      | t <sub>FADD</sub> |     | 8            | ns   |

Notes

1: The load capacity for the SRAM interface is 20 pF.

2: Because the FRCS pin uses N-channel open drain output, the pull-up time,  $\alpha$ , depends on the value of the external pull-up resistor.

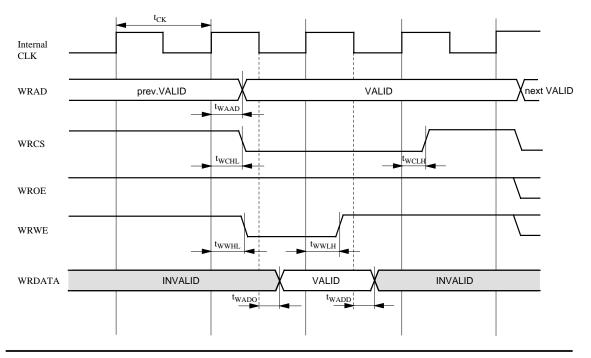

### 4. Work memory interface

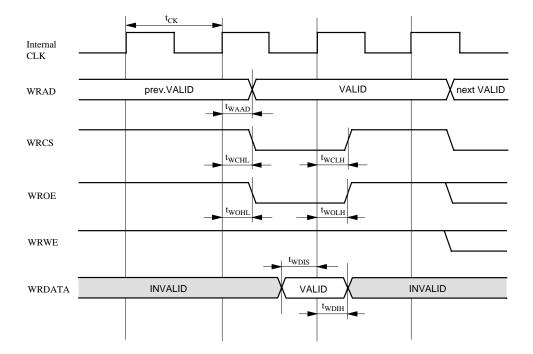

- (a) Timing charts

- WORK MEMORY Read Timing

#### • WORK MEMORY Write Timing

#### Panasonic

#### (b) AC characteristics

#### Read cycle

| Parameter                                        | Symbol            | min | max          | Unit |

|--------------------------------------------------|-------------------|-----|--------------|------|

| Internal clock cycle                             | t <sub>CK</sub>   | 40  |              | ns   |

| WRAD delay time relative to rising edge of CLK   | t <sub>WADD</sub> | _   | 20           | ns   |

| WRCS fall time relative to rising edge of CLK    | t <sub>WCHL</sub> | _   | 13           | ns   |

| WROE fall time relative to rising edge of CLK    | t <sub>WOHL</sub> | —   | 13           | ns   |

| WRCS rise time relative to rising edge of CLK    | t <sub>WCLH</sub> | _   | $6 + \alpha$ | ns   |

| WROE rise time relative to rising edge of CLK    | t <sub>WOLH</sub> | _   | 13           | ns   |

| WRDATA setup time relative to rising edge of CLK | t <sub>WDIS</sub> | 6   |              | ns   |

| WRDATA hold time relative to rising edge of CLK  | t <sub>WDIH</sub> | 12  |              | ns   |

• Write cycle

| Parameter                                              | Symbol            | min | max          | Unit |

|--------------------------------------------------------|-------------------|-----|--------------|------|

| Internal clock cycle                                   | t <sub>CK</sub>   | 40  |              | ns   |

| WRAD delay time relative to rising edge of CLK         | t <sub>WADD</sub> |     | 20           | ns   |

| WRCS fall time relative to rising edge of CLK          | t <sub>WCHL</sub> |     | 13           | ns   |

| WRWE fall time relative to rising edge of CLK          | t <sub>WWHL</sub> |     | 13           | ns   |

| WRCS rise time relative to rising edge of CLK          | t <sub>WCLH</sub> |     | $6 + \alpha$ | ns   |

| WRWE rise time relative to rising edge of CLK          | t <sub>WWLH</sub> |     | 14           | ns   |

| WRDATA validation time relative to falling edge of CLK | t <sub>WADO</sub> | _   | 12           | ns   |

| WRDATA delay time relative to falling edge of CLK      | t <sub>WADD</sub> |     | 8            | ns   |

Notes

1: The load capacity for the SRAM interface is 20 pF.

2: Because the FRCS pin uses N-channel open drain output, the pull-up time,  $\alpha$ , depends on the value of the external pull-up resistor.

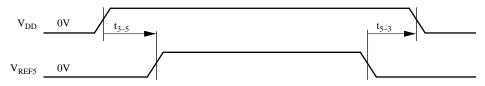

## Absolute Maximum Ratings

V<sub>SS</sub>=0V

| Parameter                                       | Symbol            | Ratings                           | Unit |

|-------------------------------------------------|-------------------|-----------------------------------|------|

| Power supply voltage                            | V <sub>DD</sub>   | -0.3 to +4.6                      | V    |

| 5 volt reference voltage *1                     | V <sub>REF5</sub> | - 0.3 to +5.7                     | V    |

| Input pin voltage (except TYPE-* pins)          | VI                | -0.3 to V <sub>DD</sub> +0.3      | V    |

| Input pin voltage (except pins labeled TYPE-A)  | V <sub>I5</sub>   | - 0.3 to 6.0*2                    | V    |

| Output pin voltage (except TYPE-* pins)         | Vo                | -0.3 to V <sub>DD</sub> +0.3      | V    |

| Output pin voltage (except pins labeled TYPE-A) | V <sub>O5</sub>   | - 0.3 to 6.0*2                    | V    |

| Output pin voltage (except pins labeled TYPE-B) | V <sub>O5</sub>   | - 0.3 to V <sub>REF5</sub> +0.3*2 | V    |

| Output current (pins labeled TYPE-HL2)          | I <sub>O</sub>    | ±6                                | mA   |

| Output current (pins labeled TYPE-HL4)          | I <sub>O</sub>    | ±12                               | mA   |

| Output current (pins labeled TYPE-L4)           | I <sub>OL</sub>   | +12                               | mA   |

| Power Dissipation                               | P <sub>D</sub>    | 1340                              | mW   |

| Operating ambient temperature                   | T <sub>opr</sub>  | -40 to 70                         | °C   |

| Storage temperature                             | T <sub>stg</sub>  | -55 to 150                        | °C   |

Notes

\*1: The rising and falling edges in the power supply sequence must satisfy the requirements outlined in the following timing chart.

Both  $t_{3-5}$  and  $t_{5-3}$  must be greater than or equal to zero. Both  $V_{DD}$  and  $V_{REF5}$  must have smooth transitions.

\*2: If  $V_{DD} \le 1.4$  V, the range is -0.3 to 4.6 V.

| *3: TYPE-A pins: | CPAD0 to 2, CPCK, CPCS, CPRD, CPWR, FRCS, FREN, WRCS, RESET, INCTRL             |

|------------------|---------------------------------------------------------------------------------|

| TYPE-B pins:     | CPDATA0 to 15, FRDATA0 to 7, WRDATA0 to 7                                       |

| TYPE-HL2 pins:   | FRAD0 to 14, WRAD0 to 14                                                        |

| TYPE-HL4 pins:   | CPIR, FROE, FRWE, WROE, WRWE, CPDATA0 to 15, CPWAIT, FRDATA0 to 7, WRDATA0 to 7 |

| TYPE-L4 pins:    | FRCS, WRCS                                                                      |

| TYPE-* pins mea  | an TYPE-A, TYPE-B, TYPE-HL2, TYPE-HL4, and TYPE-L4 pins.                        |

- \*4: The above ratings represent the maximum values that may be applied without damaging the chip, not the limits for guaranteed operation.

- \*5: Directly connect all  $V_{\text{DD}}$  pins to external power supplies and all  $V_{\text{SS}}$  pins to the ground.

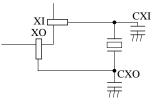

# Recommended Operating Conditions

| V <sub>SS</sub> =0 | V |

|--------------------|---|

|--------------------|---|

| Parameter                | Symbol            | Conditions                 | min  | typ | max  | Unit |

|--------------------------|-------------------|----------------------------|------|-----|------|------|

| Power supply voltage     | V <sub>DD</sub>   |                            | 3.0  | 3.3 | 3.6  | v    |

| 5 volt reference voltage | V <sub>REF5</sub> |                            | 4.75 | 5.0 | 5.25 | V    |

| Rise time for input      | t <sub>r</sub>    |                            | 0    |     | 100  | ns   |

| Fall time for input      | t <sub>f</sub>    |                            | 0    |     | 100  |      |

| Oscillation frequency    | f <sub>OSC1</sub> | 25MHz Xtal                 |      | 25  |      | MHz  |

| Recommended value for    | C <sub>XI7</sub>  | V <sub>DD</sub> =3.3V      |      | 47  |      | pF   |

| external capacitance     | C <sub>XO7</sub>  | Built-in feedback resistor |      | 47  |      | 1    |

| Ambient temperature      | Та                |                            | 0    |     | 70   | °C   |

Note: Because oscillation characteristics depend on such factors as oscillator model and external capacitance, always consult the oscillator manufacturer when selecting components.

# ■ Input/Output Capacitance

| Parameter   | Symbol           | Conditions          | min | typ | max | Unit |

|-------------|------------------|---------------------|-----|-----|-----|------|

| Input pins  | C <sub>IN</sub>  | $V_{DD} = V_I = 0V$ |     | 7   | 15  | pF   |

| Output pins | C <sub>OUT</sub> | f=1MHz, Ta=25°C     |     | 7   | 15  | pF   |

| I/O pins    | C <sub>I/O</sub> |                     |     | 7   | 15  | pF   |

# Electrical Characteristics

$V_{DD}{=}3.0$  to 3.6V,  $V_{REF5}{=}4.75$  to 5.25V,  $V_{SS}{=}0.00V,$   $f_{TEST}{=}25MHz,$  Ta=0 to 70°C

| Parameter                     | Symbol            | Conditions                                         | min                 | typ | max                 | Unit |

|-------------------------------|-------------------|----------------------------------------------------|---------------------|-----|---------------------|------|

| Quiescent supply current      | I <sub>DDS</sub>  | $V_{I}$ (pull-up) = open                           |                     |     | 50                  | μΑ   |

|                               |                   | $V_{I}$ (pull-down) = open                         |                     |     |                     |      |

|                               |                   | $V_{I}\left(XI\right)=V_{DD}^{*1}$                 |                     |     |                     |      |

|                               |                   | Other input pins and I/O pins                      |                     |     |                     |      |

|                               |                   | in the high-impedance state                        |                     |     |                     |      |

|                               |                   | are all simultaneously                             |                     |     |                     |      |

|                               |                   | connected to either the $V_{SS}$                   |                     |     |                     |      |

|                               |                   | or V <sub>DD</sub> level.                          |                     |     |                     |      |

| 5 volt reference power supply | I <sub>LRF5</sub> |                                                    |                     |     | ±20                 | μΑ   |

| V <sub>REF5</sub> (MIN5 pin)  |                   |                                                    |                     |     |                     |      |

| input leakage current         |                   |                                                    |                     |     |                     |      |

| Operating supply current      | I <sub>DDO</sub>  | $V_I = V_{DD}$ or $V_{SS}$                         |                     | 50  | 100                 | mA   |

|                               |                   | f=25MHz                                            |                     |     |                     |      |

|                               |                   | V <sub>DD</sub> =3.3V Outputs open                 |                     |     |                     |      |

| Operating supply current      | I <sub>SLP</sub>  | $V_I = V_{DD}$ or $V_{SS}$                         |                     | 3   | 6                   | mA   |

| in the SLEEP mode             |                   | f=25MHz                                            |                     |     |                     |      |

|                               |                   | V <sub>DD</sub> =3.3V Outputs open                 |                     |     |                     |      |

| Operating supply current      | I <sub>STP</sub>  | $V_I = V_{DD}$ or $V_{SS}$                         |                     |     | 50                  | μΑ   |

| in the STOP mode              |                   | f=25MHz                                            |                     |     |                     |      |

|                               |                   | V <sub>DD</sub> =3.3V Outputs open                 |                     |     |                     |      |

| Oscillator circuit: XO        |                   |                                                    |                     |     |                     |      |

| Built-in feedback resistor    | R <sub>fb7</sub>  | V <sub>I</sub> =V <sub>DD</sub> or V <sub>SS</sub> | 313                 | 940 | 2820                | kΩ   |

|                               |                   | V <sub>DD</sub> =3.3V                              |                     |     |                     |      |

| CMOS level inputs: CAPTON     | I, TESTO          | N                                                  |                     |     |                     |      |

| "H" level input voltage       | V <sub>IH2</sub>  |                                                    | $V_{DD} \times 0.7$ |     | V <sub>DD</sub>     | V    |

| "L" level input voltage       | V <sub>IL2</sub>  |                                                    | 0                   |     | $V_{DD} \times 0.3$ | V    |

| Input leakage current         | I <sub>LI</sub>   | $V_I = V_{DD}$ or $V_{SS}$                         |                     |     | ±5                  | μΑ   |

| CMOS level inputs with pull-o | lown resis        | tor: MINTEST                                       |                     |     |                     |      |

| "H" level input voltage       | V <sub>IH2</sub>  |                                                    | $V_{DD} \times 0.7$ |     | V <sub>DD</sub>     | V    |

| "L" level input voltage       | V <sub>IL2</sub>  |                                                    | 0                   |     | $V_{DD} \times 0.3$ | V    |

| Pull-down resistance          | R <sub>PD1</sub>  | V <sub>I</sub> =V <sub>DD</sub>                    | 10                  | 30  | 90                  | kΩ   |

| Input leakage current         | I <sub>LIPD</sub> | V <sub>I</sub> =V <sub>SS</sub>                    |                     |     | ±10                 | μΑ   |

Note \*1: The V<sub>DD</sub> applied to the oscillator pin XI must use a power supply different from that for the I<sub>DDS</sub> being measured.

# Electrical Characteristics (continued)

$V_{DD}\!\!=\!\!3.0$  to 3.6V,  $V_{REF5}\!\!=\!\!4.75$  to 5.25V,  $V_{SS}\!\!=\!\!0.00V$ ,  $f_{TEST}\!\!=\!\!25MHz$ , Ta=0 to 70°C

| Parameter                  | Symbol            | Conditions                                           | min                  | typ      | max               | Unit |

|----------------------------|-------------------|------------------------------------------------------|----------------------|----------|-------------------|------|

| TTL level inputs: CPAD0 t  | o CPAD2, C        | CPCK, CPCS, CPRD, CPWR, H                            | FREN, RESE           | T, INCTR | L                 |      |

| "H" level input voltage    | V <sub>I5H1</sub> |                                                      | 2.0                  |          | V <sub>REF5</sub> | V    |

| "L" level input voltage    | V <sub>I5L1</sub> |                                                      | 0                    |          | 0.8               | V    |

| Input leakage current      | I <sub>LI5</sub>  | V <sub>I</sub> =V <sub>REF5</sub> or V <sub>SS</sub> |                      |          | ±10               | μΑ   |

| Push-pull outputs: FRAD0   | to FRAD14,        | , WRAD0 to WRAD14                                    |                      |          |                   | 1    |

| "H" level output voltage   | V <sub>OH</sub>   | I <sub>0</sub> =-2.0mA                               | V <sub>DD</sub> -0.6 |          |                   | V    |

|                            |                   | $V_I = V_{DD}$ or $V_{SS}$                           |                      |          |                   |      |

| "L" level output voltage   | V <sub>OL</sub>   | I <sub>O</sub> =2.0mA                                |                      |          | 0.4               | V    |

|                            |                   | V <sub>I</sub> =V <sub>DD</sub> or V <sub>SS</sub>   |                      |          |                   |      |

| Push-pull outputs: CPIR, F | ROE, FRWE         | E, WROE, WRWE, CPWAIT                                |                      |          |                   | 1    |

| "H" level output voltage   | V <sub>OH</sub>   | I <sub>0</sub> =-4.0mA                               | $V_{DD}$ - 0.6       |          |                   | V    |

|                            |                   | $V_{I} = V_{DD}$ or $V_{SS}$                         |                      |          |                   |      |

| "L" level output voltage   | V <sub>OL</sub>   | I <sub>O</sub> =4.0mA                                |                      |          | 0.4               | V    |

|                            |                   | $V_{I} = V_{DD}$ or $V_{SS}$                         |                      |          |                   |      |

| N-channel open drain outpu | ts: FRCS, V       | VRCS                                                 | <b>_</b> _           |          |                   |      |

| "L" level output voltage   | V <sub>OL</sub>   | I <sub>O</sub> =4.0mA                                |                      |          | 0.4               | V    |

|                            |                   | $V_{I} = V_{DD}$ or $V_{SS}$                         |                      |          |                   |      |

| Output leakage current     | I <sub>LO</sub>   | V <sub>O</sub> =High-impedance state                 |                      |          | ±5                | μΑ   |

|                            |                   | $V_{I}=V_{DD}$ or $V_{SS}$                           |                      |          |                   |      |

|                            |                   | $V_0 = V_{DD}$ or $V_{SS}$                           |                      |          |                   |      |

| TTL level I/O: CPDATA0     | to CPDATA         | 15, FRDATA0 to FRDATA7,                              | WRDATA0              | to WRDA' | ГА7               |      |

| "H" level input voltage    | V <sub>I5H1</sub> |                                                      | 2.0                  |          | V <sub>REF5</sub> | V    |

| "L" level input voltage    | V <sub>I5L1</sub> |                                                      | 0                    |          | 0.8               | V    |

| "H" level output voltage   | V <sub>OH</sub>   | I <sub>0</sub> =-4.0mA                               | 2.4                  |          |                   | V    |

|                            |                   | $V_I = V_{DD}$ or $V_{SS}$                           |                      |          |                   |      |

| "L" level output voltage   | V <sub>OL</sub>   | I <sub>O</sub> =4.0mA                                |                      |          | 0.4               | V    |

|                            |                   | V <sub>I</sub> =V <sub>DD</sub> or V <sub>SS</sub>   |                      |          |                   |      |

| Output leakage current     | I <sub>LO5</sub>  | V <sub>O</sub> =High-impedance state                 |                      |          | ±10               | μΑ   |

|                            |                   | $V_{I} = V_{REF5}$ or $V_{SS}$                       |                      |          |                   |      |

|                            |                   | V <sub>O</sub> =V <sub>REF5</sub> or V <sub>SS</sub> |                      |          |                   |      |

## Application Example

The MN5571 uses two external SRAM devices to achieve high throughput. The one used as a work memory area is always required. The MN5571 can operate without the one used as font memory, but throughput suffers.

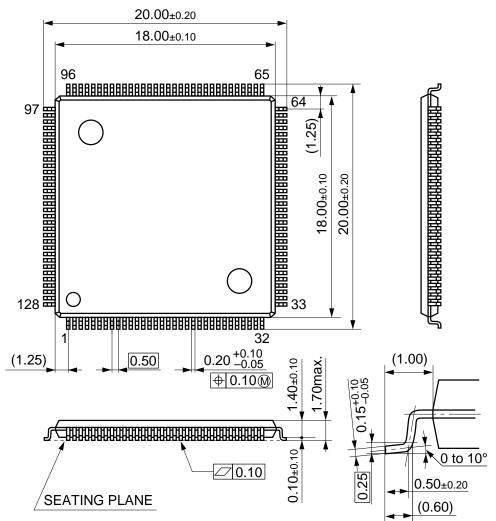

Package Dimensions (Unit: mm)

LQFP128-P-1818B