#

MAY 1998 VOLUME VIII NUMBER 2

| IN THIS ISSUE                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------|

| COVER ARTICLE LTC® 1406: 8-bit, 20MHz ADC Offers 250MHz Input Bandwidth and Tiny Footprint                                |

| Jeff Huehn                                                                                                                |

| Issue Highlights 2                                                                                                        |

| LTC in the News 2                                                                                                         |

| DESIGN FEATURES The LT®1167: Precision, Low Cost, Low Power Instrumentation Amplifier Requires a Single Gain-Set Resistor |

| 200µA, 1.2MHz Rail-to-Rail Op<br>Amps Have Over-The-Top™<br>Inputs                                                        |

| Raj Ramchandani                                                                                                           |

| LTC1710: Two 0.4Ω Switches with SMBus Control Fit into Tiny MSOP-8 Package 12 Peter Guan                                  |

| Low Distortion Rail-to-Rail Op Amps Have 0.003% THD with 100kHz Signal 14 Danh Tran                                       |

| High Speed SO-8 12-Bit ADCs<br>Run on 5V or 3V 17<br>Ricky Chow and Teo Yang Long                                         |

| A 7ns, 7mA, Single-Supply Comparator Fabricated on Linear's 6GHz Complementary Bipolar Process                            |

| <u>DESIGN IDEAS</u> 26–38 (complete list on page 26)                                                                      |

| Design Tools 39                                                                                                           |

| Sales Offices 40                                                                                                          |

| LINEAR                                                                                                                    |

TECHNOLOGY

# LTC1406: 8-Bit, 20MHz ADC Offers 250MHz Input Bandwidth and Tiny Footprint by Jeff Huehn

#### LTC Goes High Speed

Everyone knows about Linear Technology's linear and switching regulators, but over the last several years Linear has built an impressive family of data conversion products. With the recent introduction of fast 12-bit and 14-bit ADCs, and, most recently, a 16-bit part, the family continues to expand. Now, the newest member of the LTC converter family, the LTC1406, takes LTC in a new direction: high speed for communications and video conversion.

#### LTC1406 Features

- □ 20Msps sample rate, 8-bit parallel output

- □ 250MHz internal sample-and-hold

- $\square$  48.5dB S/(N + D) and 62dB THD

- □ 7.0 effective bits at 70MHz

- □ ±1LSB DNL and INL Max

- ☐ Low power with power-down mode

- ☐ Small footprint: 24-pin narrow SSOP package

#### Why Use Linear Technology?

There are other 8-bit, 20Msps converters on the market, so why use the LTC1406? The LTC1406 has several significant advantages over its seemingly similar competitors.

### Wide Input Bandwidth for Communications

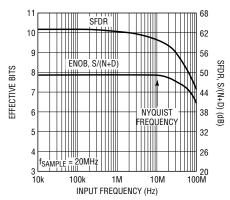

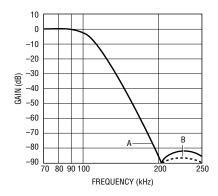

One very useful advantage is the extremely wideband sample-and-hold. The 250MHz input bandwidth of the LTC1406 allows for undersampling of very high frequency signals. Coupled with its excellent distortion, the LTC1406 has better high frequency undersampling performance than any other 8-bit, 20MHz part on the market. The signal-to-(noise + distortion) ratio is a nearly ideal 48.5dB for low frequencies; it stays flat all the way out to 10MHz. Even at 70MHz, well beyond the Nyquist frequency of 10MHz, the signal-to-(noise + distortion) ratio is still close to 44dB, which is equivalent to 7.0 ENOBs (effective number of bits). Figure 1 illustrates this outstanding performance along with the spurious free dynamic range (SFDR). For applications in communications, or any application that depends on high dynamic range and a high number of effective bits at very high input frequencies, the LTC1406 outperforms the competition.

#### **Small Footprint**

Is board space a problem? The LTC1406 is also the smallest 8-bit, 20MHz part available. It comes in the tiny GN-24 package that occupies only 52mm<sup>2</sup> (only 1.75 times the size of an

continued on page 3

7, LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode, C-Load, FilterCAD, FilterView, LinearView, Micropower SwitcherCAD, Operational Filter, Over-The-Top and SwitcherCAD are trademarks of Linear Technology Corporation. Other product names may be trademarks of the companies that manufacture the products.

# **Issue Highlights**

Our cover article for this issue introduces the LTC1406, a high speed 8-bit ADC intended for communications and video-conversion applications. It features a 20Msps sample rate, 8-bit parallel output, a 250MHz internal sample-and-hold and excellent noise and distortion specs.

Two other new data converters are also introduced in this issue: the LTC1401 and LTC1404 are low power, 12-bit serial ADCs. The LTC1401 operates on a 3V supply and samples at 200ksps. The LTC1404 is a pincompatible upgrade of the LTC1400. It samples at 600ksps and operates on either single 5V or ±5V supplies. These devices provide the highest throughput per square area of board space of any 12-bit ADC on the market.

This issue debuts a new instrumentation amp and two new op amp families: the LT1167 is the next-generation instrumentation amplifier designed to replace the previous generation of monolithic instrumentation amps, as well as discrete, multiple-op amp solutions. The gain of the LT1167 is set by the absolute value of one external resistor. Gain error depends on the ratio of one external resistor to the value of the LT1167's internal, laser-trimmed resistors, which are trimmed to better than 0.1%.

The LT1638 and LT1639 are Linear Technology's latest general-purpose, low power, dual and quad rail-to-rail operational amplifiers. The circuit topology of the LT1638 is based on Linear Technology's popular LT1490/LT1491 op amps, with substantial improvements in speed. The LT1638 is five times faster than the LT1490. The LT1638/LT1639 are "tough" op amps, with a variety of features that make them ideal for general-purpose applications.

The LT1630/LT1632 duals and LT1631/LT1633 quads are the new-

est members of Linear Technology's family of precision rail-to-rail op amps, which provide the best combination of AC performance and DC precision over the widest range of supply voltages. The LT1630/LT1631 deliver a 30MHz gain-bandwidth product, a 10V/ $\mu$ s slew rate and 6nV/ $\sqrt{Hz}$  input-voltage noise. Optimized for higher speed applications, the LT1632/LT1633 have a 45MHz gain-bandwidth product, a 45V/ $\mu$ s slew rate and 12nV/ $\sqrt{Hz}$  input voltage noise.

Expanding LTC's line of products to support the SMBus standard, we debut the LTC1710, which features two SMBus controlled  $0.4\Omega$  switches in an MSOP-8 package. The LTC1710 is a complete solution for delivering power to portable-equipment peripherals without external switches.

Rounding out the selection of new parts introduced in this issue, we debut the LT1394, an ultrafast, low power, single-supply comparator. The LT1394 is the first product made with LTC's new 6GHz complementary bipolar process.

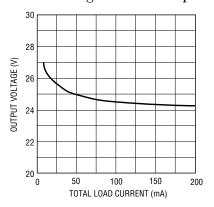

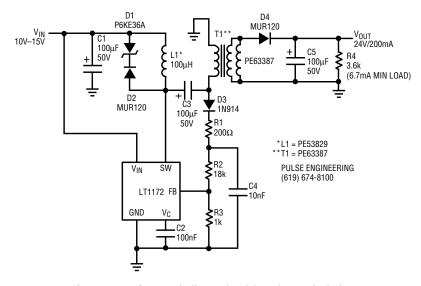

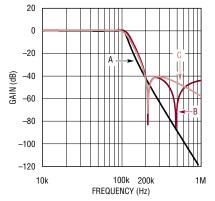

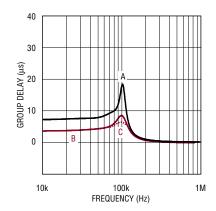

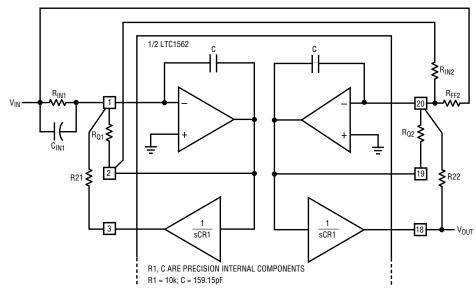

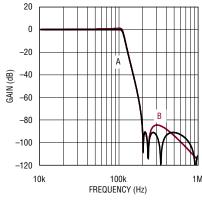

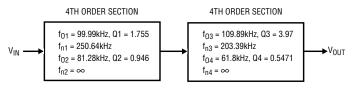

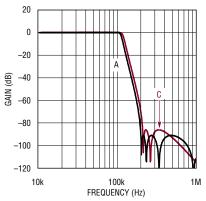

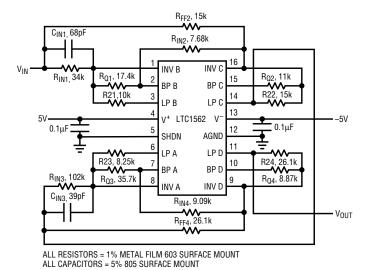

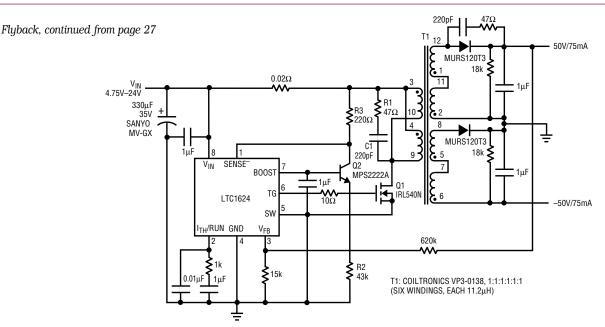

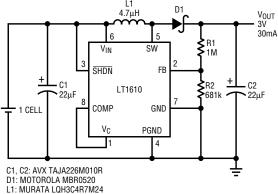

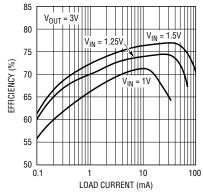

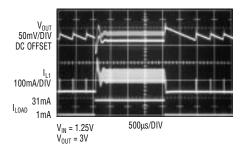

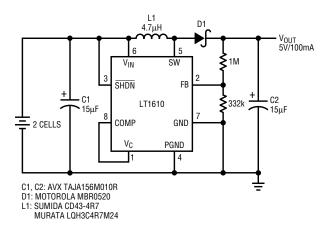

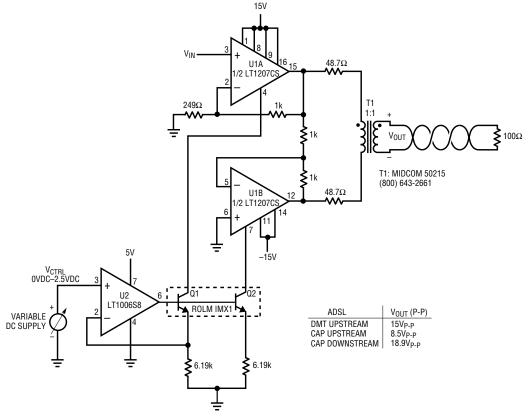

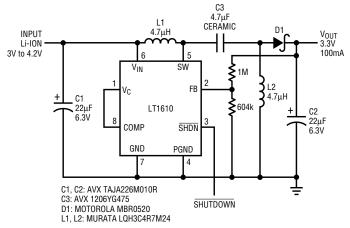

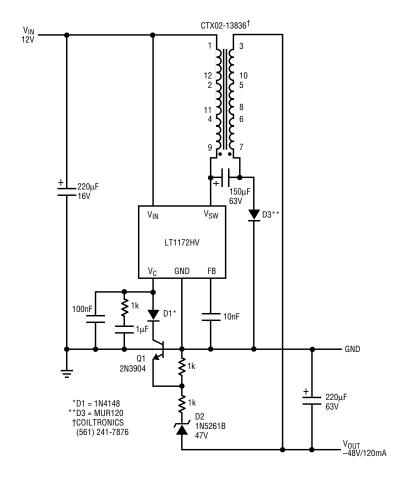

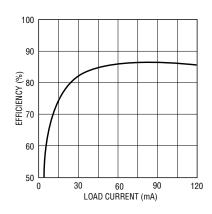

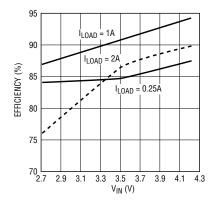

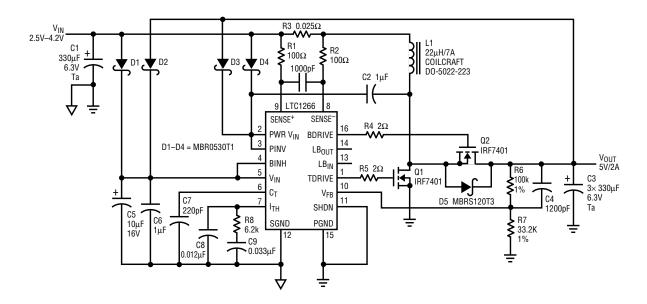

In our Design Ideas section, we present a variety of power conversion ideas: a high isolation converter that achieves 3750V<sub>RMS</sub> isolation with the LT1172 and off-the-shelf magnetics, a wide input range, low voltage flyback regulator based on the LTC 1624, a positive to negative converter for -48V telecommunications applications, a bootstrapped synchronous boost converter using the LTC1266, a battery-powered buck-boost converter that requires no magnetics and a number of battery converter circuits based on the LT1610 micropower DC/ DC converter. We also include a design primer for creating lowpass filters with added notches using the LTC1562 quad Operational Filter<sup>TM</sup> IC, and an optimized low power, low distortion ADSL line driver based on the LT1207. 🖊

#### LTC in the News...

#### Linear Technology Reports Another Quarter of Record Sales and Profits

"This was a good March quarter for us," said Robert H. Swanson, president and CEO of Linear Technology. "We achieved strong quarterly financial performance culminating in record return on sales. Recent difficulties experienced by some technology companies regarding slowing demand in Asia and in computer markets worldwide have us cautious going forward. However, our product, geographic and end-market diversity and our good March quarter performance should enable continued sequential sales and profits growth in the upcoming June quarter."

On the strength of the Company's third quarter results, it was named the "Stock of the Day" by the San Jose Mercury News in its April 16, 1998 edition. LTC also received prominent attention in the San Jose Mercury News's annual "Silicon Valley 150" report. The report included a feature article on LTC in which Elias Moosa, an analyst for BancAmerica Robertson Stephens, praised it as "truly among the premier chip companies"; the report also ranked Linear Technology as among the top twenty Silicon Valley firms for return on sales and market capitalization.

Net sales for the third quarter ended March 29, 1998, were \$125,982,000, an increase of 33% over net sales of \$95,033,000 for the third quarter of the previous year. The Company also reported record net income for the quarter of \$47,174,000 or \$0.59 diluted earnings per share, an increase of 39% from \$33,980,000 or \$0.43 diluted earnings per share, reported for the third quarter of last year. A cash dividend of \$0.06 will be paid on May 13, 1998 to shareholders of record on April 24, 1998.

Figure 1. LTC1406 SINAD and SFDR plot shows 7 effective bits at 70MHz input frequency.

LTC1406, continued from page 1

SO-8 package). It also requires only three surface mount bypass capacitors, one for the analog, digital, and output logic supplies, one for the reference input ( $V_{REF}$ ) and one for the  $V_{BIAS}$  pin, resulting in a small layout footprint in addition to a small package.

#### Low Power Shutdown Mode

The low power consumption of the LTC1406 can be reduced even further by taking advantage of the Shutdown mode. Taking the SHDN pin low powers down the converter and bias circuitry so that the part draws only a tiny leakage current from the supply. This can reduce power consumption in portable and battery-powered equipment whenever the converter is idle.

#### Overrange/ Underrange Detection

Another feature unique to the LTC1406 is the ability to detect an overrange or underrange condition using the Overflow/Underflow bit. The OF/UF output will transition from 0 to 1 at 1LSB below the 0000 0000 to 0000 0001 transition and 1LSB above the 1111 1110 to 1111 1111 transition, providing a clear indicator that the input signal is outside the full-scale conversion range of the converter. This can be used as a flag when trimming the input span to maximize the signalto-noise ratio. For imaging applications where the output of a CCD varies from pixel to pixel, for communications applications where the magnitude of the input signal is constantly changing or for any application where the input span varies, the LTC1406 makes it easy to optimize performance.

#### Ease of Use with Flexibility

Trying to make a high speed data converter perform used to be somewhere near the magic end of the "science-magic scale." It was also generally true that the more flexibility (the more options the user had for connecting the part), the more difficult it was to get the part to work properly. The LTC 1406 changes that: it was designed to make it easy to get good performance and to be very easy to use without sacrificing flexibility. It starts with very simple, straightforward connections. A power supply, a reference, a clock and an input are all you need to start converting high speed signals into ones and zeros.

Connecting the supply voltage is a good example of the simplicity and flexibility built into the LTC1406. In the simplest configuration, connect the analog, digital and output logic supplies together to a single 5V supply and bypass capacitor and you're done. If you need to interface with 3V logic, the LTC1406 is ready for that too. The logic inputs are set up to work equally well with 3V or 5V signals and the output logic supply  $(O_{VDD})$ can be connected to a separate 3V supply to provide 3V data out. This eliminates the need for circuitry to level shift a 3V clock up to 5V and/or level shift the entire 5V data bus back down to 3V.

The reference is also easier to provide. Rather than the conventional

half-flash architecture that requires two reference voltages, two bypass capacitors and two buffer amplifiers for the top and bottom of the reference ladder, the LTC1406 requires only one 2.5V reference and bypass capacitor. This is really an advantage when changing or trimming the input span. Instead of moving both the top and bottom voltages to obtain the correct span, the single 2.5V reference functions as a gain control. It also requires less current, and therefore less power, from the reference, since there is no resistive ladder to drive. The typical reference current required is about 1mA (5mW) compared to about 7mA (35mW) for most of the half-flash architectures.

#### **Flexible Analog Inputs**

#### **Easy to Drive**

One of the strongest features of the LTC 1406 is the structure of the inputs. The inputs are very easy to drive. Following the rising clock edge, the LTC1406 goes into track mode and, like other converters, the inputs draw a small current spike to charge the input sampling capacitors. However, the input capacitance is typically onefourth that of competitive parts, so the current spike necessary to charge them is much smaller. While the clock is high, the voltage across the sampling capacitors will track the voltage on the inputs. Again, this small input capacitance makes the inputs much easier to drive, particularly for high input frequencies. Reducing the capacitive load by 70%-80% greatly reduces the input-buffer-amplifier requirement and may eliminate the need for a buffer amplifier altogether.

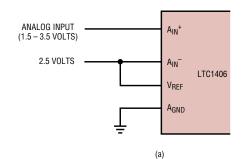

Figure 2. (a) Using  $A_{\rm IN}$ + as the input and connecting  $A_{\rm IN}$ - to  $V_{\rm REF}$  yields an input span of 1.5V-3.5V. (b) AC coupling the input yields a 2V AC-coupled span.

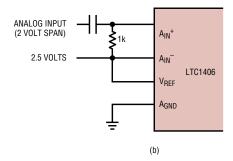

Figure 3. The LTC1406has a wideband differential track-and-hold that can capture input signals of up to 230MHz. The separate output supply and grounding pins allow for easy interface to 3V logic.

On the falling clock edge, the part samples the input voltage; the inputs draw only a small leakage current while the clock is low.

#### Differential or Single-Ended

The LTC1406's inputs are truly differential; they will always convert the difference between  $A_{IN}$ + and  $A_{IN}$ -. The maximum output code (1111 1111) occurs when  $A_{IN}$ + –  $(A_{IN}$ –) = 1V and the minimum output code (0000 0000) occurs when  $A_{IN}$ + –  $(A_{IN}$ –) = –1V. These differential inputs also have outstanding common mode rejection, so that any noise or unwanted signal that is common to both inputs will be rejected. However, the inputs need not be driven differentially to achieve good performance. If a differential signal is present, the differential inputs can be connected directly. If the input signal is single ended, there is no need for a complicated transformer to create a differential signal; the LTC1406 will handle a singleended signal as easily as a differential signal. The A<sub>IN</sub>- input can be tied to a common mode voltage and A<sub>IN</sub>+ becomes the signal input, with a ±1V span centered around  $A_{IN}$ -. Again, to simplify the hookup A<sub>IN</sub>- can be connected to V<sub>REF</sub> resulting in an input span of 1.5V-3.5V as shown in Figure 2a.

#### Rail-to-Rail Common Mode

Another nice feature of the LTC1406 input structure is that the inputs have a common mode range that extends to either rail. In single-ended mode, the 2V input span can extend from 0V-2V to 3V-5V. The  $\pm 1V$  differential-input span can also extend between the rails. This allows for direct coupling to a wide range of inputs without any additional circuitry. In addition, the input can be AC coupled to allow for a 2V input span centered around virtually any common mode voltage (see Figure 2b).

#### Keys to Using High Speed ADCs

The LTC1406 uses an internal sampleand-hold and a pipeline quantizing architecture to convert an analog signal to an 8-bit parallel output. The input is sampled on the falling clock edge, converted into an internal differential voltage and fed into a comparator to determine the most significant bit. The result of that decision is subtracted from the sample and the residue is multiplied by two and then passed on to the next stage via a similar sample-and-hold. This continues down the eight pipeline stages. The comparator outputs are then combined in a digital error-correction circuit into an 8-bit parallel word. Figure 3 is a block diagram of the LTC1406.

The one-bit-per-stage pipeline architecture of the LTC1406 is very similar to the half-flash or subranging architecture (sometimes also referred to as pipeline, the difference being the number of bits determined in each comparator cycle) used in other 8-bit, 20MHz converters. However, if you are more familiar with the successive approximation register (SAR) architecture used in many lower speed, higher resolution converters (including most of Linear Technology's converters), there are some things you need to know about high speed ADCs.

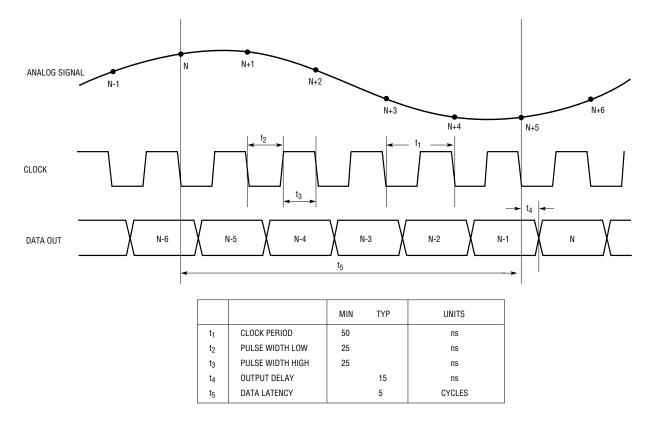

Almost all high speed converters have latency in the output data. This is defined as the delay, usually expressed as a number of clock cycles, from the sampling of the analog input to the appearance of the conversion data on the digital outputs. The most common architecture for 8-bit, 20MHz converters, the half-flash, typically has a delay of 2.5 clock cycles. The

Figure 4. As with all pipeline ADCs, there is latency in the output data. Output data is available from the LTC1406 5 cycles after the input is sampled and the conversion starts.

data latency of the LTC1406, as well as other 8-bit, one-bit-per-stage, pipeline converters, is five clock cycles. Each falling clock edge samples the input and starts a conversion. The digital representation of that sample will be available as an 8-bit parallel word following the fifth falling edge after the start of conversion. So although each conversion takes five clock cycles, a new conversion result is available on each falling edge. Figure 4 clearly illustrates the relationship between the sampled analog input and when the output data is available.

Another important consideration when using a high speed converter is the sampling clock. Most high speed converters use both phases of the clock, so it is critical to maintain a 50% duty cycle. During each clock phase, half of the stages of the ADC are sampling and half are amplifying. At conversion speeds below the maximum conversion rate, the duty cycle can deviate from 50% with no degradation in performance. At the maximum conversion rate it is important to maintain a 50% duty

cycle clock. It is also important to provide a clock that has low jitter and fast rise and fall times (<2ns).

Finally, much of the internal circuitry operates dynamically, resulting in two important consequences. First, as with most high speed ADCs, there is a lower limit on the conversion speed. The minimum conversion speed of the LTC1406 is 10kHz. Second, some high speed ADCs, including the LTC1406, are dynamically biased and the bias must be periodically refreshed. Under normal, free-running conversion conditions, the bias is refreshed during each clock cycle. However, when power is first applied or the clock stops for longer than 100µs (for example, in Shutdown mode), the part must typically be clocked for 20 clock cycles at a sample rate of greater than 10kHz before the output data will be valid.

#### Easy, Clean, Small Layout

One of the reasons that high speed converters can de difficult to use is that the board layout becomes extremely critical for high input fre-

quencies. The layout in Figure 5 shows how easy it is to get a clean, tight layout using the LTC1406 even when connecting the output logic to the digital supply and ground-it's almost automatic. It also illustrates the advantage of the tiny GN-24 package relative to the standard SO-24. The pinout is designed for a smooth flow from analog input signal to digital output. All of the supplies, reference, and analog inputs are located on one side of the part and the clock input and digital data outputs are on the other. This allows for easy separation of the analog and digital ground planes and helps to prevent digital noise from coupling into the analog inputs. As mentioned earlier, the LTC1406 requires very few external components and the pinout is designed to allow the bypass capacitors to be located very close to the package. This close bypassing minimizes lead inductance and sensitivity to currents flowing in the ground plane, which can be critical when the whole system is clocking at 20MHz.

continued on page 25

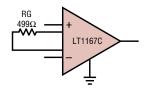

# The LT1167: Precision, Low Cost, Low Power Instrumentation Amplifier Requires a Single Gain-Set Resistor

#### Introduction

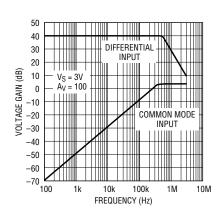

The LT1167 is the next-generation instrumentation amplifier designed to replace the previous generation of monolithic instrumentation amps, as well as discrete, multiple op amp solutions. Instrumentation amplifiers differ from operational amplifiers in that they can amplify input signals that are not ground referenced. The output of an instrumentation amplifier is referenced to an external voltage that is independent of the input. Conversely, the output voltage of an op amp, due to the nature of its feedback, is referenced to the differential and common mode input voltage.

A separate ground reference and the high CMRR of the LT1167 instrumentation amplifier reduce the effect of the input common mode voltage on the output signal. The closed-loop gain of an op amp and of most instrumentation amps is set by a resistor ratio; the gain of the LT1167 is set by the absolute value of one external resistor. Gain error depends on the ratio of one external resistor to the value of the LT1167's internal, lasertrimmed resistors, which are trimmed to better than 0.1%. Once the gain is set, it is expected to remain constant when the output voltage or output current changes. Any change in gain with output swing will show up as gain nonlinearity.

Parameters such as gain error, voltage offset and CMRR are a function of trimming. Gain nonlinearity cannot be trimmed; it is a function of careful design and die layout. The use of common centroid geometries and isothermal layout cancels the errors due to die stress and thermal gradients. If this is not done correctly, all the trimming in the world will not improve performance.

#### **Input Protection**

Instrumentation amplifiers must survive in a hostile environment. Not only does the LT1167 have to endure ESD during handling (power off) but it must also survive excessive voltage during operation. The inputs of the LT1167 have low leakage internal diodes from each input to the supplies. These diodes have a maximum current rating of 20mA and protect the IC when the input voltage exceeds the supply rails. Precision and indestructibility are combined when an external 20k resistor is placed in series with each input. There is little offset voltage penalty because the 320pA offset current from the LT1167 multiplied by the 20k input resistors contributes only 6.4 µV additional offset. With the 20k resistors, the LT1167 can handle both ±400VDC input faults and ESD spikes over 4kV. This meets the IEC 1004-2 level 2 European standard.

The low noise voltage of 7.5nV√Hz is achieved by idling a large portion of the 0.9mA supply current in the input stage. Input bias current is not compromised due to the use of superbeta transistors, current-cancellation circuitry and trimming. The LT1167's input bias current is better than that of a JFET input stage at only 350pA maximum at room temperature; it does not double for every 10°C. The LT1167 is also trimmed for critical DC parameters, such as input offset voltage and CMRR. These trims allow the amplifier to achieve very high DC accuracy; total input-referred offset voltage is only 60µV and CMRR is better than 110dB at a gain of ten. Worst-case input offset is at a gain of one; it is guaranteed to be less than 240µV for the prime grade. The LT1167 is offered in 8-pin PDIP and by Alexander Strong

SO packages, saving significant board space compared to discrete designs. With these advantages, the LT1167 will easily find its way into many applications.

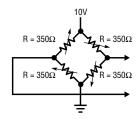

PRECISION BRIDGE TRANSDUCER

LT1167 MONOLITHIC

INSTRUMENTATION AMPLIFIER, G = 100

SUPPLY CURRENT = 1.3mA MAX

"ROLL YOUR OWN" INSTRUMENTATION AMP, G = 100

"0.02% RESISTOR MATCH, 3PPM/C TRACKING

"DISCRETE 1%RESISTOR, 100PPM/C TRACKING

SUPPLY CURRENT = 1.35mA FOR THREE AMPLIFIERS

Figure 1. "Roll your own" vs LT1167

Table 1a. "Roll your own" vs LT1167 error budget

|                                     |                                                   | "Dall Varra Orra" Office 12                                     | Error (PPM) of Full Scale |                    |

|-------------------------------------|---------------------------------------------------|-----------------------------------------------------------------|---------------------------|--------------------|

| Error Source                        | LT1167 Circuit Calculations                       | "Roll Your Own" Circuit Calculations                            | LT1167                    | "Roll Your<br>Own" |

|                                     | Absolute Accura                                   | cy at T <sub>A</sub> = 25° C                                    |                           |                    |

| Input Offset Current                | I <sub>OS</sub> × R <sub>S</sub> /V <sub>FS</sub> | $I_{OS} \times R_S / V_{FS}$                                    | 4                         | 4                  |

| Input Offset Voltage                | V <sub>OSI</sub> /V <sub>FS</sub>                 | $\Delta V_{0S}/V_{FS}$                                          | 3000                      | 6500               |

| Output Offset Voltage               | V <sub>OSO</sub> /G/V <sub>FS</sub>               | $V_{OS} \times NG/G/V_{FS}$                                     | 150                       | 75                 |

| CMRR                                | $CMRR \times V_{CM}/V_{FS}$                       | $RM \times V_{CM}/G/V_{FS}$                                     | 790                       | 500                |

| Total Absolute Error                |                                                   |                                                                 | 3944                      | 7079               |

|                                     | Drift to                                          | 85° C                                                           |                           |                    |

| Input Offset Voltage Drift          | $TCV_{OSI} \times \Delta T/V_{FS}$                | $TC\Delta V_{OS} \times \Delta T/V_{FS}$                        | 1200                      | 5700               |

| Output Offset Voltage Drift         | $TCV_{OSO} \times \Delta T/G/V_{FS}$              | ${\sf TCV_{OS}} \times {\sf NG} \times \Delta {\sf T/G/V_{FS}}$ | 180                       | 78                 |

| Gain Drift                          | $(TCG + TCR) \times \Delta T$                     | $TCRM \times \Delta T$                                          | 3,600                     | 6000               |

| Total Drift Error                   |                                                   |                                                                 | 4980                      | 11,778             |

| Resolution                          |                                                   |                                                                 |                           |                    |

| Gain Nonlinearity                   | GNL                                               | RNL                                                             | 15                        | 10                 |

| Typical 0.1Hz–10Hz<br>Voltage Noise | e <sub>n</sub> /V <sub>FS</sub>                   | $e_n \times \sqrt{2}/V_{FS}$                                    | 14                        | 21                 |

| Total Resolution Error              |                                                   |                                                                 | 29                        | 31                 |

| Grand Total Error                   |                                                   |                                                                 | 8953                      | 18,888             |

#### "Roll Your Own"—Discrete vs Monolithic LT1167 **Error Budget Analysis**

The LT1167 offers performance superior to that of "roll your own," three-op amp discrete designs. A typical application that amplifies and buffers a bridge transducer's differential output is shown in Figure 1. The amplifier, with its gain set to one

hundred, amplifies a differential, fullscale output voltage of 20mV over the industrial temperature range. The discrete instrumentation amp uses the best precision, low power, superbeta quad op amp available, the LT1114. This comparison demonstrates that the LT1167 outperforms a discrete instrumentation amplifier using a state-of-the-art op amp. The

error budget comparison in Table 1 shows how various errors are calculated and referenced to the bridge's full-scale output of 20mV. The table shows that some of the greatest differences in error between the LT1167 and the discrete solution are input offset voltage, input offset voltage drift and CMRR. Expensive precision resistor arrays that can deliver 0.02%

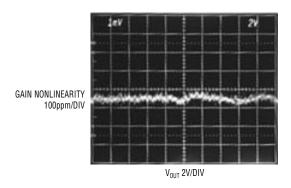

Figure 2. LT1167 gain nonlinearity:  $R_C = 1k$ ;  $V_O = \pm 10V$

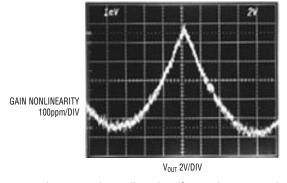

Figure 3. Gain nonlinearity of a previous generation instrumentation amp:  $R_C = 1k$ ;  $V_O = \pm 10V$

matching are required to match the LT1167's CMRR performance. The total error for the LT1167 solution is much lower than that of the discrete solution. The LT1167 has other advantages over a discrete design, including lower power dissipation, lower component cost and smaller size. The clear advantage goes to the LT1167.

#### LT1167 vs the Competition

What was said about the LT1167 when compared to discrete solutions is also applicable to previous IC instrumentation amplifiers. Improvements in circuit design and common centroid layout greatly enhance the CMRR, PSRR, gain error and nonlinearity over competitive IC solutions.

I T1167 Snec

Term

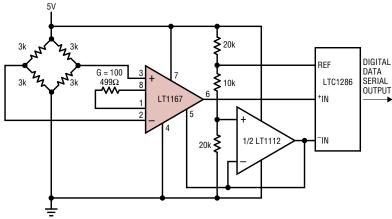

Figure 4. Single-supply pressure monitor

The LT1167 has a 10dB improvement for CMRR and a 20dB improvement in PSRR for the worst-case condition of unity gain. Gain error is better than

Comment

0.1% for all gains up to one hundred, which is a  $2.5 \times$  to  $5 \times$  improvement over previous ICs. This gain error is maintained even when the output has to drive heavy loads, thanks to improvements in common centroid layout. The LT1167 maintains excellent performance even when driving heavy loads. Figure 2 is a photo of the LT1167 in a gain of one thousand driving a 1k load. Figure 3 is a previous generation IC instrumentation amplifier in the same condition. You can see why a 10k load resister and not a 1k resistor was specified for older ICs.

### Table 1b. Terms used in Table 1a

| ierm                             | LITTE/ Spec           | LITTIAC Spec         | Comment                                             |

|----------------------------------|-----------------------|----------------------|-----------------------------------------------------|

| I <sub>OS</sub>                  | 450pA                 | 500pA                | Input Offset Current                                |

| R <sub>S</sub>                   | 350Ω/2                | $350\Omega/2$        | Source Resistance                                   |

| V <sub>FS</sub>                  | 20mV                  | 20mV                 | Full-Scale Input Voltage                            |

| V <sub>OSI</sub>                 | 60μV                  | N/A                  | Input Offset Voltage                                |

| $\Delta V_{0S}$                  | N/A                   | 130μV                | Input Offset Voltage Match                          |

| V <sub>OSO</sub>                 | 300μV                 | N/A                  | Output Offset Voltage                               |

| V <sub>OS</sub>                  | N/A                   | 75μV                 | Offset Voltage                                      |

| NG                               | N/A                   | 2V/V                 | Noise Gain of Output Op Amp                         |

| G                                | 100V/V                | 100V/V               | Gain                                                |

| CMRR                             | 110dB (3.16ppm)       | N/A                  | Common Mode Rejection Ratio                         |

| V <sub>CM</sub>                  | 5V                    | 5V                   | Common Mode Voltage                                 |

| RM                               | NA                    | 0.02%                | Resistor Match                                      |

| TCV <sub>OSI</sub>               | 0.4V/°C               | N/A                  | Temperature Coefficient of<br>Input Offset Voltage  |

| ΔΤ                               | 60°C                  | 60°C                 | Change in Temperature                               |

| TC <sub>\D</sub> V <sub>OS</sub> | N/A                   | 1.9µV/°C             | Temperature Coefficient of<br>Offset Voltage Match  |

| TCV <sub>OSO</sub>               | 6μV/°C                | N/A                  | Temperature Coefficient of<br>Output Offset Voltage |

| TCV <sub>OS</sub>                | N/A                   | 1.3μV/°C             | Temperature Coefficient of Offset Voltage           |

| TCG                              | 50ppm/°C              | N/A                  | Temperature Coefficient of Gain                     |

| TCR                              | 10ppm/°C              | N/A                  | Temperature Coefficient of<br>Resistance            |

| TCRM                             | N/A                   | 100ppm/°C            | Temperature Coefficient of<br>Resistor Match        |

| GNL                              | 15ppm                 | N/A                  | Gain Nonlinearity                                   |

| RNL                              | N/A                   | 10ppm                | Resistor Nonlinearity                               |

| e <sub>n</sub>                   | 0.28μV <sub>P-P</sub> | 0.3μV <sub>P-P</sub> | 0.1Hz-10Hz Voltage Noise                            |

#### Low I<sub>B</sub> Favors High Impedance Bridges, Lowers Dissipation

The LT1167's low supply current, low supply voltage operation and low input bias current (350pA max) allow it to fit nicely into battery powered applications. Low overall power dissipation necessitates using higher impedance bridges. Figure 4 shows the LT1167 connected to a  $3k\Omega$ bridge's differential output. The bridge's impedance is almost an order of magnitude higher than that of the bridge used in the error-budget table. The picoampere input bias currents will still keep the error caused by offset current to a negligible level. The LT1112 level shifts the LT1167's reference pin and the ADC's analog ground pins above ground. This is necessary in single-supply applications because the output cannot swing to ground. The LT1167's and LT1112's

combined power dissipation is still less than the bridge's. This circuit's total supply current is just 3mA.

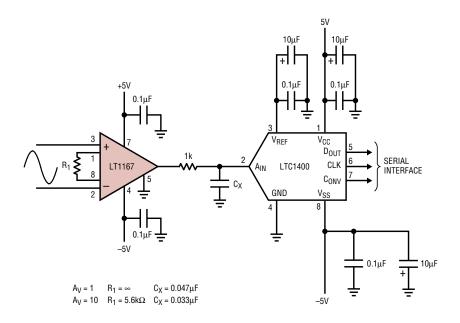

#### **ADC Signal Conditioning**

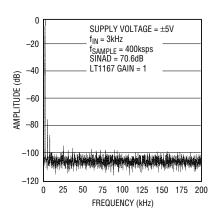

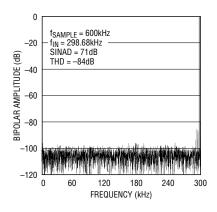

The LT1167 is shown in Figure 5 changing a differential signal into a single-ended signal. The single-ended signal is then filtered with a passive 1st order RC lowpass filter and applied to the LTC1400 12-bit analog-to-digital converter (ADC). The LT1167's output stage can easily drive the ADC's small nominal input capacitance, preserving signal integrity. Figure 6 shows two FFTs of the amplifier/ADC's output. Figures 6a and 6b show

the results of operating the LT1167 at unity gain and a gain of ten, respectively. This results in a typical SINAD of 70.6dB.

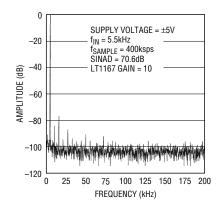

#### **Current Source**

Figure 7 shows a simple, accurate, low power programmable current source. The differential voltage across pins 2 and 3 is mirrored across  $R_G$ . The voltage across  $R_G$  is amplified and applied across  $R_I$ , defining the output current. The  $50\mu A$  bias current flowing from pin 5 is buffered by the LT1464 JFET operational amplifier, which increases the resolution of the current source to 3pA.

Figure 5. The LT1167 converting differential signals to single-ended signals; the LT1167 is ideal for driving the LTC1400.

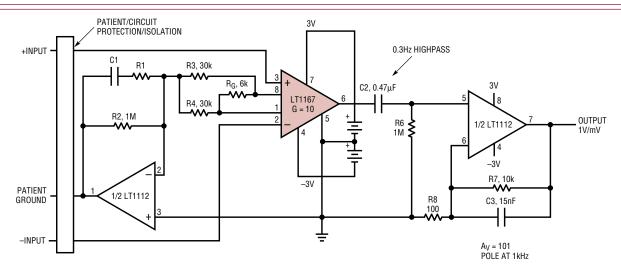

#### Nerve-Impulse Amplifier

The LT1167's low current noise makes it ideal for ECG monitors that have  $M\Omega$  source impedances. Demonstrating the LT1167's ability to amplify low level signals, the circuit in Figure 8 takes advantage of the amplifier's high gain and low noise operation. This circuit amplifies the low level nerve impulse signals received from a patient at pins 2 and 3 of the LT1167. R<sub>G</sub> and the parallel combination of R3 and R4 set a gain of ten. The potential on LT1112's pin 1 creates a ground for the common mode signal. The LT1167's high CMRR of 110db ensures that the desired differential signal is amplified and unwanted common mode signals are attenuated. Since the DC portion of the signal is not important, R6 and C2 make up a 0.3Hz highpass filter. The AC signal at LT1112's pin 5 is amplified by a gain of 101 set by R7/R8 + 1. The parallel combination of C3 and R7 forms a lowpass filter that decreases this gain at frequencies above 1kHz.

The ability to operate at ±3V on 0.9mA of supply current makes the LT1167 ideal for battery-powered applications. Total supply current for this application is 1.7mA. Proper safeguards, such as isolation, must be added to this circuit to protect the patient from possible harm.

continued on page 38

Figure 7. Precision current source

Figure 6. Operating at a gain of one (left) or ten (right), Figure 5's circuit achieves 12-bit operation with a SINAD of 70.6dB

# 200µA, 1.2MHz Rail-to-Rail Op Amps Have Over-The-Top Inputs

#### Introduction

The LT1638 is Linear Technology's latest general-purpose, low power, dual rail-to-rail operational amplifier; the LT1639 is a quad version. The circuit topology of the LT1638 is based on Linear Technology's popular LT1490/LT1491 op amps, with substantial improvements in speed. The LT1638 is five times faster than the LT1490. The LT1638/LT1639 are "tough" op amps, with a variety of features that make them ideal for general-purpose applications. A unique input stage allows the LT1638 to be operated with input common mode voltages up to 44V above the negative rail. The LT1638 dual and LT1639 quad op amps operate on all single and split supplies with a total voltage of 2.5V to 44V. These amplifiers are reverse-battery protected and draw no current for reverse supplies up to 18V. For single 5V supply operation, typical specifications include 200µV input offset voltage, 15nA input bias current, 1nA input offset current, open-loop voltage gain of 1500V/mV,  $0.4V/\mu s$  slew rate, 98dB common mode rejection ratio and 100dB power supply rejection ratio. The output can swing within 30mV of the positive rail and within

5mV of the negative rail with no load. The gain-bandwidth product is 1.2MHz and the part is stable with capacitive loads up to 200pF under all loading conditions. Additional performance specifications are shown in Table 1.

The LT1638 dual is available with industry standard pinout in 8-pin MSOP, SO and miniDIP packages. The LT1639 quad is available with industry-standard pinout in 14-pin SO and 14-pin miniDIP packages.

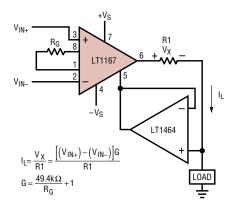

#### **Input-Stage Architecture**

The input stage of the LT1638 is shown in Figure 1. Like the LT1490 rail-to-rail op amp, the LT1638 uses two input stages to achieve rail-torail capability. Device Q7 controls which stage is active by steering the tail current between the two stages as a function of input common mode voltage. The LT1638 has three modes of operation. For input common mode voltages between  $V_{EE}$  and  $(V_{CC} - 1V)$ , the PNP stage (Q5-Q6) is active and Q7 and the NPN stage (Q1–Q4) are off. Since Q7 is off, the entire 10µA of tail current will flow through the PNP stage (Q5-Q6). The input bias current is the base current of Q5 or Q6,

by Raj Ramchandani

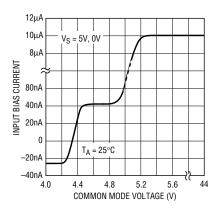

typically 15nA, as shown in Figure 2. The input offset voltage for this stage is trimmed to less then 300 µV. As the input common mode voltage is increased above  $V_{CC}$  – 1V, Q7 turns on, diverting the tail current from the PNP stage to the NPN stage. When the PNP stage is completely off, the 10µA tail current will flow through the current mirror D3-Q8. The 10µA current through Q8 sets the bias for the NPN input stage. In the NPN stage, Q1 and Q2 serve as emitter followers, driving the differential pair formed by Q3 and Q4. Further increases in the common mode voltage will cause Q1 and Q2 to saturate due to the forward voltage of D1 and D2. This will cause the input bias current to increase, as shown in Figure 2. At  $V_{\text{CM}}$  =  $V_{\text{CC}}$  the input bias current is typically 1µA and the untrimmed input offset voltage is typically 600µV. As Figure 2 shows, when  $V_{CM} = V_{CC}$  the NPN input stage is beginning to saturate but is not yet fully saturated. When  $V_{\text{CM}}$  is approximately 200mV above V<sub>CC</sub>, the Schottky diodes will reverse bias, causing Q1 and Q2 to fully saturate. The Schottkys, in combination with the input devices Q1 and Q2, will cause Q1's and Q2's base current to equal their

Figure 1. LT1638 input stage

Figure 2. Input bias current vs common mode voltage

| Table 1. LT1638/LT1639 typical DC performance, 25°C |                                             |            |            |                       |

|-----------------------------------------------------|---------------------------------------------|------------|------------|-----------------------|

| Parameter                                           | Conditions                                  | $V_s = 3V$ | $V_s = 5V$ | V <sub>s</sub> = ±15V |

| Offset Voltage                                      | $V_{CM} = V_{EE}$ to $(V_{CC} - 1V)$        | 200μV      | 200μV      | 200μV                 |

| Offset Voltage                                      | $V_{CM} = V_{EE} + 44V$                     | 600μV      | 600μV      | 600μV                 |

| Input Bias Current                                  | $V_{CM} = V_{EE} \text{ to } (V_{CC} - 1V)$ | 15nA       | 15nA       | 15nA                  |

| input bias ourient                                  | $V_{CM} = V_{EE} + 44V$                     | 10μΑ       | 10μΑ       | 10μΑ                  |

| Input Offset Current                                | $V_{CM} = V_{EE} \text{ to } (V_{CC} - 1V)$ | 1nA        | 1nA        | 1nA                   |

| input Onset Gunent                                  | $V_{CM} = V_{EE} + 44V$                     | 200nA      | 200nA      | 200nA                 |

| CMRR                                                | $V_{CM} = V_{EE} \text{ to } (V_{CC} - 1V)$ | 98dB       | 98dB       | 98dB                  |

| Civinn                                              | $V_{CM} = V_{EE} + 44V$                     | 88dB       | 88dB       | 88dB                  |

| Open-Loop Gain                                      | $R_L = 10k$                                 | 1500k      | 1500k      | 500k                  |

| Output Voltage (Low)                                | No Load                                     | 5mV        | 5mV        | -14.995V              |

| Output voitage (Low)                                | $I_{SINK} = 10mA$                           | 500mV      | 500mV      | -14.5V                |

| Output Voltage (High)                               | No Load                                     | 2.965V     | 4.965V     | 14.965V               |

| Output voitage (riigii)                             | $I_{SOURCE} = 10mA$                         | 2.6V       | 4.6V       | 14.6V                 |

| Output Current                                      | Source                                      | 15mA       | 25mA       | 40mA                  |

| Output Guireill                                     | Sink                                        | 25mA       | 25mA       | 40mA                  |

| Supply Current per Amp                              |                                             | 190μΑ      | 190μΑ      | 240μΑ                 |

emitter current when the input stage is saturated, typically  $10\mu A$ . The device can operate with the input common mode as high as 44V above the negative rail. The input offset voltage for this mode of operation is typically  $600\mu V$ .

#### **Reverse-Battery Protection**

The LT1638 and LT1639 can withstand typical reverse supply voltages of 40V and are guaranteed to withstand reverse supply voltages up to 18V. The input stage incorporates phase-reversal protection to prevent the output from phase reversing when the input is forced up to 22V below the negative supply. Input-protection resistors also limit the current from becoming excessive when the input is forced up to this extreme.

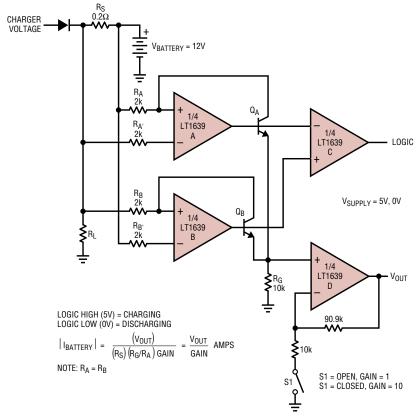

#### An Over-The-Top Application

The battery-current monitor shown in Figure 3 demonstrates the LT1638's ability to operate with its inputs above the positive rail. In this application, a conventional amplifier would be limited to a battery voltage between 5V and ground, but the LT1638 can handle battery voltages as high as 44V. The LT1638 can be shut down

by removing  $V_{CC}$ . With  $V_{CC}$  removed, the input leakage is less then 0.1nA. No damage to the LT1639 will result from inserting the 12V battery backward.

When the battery is charging, amplifier B senses the voltage drop across R<sub>S</sub>. The output of amplifier B causes Q<sub>B</sub> to drain sufficient current through R<sub>B</sub> to balance the inputs of amplifier B. Likewise, amplifier A and Q<sub>A</sub> form a closed loop when the battery is discharging. The current through  $Q_A$  or  $Q_B$  is proportional to the current in R<sub>S</sub>. This current flows into R<sub>G</sub> and is converted into a voltage. Amplifier D buffers and amplifies the voltage across R<sub>G</sub>. Amplifier C compares the outputs of amplifier A and amplifier B to determine the polarity of current through R<sub>s</sub>. The scale factor for V<sub>OUT</sub> with S1 open is 1V/A. With S1 closed the scale factor is 1V/100mA and currents as low as 5mA can be measured.

#### Conclusion

The LT1638 is an ideal candidate for general purpose op amp applications. With its Over-The-Top capability, reverse-battery protection and rail-to-rail input and output features, the LT1638/LT1639 is suitable for multiple applications.

Figure 3. LT1638 battery current monitor—an Over-The-Top application

# LTC1710: Two $0.4\Omega$ Switches with SMBus Control Fit into Tiny MSOP-8 Package

by Peter Guan

#### Introduction

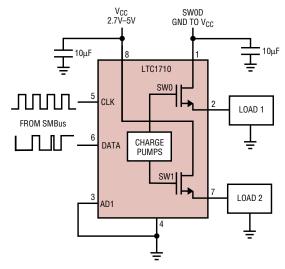

The LTC1710 SMBus dual switch is a complete solution for supplying power to portable-equipment peripherals without the need for external switches. Two internal high-side N-channel switches, each capable of delivering 300mA at an  $R_{\rm DS(ON)}$  of  $0.4\Omega,$  are available in the tiny MSOP-8 package. With a low standby current of  $14\mu A,$  the LTC1710 operates on an input voltage of 2.7V to 5.5V while maintaining the SMBus-specified 0.6V  $V_{\rm IL}$  and 1.4V  $V_{\rm IH}$  input thresholds.

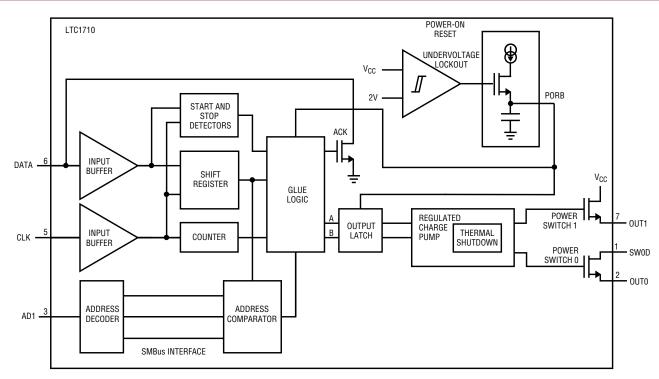

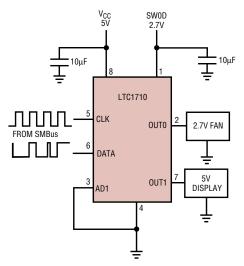

Figure 1 shows a typical application of the LTC1710 switching two different SMBus peripherals. Figure 2 shows a block diagram of the LTC1710 architecture, which can be broken down into four basic building blocks: the two N-channel power MOSFETs, the regulated charge-pump driver, the power-on reset and undervoltage-lockout units and the SMBus interface components.

#### Two $0.4\Omega$ Switches in MSOP-8

To fully enhance the power switches, the LTC1710 uses a charge-pump tripler to boost and regulate the gate drive of each switch. Running at about 300kHz, each charge pump is programmed to supply a ramped voltage to the gate of the switch, so that it turns on slowly and smoothly, avoiding large current spikes into the load. Since the charge pumps drive only the gates of the switches, only a small amount of current is needed; hence, the charge-pump caps are integrated on the IC.

The drains of the two N-channel switches are independent of each other. Switch 1's drain is connected to  $V_{\rm CC}$ , but the potential of switch 0's drain can be anywhere between  $V_{\rm CC}$  and GND. As a result, SMBus peripherals requiring different input voltages can be simultaneously switched by the LTC1710 (Figure 3).

Though unlikely in normal operating conditions, if the internal switches

become extremely hot as a result of sourcing too much output current, an internal thermal shutdown circuit becomes active at around 120°C and turns off the switch outputs temporarily until the temperature drops by about 15°C.

# Power-On Reset and Undervoltage Lockout

To ensure that the LTC1710 starts up with both switches off, an internal power-on reset (POR) signal inhibits operation until about  $300\mu s$  after  $V_{CC}$  crosses the undervoltage lockout threshold (UVLO, typically 2V). The circuit also includes some hysteresis and delay to avoid nuisance resets. Once operation begins,  $V_{CC}$  must drop below the UVLO threshold for at least  $100\mu s$  to trigger another POR sequence.

#### Three-State Programmable Address Pin

To identify itself on the SMBus, the LTC1710 has a three-state programmable address pin (AD1) that can be tied directly to  $V_{CC}$ , to GND or to  $V_{CC}$ / 2 with the help of two 1M resistors. To conserve standby current, it's preferable to tie the address pin to either  $V_{CC}$  or GND. The third state of  $V_{CC}/2$ should be used only when more than two addresses are needed on the bus. The three available addresses are 1011000 (AD1 = GND), 1011010 (AD1  $= V_{CC}$ ) and 1011001 (AD1 =  $V_{CC}/2$ ). Notice that the five MSBs of the LTC1710 addresses are hardwired to 10110XX, which, according to the SMBus specifications, places the LTC1710 directly in the reserved address range for power-plane switching.

Figure 1. Typical application: the LTC1710 switches two SMBus peripherals.

Figure 2. LTC1710 block diagram

Figure 3. The LTC1710 switches two SMBus peripherals with different input voltages.

#### **SMBus Operation**

The SMBus is a serial bus interface that uses only two bus lines, DATA and CLK, to control low power peripheral devices in portable equipment.

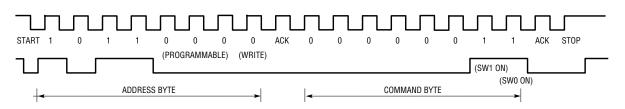

The LTC1710 is a slave-only device that uses the Send Byte protocol of the SMBus for communication. The master of the bus initiates communication to its slave devices with the Start signal, which is the switching of the DATA line from high to low while CLK is high. Upon detecting this Start signal, all slave devices on the bus, including the LTC1710, wake up and get ready to shift in the data that will follow. Beginning on the next rising CLK edge, the master sends out the first byte. The first seven bits of this byte consist of the address of the slave with which the master wishes to communicate. The last bit indicates whether the following command will be a read (logic one) or write (logic zero). Since the LTC1710 is a slave device that can only be written to by a master, it will ignore the read command, even if the address matches. If the first byte does match, then the LTC1710 will acknowledge proper reception to the master by pulling the DATA line low during the next CLK cycle. The master then sends the command byte with its two LSBs as the controlling signal for the switch outputs. A logic one turns on the internal charge pump to drive up the gate voltage and the output. A logic zero shuts down the charge pump and discharges the output to zero. After reception of the second byte, the LTC1710 again acknowledges the master by pulling DATA low for the next CLK cycle. At this point, valid data is shifted into the output latch of the LTC1710. However, the output switch won't be enabled until the Stop signal (DATA going from low to high while CLK is high) is detected. With this double buffering feature of continued on page 25

Figure 4. SMBus Send Byte protocol

# Low Distortion Rail-to-Rail Op Amps Have 0.003% THD with 100kHz Signal

by Danh Tran

#### Introduction

The LT1630/LT1632 duals and LT1631/LT1633 quads are the newest members of Linear Technology's family of rail-to-rail op amps, which provide the best combination of AC performance and DC precision over the widest range of supply voltages. The LT1630/LT1631 deliver a 30MHz gain-bandwidth product, a 10V/µs slew rate and 6nV/\day{Hz input-voltage noise. Optimized for higher speed applications, the LT1632/LT1633 have a 45MHz gain-bandwidth product, a 45V/ $\mu$ s slew rate and 12nV/ $\sqrt{Hz}$ input voltage noise. In a low supply environment, these op amps maximize system dynamic range and precision. The very large open loop gain of these devices (a few million) virtually eliminates gain error. Because input offset error is so important on low supplies, it is guaranteed over the whole rail-to-rail input range. To achieve this, these amplifiers use an LTC proprietary trim algorithm to minimize the input offset at two common mode voltages, one at the negative supply and the other at the positive supply. To make designing with these amplifiers straightforward, their performance is fully specified for 3V, 5V and ±15V supplies.

###

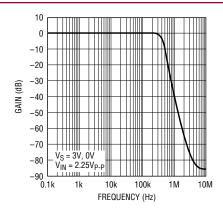

Figure 1. LT1630 total harmonic distortion + noise vs frequency

#### **Device Characteristics**

The LT1630/LT1631 have a gainbandwidth product of 30MHz, a 10V/µs slew rate and a low input noise voltage of 6nV/√Hz. With a 4.1mA typical supply current per amplifier, the LT1630/LT1631 can sink or source currents in excess of 50mA on a ±15V supply, allowing them to drive low impedance loads. Input offset voltage with a 5V supply is specified at 525µV maximum over the entire input range; a minimum open loop gain of 500,000 ensures a very small gain error. To maximize common mode rejection, the LT1630/ LT1631 also employ a patented trim technique that keeps the input offset shift to less than 525µV when the input common mode voltage is varied from rail-to-rail. The output can swing to within 40mV to either rail while providing 0.5mA output current. Furthermore, the device's characteristics change very little over the supply range of 3V to  $\pm 15$ V: the worst-case supply rejection is 87dB and the typical gainbandwidth product is constant at 30MHz. The LT1630/LT1631 have only 0.003% THD with a 100kHz signal while operating on a low supply voltage, as shown in Figure 1.

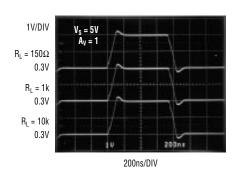

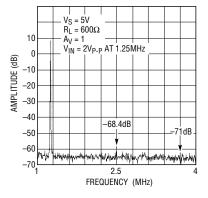

Optimized for higher frequency and slew rate applications, the LT1632/

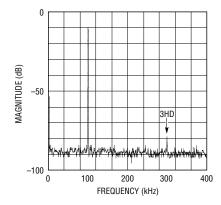

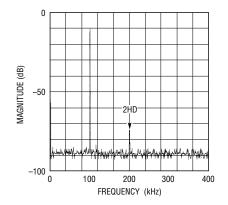

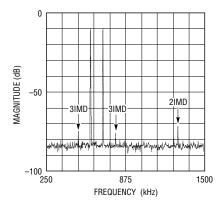

LT1633 deliver a gain-bandwidth product of 45MHz, a slew rate of 45V/us and an input voltage noise of  $12\text{nV}/\sqrt{\text{Hz}}$ . These devices consume 4.6mA of supply current per amplifier and have a short-circuit current of 70mA operating on a ±15V supply. The input offset voltage is guaranteed to be less than 1350µV over the whole input range and the open loop gain is specified to be greater than 450,000 on a 5V supply. Also, using the proprietary trim technique, the LT1632/ LT1633 is guaranteed to have an input-offset shift of less than 1500μV when the input common mode voltage is varied from rail-to-rail. Like the LT1630/LT1631, the LT1632/ LT1633's characteristics don't change much over the specified supply range of 3V to ±15V. Figure 2 illustrates the large-signal response of LT1632 with various loads for a 5V supply. Figure 3 shows the harmonic distortion of LT1632 with a 1.25MHz sinusoidal signal. Table 1 summarizes the performance of these newest rail-to-rail amplifiers.

The LT1630/LT1632 dual amplifiers are available in either 8-pin SO or 8-pin miniDIP packages. The LT1631/LT1633 quad amplifiers are available in the 14-pin SO.

Figure 2. LT1632 large-signal response

Figure 3. LT1632 harmonic distortion

|     | 1  |  |

|-----|----|--|

| - 4 | 7  |  |

|     | L. |  |

| Table 1. Amplifier characteristics: $V_S = 5V$ , $25^{\circ}C$ |                      |               |               |     |

|----------------------------------------------------------------|----------------------|---------------|---------------|-----|

| Parameter                                                      |                      | LT1630/LT1631 | LT1632/LT1633 |     |

| Gain-Bandwidth Product                                         |                      | 30MHz         | 45MHz         | Тур |

| Slew Rate                                                      | $V_S = \pm 15V$      | 10V/μs        | 45V/μs        | Тур |

| Input Noise Voltage                                            |                      | 6nV/√Hz       | 12nV/√Hz      | Тур |

| Offset Voltage                                                 | $V_{CM} = V-, V+$    | <525μV        | <1350μV       | Max |

| Offset Voltage Shift                                           | $V_{CM} = V-, V+$    | <525μV        | <1500μV       | Max |

| Open Loop Gain                                                 | $R_L = 10k$          | 500k          | 450k          | Min |

| Input Bias Current                                             | $V_{CM} = V-, V+$    | 1μΑ           | 2.2μΑ         | Max |

| Input Offset Current                                           | $V_{CM} = V-, V+$    | 150nA         | 440nA         | Max |

| Output Voltage                                                 | No Load              | 15mV          | 15mV          | Тур |

| Swing to Rail                                                  | $I_0 = 20 \text{mA}$ | 900mV         | 900mV         | Тур |

| Short-Circuit Current                                          | $V_S = 5V$           | ±40mA         | ±40mA         | Тур |

| Short-Gircuit Guffelit                                         | $V_S = \pm 15V$      | ±70mA         | ±70mA         | Тур |

| Operating Supply Voltage Range                                 |                      | 2.7V-30V      | 2.7V-30V      |     |

| Specified Supply Voltages                                      |                      | 3V, 5V, ±15V  | 3V, 5V, ±15V  |     |

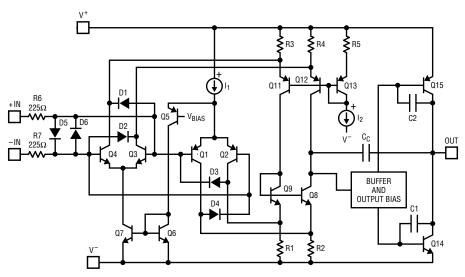

#### The Rail-to-Rail Architecture

Figure 4 shows the simplified schematic of these amplifiers. The circuit is composed of three distinct stages: an input stage, an intermediate stage and an output stage. The input stage consists of two differential amplifiers, a PNP stage (Q1-Q2) and an NPN stage (Q3-Q4), that are active over different portions of the input common mode range. Each input stage is trimmed for minimum offset voltage and maximum common mode rejection. The intermediate stage is a folded cascode configuration formed by Q8-Q12, which provides most of the voltage gain. A pair of complementary common emitter devices, Q14-Q15, creates an output stage which can swing from rail to rail. The amplifiers are fabricated on Linear Technology's proprietary complementary bipolar process, which ensures that the output devices, Q14 and Q15, possess a very similar DC and AC characteristics.

Let's first examine the input stage. Transistor Q5 switches tail current  $I_1$  between the two input stages. When the input common mode voltage,  $V_{\text{CM}}$ , is between the negative supply and 1.5V below positive supply, Q5 is reverse biased and the PNP differential pair Q1–Q2 is active. As  $V_{\text{CM}}$  moves further toward the positive supply, Q5 will be forward biased and steer

the tail current I<sub>1</sub> through the current mirror Q6-Q7 to activate the NPN differential pair. The PNP pair becomes inactive for the rest of the input common mode range, up to the positive supply. The input stages are protected by a pair of back-to-back diodes D5–D6. When a differential voltage of more than 0.7V is applied to the inputs, these diodes will turn on. preventing the emitter-base breakdown of the input transistors. To prevent the output from reversing polarity when the input voltage exceeds the power supplies, two pairs of crossing diodes, D1-D4, are employed. When the input voltage

exceeds either supply by approximately 700mV, D1–D2 or D3–D4 will turn on and force the output to the proper polarity.

The collector currents of the input pairs are combined at the intermediate stage, consisting of Q8–Q12. Most of the voltage gain of the amplifier is generated in this stage. Its output is then buffered and applied to output transistors Q14 and Q15. Capacitors C1 and C2 form local feedback loops at the output stage to lower the output impedance at high frequency.

#### **Applications**

The ability to accommodate any input and output signals that fall within the device's supplies makes these amplifiers very easy to use. They exhibit a very good transient response and can drive low impedance loads, which makes them suitable for high performance applications. The following applications demonstrate the versatility of these amplifiers.

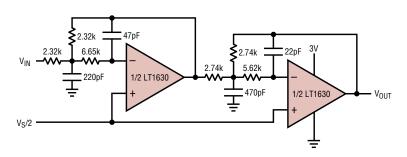

## 400kHz 4th Order Butterworth Filter for 3V Operation

The circuit shown in Figure 5 makes use of the low voltage operation and the wide bandwidth of the LT1630 to create a 400kHz 4th order lowpass filter with a 3V supply. The amplifiers are configured in the inverting mode for the lowest distortion and the output can swing rail-to-rail for the

Figure 4. LT1630 simplified schematic

Figure 5. Single-supply, 400kHz, 4th order Butterworth filter

Figure 6. Frequency response of filter in Figure 5

maximum dynamic range. Figure 6 displays the frequency response of the filter. Stopband attenuation is greater than 85dB at 10MHz. With a  $2.25V_{P-P}$ , 100kHz input signal, the filter has harmonic distortion products of less than -87dBc.

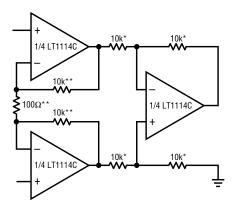

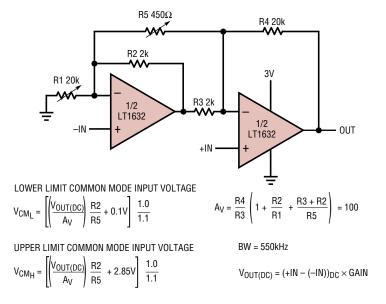

#### 40dB Gain, 550kHz Instrumentation Amplifier

An instrumentation amplifier with a rail-to-rail output swing, operating from a 3V supply, can be constructed with the LT1632, as shown in Figure 7. The amplifier has a nominal gain of 100, which can be adjusted with resistor R5. The DC output level is equal to the input voltage  $(V_{IN})$  between

the two inputs multiplied by the gain of 100. Common mode range can be calculated by the equations shown with Figure 7. For example, the common mode range is from 0.15V to 2.65V if the output voltage is at one-half of the 3V supply. The common mode rejection is greater than 110dB at 100Hz when trimmed with resistor R1. Figure 8 shows the amplifier's cutoff frequency of 550kHz.

#### Conclusion

The LT1630–LT1633 family of rail-to-rail amplifiers extends the performance of rail-to-rail operation by offering high speed characteristics

combined with precision. The combination of low distortion, high slew rate and wide bandwidth allows these amplifiers to be used in applications where the signal amplitude could be as large as the power supplies, and where both AC and DC performance are required. These amplifiers maintain their precision by specifying the input offset over the whole input common mode range and by having the typical open loop gain of a few million. These characteristics, combined with a wide supply operation and a large output current capability, make these amplifiers truly versatile and ideal for demanding applications.

Figure 7. Single-supply instrumentation amplifier

Figure 8. Frequency response of Figure 7's instrumentation amplifier

# High Speed SO-8 12-Bit ADCs Run on 5V or 3V by Ricky Chow and

by Ricky Chow and Teo Yang Long

#### Introduction

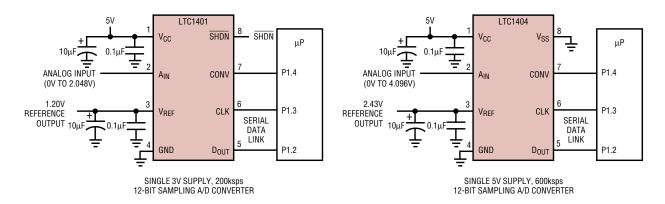

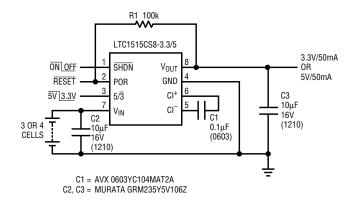

Advancing the leading edge of high speed, low power 12-bit serial ADCs in SO-8, LTC introduces the LTC 1401 and LTC1404. The LTC1401 is a single 3V supply, 200ksps 12-bit ADC. The LTC1404 is a pin-to-pin compatible upgrade of the existing LTC1400. It samples at 600ksps on either single 5V or ±5V supplies. Both of these devices are small in size but big in features. They achieve speeds that are far ahead of the pack. Once again, LTC has rewritten the record for the highest throughput per square area of board space of any 12-bit ADC on the market. Both devices satisfy tomorrow's digitally based signal-processing requirements while achieving a minimum footprint.

# Full ADC Features in an SO-8 Package

#### 3V, 5V or ±5V Supplies

The LTC1401 provides a complete 200ksps unipolar A/D solution operating on a single supply as low as 2.7V. The typical supply current is 5mA and the analog input range is from 0V to 2.048V, yielding an LSB of 0.5mV. Unlike the LTC1400 and LTC1404, the unipolar LTC1401 replaces the unused negative supply pin with a power-down input. The

user can power the chip down immediately by pulling this pin low. Like the LTC1400, the LTC1404 operates on a single 5V or ±5V supplies and consumes about 15mA. The analog input signal range is automatically determined by the supply voltage. If V<sub>SS</sub> is connected to ground, the chip operates in unipolar mode and accepts analog signals between 0V and 4.096V. If  $V_{SS}$  is connected to a -5V supply, the chip enters bipolar mode, in which case the input range is  $\pm 2.048$ V. In either mode, the LSB is 1mV. Figure 1 shows a typical application for LTC1401 or LTC1404.

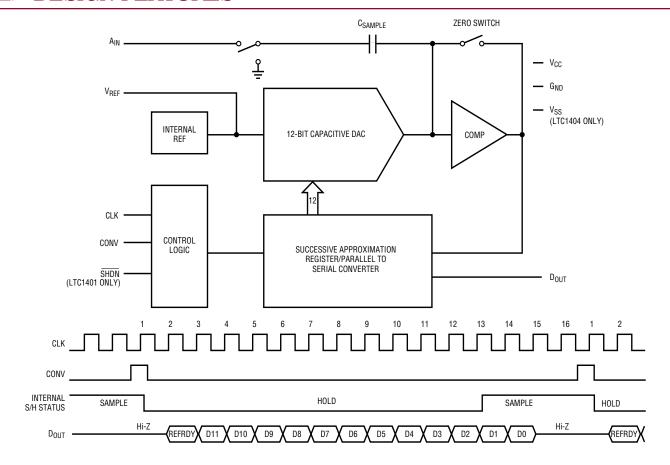

#### Reference, S/H and Serial I/O

The common features shared by both devices include a precision internal reference, which can be overdriven externally, and high frequency S/H circuitry. The high impedance analog input can be driven through a MUX without adding any DC errors due to on-resistance. The low input capacitance allows fast acquisition time for the sample-and-hold, even with high source impedance. There is a simple 3-wire digital interface to the host computer, DSP or microcontroller. The interface consists of a serial input clock (CLK), data output (DOLT) and a convert-input start (CONV) signal. The

CONV input allows precise control of each sample conversion, so vital to DSP applications that require precise sampling. The rising CLK edge synchronizes all the ADC events to make sure that none of the ADC's critical comparisons occur simultaneously with a clock edge or data-out transition. The D<sub>OUT</sub> pin is at high impedance when the ADC is not converting. During operation, it first pipes out a REFRDY bit and follows this with the 12-bit serial data. Figure 2 shows the block diagram and the digital timing. The block diagram illustrates the pinout and functional differences between the LTC1401 and LTC1404. The REFRDY bit indicates that the internal reference is ready for conversion. REFRDY is a logic 1 if the reference is valid; otherwise it outputs a 0. This bit indicator becomes a very useful feature when the chip is toggling between the active and powerdown modes.

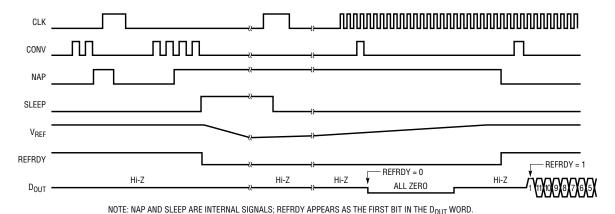

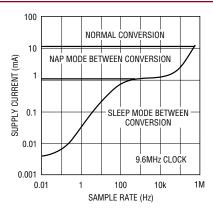

#### NAP and SLEEP Shutdown Modes

The combination of CLK and CONV signals serves another very important function. The ADCs can be placed in NAP or SLEEP mode with the proper manipulation of these two input signals. Figure 3 shows the power-down

Figure 1. LTC1401 and LTC1404 typical applications

Figure 2. Block and timing diagrams

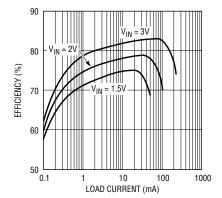

timing waveform. With CLK held at a logic low, two consecutive CONV pulses activate NAP mode and shut down all internal circuitry except the reference, which fully charges the external bypass capacitor; the REFRDY bit is high. Under this condition, the supply currents for the LTC1401 and LTC1404 are 500µA and 1.3mA, respectively. Either ADC can be reawakened quickly to resume conversion. If the ADC is not reawak-

ened and CLK is still held low, another two consecutive CONV pulses (a total of four pulses) activate the SLEEP mode and shut down the reference; the charge on its bypass capacitors goes to zero and the REFRDY bit goes low, reducing the supply current to  $6.5\mu A$  for the LTC1401 and  $8\mu A$  for the LTC1404. Figure 4 shows the power supply consumption of the LTC1404 in its various operating modes.

#### Reference Ready Indicator

In NAP or SLEEP mode, the first rising CLK edge returns the ADC to normal operation. When SLEEP is deactivated on the LTC1404, the internal reference is first powered up and the reference capacitor is slowly charged. Since the LTC1404 has limited source-current capability to charge the capacitor, a finite time is needed and this time depends on the capacitance value. Guesswork as to when the

Figure 3. NAP and SLEEP mode waveforms

Figure 4. LTC1404 power consumption in various operating modes

capacitor is fully charged is eliminated by monitoring the REFRDY bit. The REFRDY bit guarantees that the reference is steady and the digital result is correct. Some competing ADCs need an off-chip reference. With these parts, it is up to the system designer to come up with a way to put the reference to sleep and to determine just how long it takes to wake up. Because of board-level variations or varying reference loading conditions, the converted output may not be correct because of different reference wake-up times. With their proprietary power-down scheme, the high speed LTC1401 and LTC1404 can save more power when operating at low sampling rates than some "micropower" ADCs without a powerdown feature.

#### Easy to Apply

#### **Ground Plane**

As with other high resolution, high speed ADCs, the LTC1401/LTC1404 needs some basic attention to layout details. These include grounding, bypassing and lead inductance. The best performance is achieved when the LTC1401/LTC1404 is applied as an analog device and powered from an analog supply. Its ground pin should be connected to an analog ground plane. This ground plane should have only one connection to the system ground. This prevents system-ground currents from taking a short cut through the analog ground. This single connection should be made to a point near the ADC ground pin.

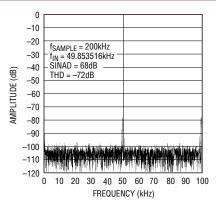

Figure 5a. LTC1401 FFT

Alternatively, a  $10\Omega$  resistor or a ferrite bead jumper instead of a direct short may help to reduce the digital noise.

#### Supply Bypassing

Noise on the power supply can cause ADC errors. At low frequencies, the converter has very good power supply rejection, but as frequency increases, all converters lose the ability to reject power-supply noise. To eliminate power-supply noise, the LTC1401/ LTC1404 V<sub>CC</sub> pin should be bypassed directly to the analog ground plane with a good 10µF AVX capacitor in parallel with a 0.1µF ceramic; for better results, another 10µF AVX capacitor can be added. At 600ksps, the LTC1404's CLK frequency can be as high as 9.6MHz. Some poor quality capacitors can lose more than 80% of their capacitance in this frequency range. Therefore, it is important to consult the manufacturer's data sheet before selecting a capacitor. For the LTC1404, at 600ksps, every bit decision must be determined within 104ns (9.6MHz). During this short time interval, the supply disturbance due to CLK transition must settle, the ADC must update its DAC, make a comparator decision, latch the new DAC information and output the serial data. Both of these ADCs have only one power supply pin, which is connected to both the internal analog and digital circuitry. Any ringing due to poor bypassing, parasitic trace inductance, CLK and CONV over/ undershoot or unnecessary Dour current loading can cause ADC errors.

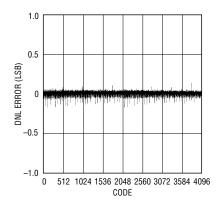

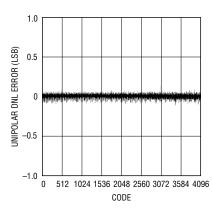

Figure 5b. LTC1401 DNL error

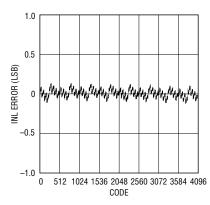

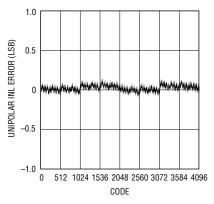

Figure 5c. LTC1401 INL error

Narrow power supply traces should be avoided. Their comparatively high inductance can lead to compromised bypass performance and conversion errors. The input signals for the CLK and CONV pins should be terminated properly. The  $D_{OUT}$  signal should be buffered if necessary to drive a long trace or heavy load.

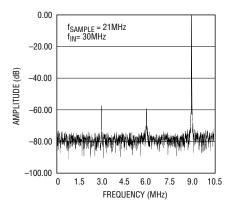

#### DC and AC Performance

With these basic concerns in mind, it is not difficult to obtain the best performance from the LTC1401 and LTC1404. The DC performance of the LTC1401 and LTC1404 includes ±1LSB INL and DNL. No missing codes are guaranteed over temperature. In addition to these excellent DC specifications, these devices have curvature-corrected 1.20V (LTC1401) or 2.43V (LTC1404) precision references. For high frequency conversion applications, the LTC1401 and LTC1404 excel, with outstanding AC performance. Figures 5 and 6 show the performance of the LTC1401 and LTC1404, respectively.

continued on page 24

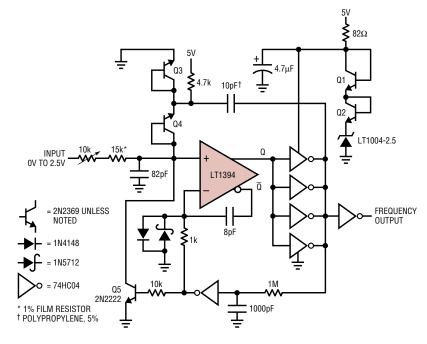

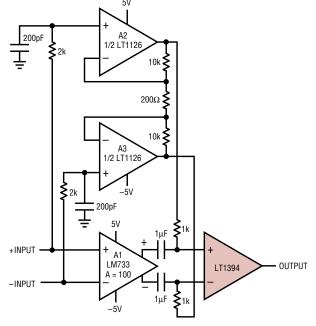

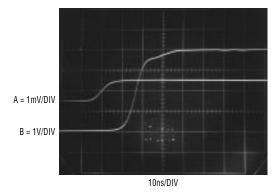

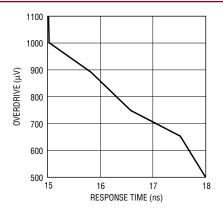

# A 7ns, 6mA, Single-Supply Comparator Fabricated on Linear's 6GHz Complementary Bipolar Process

by Jim Williams and Brian Hamilton

#### Introduction

The LT1394 is an ultrafast (7ns), low power (6mA), single-supply comparator designed to operate on either 5V or ±5V supplies. It has a maximum offset voltage of 2.5mV, complementary TTL compatible outputs and output latch capability. The LT1394 is the first product made with Linear Technology's 6GHz complementary bipolar technology. This fine-line geometry process results in a product with dramatically improved speed and power compared to industry-standard comparators developed in slower NPN-only technologies.

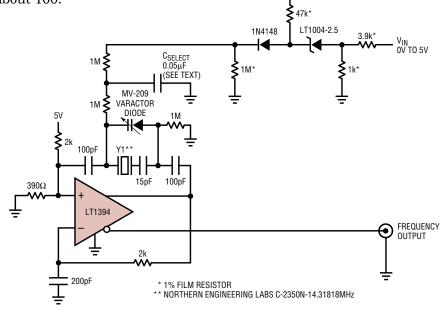

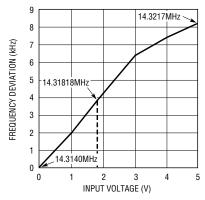

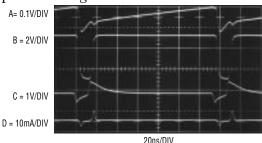

These features combine to make the LT1394 well suited for applications such as high performance NTSC crystal oscillators, single-supply voltage-to-frequency converters and high speed, high accuracy level detectors. The LT1394 is offered in SO-8 and is pin compatible with the industry-standard LT1016 and LT1116 comparators.

#### **Circuit Description**

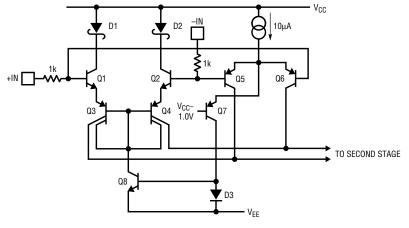

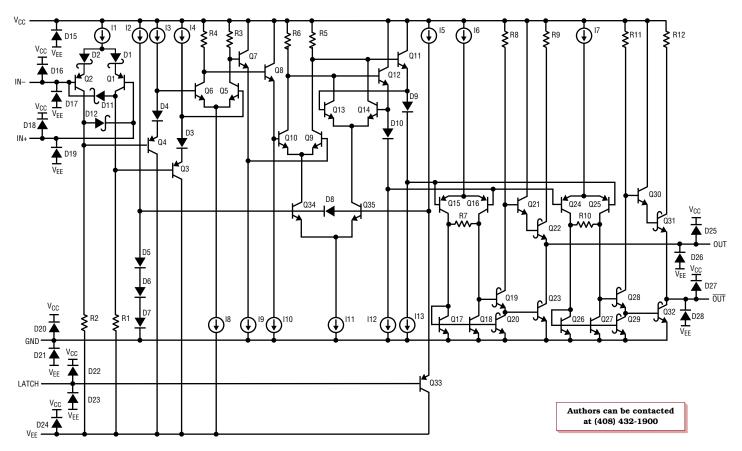

A simplified schematic of the LT1394 can be seen in Figure 1. There are differential inputs (+IN/-IN), differential outputs (OUT/ $\overline{\text{OUT}}$ ), a latch input (LATCH) and three power supply pins (V<sub>EE</sub>, V<sub>CC</sub> and GND). The circuit topology consists of a differential input

stage, a level-shifting gain stage, a latch stage and complementary output stages. The complementary output stages offer improved flexibility for the user; the latch stage provides superior sampling accuracy of the input signal without the need for an external latch.

The input stage of the LT1394 uses a PNP differential pair (Q1–Q2) with Schottky diodes in the emitters (D1–D2) and resistive loads (R1–R2). The Schottky diodes in series with the emitters allow differential input voltages that are greater than the base-emitter breakdown of the input transistors. Two additional Schottky

Figure 1. LT1394 simplified schematic

diodes (D11-D12) prevent output phase reversal when either input is taken far enough below V<sub>EE</sub> to forward bias the base-collector junction of its corresponding PNP input transistor. To allow single-supply operation, the input stage has been designed to have small voltage swings across load resistors R1 and R2. This ensures that the input PNPs will not saturate with the LT1394 inputs at

The signal path remains differential as it is buffered and level shifted via transistors Q3-Q4 and diodes D3-D4. The level shift prevents current source I<sub>8</sub> from saturating. The second gain stage, comprising transistors Q5-Q6 and resistors R3-R4, takes additional gain while level shifting the signal back to  $V_{CC}$ . The differential output of the second gain stage is buffered by transistors Q7-Q8, which then drive the latch stage.

In the latch stage, transistors Q9-Q10 and resistors R5-R6 act as a third gain stage. Q11-Q12 buffer the signal at resistors R5-R6, driving another differential pair (Q13–Q14). Q13 and Q14, when activated, provide positive feedback to resistors R5–R6, creating the latch. When the LATCH pin is low, the LT1394 is in flow-through or GAIN mode. Current I<sub>11</sub> is steered through Q34, activating the Q9-Q10 differential pair. When the LATCH pin is high, the LT1394 is in LATCH mode. Current I<sub>11</sub> is steered through Q35, activating the Q13–Q14 differential pair. The output of the gain/latch stage has additional level shifting from the emitters of transistors Q11-Q12 via diodes D9-D10. This level shifting prevents the output stage current sources I<sub>6</sub> and I<sub>7</sub> from saturating.

The LT1394 provides complementary outputs by using two identical output stages connected in opposite phases. Examining the output circuitry for the OUT pin, a PNP differential pair (Q15-Q16) is driven from the outputs of the latch stage. When I<sub>6</sub>'s current is steered through Q16, it drives R7 and the base of Q19. R7 improves switching speed by reducing the gain of the differential pair Q15-Q16 and lowering the impedance at the base of Q19. Q19's emitter current then drives the base of Q23, turning it on until the OUT pin has been pulled low and Q23's Schottky clamp diode has turned on. Conversely, if I<sub>6</sub>'s current is steered through Q15, it allows R8 to pull up the Darlington-connected output transistors Q21 and Q22, bringing the OUT pin high. For faster output switching times, Q15's collector current flows into the Q17/Q18/Q20 current mirror. Q20's collector current helps turn off Q23, whereas the collector current of Q18 helps turn off Q19.

#### Linear Technology's **6GHz** Complementary Bipolar Technology