#### NOVEMBER 1999

#### IN THIS ISSUE.

| <u>COVER ARTICLE</u><br>SOT-23 Micropower, Rail-to-Rail<br>Op Amps Operate with Inputs above<br>the Positive Supply |

|---------------------------------------------------------------------------------------------------------------------|

| Raj Ramchandani                                                                                                     |

| Issue Highlights 2                                                                                                  |

| LTC <sup>®</sup> in the News 2                                                                                      |

| DESIGN FEATURES                                                                                                     |

| 3ppm/°C Micropower Reference Draws<br>Only 50μA and Operates on 2.8V<br>                                            |

| John Wright                                                                                                         |

| Smart Battery Charger Is<br>Programmed via the SMBus                                                                |

| Mark Gurries                                                                                                        |

| LTC1755 Smart Card Interface<br>Provides Inductorless Boost and<br>Signal-Level Translators                         |

| Steven Martin                                                                                                       |

| LT <sup>®</sup> 1306: Synchronous Boost DC/DC<br>Converter Disconnects Output<br>in Shutdown14                      |

| Bing Fong Ma                                                                                                        |

| Versatile Dual Hot Swap<br>Controller/Power Sequencer Allows<br>Live Backplane Insertion                            |

| Bill Poucher                                                                                                        |

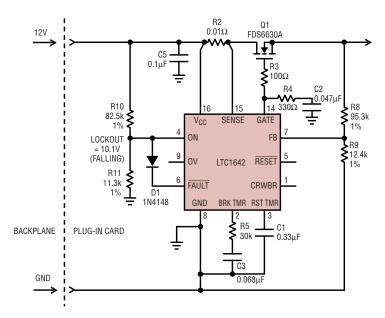

| LTC1642: a Hot Swap Controller<br>with Foldback Current Limiting<br>and Overvoltage Protection                      |

| Pat Madden                                                                                                          |

| DESIGN IDEAS                                                                                                        |

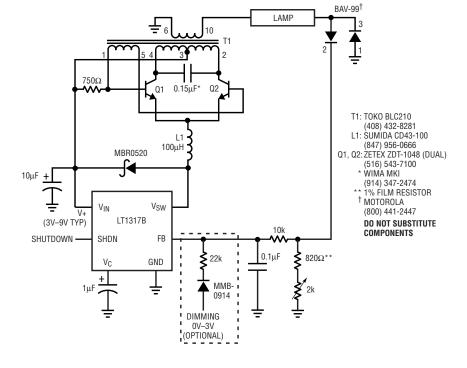

| Cost and Space Efficient<br>Backlighting for Small LCD Panels<br>27                                                 |

| Jim Williams                                                                                                        |

|                                                                                                                     |

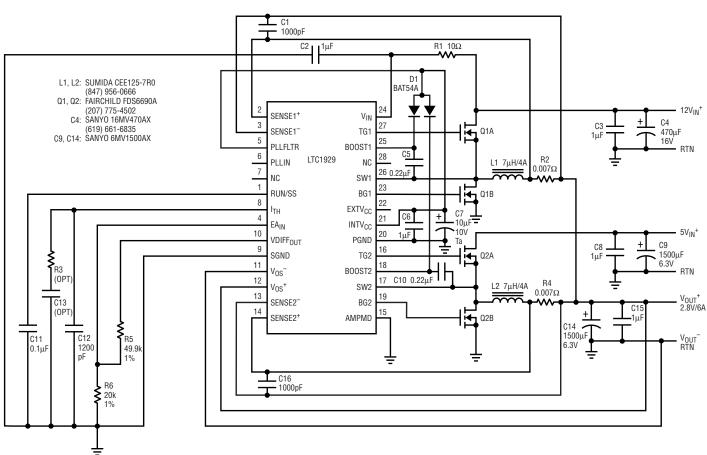

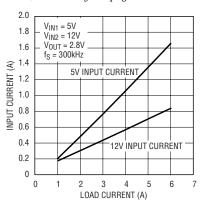

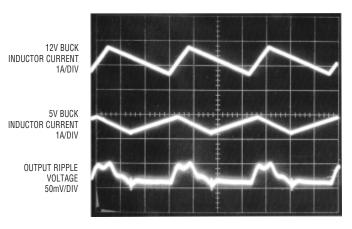

| High Efficiency PolyPhase Converter<br>Combines Power from Multiple Inputs<br>                                      |

| Wei Chen and Craig Varga                                                                                            |

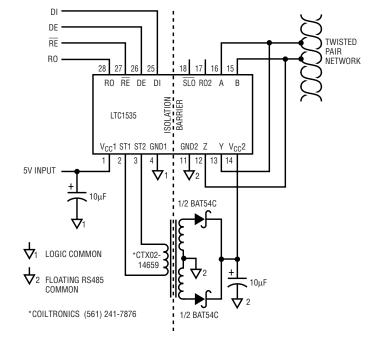

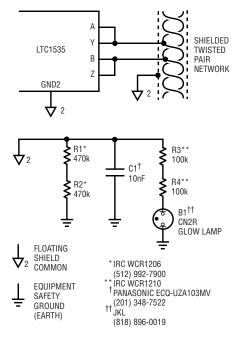

| Isolated RS485 Transceiver<br>Breaks Ground Loops 29<br>Mitchell Lee                                                |

| (More Design Ideas on pages 33–37;<br>complete list on page 27)                                                     |

| New Device Cameos                                                                                                   |

| Design Tools 39                                                                                                     |

| Sales Offices 40                                                                                                    |

|                                                                                                                     |

# SOT-23 Micropower, Rail-to-Rail Op Amps Operate with Inputs above the Positive Supply by Raj Ramchandani

#### Introduction

The only SOT-23 op amps featuring Over-The-Top<sup>™</sup> operation—the ability to operate with either or both inputs above the positive rail—are the 55µA LT1782 and the 300µA LT1783. Over-The-Top operation is important in many current-sensing applications, where the inputs are required to operate at or above the supply. A wide supply voltage range, from 2.7V to 18V, gives the LT1782/ LT1783 broad applicability. The guaranteed offset voltage of 950µV over temperature is the lowest of any SOT-23 op amp. There is even a shutdown feature for ultralow supply current applications.

#### **General Purpose Appeal**

The LT1782/LT1783 SOT-23 op amps are ideal for general-purpose applications that demand high performance. These SOT-23 op amps handle input voltages as high as 18V, both differential and common mode, independent of the supply voltage, making them ideal for applications with wide input range requirements and/or unusual input conditions. (For a description of the unique input stage that achieves this, see *Linear Technology* VIII:2, May 1998, p.10.) In applications that require more bandwidth than the 200kHz LT1782, the LT1783's sixfold increase in supply current gives it six times more bandwidth and slew rate. The LT1782/LT1783 are available in two pinouts: a 6-lead version with a shutdown feature that reduces supply current to only  $5\mu$ A and a standard-pinout 5-lead version. Table 1 summarizes the performance of these new op amps.

#### **Read All of the Specs**

The appeal of other SOT-23 op amps begins to diminish when the specifications are reviewed in detail. Common factors that keep most SOT-23 parts from being general-purpose amplifiers include low supply voltage range, high input offset voltage, low voltage gain and poor output stage performance.

To address these problems, the LT1782/LT1783 are fabricated on Linear Technology's "workhorse" high speed bipolar process, which allows the amplifiers to operate on all single and split supplies with a total voltage of 2.7V to 18V. For improved precision, thin film resistors are tightly trimmed at wafer sort; this guarantees that the input offset voltage will

continued on page 3

$\checkmark$ , LTC and LT are registered trademarks of Linear Technology Corporation. Adaptive Power, Burst Mode, C-Load, FilterCAD, Hot Swap, LinearView, Micropower SwitcherCAD, No Latency ΔΣ, No R<sub>SENSE</sub>, Operational Filter, OPTI-LOOP, Over-The-Top, PolyPhase, PowerSOT, SwitcherCAD and UltraFast are trademarks of Linear Technology Corporation. Other product names may be trademarks of the companies that manufacture the products.

# LINEAR TEGHNOLOGY

# **Issue Highlights**

Our cover article for this issue introduces the LT1782/LT1783, the only SOT-23 op amps featuring Over-The-Top operation—the ability to operate with either or both inputs above the positive rail. Over-The-Top operation is important in many current-sensing applications, where the inputs are required to operate at or above the supply. A wide supply voltage range, from 2.7V to 18V, gives the LT1782/ LT1783 broad applicability. The guaranteed offset voltage of  $950\mu$ V over temperature is the lowest of any SOT-23 op amp.

In our Design Features section, we debut a new micropower, precision voltage reference: the new LT1461 bandgap voltage reference is a low dropout reference that has superb temperature coefficient, tight output tolerance and low supply current. High output current and unmeasurable thermal regulation make the LT1461 ideal for micropower precision regulator applications. To achieve these characteristics, new wafer trim techniques were developed and extensive characterization of thermal hysteresis and long-term drift were performed.

In the power realm, we present two new products: The LTC1759 Smart Battery Charger and the LT1306 synchronous boost converter. The LTC1759 is a Smart Battery Charger that offers constant-current (CC) and constant-voltage (CV), charging modes. The LTC1759 also incorporates such features as SMBus programmable output voltage and current, external, resistor programmable current limit, LTC's patented programmable AC wall adapter current limiting to maximize charge rate and efficiencies as high as 95%.

The LT1306 is a synchronous boost DC/DC converter with the ability to disconnect its output from its input in shutdown (traditional boost converters lack this ability). Additionally, the LT1306 can regulate the output when the input voltage exceeds the

output voltage. This is useful, for example, for generating a 5V supply from a 4-cell alkaline battery. Lastly, inrush current is controlled, so a new battery can be installed without risking high inrush current as the battery initially charges the output capacitor.

Two new additions to LTC's Hot Swap<sup>™</sup> controller family, the LTC1642 and LTC1645, are premiered in this issue. The LTC1642 limits the charging current drawn by a board's capacitors, allowing safe circuit board insertion into a hot backplane. It also offers additional capabilities, some new to the Hot Swap family: a maximum recommended operating voltage of 16.5V, a programmable electronic circuit breaker with foldback current limiting, overvoltage protection to 33V, and a voltage reference and uncommitted comparator.

The LTC1645's two channels can be set to ramp up and down separately at a programmable rate or they can be programmed to rise and fall simultaneously, ensuring power supply tracking at the two outputs. Two high-side switch drivers control the external N-channel FET gates for supply voltages ranging from 1.2V to 12V. Programmable electronic circuit breakers protect against shorts at either output.

Another new interface product is the LTC1755 smart card interface. The LTC1755 provides a simple and complete solution to smart card interfacing. Requiring only two bypass capacitors and one charge pump capacitor, the LTC1755 interfaces seamlessly between a smart card socket and a host microcontroller. It is designed to comply with all of the available electrical standards for smart card interfacing.

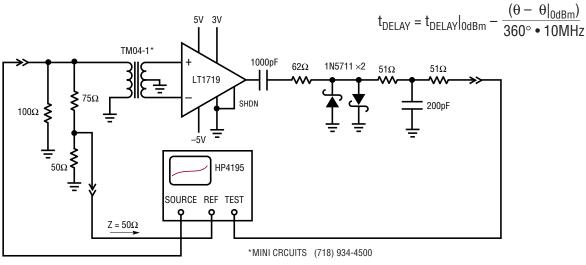

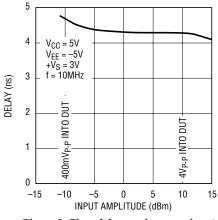

This issue offers a variety of Design Ideas, including a PolyPhase<sup>TM</sup> DC/DC converter that combines power from multiple inputs, an isolated RS485 transceiver, a sine wave to square wave converter using the LT1719 comparator and a tiny backlight power

#### LTC in the News...

On October 12, 1999, Linear Technology Corporation announced its financial results for the first quarter of fiscal year 2000. Robert H. Swanson, Chairman and CEO, stated, "Although the summer quarter historically has minimum growth, this was a strong quarter for us as demand from our customers continued strong, increasing in all major markets." The Company reported sales of \$147,531,000 (a 5% increase over sales for the previous quarter) and net income of \$58,457,000 compared with \$44,382,000 a year ago. Net sales were up 27% over last year.

Immediately after first quarter earnings were released to the press, Linear Technology Chairman and CEO Robert H. Swanson was interviewed live on CNNfn's *Digital Jam* by commentator Bruce Francis. The interview focused on Linear's earnings and the forces driving the analog market. *Digital Jam* is received nationally in over 12,000,000 households.

The Company was featured in the *New York Times* in an article entitled "Analog's Success Stories." Linear Technology was touted as a "pure play" analog company that is an apparent paradox of the digital revolution. As Jill Hauser of T. Rowe Price observed in the story, "if anything, the digital phenomenon has increased demand, it has driven analog."

*Barron's* recently speculated in an article that Linear Technology might soon become one of the S&P 500 Index companies. The S&P is the most widely used benchmark for professional investors.

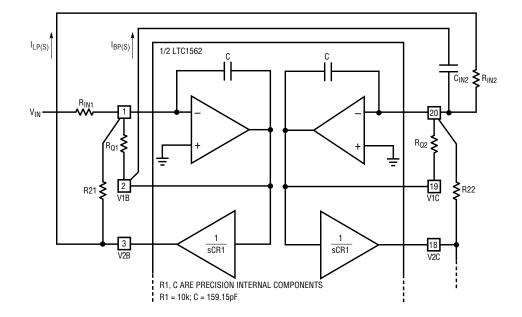

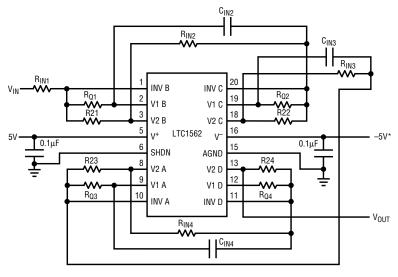

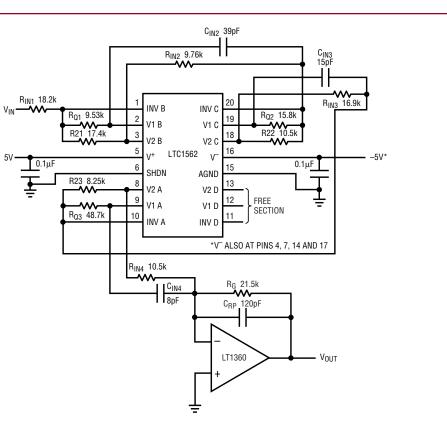

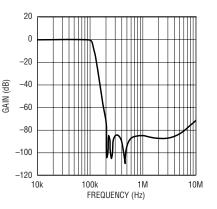

supply for palmtop devices, plus the third in a series of articles on designing filters with added stopband notches using the LTC1562 Operational Filter<sup>TM</sup> IC.

We conclude with six New Device Cameos.

| DESIGN FEATURES | 7 |

|-----------------|---|

|-----------------|---|

Table 1. LT1782/LT1783 SOT-23 guaranteed performance,  $V_s = 3V/0V$  or 5V/0V,  $T_A = 25^{\circ}C$

| Parameter                                      | LT1782      | LT1783      |

|------------------------------------------------|-------------|-------------|

| Supply Voltage Range                           | 2.7V to 18V | 2.7V to 18V |

| Supply Current                                 | 55μΑ        | 300µA       |

| Input Offset Voltage                           | 800μV       | 800µV       |

| Input Bias Current                             | 15nA        | 80nA        |

| Input Current, V <sup>+</sup> = 0V (typ)       | 0.1nA       | 0.1nA       |

| Input Offset Current                           | 2nA         | 8nA         |

| Open Loop Gain, $RL = 10k\Omega$               | 200V/mV     | 200V/mV     |

| PSRR                                           | 90dB        | 90dB        |

| CMRR                                           | 90dB        | 90dB        |

| Common Mode Range                              | 0V to18V    | 0V to 18V   |

| Output Swing, Low, Relative to V <sup>-</sup>  | 8mV         | 8mV         |

| Output Swing, High, Relative to V <sup>+</sup> | 90mV        | 90mV        |

| Slew Rate (typ)                                | 0.07V/µs    | 0.42V/µs    |

| Gain Bandwidth Product (typ)                   | 200kHz      | 1.25MHz     |

| C <sub>LOAD</sub> Stability (typ)              | 500pF       | 500pF       |

| Input Noise Voltage (typ)                      | 50nV/√Hz    | 20nV/√Hz    |

| Input Noise Current (typ)                      | 0.06pA/√Hz  | 0.14pA/√Hz  |

be under  $950\mu V$  over the commercial temperature range. This results in the lowest offset voltage of any SOT-23 amplifier. Furthermore, unlike competitive amplifiers with meager open-loop voltage gains of 20V/mV or less, the LT1782/LT1783 have a guaranteed voltage gain of 200V/mV into a 10k load.

Finally, to optimize the output stage, nitride capacitors were added to the process. This halves the area of the internal compensation capacitors and allows small die size with excellent frequency stability. In fact, the LT1782/LT1783 are stable with capacitive loads up to 500pF under all load conditions. The minimum

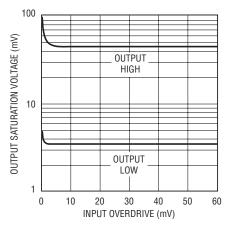

output stage current is ±18mA and the output swing is guaranteed within 8mV of ground and 90mV of the positive rail with no load. A problem encountered with other op amps in some applications is that as the output approaches the rail or ground, the gain degrades. The data sheet typically claims the output can swing to within a few millivolts of the rail, but the input overdrive required to achieve this can be quite high. This is not the case with the LT1782/LT1783; a few millivolts of input overdrive is enough to swing the outputs to their guaranteed value. Figure 1 shows the typical output saturation voltage vs input overdrive.

#### **Other Niceties**

Attention to small details is important for universal acceptance into general-purpose applications. The parts are completely specified on 3V, 5V and  $\pm 5V$  supplies and the op amps operate properly if the shutdown pin is left floating. Input-stage phasereversal protection prevents the output from reversing phase when the input is forced up to 9V below the negative supply. Input protection resistors safely limit the current to less than 3mA when the inputs are forced to this extreme.

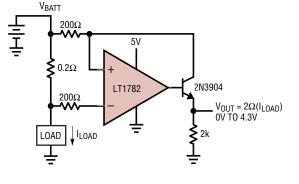

#### An Over-The-Top **Sensing Application**

The circuit of Figure 2 utilizes the Over-the-Top capabilities of the LT1782. The  $0.2\Omega$  resistor senses the load current while the op amp and NPN transistor form a closed loop, making the collector current of Q1 proportional to the load current. The 2k load resistor converts the current into a voltage. The positive input voltage,  $V_{BATT}$ , is not limited to the 5V supply of the op amp and could be as high as 18V. The LT1783 draws only 0.1nA of current through the inputs when it is powered down, extending the battery life.

#### Conclusion

Linear Technology's first SOT-23 op amps are not just space savers, they are tiny, tough and boast a variety of features that all join to make the LT1782/LT1783 truly general purpose amplifiers. These new products will enhance the superior line of operational amplifiers from Linear Technology.

Figure 1. Output saturation voltage vs input overdrive

Figure 2. Positive-supply-rail current-sense application

# 3ppm/°C Micropower Reference Draws Only 50µA and Operates on 2.8V

by John Wright

### Introduction

The new LT1461 bandgap voltage reference is a low dropout reference that has superb temperature coefficient, tight output tolerance and low supply current. In addition, high output current together with unmeasurable thermal regulation make the LT1461 ideal for micropower precision regulator applications. To achieve these characteristics, new wafer trim techniques were developed and extensive characterization of thermal hysteresis and long-term drift were performed.

#### How It's Done

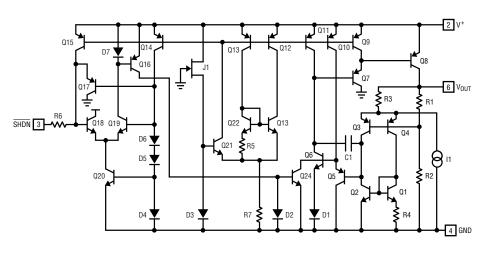

At the heart of the LT1461 is the bandgap core: Q1, Q2, Q3 and Q4 of Figure 1. Q1 and Q2 generate a  $\Delta V_{BE}$ , whereas Q3 and Q4 provide the attendant  $V_{BE}$ . The bandgap voltage is impressed across R1, and R2 provides gain for numerous voltage options. I1 provides patented curvature compensation that modifies the  $\Delta V_{BE}$  current and greatly improves the temperature coefficient. High output current and excellent load regulation are the result of careful layout techniques and four betas of current gain from Q5 through Q8. The LT1461 has a shutdown control

that can be used to turn off the reference during high output current conditions; it also has thermal shutdown or current-limit protection for the device during overload. Table 1 summarizes the performance specifications of the new reference.

#### How It's Really Done

In order for the factory to trim the output voltage to a very tight tolerance, four pins of the package are dedicated to trimming R1. This trim allows the LT1461 output voltage to be adjusted to better than 0.02%. The final specification, however, is a conservative 0.04%, because the part is measured with different factory testers and a safety margin or guardband is applied for thermal hysteresis.

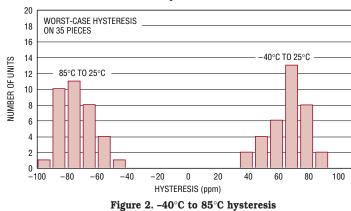

The idea of this guardband is to ensure that the parts will remain 0.04%accurate even after they are exposed to temperature excursions of  $-40^{\circ}$ C to  $85^{\circ}$ C. When a part is trimmed to high accuracy, its output voltage is valid only for the mechanical stress conditions that are present at the time of trim. The amount of stress will change with temperature because the thermal coefficient of expansion is different

Figure 1. Simplified schematic of the LT1461

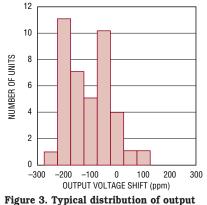

between the plastic package and the silicon chip. When the part returns to its "trimmed" temperature, there is no guarantee that the stress returns to exactly the initial amount, and the output voltage will be slightly different. This difference is called "thermally induced hysteresis shift" or "thermal hysteresis" and is expressed in parts per million (ppm). Figure 2 shows a distribution plot of thermally induced hysteresis shift on parts that were cycled several times between -40°C and 85°C. The LT1461 initial accuracy is specified broadly enough to include this hysteresis shift.

The output trim on the LT1461 uses all available pins on the package, so the temperature coefficient must be trimmed at wafer sort. If a reference has its bandgap voltage trimmed to the proper target or "bogie," it will have a near zero temperature drift. The problem is that the bogie moves with process variations and can differ from die to die. The solution is to measure the temperature coefficient at wafer sort and use an algorithm to correct the bandgap voltage. This requires wafer sorts at 75°C and 25°C to establish the drift. For example, if the bandgap voltage is trimmed to 1.2000V at 75°C and it moves 300µV to 1.2003V at 25°C, this corresponds to a -5ppm/°C drift. Once the TC is known, the bandgap voltage can easily be trimmed for zero TC by adjusting R3. The TC distribution widens when the parts are assembled in plastic because of stress on Q3 and Q4.

#### What the User Knows

Users encounter several problems when applying precision references and again thermal hysteresis is front and center. When a reference is soldered into a PC board, the elevated temperature and subsequent cooling

| Table 1. LT1461 performance, $V_{IN} = V_{OUT} + 0.5V$ |                           |       |      |      |                    |

|--------------------------------------------------------|---------------------------|-------|------|------|--------------------|

| Parameter                                              | Conditions                | Min   | Тур  | Max  | Units              |

| Output Voltage                                         | LT1461A                   | -0.04 |      | 0.04 |                    |

|                                                        | LT1461B                   | -0.06 |      | 0.06 | %                  |

| Output Voltage                                         | LT1461C                   | -0.08 |      | 0.08 | /0                 |

|                                                        | LT1461D                   | -0.15 |      | 0.15 |                    |

|                                                        | LT1461A                   |       |      | 3    |                    |

| Output Voltage<br>Temperature Coefficient              | LT1461B                   |       |      | 7    |                    |

|                                                        | LT1461C                   |       |      | 12   | ppm/°C             |

|                                                        | LT1461D<br>-40°C to 125°C |       |      | 20   |                    |

| Load Regulation                                        | Sourcing<br>0mA to 50mA   |       | 12   | 30   | ppm/mA             |

| Dropout Voltage                                        | Sourcing 1mA              |       | 0.13 | 0.3  | V                  |

| Supply Current                                         | No Load                   |       | 35   | 50   | μA                 |

| Output Voltage Noise                                   | $0.1 Hz \le f \le 10 Hz$  |       | 8    |      | ppm <sub>P-P</sub> |

| Long-Term Drift of<br>Output Voltage                   |                           |       | 60   |      | ppm/√kHr           |

| Thermal Hysteresis                                     | –40°C to 85°C             |       | 65   |      | ppm                |

cause stress that is very different from stress that is caused by automatic testers at the LTC factory. Additionally, there is now an unrelieved mechanical bias on the leadframe when the solder cools. Figure 3 shows the SO-8 LT1461 output shift of about –100ppm after IR soldering onto a PC board. After 336 hours, as the stress relaxes, the output voltage typically shifts about 45ppm back toward the initial state where the device was factory trimmed.

Another type of stress is caused if a PC board is flexed, for example when held in a card cage. The stress on the board is transmitted directly to the IC package. A simply way to reduce the stress-related shifts is to mount the reference near the short edge of the PC board or in a corner. The board edge acts as a stress boundary, or a region where the flexure of the board is minimum. The package should be mounted so that the leads absorb the stress and not the package. (See "Understanding and Applying Voltage References," in *Linear Technology* VII:2 and VII:3, June and August, 1997, for more information on the effects of stress on voltage reference performance and techniques for mitigating it.)

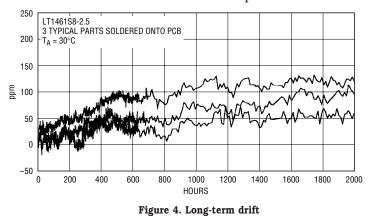

### Long-Term Drift

Some manufactures are now touting phenomenal long-term drift specifications. Long-term drift cannot be extrapolated from accelerated high temperature testing. This erroneous technique gives drift numbers that are wildly optimistic. The only way long-term drift can be measured is over the time interval of interest. The erroneous technique uses the Arrhenius Equation to derive an acceleration factor from elevated temperature readings. The equation is:

$$A_{\rm F} = e^{\frac{{\rm E}_{\rm A}}{{\rm K}}} \cdot \left(\frac{1}{{\rm T}1} - \frac{1}{{\rm T}2}\right)$$

where:  $E_A$  = Activation Energy (assume 0.7)

K = Boltzmann's Constant

T2 = Test Condition Temperature in Kelvin

T1 = Use Condition Temperature in Kelvin

To show how absurd this technique is, compare the LT1461 data. Typical 1000hr long-term drift at 30°C = 60ppm. The typical 1000hr longterm drift at 130°C = 120ppm. From the Arrhenius Equation the acceleration factor is:

$$A_{\rm F} = e^{\frac{0.7}{0.0000863} \cdot \left(\frac{1}{303} - \frac{1}{403}\right)} = 767$$

The erroneous projected long-term drift is:

#### 120ppm/767 = 0.156ppm/1000hr at 30°C

For a 2.5V reference, this corresponds to a 0.39µV shift after 1000 hr. *continued on page 36*

Figure 3. Typical distribution of output voltage shift after soldering onto PC board

Linear Technology Magazine • November 1999

# Smart Battery Charger Is Programmed via the SMBus

by Mark Gurries

### Introduction

Smart Batteries are becoming prevalent in the laptop computer world because they offer an industry-standard, high accuracy "gas gauge" system. These batteries conform to a set of specifications that define the operation of all of the components in a Smart Battery powered System (SBS). The battery has an embedded controller that tracks information related to battery charging and use. This information is provided to the system via a serial, 2-wire SMBus interface, a variant of the I<sup>2</sup>C<sup>™</sup> bus in wide use today. The battery can be queried for information on remaining capacity, total capacity, time remaining at current rate of discharge, discharge current, terminal voltage and so on. Since most Smart Batteries can become a master on the bus, the battery can control the Smart Battery Charger for optimal charging. The LTC1759 Smart Battery Charger IC is designed to be controlled by this type of Smart Battery. In addition, a safety signal provided by the battery indicates whether the battery is present in the system and warns of possible thermal problems or battery faults if other systems fail. The emphasis of the SBS is on safety, ease of use and compatibility.

There are two types of Smart Battery Chargers (SBCs) allowed by the SBS specifications. A Level 2 charger, such as the LTC1759, is a slave on the SMBus and responds to commands from the battery to control charging. A Level 3 charger can be either a slave or a master on the SMBus, since it can query the battery to determine charging information. The SBC is independent of batterychemistry type. It provides charging current and charging voltage in response to commands from the battery. Charge termination is sent by the battery as either zero current or I<sup>2</sup>C is a trademark of Philips Electronics N.V.

zero voltage or as "terminate charge" alarm. Charging will also terminate if the safety signal indicates that the battery is not present or the battery is too hot to charge safely.

The LTC1759 is a complete Level 2 Smart Battery Charger. It is able to autonomously charge a Smart Battery by receiving and interpreting commands over its built-in SMBus interface. The LTC1759 adheres to all the safety requirements of the Smart Battery Charger Specification, including 3-minute timers that protect from SMBus communication failures and overcharging of Li-Ion batteries during wake-up mode-features absent from some competing solutions. Hardware-programmable current and voltage limits provide an additional level of protection that cannot be altered by errant software.

The LTC1759 manages all the complexities of a Smart Battery Charger System. This is appealing to those who wish to support Smart Batteries without getting involved in all the details. SBC compliance, safety, output voltage accuracy, SMBus accelerators and LTC's patented wall adapter current limiting are just a few of the features that make this an outstanding part.

#### LTC1759 Smart Battery Charger Features

The LTC1759 merges the intelligence of a Smart Battery Charger with a constant-current (CC), constant-voltage (CV), current mode switching battery charger circuit. The LTC1759 incorporates the following features:

- □ 0.5% output voltage accuracy at room temperature, 1% over temperature range

- □ 5% output current regulation

- An external, resistor-programmable voltage limit, with four ranges that support stacking of the popular 4.2V battery cell

- □ An SMBus programmable output voltage, from 2.465V to 21V in either 16mV or 32mV granularity, depending upon the programmed voltage range (10-bit resolution)

- An external, resistor-programmable current limit with four limits: 1A, 2A, 4A and 8A

- An SMBus programmable output current with 10-bit resolution over all ranges

- LTC's patented programmable AC wall adapter current limiting to maximize charge rate

- Low  $V_{IN}$ -to- $V_{OUT}$  operation (dropout < 0.5V)

- □ 95% efficiency

- □ Compliant with Smart Battery Charger Specification Rev. 1.0, Level 2

- Low power consumption when AC is not present, while remaining compliant with all Smart Battery Charger requirements for status and interrupts

- □ Built-in SMBus accelerators (similar to the LTC1694)

- New 36-pin narrow SSOP package (0.209" wide)

#### **Circuit Description**

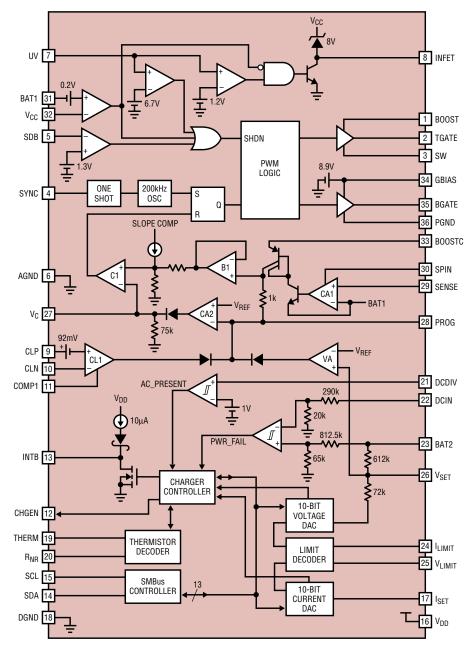

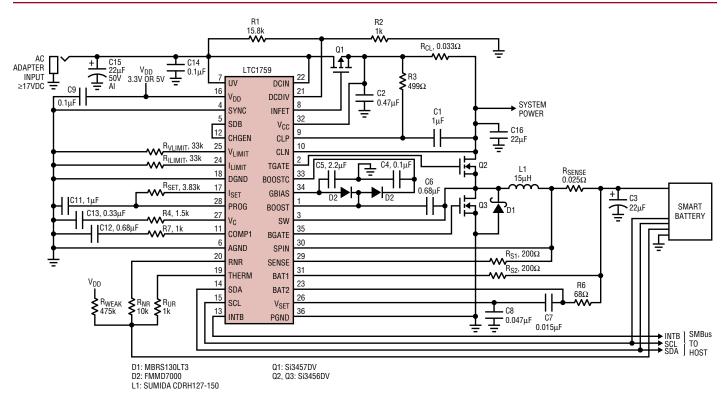

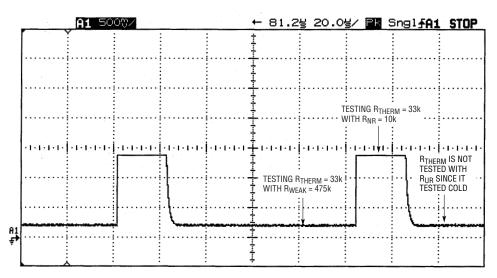

The LTC1759 is composed of a synchronous, current mode, PWM step-down (buck) switcher controller, a charger controller, two 10-bit DACs to control charger parameters, a thermistor Safety Signal decoder, hardware voltage and current limit decoders and an SMBus controller block (refer to Figure 1).

The Smart Battery or system controller programs both constantcurrent (CC) and constant-voltage (CV) limit values though commands over the SMBus interface. The buck converter uses N-channel MOSFETs for switches, allowing low cost, high efficiency operation. It also provides reverse battery discharge protection and ultralow dropout operation. A

When a constant-voltage value is received via an SMBus transmission, the value is scaled, adjusted to cancel offset and limited to a value below that programmed by the R<sub>VLIMIT</sub> resistor. This modified value programs the voltage DAC, setting the DC charging voltage. The voltage DAC drives the bottom of an internal voltage divider network. The top of the voltage divider is connected directly to the battery output though the BAT2 pin. A voltage error amplifier, VA, compares the divided battery voltage on the V<sub>SET</sub> pin with an internal, precision reference voltage. The output of the VA amp is configured as a current source that can drive the PROG pin. The PROG pin is a current summing node for both current and voltage feedback loops. The VA loop steals control of the current feedback loop when the battery voltage exceeds the programmed voltage, forcing the charging current down to the level required to maintain the programmed voltage. Since the  $\Delta\Sigma$  DAC output is in the form of a series of pulses, a smoothing network is needed to filter the pulses into DC at the  $V_{SET}$  pin. The capacitors C5 and C4 form a capacitance divider that provides some filtering of the feedback voltage from the battery while filtering the DAC pulses.

The LTC1759 requires two power supplies. The PWM circuitry runs directly off the wall adapter supply through the  $V_{CC}$  pin, whereas the logic functions run independently from the V<sub>DD</sub> supply. This allows the PWM circuitry to go into 40µA micropower shutdown mode when AC power is removed, allowing the logic and SMBus activity to remain alive, as required by Intel's ACPI standards. This separate supply also allows the logic and SMBus to run at 3V or 5V depending on the system designer's needs. To minimize power draw of the LTC1759 logic, the logic circuits are driven by a clock circuit that shuts down when there is no activity and wakes up to service SMBus activity or to generate interrupts. Once the request is serviced, the LTC1759 goes back to sleep.

Figure 1. LTC1759 block diagram

thermistor safety-detection circuit isused to detect the presence of a battery and determine whether the temperature of the battery allows safe charging to occur. Linear Technology's patented input current limiting feature is implemented, allowing the fastest battery charge times without overloading the wall adapter.

When a constant current value is received via an SMBus transmission, it is scaled and limited to a value below that programmed by the  $R_{ILIMIT}$  resistor. This modified value programs the current DAC, setting the DC charging current. The current DAC is a

10-bit delta-sigma DAC that sinks current from the PROG pin when charging current is desired (refer to Figure 2). Amplifier CA1 senses the voltage drop across  $R_{SENSE}$  and forces this voltage across  $R_{S2}$  (200 $\Omega$ ); the current through  $R_{S2}$  is sent through a current mirror as a pull-up current on the PROG pin. The matching of current through  $R_{S2}$  with current from the PROG pin by CA2 implements constant-current operation. Since the delta-sigma DAC output is a series of pulses, a smoothing capacitor is needed to filter the pulses into DC.

# ▲ DESIGN FEATURES

Shutdown of the PWM through the CHGEN–SDB pin combination occurs when the AC power is lost or the battery is removed. The LTC1759 detects the AC loss through the DCDIV pin. This threshold is usually set just below the lowest valid voltage of the wall adapter. AC power status may be read by the system over the SMBus. The UV pin is only used to put the PWM circuitry into micropower shutdown and is connected directly to the wall adapter supply.

Inductor selection is not critical with the design, since the loop response of the charger is intentionally set to be very slow. Almost any value will work, with a practical lower limit of about  $15\mu$ H. Lower inductance will create higher ripple currents, requiring a lower ESR capacitor on the output. It will also cause cosmetically ugly discontinuous switching operation to occur at higher currents than necessary.

Output capacitor selection is not ESR critical but must be able to handle all of the ripple current from the charger. Do not count on the battery to carry the ripple current because the effective impedance as seen by

#### Figure 2. A complete 4A Smart Battery Charger

the charger can be much greater than the ESR of the capacitor. Many battery packs have built-in series-protection MOSFETs that raise the ESR of the battery. There may also be optional power-routing MOSFETs in series with the battery in multiple-battery configurations, further increasing the battery ESR. From the charger point of view, the output capacitor ESR can be as high as  $1\Omega$ , allowing a wide range of capacitor options. When using a resistive or electronic load, some instability may occur. This can be fixed by adding a temporary  $300\Omega$ resistor in series with the PROG pin capacitor or putting a 10µF capacitor on the output. Avoid using ceramic capacitors in the output because they tend to make noise when the switcher goes discontinuous and starts to drop cycles at audible frequencies under very light load currents-use tantalums instead. Input capacitance selection is driven by the input ripple current of the charger, which is usually 1/2 of the maximum output current. For a 4A charger, a  $22\mu$ F, 50V ceramic is recommended, since this part can typically handle 2A of ripple current. It also takes up the

least amount of space and can cost less than other capacitor options.

Current protection, from battery to wall adapter, is provided by a P-channel MOSFET (Q1). A voltage comparator monitors the voltage across the MOSFET and will turn it off when the wall adapter drops to less than 200mV above the battery voltage. Although an inexpensive diode could be used instead of this MOSFET, the MOSFET only adds 100mV to the already low 0.4V dropout mode of operation without producing extra heat. During startup without a battery, the MOSFET parasitic diode is used to allow wall adapter power to reach the  $V_{CC}$  pin and power up the PWM control circuitry.

Primary compensation is done on the PROG pin; however, DAC pulse filter requirements determine the effective value of the capacitor. Pulse ripple current must be less than 20mV or loop jitter will occur, giving the appearance of loop instability at light charging currents. The  $V_C$  pin capacitor's primary function is to provide soft-start support. There must always be a resistor of 1.5k in series

| Table 1. $I_{LIMIT}$ trip points and ranges        |         |                                                                                                     |                            |  |  |

|----------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------|----------------------------|--|--|

| R <sub>ILIMIT</sub>                                |         | Nominal Charging Current Range                                                                      | Granularity                |  |  |

| 0Ω                                                 |         | 0 < I < 1023mA                                                                                      | 1mA                        |  |  |

| 10k                                                |         | 0 < I < 2046mA                                                                                      | 2mA                        |  |  |

| 33k                                                |         | 0 < I < 4092mA                                                                                      | 4mA                        |  |  |

| Open (>250k) or shorted to $V_{DD}$ 0 < I < 8184m  |         | 0 < I < 8184mA                                                                                      | 8mA                        |  |  |

| Table 2. V <sub>LIMIT</sub> trip points and ranges |         |                                                                                                     |                            |  |  |

|                                                    | Table 2 | $P_{\rm LIMIT}$ trip points and ranges                                                              |                            |  |  |

| R <sub>vlimit</sub>                                |         | e. V <sub>LIMIT</sub> trip points and ranges<br>al Charging Voltage (V <sub>OUT</sub> ) Range       | Granularity                |  |  |

| R <sub>vlimit</sub><br>0                           |         |                                                                                                     | <b>Granularity</b><br>16mV |  |  |

|                                                    |         | al Charging Voltage (V <sub>out</sub> ) Range                                                       | -                          |  |  |

| 0                                                  |         | al Charging Voltage (V <sub>out</sub> ) Range<br>2465 < V <sub>out</sub> < 8432mV                   | 16mV                       |  |  |

| 0<br>10k                                           |         | al Charging Voltage ( $V_{out}$ ) Range<br>2465 < $V_{out}$ < 8432mV<br>2465 < $V_{out}$ < 12,640mV | 16mV<br>16mV               |  |  |

2465 < V<sub>OUT</sub> < 32,768mV

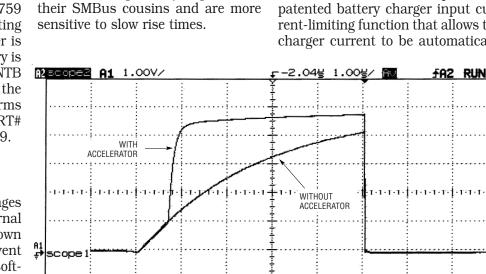

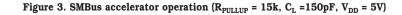

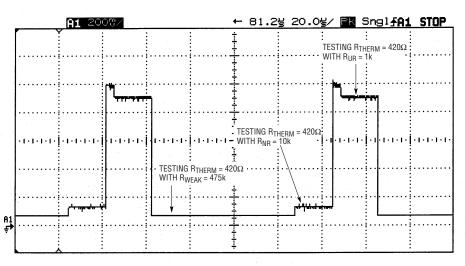

Both SCL and SDA have dynamic pull-up circuits that improve the rise time on systems with significant capacitance on the two SMBus signals. The dynamic pull-up circuitry detects a rising edge on SDA or SCL and applies 2mA-5mA pull-up to  $V_{\text{DD}}$ for approximately 1µs (Figure 3). This action allows the bus to meet SMBus rise-time requirements with as much as 150pF on each SMBus signal. The improved rise time will benefit all of the devices that use the SMBus line, especially devices that use the I<sup>2</sup>C logic levels.

#### AC Adapter Current Limiting

Wall adapters are typically AC/DC converters with 20V output at 3A-4A of load current. When a notebook is running, all of the available current from the wall adapter may be consumed by the system, leaving no power for charging the battery. However, as soon as the system's power requirements drop below the wall adapter's current limit, battery charging can resume. In order to recharge the battery in the shortest time possible, the recharging should start as soon as there is any current leftover from the system. The ideal situation is when the sum of battery charging current and the system current is just below the wall adapter's current limit. The LTC1759 incorporates a patented battery charger input current-limiting function that allows the charger current to be automatically

32mV

in the lower ranges. The voltage limits

Unlike the I<sup>2</sup>C bus, which allows the

use of variable pull-up currents on

the bus signals, the SMBus pull-up

current is specified as a maximum of

350µA. In larger systems, the capaci-

tance load on the SMBus can cause

rise-time violations ( $T_{RISE} > 1 \mu s$ ),

which could result in a communica-

tion failure. This is especially the case

when I<sup>2</sup>C devices are mixed with

SMBus-compliant devices on the same

bus. The thresholds of the I<sup>2</sup>C bus

receivers are generally higher than

are ROM mask programmable.

**SMBus Acceleration**

with the  $V_{\rm C}$  pin capacitor to allow proper shutdown.

Open or tied to V<sub>DD</sub>

From a thermal standpoint, the output voltage remains approximately 0.5% accurate over the battery temperature charging range. This higher precision allows a higher charge capacity in the battery, and, more importantly, will cause fewer problems with voltage-based charge termination circuitry in the battery.

#### **SMB** Alert

The SBS standards allow for the option of an open-collector interrupt line to notify the host when a critical power event has occurred. This feature is called SMBALERT#. The LTC1759 implements this feature by asserting the INTB line low when AC power is lost or restored and when a battery is physically installed or removed. INTB is cleared when the host reads the LTC1759 status register or performs a successful read of the SMBALERT# Response address of the LTC1759.

#### Setting Safe Voltage and Current Ranges

The LTC1759 voltage/current ranges are programmed with two external resistors,  $R_{VLIMIT}$  and  $R_{ILIMIT}$ , as shown in Tables 1 and 2. These limits prevent communication errors or errant software from causing the charger to damage the battery. At the same time, the variable granularity allows for better control of voltage and current

| Table 3. Safety signal resistance ranges |                                                         |             |  |  |  |  |

|------------------------------------------|---------------------------------------------------------|-------------|--|--|--|--|

| Safety Signal Resistance                 | ChargerStatus Bits                                      | Description |  |  |  |  |

| 0Ω–500Ω                                  | SAFETY_UR = 1<br>SAFETY_HOT = 1<br>BATTERY_PRESENT = 1  | Underrange  |  |  |  |  |

| 500Ω–3k                                  | SAFETY_HOT = 1<br>BATTERY_PRESENT = 1                   | Hot         |  |  |  |  |

| 3k–30k                                   | All Safety Bits Clear<br>BATTERY_PRESENT = 1            | Ideal       |  |  |  |  |

| 30k–100k                                 | SAFETY_COLD = 1<br>BATTERY_PRESENT = 1                  | Cold        |  |  |  |  |

| >100k                                    | SAFETY_OR = 1<br>SAFETY_COLD = 1<br>BATTERY_PRESENT = 0 | Overrange   |  |  |  |  |

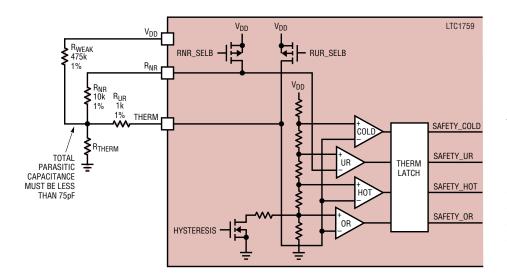

Figure 4. LTC1759 safety-signal-monitoring circuitry

Figure 5. Testing a cold thermistor

reduced to avoid overloading the wall adapter, yet still charge the battery with the maximum available current.

### Improved Safety Signal Sensing

The Safety Signal in most Smart Batteries is a resistor or thermistor to the battery's negative terminal. The SBC must sense the resistance of the Safety Signal to ground and determine if the battery is connected and whether it is safe to charge. The SBC must report the status of the Safety Signal during an SMBus read of the ChargerStatus() register. Table 3 shows the five ranges of resistance and what the ChargerStatus() bits must indicate.

The LTC1759 monitors the safety signal using a state machine to control the thermistor sensing scheme of Figure 4. This approach allows the LTC1759 to conserve power while supporting battery-presence detection and safety signal reporting when AC is not present. It also provides high noise immunity at the underrange-to-hot trip point.

The state machine sequentially switches R<sub>WEAK</sub>, R<sub>NR</sub> and R<sub>UR</sub> to pullup against the battery's internal thermistor. The resulting voltage is monitored by the comparators and used to determine the thermistor's operating range. The state machine is able to sample the safety signal with all three resistors in 100µs. This allows the thermistor to be read during an SMBus read requesting Safety Signal status and then shut down to conserve power. A system using a fixed 10k pullup for all ranges will waste current when AC is not present. R<sub>WEAK</sub> is used to continuously monitor battery presence; it uses very little current and allows detection of the insertion or removal of a battery regardless of whether or not AC is present.  $R_{NR}$  is used to determine if the safety range is cold or ideal.  $R_{IIR}$  is used to determine if the safety range is hot or underrange. The testing of R<sub>THERM</sub> is shown for a cold and underrange thermistor in Figures 5 and 6, respectively. When AC is present, the state machine continuously tests the

continued on page 18

# LTC1755 Smart Card Interface Provides Inductorless Boost and Signal-Level Translators

by Steven Martin

### Introduction

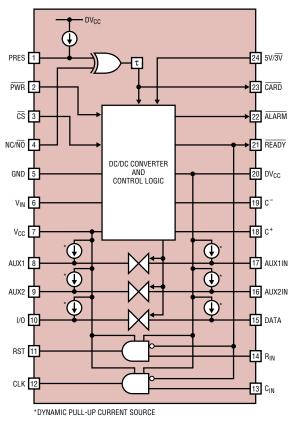

Already common in Europe and some of the Far East, smart cards may soon replace magnetic stripe cards in the U.S. The LTC1755 provides a simple and complete solution to smart card interfacing. Requiring only two bypass capacitors and one charge pump capacitor, the LTC1755 interfaces seamlessly between a smart card socket and a host microcontroller. It is designed to comply with all of the available electrical standards for smart card interfacing. Figure 1 shows the LTC1755 in a typical smart card application.

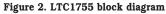

Figure 2 shows the block diagram of the LTC1755. An internal power management unit delivers a selectable 3V or 5V regulated output voltage to the smart card. Two unidirectional and three bidirectional communication channels provide the signal translation necessary to interface from a microcontroller at one supply voltage to a smart card at another supply voltage. A smart card detection channel observes the state of a mechanical switch and delivers the information to the microcontroller after an appropriate debounce period. Finally, the LTC1755 provides all fault detection necessary to comply with both the EMV and ISO-7816-3 smart card

standards. These include short-circuit detection, smart card removal during a transaction and undervoltage and overtemperature faults. In the event of a fault condition, the smart card is properly deactivated and an alarm output notifies the microcontroller of the fault.

#### Power Management Unit

Unlike solutions that require an external inductor and current sense resistor to generate power to the card, the power management section of the LTC1755 requires only a small flying capacitor to provide step-up capability. Sense circuitry determines how much input voltage is available and decides whether to step the input voltage up or down to provide the required output voltage to the smart card. For example, if the input supply voltage is 3.3V and the required smart card

voltage is 5V, the LTC1755 will operate as a charge pump to deliver the higher voltage; if the input supply voltage is 5V and the required smart card voltage is 3V, it will automatically step down to provide the correct output voltage.

The entire LTC1755, including the power management circuitry, is designed to consume low power under light or no load conditions. This can result in considerable power savings for battery-powered applications. Furthermore, the shutdown current is only several microamperes.

Figure 1. LTC1755 typical application

# **↓ DESIGN FEATURES**

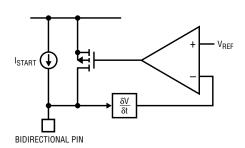

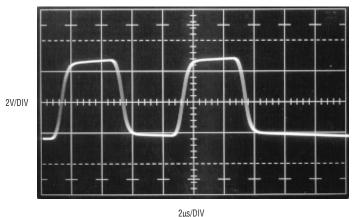

To prevent high inrush current during turn-on, an automatic softstart feature increases the supply voltage of the smart card at a fixed rate. This is particularly important when the LTC1755 is in step-up mode because the input current will be twice the output current. With a 10µF output capacitor, the rise time of approximately 2ms limits the input current to 50mA, thus preventing start-up problems. The READY pin tells the microcontroller when the output voltage has reached its final value. This signal also enables the communication channels, thereby ensuring proper compliance with smart card standards. Figure 3 shows the card supply voltage ramp as well as the **READY** pin indicating that the output has reached its final state.

During smart card deactivation, either by direct user control or by automatic fault deactivation, the LTC1755 discharges the smart card supply pin in under 250µs. Rapid discharge is important to ensure that the card's supply is completely removed in the event of smart card removal during a transaction. This requirement is specified in various smart card standards.

#### **Bidirectional** Communication Channels

There are three bidirectional channels for communicating with the smart card. These channels, which are opendrain  $I^2C^{TM}$  style, provide level translation, direction arbitration and short-circuit protection. Unlike analog approaches, the LTC1755 uses control logic with active pull-up and pull-down devices on both sides of the channel. This allows the required source and sink currents to be achieved independent of the input voltage on the transmitting side of the channel. The direction-control logic arbitrates which side of the channel is the *talker* and which side is the *listener*. Upon receipt of a low on one side of the channel, that side becomes the talker and the other side becomes the listener. Transmission in the opposite direction is instantly blocked to prevent the channel from latching. Once the talker side of the channel is relinquished, both sides return high and either side is a candidate to become the next talker.

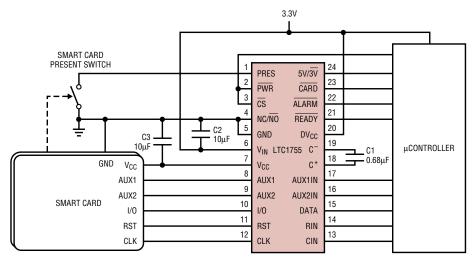

To meet the stringent rise-time requirements imposed by ISO-7816-3 while keeping power dissipation and  $V_{OL}$  to a minimum, an accelerator circuit (see Figure 4) is built into each pull-up current source on the bidirectional channels. Normally, a small current, I<sub>START</sub>, pulls each bidirectional pin to its respective power supply rail. An open-drain transistor can easily overcome I<sub>START</sub> whenever a low is asserted. When the low is relinquished, ISTART slowly begins to charge the pin toward its rail again. An internal edge-rate-detection comparator notices that the node is moving upward and fires a large pull-up cur-

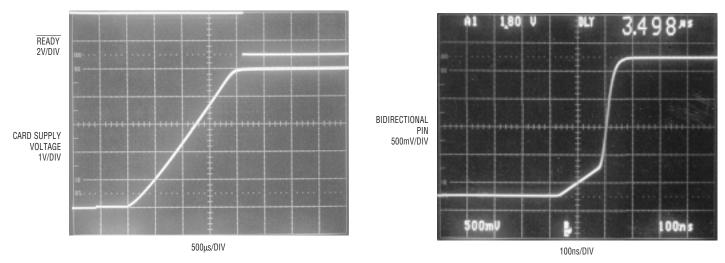

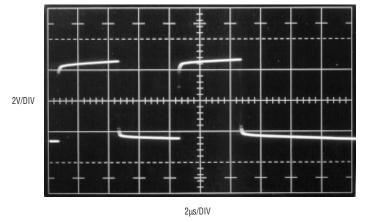

Figure 4. Dynamic pull-up current source

rent source to assist. Once the larger current source begins to enhance the edge rate of the node, the decision to enhance is reinforced, thereby effecting a dynamic form of hysteresis. After the node has reached the power supply rail, the comparator resets and only  $I_{START}$  is available again. Figure 5 shows the waveform of a bidirectional pin. The 10% to 90% rise time is on the order of 150ns.

#### Unidirectional Communication Channels

There are two unidirectional channels on the LTC1755 that provide the level-shifted clock and reset signals used by the smart card for synchronization. The clock channel is designed specifically for high speed and can faithfully transmit a 5MHz signal. Both of these channels are disabled and provide a valid low before the smart card supply voltage has reached its final value. Once the card supply voltage is valid, these channels will simply transmit the signals present

Figure 3. Smart card supply voltage and READY upon activation

Figure 5. Bidirectional pin with dynamic pull-up

at their respective inputs. To comply with smart card standards, the RST pin is always brought low before the CLK pin upon deactivation.

### Smart Card Detection Channel

The LTC1755 incorporates the only card detection solution that does not require additional de-bounce circuitry or software. This channel detects the presence of a smart card by forcing a small current and monitoring the voltage on a mechanical detection switch. Once a smart card is detected, the channel starts the debounce timer. The presence of a card is reported to the microcontroller only if the card has been present for a minimum of 40ms. Existing solutions provide either no debounce capability or minimal (only tens of microseconds) debounce time. These solutions require additional software or hardware to mask out the transients associated with the physical insertion of the smart card. Also, unlike other solutions, the switch-sense current is generated by the LTC1755 so no external components are required. Once a valid card indication occurs. the channel alerts the microcontroller by asserting the  $\overline{CARD}$  pin.

For maximum flexibility the smart card detection channel can be programmed to respond to either a normally open or normally closed switch. A built-in XOR gate is used as a controlled inverter to provide this function.

#### Fault Detection and Avoidance

Specifications relating to faults on the smart card pins are very stringent. For example, ISO7816-3 (section 1.4.8) specifies that the smart card socket must be capable of surviving a "metal plate" connection between any or all contacts without damage. To accommodate these fault conditions, the LTC1755 uses voltage sensing on the low impedance pins to detect if they are being forced to an inappropriate level. For example, the voltage on the smart card supply pin,  $V_{CC}$ , is compared with an internal reference to determine if a short circuit exists. If a fault persists for a prescribed period, the LTC1755 automatically deactivates the smart card and asserts the ALARM output. The small timeout period prevents false errors from plaguing the microcontroller. The clock and reset channels respond to faults in a similar way. The digital levels on the outputs of these channels (CLK and RST) are compared to those being presented at their inputs. If these signals differ for several microseconds, a fault is declared and the smart card is deactivated. Again, the ALARM output alerts the microcontroller that an electrical fault exists. In both cases, since the smart card becomes deactivated, there is no power available to deliver excessive current for a prolonged period.

The three bidirectional pins on the smart card side of the channel are protected against short circuits to the

smart card supply voltage by means of a constant-current pull-down output. Rather than a simple pull-down transistor to transmit a low to the smart card, these channels use a current source implementation. The 3.5mA current source provides enough current to meet the edge rate and  $V_{OL}$  requirements while limiting the current available during a fault. The available smart card standards specify that no more than 5mA flow during faults on these pins. Of course, short circuits to ground on these channels are indistinguishable from a normal signal and must be detected by the data-error checking routines.

### Conclusion

The LTC1755, designed specifically for smart card applications, provides all of the necessary level shifting and power circuitry to interface with a smart card socket. To further reduce board level complexity, it includes a smart card detection channel with built-in debounce circuitry. Since the LTC1755 provides all of the necessary smart card interface functions, only bypass capacitors and one charge pump capacitor are required for operation. Under most circumstances the operation of the LTC1755 is simple and provides a nearly transparent path to the smart card. However, when an electrical error condition occurs the LTC1755 responds quickly by powering down the smart card and alerting the microcontroller.  $\boldsymbol{\square}$

Articles, Design Ideas, Tips from the Lab...

# LT1306: Synchronous Boost DC/DC Converter Disconnects Output in Shutdown

by Bing Fong Ma

### Introduction

Step-up or boost DC/DC converters traditionally suffer from a lack of true shutdown capability. The output of a boost converter is connected to the input through the inductor and diode; when the device is powered down, the load is still connected to the input source, presenting a possible discharge path. Even some synchronous boost converters suffer from this limitation. The unique configuration of the LT1306's internal 2 ampere switch and rectifier overcomes this limitation. When the LT1306 is shut down, the output is disconnected from the input, eliminating the discharge path.

Additionally, the LT1306 can regulate the output when the input voltage exceeds the output voltage. This is useful for generating a 5V supply

from a 4-cell alkaline battery. When fresh, the battery voltage measures about 6.5V, but when depleted, the battery voltage is only 4V. A simple boost converter output will follow the input voltage only when the battery voltage exceeds 5V, while a step-down, or buck converter will lose regulation when the battery voltage falls below 5V. The LT1306 regulates the output to 5V in both situations.

Lastly, the LT1306 controls inrush current. A user installing a new battery need not worry about high inrush current as the battery initially charges the output capacitor. The LT1306 provides a clean solution to a difficult problem.

The LT1306 packs all these features in an SO-8 package. The constant frequency, current mode PWM device runs at 340kHz and features Burst Mode<sup>TM</sup> operation to maintain high efficiency at light loads. No-load quiescent current is 160 $\mu$ A, while the device consumes just 9 $\mu$ A in shutdown. The device can be externally synchronized to frequencies between 425kHz and 500kHz.

#### **Circuit Description**

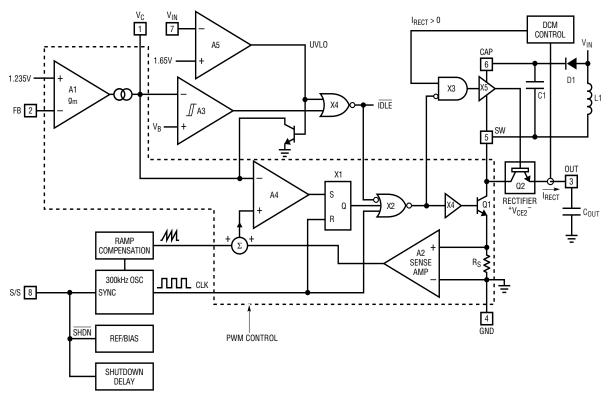

In the block diagram of Figure 1, the PWM control path is shown enclosed within the dashed line. The free-running frequency of the oscillator is trimmed to 340kHz. The main power switch, Q1, is turned on at the trailing edge of the clock pulse. Q1 is switched off when the switch current (sensed across resistor  $R_S$ ) exceeds a

Figure 1. LT1306 block diagram

Figure 2. DC transfer characteristics of the mode control comparator plotted with  $V_0$  as an independent variable;  $V_{IN}$  is considered fixed.

programmed level set by the error amplifier output,  $V_c$ , and the compensation ramp. This is current mode control. The switch current limit is reached when  $V_c$  clamps at 1.28V.

The error amplifier output determines the peak switch current required to regulate the output voltage.  $V_C$  is therefore a measure of the output power. At heavy loads, the peak and average inductor current are both high. The LT1306 operates in continuous-conduction mode (CCM) as  $V_C$  increases. As the load decreases, the average inductor current moves lower with an accompanying decrease in the peak inductor current returns to zero within each switching

cycle, the converter is said to operate in discontinuous-conduction mode (DCM). Further reduction in load moves  $V_C$  towards its lower operating range.

Hysteretic comparator A3 determines if  $V_{\rm C}$  is too low for the LT1306 to operate efficiently. As V<sub>C</sub> falls below the Burst Mode threshold, V<sub>B</sub>, comparator A3 turns off Q1. Any energy stored in the inductor is delivered to the output through the synchronous rectifier. The LT1306 draws only 160µA from the input in this idle state. As the output voltage droops, V<sub>C</sub> rises above the upper trip point of A3. The LT1306 again wakes up and delivers power to the load. If the load remains light, the output voltage will rise and V<sub>C</sub> will fall, causing the converter to idle again. Power delivery therefore occurs in bursts. The burst frequency is dependent on the input voltage, the inductance, the load current and the output filter capacitance. The output voltage ripple in Burst Mode operation is higher than those in CCM and DCM operation. Burst operation increases light load efficiency because the higher peak switch current characteristic of Burst Mode operation allows the converter to deliver more energy in each switching cycle than possible with cycle-skipping DCM operation. Thus, fewer switching cycles are required to

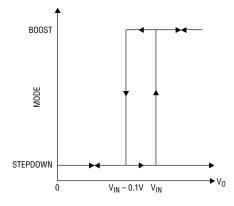

BOOST

Figure 3. DC transfer characteristics of the mode control comparator plotted with  $V_{\rm IN}$  as an independent variable;  $V_0$  is considered fixed.

maintain a given output. Chip supply current also becomes a small fraction of the total input current.

The synchronous rectifier is represented as an NPN transistor, Q2, in the block diagram. A rectifier driver, X5, supplies variable base drive to Q2 and controls the voltage across the rectifier. The supply voltage for driver X5 is generated locally with the bootstrap circuit comprising D1 and C1. When switch Q1 is on, the bootstrap capacitor C1 is charged from the input to the voltage  $V_{IN} - V_{D1(ON)}$ – V<sub>CESAT1</sub>. The charging current flows from the input through D1, C1 and Q1 to ground. After Q1 is switched off, the node SW goes above Vo by the collector-emitter saturation voltage of Q2. D1 becomes reverse biased and the CAP pin voltage is approximately  $V_{O} + V_{IN} - V_{D1(ON)}$ . The capacitor C1 supplies the Q2 base drive. The charge consumed is replenished during Q1's on-interval.

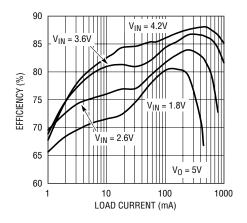

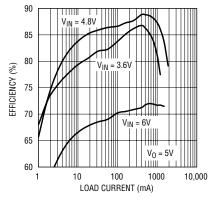

Figure 5. Efficiency of Figure 4's circuit

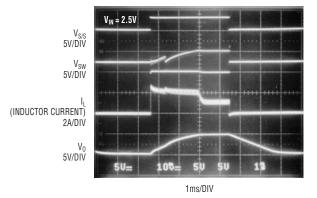

Figure 6. Start-up to shutdown transient response: note that the input start-up current is well controlled and that the output falls to zero in shutdown ( $I_L$  is also the input current, as the inductor is at the input).

Figure 7. Transient response of the converter in Figure 4 with a 50mA to 800mA load step

In boost operation, X5 drives the rectifier Q2 into saturation with constant forced  $\beta$ . X5 ceases supplying base current to Q2 when the inductor current falls to zero. If V<sub>IN</sub> is greater than V<sub>0</sub>, Q2 will not be driven into saturation. Instead, the collector-emitter voltage of Q2 increases so that the inductor voltage reverses polarity as Q1 switches. Since the inductor voltage is always bipolar, volt-second balance can be maintained regardless of the input voltage. The LT1306 can therefore operate as a step-down converter.

During start-up, the inductor voltage of a boost converter with a diode rectifier remains positive until the output voltage rises to one diode voltage below the input voltage. A high input-transient current spike invariably results. In the LT1306, the inductor voltage reverses polarity every switching cycle. This, with cycleby-cycle current limit, eliminates the inrush current spike.

The rectifier voltage drop depends on both the input and output voltages. Efficiency in step-down operation is approximately that of a linear regulator. For sustained step-down operation, the maximum output current will be limited by the package thermal characteristics.

A hysteretic comparator inside driver X5, which detects the crossover between the input and the output voltages, signals the driver to provide appropriate base current to the rectifier. DC transfer characteristics of this comparator are illustrated in Figures 2 and 3.

When shutdown is activated  $(V_{S/S} < 0.45V)$ , all circuits except synchronous rectifier Q2 and its driver X5 are shut off. If  $V_0$  is above  $V_{IN}$ , Q2 will be driven into saturation. Stored inductive energy flows to the output through the saturated rectifier. As V<sub>0</sub> falls below  $V_{IN}$ , X5 reduces the base drive to Q2, which increases the rectifier voltage. The inductor voltage is now negative. The inductor current continues to fall to zero. The driver X5 then turns off and the rectifier Q2 becomes an open circuit. The LT1306 consumes 9µA from the input in shutdown.

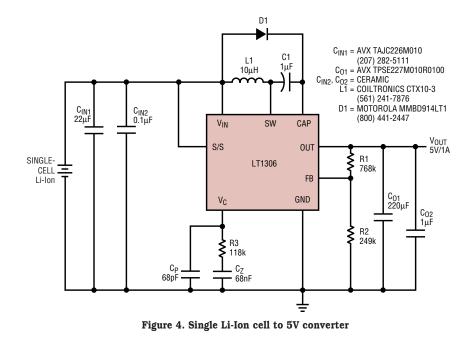

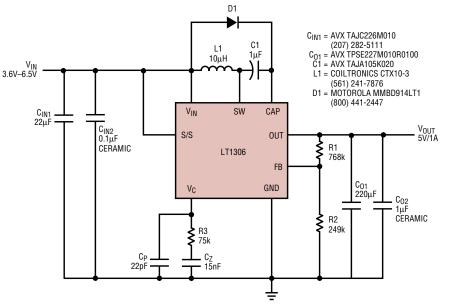

# Single Li-ion Cell to 5V Converter

The LT1306 is ideally suited for generating 5V output from a single Li-ion cell. The circuit shown in Figure 4 is capable of supplying 1A of DC output current. The value of resistor R3 is chosen so that the overall feedback loop gain crosses 0dB before the righthalf plane (RHP) zero. The capacitor  $C_Z$  and the resistor R3 form a low frequency zero in the loop response. C<sub>P</sub> ensures adequate gain margin beyond the RHP zero. The value of R3 is inversely proportional to the error amplifier g<sub>m</sub>. Low g<sub>m</sub> and high R3 improve converter load-transient response.

Figure 8. 2-cell to 3.3V output converter

# DESIGN FEATURES

In applications where high pulse current (>1A) is drawn from the output, a large electrolytic capacitor (>1000 $\mu$ F) is typically used to hold up the output voltage during the load pulse. Higher output filter capacitance lowers the dominant pole frequency of the gain response so that higher loop gain (that is, a higher value of R3) is required in the compensation network to give the same loop crossover frequency.

Efficiency curves of the converter are shown in Figure 5. Figure 6 shows a start-up-to-shutdown transient. The converter operates in step-down mode until the output voltage exceeds the input voltage (2.5V). The mode switching is evidenced by the sudden decrease in the SW node voltage. The input start-up current is well controlled at the switch current limit of 2.2A. The converter then produces a

Figure 10. 4-cell to 5V output converter

steady state output of 5V. Pulling the S/S pin low for at least  $33\mu s$  disconnects the load. Figure 7 shows the load transient response of the converter.

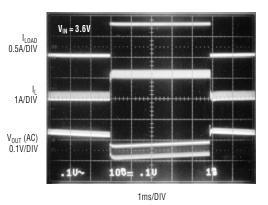

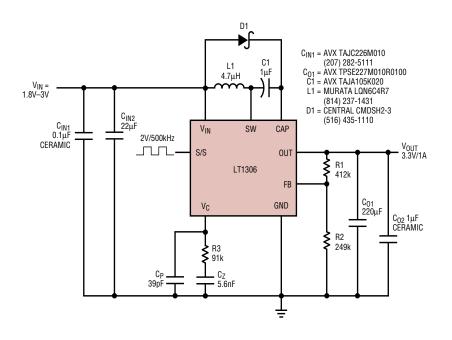

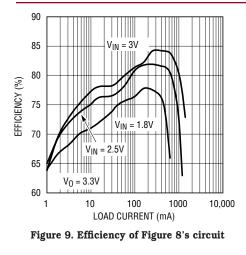

#### 2-Cell to 3.3V Converter

Figure 8 depicts an externally synchronized 2-cell to 3.3V converter running at 500kHz. A  $4.7\mu$ H inductor is used to take advantage of the higher switching frequency. Driving the S/S pin with a clock generator, which has a 2V amplitude and less than 20ns of rise time, synchronizes the LT1306. Synchronization is positive-edge triggered. Diode D1 is a CMDSH2-3 Schottky diode. Compared to a junc-

tion diode, a Schottky diode increases the bootstrap voltage and affords higher operating headroom for rectifier Q2. In situations where reduced headroom is acceptable (such as over the commercial temperature range), a 1N4148 or 1N914 diode can also be used. The converter efficiency is plotted in Figure 9.

#### 4-Cell to 5V Converter

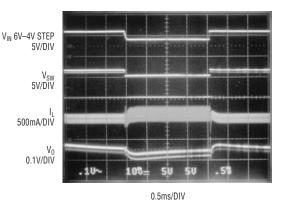

Due to its ability to establish voltsecond balance with  $V_{IN}$  greater than  $V_0$ , the LT1306 is also suited for applications where the battery voltage straddles the desired output voltage. One such example is the 4-cell to 5V converter shown in Figure 10.

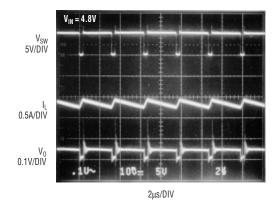

Figure 11. Continuous conduction mode switching waveforms in boost mode;  $V_{IN}$  = 4.8V,  $V_0$  = 5V

# **∠** *T* **DESIGN FEATURES**

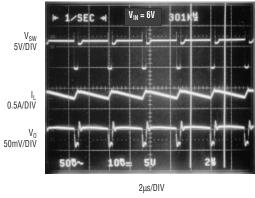

Figure 12. Continuous conduction mode switching waveforms in step-down mode;  $V_{IN} = 6V$ ,  $V_{O}= 5V$

The continuous-conduction mode switch-node voltage and the inductor current for step-down operations (Figure 12) are contrasted with those of boost operation in Figure 11. Note that in step-down mode, when the rectifier is conducting, the switch voltage exceeds  $V_{\rm IN}$ . Input step (from 4V to 6V) transient response is illustrated in Figure 13. The converter efficiency is plotted in Figure 14.

#### Smart Battery, continued from page 10

thermistor every 100 $\mu s.$  When AC is not present,  $R_{NR}$  and  $R_{UR}$  thermistor testing occurs only when a battery is first inserted or removed or during a transmission requesting Safety Signal status.

The underrange detection scheme is a very important feature of the LTC1759. As can be seen from Figure 6, the  $R_{UR}/R_{THERM}$  trip point of 0.333 •  $V_{DD}$  (1V) is well above the 0.047 •  $V_{DD}$  (140mV) threshold of a system using a 10k pull-up for all ranges. A system using a 10k pull-up would not be able to resolve the important underrange-to-hot transition point with a modest 100mV of ground offset between the battery and thermistordetection circuitry. Such offsets are anticipated when charging at normal current levels.

#### Conclusion

The LTC1759 complies with the Smart Battery Charger standard published by the Smart Battery System organi-

#### Conclusion

The LT1306 is a complete synchronous boost DC/DC converter offering a set of features that few competing devices are able to match. The unique rectifier design results in a boost/ step-down converter that disconnects the load in shutdown and controls input current during startup.  $\measuredangle$

Authors can be contacted

at (408) 432-1900

Figure 13. Transient response of the circuit in Figure 10 with step input (4V-6V)

Figure 14. Efficiency of Figure 10's circuit

Figure 6. Testing an underrange thermistor

zation, in which Linear Technology is a promoter and voting member. The charger controller also complies with Intel's ACPI standard by being able to respond to system commands even when there is not AC wall adapter power. The charger offers the widest current and voltage range of operation compared to competitive parts. Feature for feature, it also offers the highest integration possible today with a Smart Battery Charger. The LTC1759 achieves significant cost savings, performance and safety advantages over other Smart Battery Chargers currently available.

# Versatile Dual Hot Swap Controller/ **Power Sequencer Allows** Live Backplane Insertion

by Bill Poucher

### Introduction

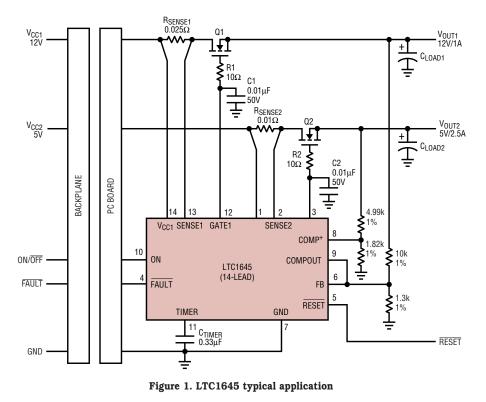

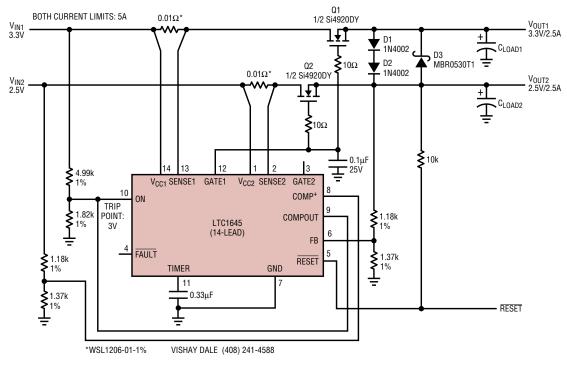

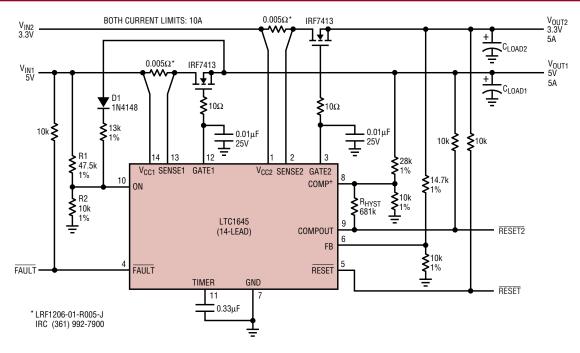

When a circuit board is inserted into a live backplane, the supply bypass capacitors on the board can draw large transient currents from the backplane power bus as they charge. These transient currents can destroy capacitors, connector pins and board traces and can disrupt the system supply, causing other boards in the system to reset. The new dual-channel LTC1645 Hot Swap controller is designed to ramp a circuit board's supply voltages in a controlled manner, preventing glitches on the system supply and damage to the board.

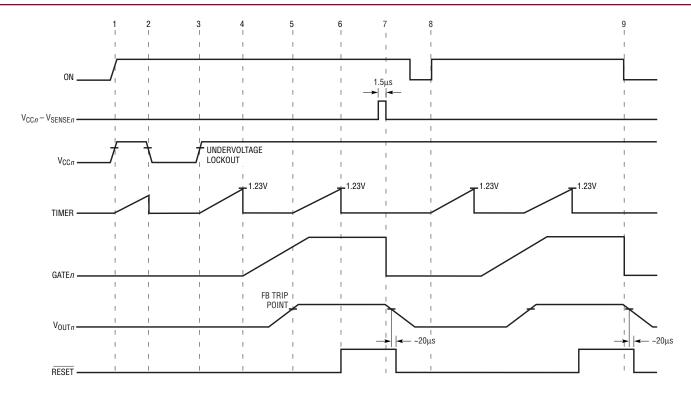

The LTC1645's two channels can be set to ramp up and down separately, or they can be programmed to rise and fall simultaneously, ensuring power supply tracking at the two outputs. Using external N-channel pass transistors, the supply voltages can be ramped at a programmable

rate. Two high-side switch drivers control the external N-channel FET gates for supply voltages ranging from 1.2V to 12V. Programmable electronic circuit breakers protect against shorts at either output. The LTC1645 is available in the 14-pin and 8-pin SO packages. The 14-pin version additionally provides a system reset signal and a second "spare" comparator to indicate when board supply voltages drop below user-programmable levels. It also has a fault signal to indicate an overcurrent condition and a timer pin to create a delay before ramping up the supply voltages and deasserting the system reset signal.

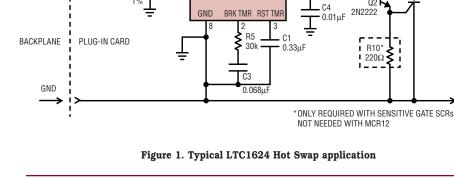

#### **Typical Hot Swap Application**

Figure 1 shows a typical Hot Swap application using the LTC1645. Q1 and Q2 control the board's power supplies, R<sub>SENSE1</sub> and R<sub>SENSE2</sub> provide

current fault detection and R1 and R2 prevent high frequency oscillation. By ramping the gates of the pass transistors up and down at a controlled rate, the transient surge current (I =  $C \cdot dv/dt$ ) drawn from the main backplane supply is limited to a safe value when the board makes connection.

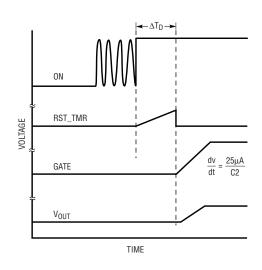

The timing for the board is shown in Figure 2. When power is first applied to the chip, the gates of the FETs (GATE1 and GATE2 pins) are pulled low. Once the ON pin rises at time point 1, the LTC1645 must complete a timing cycle before the GATE pin voltages are allowed to rise. This allows the connector pins to finish bouncing and make a solid connection. C<sub>TIMER</sub> charges to 1.23V with a 2µA current source, setting the delay timing cycle equal to t =  $(1.23V \cdot C_{\text{TIMER}})/2\mu A$ . In this example, the undervoltage lock-

Figure 2. Typical insertion and electronic-circuit-breaker timing

out circuit discharges the TIMER pin and prevents both channels from turning on when  $V_{CC1} < 2.23V$  or  $V_{CC2}$ < 1.12V (time point 2). At time point 4, the timing cycle is completed and the GATE pins are pulled up by an internal 10µA current source; the voltage at GATE1 begins to rise with a slope of 10µA/C1 and the voltage at GATE2 begins to rise with a slope of 10µA/ C2. The supply voltages follow their respective gate voltages minus the

Figure 3. On-pin operation

external FET threshold voltage; the ramp time for each supply is  $(V_{CCn} \bullet Cn)/10\mu A$ .

#### Voltage Monitor and Spare Comparator

The 14-pin version of the LTC1645 provides two precision comparators for monitoring input or output voltage levels. Both comparators have a 1.238V reference as the negative input and have open-drain outputs that

require an external pull-up to generate a logic high. The spare comparator monitors COMP+ and releases COMP-OUT immediately whenever COMP+ is above 1.238V. The FB comparator releases RESET one timing cycle after the FB pin rises above 1.238V (Figure 2, time points 5 and 6) and includes a glitch filter to prevent system resets during short negative transients on the FB pin. The filter time is 20µs for large transients (greater than 150mV) and up to 100us for smaller 10uA transients.

In Figure 1, the COMPOUT pin has been tied to the FB pin so that RESET will not release until both output supplies remain above their programmable voltages for one timing cycle.

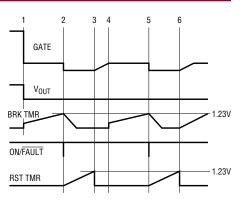

#### **Electronic Circuit Breaker**

The LTC1645 features an electronic circuit breaker function that protects against short circuits or excessive output current. Load current for each supply is monitored by a sense resistor between the supply input and sense pin of the chip. The circuit breaker trips whenever the voltage across the sense resistor exceeds 50mV for more than 1.5µs. When the circuit breaker of either channel trips, both GATE pins are immediately pulled to ground and the external FETs are quickly turned off (Figure 2, time point 7). When the ON pin is cycled off and on (time point 8), the circuit breaker resets and another timing cycle starts. If the circuit breaker feature is not required. short the SENSE pins to their respective V<sub>CC</sub> pins.

> Authors can be contacted at (408) 432-1900

# DESIGN FEATURES 🖊

Figure 4. Ramping 3.3V and 2.5V up and down together

#### The ON Pin

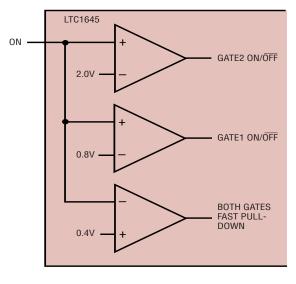

The ON pin has multiple thresholds to control the ramping up and down of the GATEn pins. Figure 3 is a block diagram showing operation of the ON pin. If the ON pin voltage is below 0.4V, GATE1 and GATE2 are immediately pulled to ground. While the voltage is between 0.4V and 0.8V, GATE1 and GATE2 are each pulled to ground with a 40µA current. Between 0.8V and 2V, the GATE1 10µA pullup is turned on after one timing cycle, but GATE2 continues to be pulled to ground with a 40µA current. When the voltage exceeds 2V, both the GATE1 and GATE2 10µA pull-ups are turned on one timing cycle after the voltage exceeds 0.8V.

# Power Supply Tracking and Sequencing

Some applications require that the difference between two power supply voltages not exceed a certain value. This requirement applies during power-up and power-down, as well as during steady state operation; often this is done to prevent latch-up in a dual-supply ASIC. Other systems require one supply to come up after another, for example, when a system clock needs to start before a block of

logic. Typical dual supplies or backplane connections may come up at arbitrary rates depending on load current, capacitor size, soft-start rates and so on. Traditional solutions can be cumbersome or require complex circuitry to meet the necessary requirements.

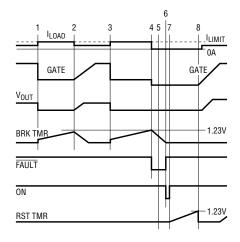

The LTC1645 provides simple solutions to power supply tracking and sequencing needs. The LTC1645 can guarantee supply tracking by ramping the supplies up and down together and allows nearly any combination of supply ramping to satisfy various sequencing specifications. Figure 4 shows an application ramping  $V_{OUT1}$  and  $V_{OUT2}$  up and down together. The ON pin must reach 0.8V to turn on GATE1, which ramps up  $V_{OUT1}$  and  $V_{OUT2}$ . The spare comparator pulls the ON pin low until  $V_{CC2}$  is above 2.3V, and the ON pin cannot reach 0.8V before  $V_{CC1}$  is above 3V.

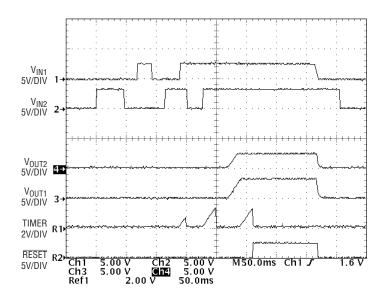

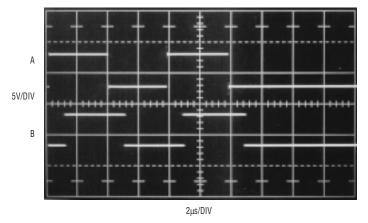

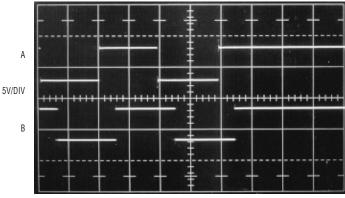

Figure 5. Input, output and control signals of Figure 4's circuit

Thus, both input supplies must be within regulation before a timing cycle can start. At the end of the timing cycle, the output voltages ramp up together. If either input supply falls out of regulation or if an overcurrent condition is detected, the gates of Q1 and Q2 are pulled low together.

Figure 5 shows an oscilloscope photo of of Figure 4's circuit in action. On power-up,  $V_{OUT1}$  and  $V_{OUT2}$  ramp up together. On power-down, the LTC1645 turns off Q1 and Q2 simultaneously. Charge remains stored on  $C_{LOAD1}$  and  $C_{LOAD2}$  and the output voltages will vary depending on the loads. D1 and D2 turn on at  $\approx 1V$  ( $\approx 0.5V$  each), ensuring that  $V_{OUT1}$  never exceeds  $V_{OUT2}$  by more than 1.2V, while D3 guarantees that  $V_{OUT2}$  is never greater than  $V_{OUT1}$  by more than 0.4V. Barring an overvoltage

Figure 6. Ramping up 5V followed by 3.3V