# 100MHz Current Feedback Amplifier

## **FEATURES**

- 100MHz Bandwidth at A<sub>V</sub> = 1

- 1000V/µs Slew Rate

- Wide Supply Range: ±5V to ±15V

- 1mV Input Offset Voltage

- 1µA Input Bias Current

- 5MΩ Input Resistance

- 75ns Settling Time to 0.1%

- 50mA Output Current

- 6mA Quiescent Current

# **APPLICATIONS**

- Video Amplifiers

- Buffers

- IF and RF Amplification

- Cable Drivers

- 8-, 10-, 12-Bit Data Acquisition Systems

## DESCRIPTION

The LT1223 is a 100MHz current feedback amplifier with very good DC characteristics. The LT1223's high slew rate,  $1000V/\mu s$ , wide supply range,  $\pm 15V$ , and large output drive,  $\pm 50 mA$ , make it ideal for driving analog signals over double-terminated cables. The current feedback amplifier has high gain bandwidth at high gains, unlike conventional op amps.

The LT1223 comes in the industry standard pinout and can upgrade the performance of many older products.

The LT1223 is manufactured on Linear Technology's proprietary complementary bipolar process.

# TYPICAL APPLICATION

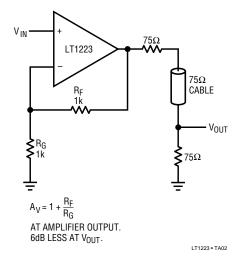

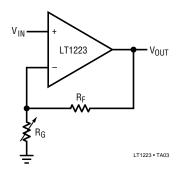

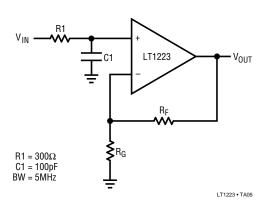

#### Video Cable Driver

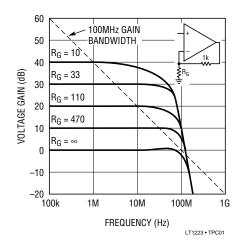

#### **Voltage Gain vs Frequency**

# **ABSOLUTE MAXIMUM RATINGS**

# PACKAGE/ORDER INFORMATION

| NULL 1 8 SHUTDOWN                                                                                                                                                                                                     | ORDER PART<br>NUMBER                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| -IN 2 7 V+ HIN 3 6 OUT V- 4 5 NULL  J8 PACKAGE N8 PACKAGE 8-LEAD CERAMIC DIP 8-LEAD PLASTIC DIP                                                                                                                       | LT1223MJ8<br>LT1223CJ8<br>LT1223CN8<br>LT1223CS8 |

| S8 PACKAGE 8-LEAD PLASTIC SOIC $T_{J MAX} = 175^{\circ}C, \theta_{JA} = 100^{\circ}C/W(J8)$ $T_{J MAX} = 150^{\circ}C, \theta_{JA} = 100^{\circ}C/W(N8)$ $T_{J MAX} = 150^{\circ}C, \theta_{JA} = 150^{\circ}C/W(S8)$ | S8 PART MARKING<br>1223                          |

# **ELECTRICAL CHARACTERISTICS** $v_{\text{S}} = \pm\,15\text{V},\, T_{\text{A}} = 25^{\circ}\text{C},\, \text{unless otherwise noted}.$

| SYMBOL              | PARAMETER                                              | CONDITIONS                                                          | MIN | LT1223M/C<br>TYP | MAX | UNITS  |

|---------------------|--------------------------------------------------------|---------------------------------------------------------------------|-----|------------------|-----|--------|

| $V_{0S}$            | Input Offset Voltage                                   | V <sub>CM</sub> = 0V                                                |     | ±1               | ±3  | mV     |

| I <sub>IN</sub> +   | Noninverting Input Current                             | V <sub>CM</sub> = 0V                                                |     | ±1               | ±3  | μА     |

| I <sub>IN</sub> -   | Inverting Input Current                                | V <sub>CM</sub> = 0V                                                |     | ±1               | ±3  | μΑ     |

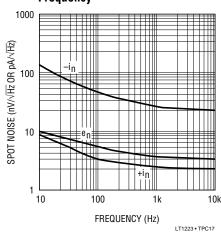

| e <sub>n</sub>      | Input Noise Voltage Density                            | $f = 1kHz$ , $R_F = 1k$ , $R_G = 10\Omega$                          |     | 3.3              |     | nV/√Hz |

| i <sub>n</sub>      | Input Noise Current Density                            | $f = 1 \text{kHz}, R_F = 1 \text{k}, R_G = 10 \Omega$               |     | 2.2              |     | pA/√Hz |

| R <sub>IN</sub>     | Input Resistance                                       | V <sub>IN</sub> = ±10V                                              | 1   | 10               |     | MΩ     |

| C <sub>IN</sub>     | Input Capacitance                                      |                                                                     |     | 1.5              |     | pF     |

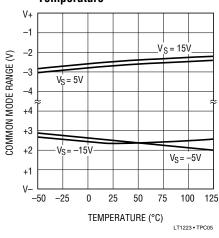

|                     | Input Voltage Range                                    |                                                                     | ±10 | ±12              |     | V      |

| CMRR                | Common-Mode Rejection Ratio                            | V <sub>CM</sub> = ±10V                                              | 56  | 63               |     | dB     |

|                     | Inverting Input Current Common-Mode Rejection          | V <sub>CM</sub> = ±10V                                              |     | 30               | 100 | nA/V   |

| PSRR                | Power Supply Rejection Ratio                           | $V_S = \pm 4.5 \text{V to } \pm 18 \text{V}$                        | 68  | 80               |     | dB     |

|                     | Noninverting Input Current Power Supply Rejection      | $V_S = \pm 4.5 \text{V to } \pm 18 \text{V}$                        |     | 12               | 100 | nA/V   |

|                     | Inverting Input Current Power Supply Rejection         | $V_S = \pm 4.5 \text{V to } \pm 18 \text{V}$                        |     | 60               | 500 | nA/V   |

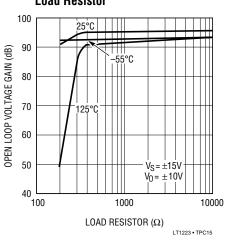

| A <sub>V</sub>      | Large Signal Voltage Gain                              | $R_{LOAD} = 400\Omega$ , $V_{OUT} = \pm 10V$                        | 70  | 89               |     | dB     |

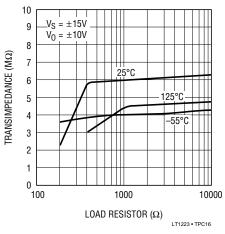

| $\overline{R_{OL}}$ | Transresistance, ΔV <sub>OUT</sub> /ΔI <sub>IN</sub> - | $R_{LOAD} = 400\Omega$ , $V_{OUT} = \pm 10V$                        | 1.5 | 5                |     | MΩ     |

| V <sub>OUT</sub>    | Maximum Output Voltage Swing                           | $R_{LOAD} = 200\Omega$                                              | ±10 | ±12              |     | V      |

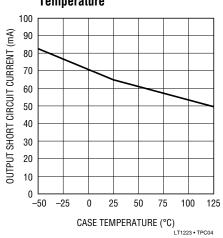

| I <sub>OUT</sub>    | Maximum Output Current                                 | $R_{LOAD} = 200\Omega$                                              | 50  | 60               |     | mA     |

| SR                  | Slew Rate                                              | R <sub>F</sub> = 1.5k, R <sub>G</sub> = 1.5k, (Note 2)              | 800 | 1300             |     | V/µs   |

| BW                  | Bandwidth                                              | R <sub>F</sub> = 1k, R <sub>G</sub> = 1k, V <sub>OUT</sub> = 100mV  |     | 100              |     | MHz    |

| t <sub>r</sub>      | Rise Time                                              | R <sub>F</sub> = 1.5k, R <sub>G</sub> = 1.5k, V <sub>OUT</sub> = 1V |     | 6.0              |     | ns     |

| t <sub>PD</sub>     | Propagation Delay                                      | R <sub>F</sub> = 1.5k, R <sub>G</sub> = 1.5k, V <sub>OUT</sub> = 1V |     | 6.0              |     | ns     |

|                     | Overshoot                                              | R <sub>F</sub> = 1.5k, R <sub>G</sub> = 1.5k, V <sub>OUT</sub> = 1V |     | 5                |     | %      |

| $\overline{t_s}$    | Settling Time, 0.1%                                    | R <sub>F</sub> = 1k, R <sub>G</sub> = 1k, V <sub>OUT</sub> = 10V    |     | 75               |     | ns     |

|                     | Differential Gain                                      | $R_F = 1k, R_G = 1k, R_L = 150\Omega$                               |     | 0.02             |     | %      |

|                     | Differential Phase                                     | $R_F = 1k, R_G = 1k, R_L = 150\Omega$                               |     | 0.12             |     | Deg    |

| R <sub>OUT</sub>    | Open-Loop Output Resistance                            | V <sub>OUT</sub> = 0, I <sub>OUT</sub> = 0                          |     | 35               |     | Ω      |

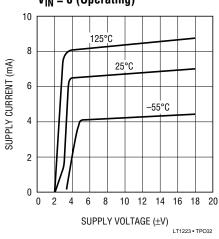

| Is                  | Supply Current                                         | V <sub>IN</sub> = 0V                                                |     | 6                | 10  | mA     |

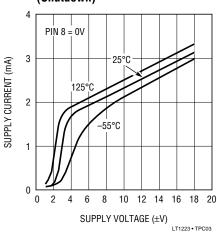

|                     | Supply Current, Shutdown                               | Pin 8 Current = 200μA                                               |     | 2                | 4   | mA     |

# **ELECTRICAL CHARACTERISTICS** $V_S=\pm\,15V,\ V_{CM}=\,0V,\ 0^\circ C \le T_A \le 70^\circ C,\ unless\ otherwise\ noted.$

|                   |                                                        |                                              |     | LT1223C |     |       |      |

|-------------------|--------------------------------------------------------|----------------------------------------------|-----|---------|-----|-------|------|

| SYMBOL            | PARAMETER                                              | CONDITIONS                                   | MIN | TYP     | MAX | UNITS |      |

| V <sub>OS</sub>   | Input Offset Voltage                                   | V <sub>CM</sub> = 0V                         | •   | ±1      | ±3  | mV    |      |

| I <sub>IN</sub> + | Noninverting Input Current                             | V <sub>CM</sub> = 0V                         | •   | ±1      | ±3  | μΑ    |      |

| I <sub>IN</sub> — | Inverting Input Current                                | V <sub>CM</sub> = 0V                         | •   | ±1      | ±3  | μΑ    |      |

| R <sub>IN</sub>   | Input Resistance                                       | V <sub>IN</sub> = ±10V                       | •   | 1       | 10  |       | MΩ   |

| -                 | Input Voltage Range                                    |                                              | •   | ±10     | ±12 |       | V    |

| CMRR              | Common-Mode Rejection Ratio                            | V <sub>CM</sub> = ±10V                       | •   | 56      | 63  |       | dB   |

|                   | Inverting Input Current Common-Mode Rejection          | V <sub>CM</sub> = ±10V                       | •   |         | 30  | 100   | nA/V |

| PSRR              | Power Supply Rejection Ratio                           | $V_S = \pm 4.5 V \text{ to } \pm 18 V$       | •   | 68      | 80  |       | dB   |

|                   | Noninverting Input Current Power Supply Rejection      | $V_S = \pm 4.5 \text{V to } \pm 18 \text{V}$ | •   |         | 12  | 100   | nA/V |

| -                 | Inverting Input Current Power Supply Rejection         | $V_S = \pm 4.5 \text{V to } \pm 18 \text{V}$ | •   |         | 60  | 500   | nA/V |

| A <sub>V</sub>    | Large-Signal Voltage Gain                              | $R_{LOAD} = 400\Omega$ , $V_{OUT} = \pm 10V$ | •   | 70      | 89  |       | dB   |

| R <sub>OL</sub>   | Transresistance, ΔV <sub>OUT</sub> /ΔI <sub>IN</sub> – | $R_{LOAD} = 400\Omega$ , $V_{OUT} = \pm 10V$ | •   | 1.5     | 5   |       | MΩ   |

| V <sub>OUT</sub>  | Maximum Output Voltage Swing                           | $R_{LOAD} = 200\Omega$                       | •   | ±10     | ±12 |       | V    |

| I <sub>OUT</sub>  | Maximum Output Current                                 | $R_{LOAD} = 200\Omega$                       | •   | 50      | 60  |       | mA   |

| Is                | Supply Current                                         | V <sub>IN</sub> = 0V                         | •   |         | 6   | 10    | mA   |

|                   | Supply Current, Shutdown                               | Pin 8 Current = 200μA                        | •   |         | 2   | 4     | mA   |

# **ELECTRICAL CHARACTERISTICS** $v_S=\pm\,15V,\ v_{CM}=0V, -55^\circ C \le T_A \le 125^\circ C,\ unless\ otherwise\ noted.$

| SYMBOL              | PARAMETER                                         | CONDITIONS                                   |   | MIN | LT1223M<br>TYP | MAX | UNITS |

|---------------------|---------------------------------------------------|----------------------------------------------|---|-----|----------------|-----|-------|

| $\overline{V_{0S}}$ | Input Offset Voltage                              | V <sub>CM</sub> = 0V                         | • |     | ±1             | ±5  | mV    |

| I <sub>IN</sub> +   | Noninverting Input Current                        | V <sub>CM</sub> = 0V                         | • |     | ±1             | ±5  | μА    |

| I <sub>IN</sub> —   | Inverting Input Current                           | V <sub>CM</sub> = 0V                         | • |     | ±1             | ±10 | μА    |

| R <sub>IN</sub>     | Input Resistance                                  | V <sub>IN</sub> = ±10V                       | • | 1   | 10             |     | MΩ    |

|                     | Input Voltage Range                               |                                              | • | ±10 | ±12            |     | V     |

| CMRR                | Common-Mode Rejection Ratio                       | V <sub>CM</sub> = ±10V                       | • | 56  | 63             |     | dB    |

|                     | Inverting Input Current Common-Mode Rejection     | $V_{CM} = \pm 10V$                           | • |     | 30             | 100 | nA/V  |

| PSRR                | Power Supply Rejection Ratio                      | $V_S = \pm 4.5 \text{V to } \pm 15 \text{V}$ | • | 68  | 80             |     | dB    |

|                     | Noninverting Input Current Power Supply Rejection | $V_S = \pm 4.5 \text{V to } \pm 15 \text{V}$ | • |     | 12             | 200 | nA/V  |

|                     | Inverting Input Current Power Supply Rejection    | $V_S = \pm 4.5 \text{V to } \pm 15 \text{V}$ | • |     | 60             | 500 | nA/V  |

| A <sub>V</sub>      | Large-Signal Voltage Gain                         | $R_{LOAD} = 400\Omega$ , $V_{OUT} = \pm 10V$ | • | 70  | 89             |     | dB    |

| $R_{0L}$            | Transresistance, $\Delta V_{OUT}/\Delta I_{IN}$   | $R_{LOAD} = 400\Omega$ , $V_{OUT} = \pm 10V$ | • | 1.5 | 5              |     | MΩ    |

| V <sub>OUT</sub>    | Maximum Output Voltage Swing                      | $R_{LOAD} = 200\Omega$                       | • | ±7  | ±12            |     | V     |

| I <sub>OUT</sub>    | Maximum Output Current                            | $R_{LOAD} = 200\Omega$                       | • | 35  | 60             |     | mA    |

| $\overline{I_S}$    | Supply Current                                    | V <sub>IN</sub> = 0V                         | • |     | 6              | 10  | mA    |

|                     | Supply Current, Shutdown                          | Pin 8 Current = 200μA                        | • |     | 2              | 4   | mA    |

The ullet denotes the specifications which apply over the full operating temperature range.

Note 1: A heat sink may be required.

**Note 2:** Noninverting operation,  $V_{OUT} = \pm 10V$ , measured at  $\pm 5V$ .

# TYPICAL PERFORMANCE CHARACTERISTICS

# Supply Current vs Supply Voltage (Shutdown)

Output Short Circuit-Current vs Temperature

### Input Common-Mode Limit vs Temperature

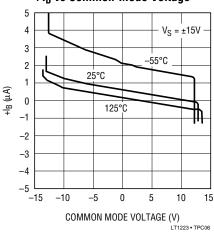

+IB vs Common-Mode Voltage

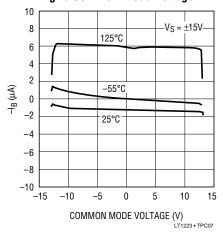

-I<sub>B</sub> vs Common-Mode Voltage

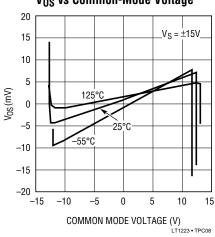

V<sub>OS</sub> vs Common-Mode Voltage

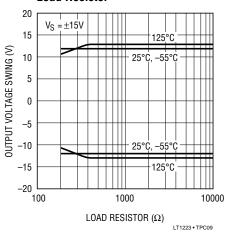

Output Voltage Swing vs Load Resistor

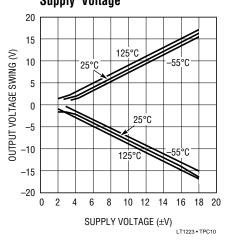

Output Voltage Swing vs Supply Voltage

# TYPICAL PERFORMANCE CHARACTERISTICS

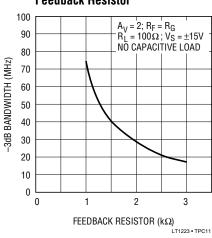

#### -3dB Bandwidth vs Feedback Resistor

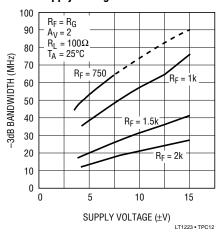

### -3dB Bandwidth vs Supply Voltage

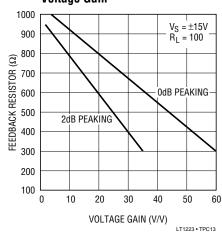

### Minimum Feedback Resistor vs Voltage Gain

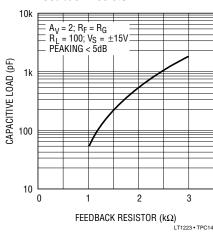

#### Maximum Capacitive Load vs Feedback Resistor

#### Open-Loop Voltage Gain vs Load Resistor

## Transimpedance vs Load Resistor

### Spot Noise Voltage and Current vs Frequency

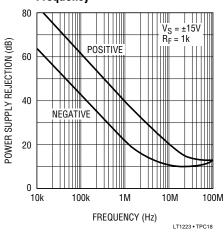

# Power Supply Rejection vs Frequency

## **Output Impedance vs Frequency**

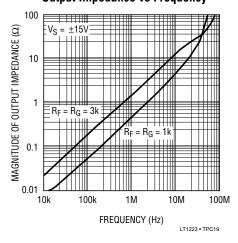

# TYPICAL PERFORMANCE CHARACTERISTICS

SETTLING TIME (µs)

LT1223 • TPC24

# APPLICATIONS INFORMATION

80

LT1223 • TPC23

100

#### **Current Feedback Basics**

20

40

SETTLING TIME (ns)

The small-signal bandwidth of the LT1223, like all current feedback amplifiers, isn't a straight inverse function of the closed-loop gain. This is because the feedback resistors determine the amount of current driving the amplifier's internal compensation capacitor. In fact, the amplifier's feedback resistor ( $R_{\text{F}}$ ) from output to inverting input works with internal junction capacitances of the LT1223 to set the closed-loop bandwidth.

Even though the gain set resistor ( $R_G$ ) from inverting input to ground works with  $R_F$  to set the voltage gain just like it

does in a voltage feedback op amp, the closed-loop bandwidth does not change. This is because the equivalent gain bandwidth product of the current feedback amplifier is set by the Thevenin equivalent resistance at the inverting input and the internal compensation capacitor. By keeping  $R_{\text{F}}$  constant and changing the gain with  $R_{\text{G}}$ , the Thevenin resistance changes by the same amount as the change in gain. As a result, the net closed-loop bandwidth of the LT1223 remains the same for various closed-loop gains.

0

20

40

60

SETTLING TIME (ns)

80

LT1223 • TPC25

100

The curve on the first page shows the LT1223 voltage gain versus frequency while driving  $100\Omega$ , for five gain settings from 1 to 100. The feedback resistor is a constant 1k and the gain resistor is varied from infinity to  $10\Omega$ . Shown for comparison is a plot of the fixed 100 MHz gain bandwidth limitation that a voltage feedback amplifier would have. It is obvious that for gains greater than one, the LT1223 provides 3 to 20 times more bandwidth. It is also evident that second order effects reduce the bandwidth somewhat at the higher gain settings.

#### **Feedback Resistor Selection**

Because the feedback resistor determines the compensation of the LT1223, bandwidth and transient response can be optimized for almost every application. To increase the bandwidth when using higher gains, the feedback resistor (and gain resistor) can be reduced from the nominal 1k value. The Minimum Feedback Resistor versus Voltage Gain curve shows the values to use for  $\pm 15$ V supplies. Larger feedback resistors can also be used to slow down the LT1223 as shown in the -3dB Bandwidth versus Feedback Resistor curve.

## **Capacitive Loads**

The LT1223 can be isolated from capacitive loads with a small resistor ( $10\Omega$  to  $20\Omega$ ) or it can drive the capacitive load directly if the feedback resistor is increased. Both techniques lower the amplifier's bandwidth about the same amount. The advantage of resistive isolation is that the bandwidth is only reduced when the capacitive load is present. The disadvantage of resistor isolation is that resistive loading causes gain errors. Because the DC accuracy is not degraded with resistive loading, the desired way of driving capacitive loads, such as flash converters, is to increase the feedback resistor. The Maximum Capacitive Load versus Feedback Resistor curve shows the value of feedback resistor and capacitive load that gives 5dB of peaking. For less peaking, use a larger feedback resistor.

## **Power Supplies**

The LT1223 may be operated with single or split supplies as low as  $\pm 4V$  (8V total) to as high as  $\pm 18V$  (36V total). It

is not necessary to use equal value split supplies, however, the offset voltage will degrade about  $350\mu V$  per volt of mismatch. The internal compensation capacitor decreases with increasing supply voltage. The -3dB Bandwidth versus Supply Voltage curve shows how this affects the bandwidth for various feedback resistors. Generally, the bandwidth at  $\pm 5V$  supplies is about half the value it is at  $\pm 15V$  supplies for a given feedback resistor.

The LT1223 is very stable even with minimal supply bypassing, however, the transient response will suffer if the supply rings. It is recommended for good slew rate and settling time that  $4.7\mu F$  tantalum capacitors be placed within 0.5 inches of the supply pins.

## **Input Range**

The noninverting input of the LT1223 looks like a 10M resistor in parallel with a 3pF capacitor until the common mode range is exceeded. The input impedance drops somewhat and the input current rises to about  $10\mu A$  when the input comes too close to the supplies. Eventually, when the input exceeds the supply by one diode drop, the base collector junction of the input transistor forward biases and the input current rises dramatically. The input current should be limited to 10mA when exceeding the supplies. The amplifier will recover quickly when the input is returned to its normal common mode range unless the input was over 500mV beyond the supplies, then it will take an extra 100ns.

## Offset Adjust

Output offset voltage is equal to the input offset voltage times the gain plus the inverting input bias current times the feedback resistor. For low gain applications (3 or less) a  $10k\Omega$  pot connected to pins 1 and 5 with wiper to V+ will trim the inverting input current ( $\pm 10\mu$ A) to null the output; it does not change the offset voltage very much. If the LT1223 is used in a high gain application, where input offset voltage is the dominate error, it can be nulled by pulling approximately  $100\mu$ A from pin 1 or 5. The easy way to do this is to use a  $10k\Omega$  pot between pin 1 and 5 with a 150k resistor from the wiper to ground for 15V supply applications. Use a 47k resistor when operating on a 5V supply.

#### Shutdown

Pin 8 activates a shutdown control function. Pulling more than  $200\mu A$  from pin 8 drops the supply current to less than 3mA, and puts the output into a high impedance state. The easy way to force shutdown is to ground pin 8, using an open collector (drain) logic stage. An internal resistor limits current, allowing direct interfacing with no additional parts. When pin 8 is open, the LT1223 operates normally.

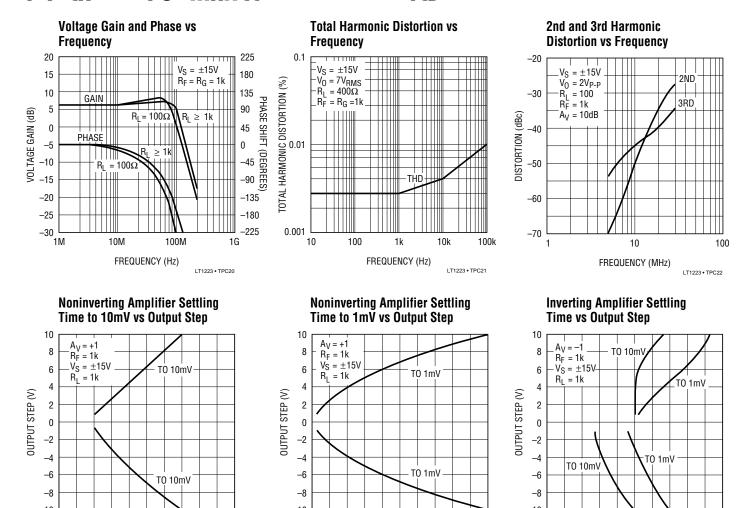

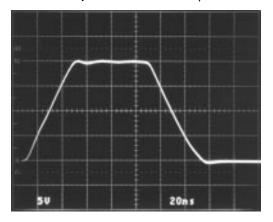

#### Slew Rate

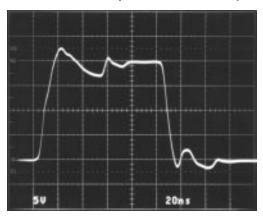

The slew rate of a current feedback amplifier is not independent of the amplifier gain configuration the way it is in a traditional op amp. This is because the input stage and the output stage both have slew rate limitations. Inverting amplifiers do not slew the input and are therefore limited only by the output stage. High gain, noninverting amplifiers are similar. The input stage slew rate of the LT1223 is about 350V/us before it becomes nonlinear and is enhanced by the normally reverse-biased emitters on the input transistors. The output slew rate depends on the size of the feedback resistors. The peak output slew rate is about 2000V/us with a 1k feedback resistor and drops proportionally for larger values. At an output slew rate of 1000V/µs or more, the transistors in the "mirror circuits" will begin to saturate due to the large feedback currents. This causes the output to have slew induced overshoot and is somewhat unusual looking; it is in no way harmful or dangerous to the device. The photos show the LT1223 in a noninverting gain of three ( $R_F = 1k$ ,  $R_G = 500\Omega$ ) with a 20V peak-to-peak output slewing at 500V/μs, 1000V/μs and 2000V/µs.

## **Settling Time**

The Inverting Amplifier Settling Time versus Output Step curve shows that the LT1223 will settle to within 1mV of final value in less than 100ns for all output changes of 10V or less. When operated as an inverting amplifier there is less than  $500\mu V$  of thermal settling in the amplifier. However, when operating the LT1223 as a noninverting amplifier, there is an additional thermal settling component that is about  $200\mu V$  for every volt of input common mode change. So a noninverting gain of one amplifier will

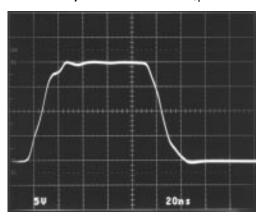

#### Output Slew Rate of 500V/µs

Output Slew Rate of 1000V/µs

Output Slew Rate at 2000V/µs Shows Aberrations (See Text)

have about 2.5mV thermal tail on a 10V step. Unfortunately, reducing the input signal and increasing the gain always results in a thermal tail of about the same amount for a given output step. For this reason we show separate graphs of 10mV and 1mV non-inverting amplifier settling times. Just as the bandwidth of the LT1223 is fairly constant for various closed-loop gains, the settling time remains constant as well.

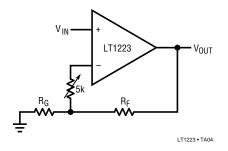

### Adjustable Gain Amplifier

To make a variable gain amplifier with the LT1223, vary the value of  $R_G$ . The implementation of  $R_G$  can be a pot, a light controlled resistor, a FET, or any other low capacitance variable resistor. The value of  $R_F$  should not be varied to change the gain. If  $R_F$  is changed, then the bandwidth will be reduced at maximum gain and the circuit will oscillate when  $R_F$  is very small.

## Adjustable Bandwidth Amplifier

Because the resistance at the inverting input determines the bandwidth of the LT1223, an adjustable bandwidth circuit can be made easily. The gain is set as before with  $R_F$  and  $R_G$ ; the bandwidth is maximum when the variable resistor is at a minimum.

## **Accurate Bandwidth Limiting The LT1223**

It is very common to limit the bandwidth of an op amp by putting a small capacitor in parallel with  $R_{\text{F}}$ . DO NOT PUT A SMALL CAPACITOR FROM THE INVERTING INPUT OF A CURRENT FEEDBACK AMPLIFIER TO ANYWHERE ELSE, ESPECIALLY NOT TO THE OUTPUT. The capacitor on the inverting input will cause peaking or oscillations. If you need to limit the bandwidth of a current feedback amplifier, use a resistor and capacitor at the noninverting input (R1 & C1). This technique will also cancel (to a degree) the peaking caused by stray capacitance at the inverting input. Unfortunately, this will not limit the output noise the way it does for the op amp.

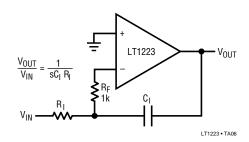

### **Current Feedback Amplifier Integrator**

Since we remember that the inverting input wants to see a resistor, we can add one to the standard integrator circuit. This generates a new summing node where we can apply capacitive feedback. The LT1223 integrator has excellent large signal capability and accurate phase shift at high frequencies.

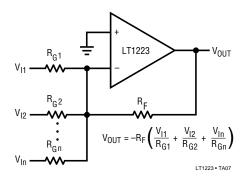

## **Summing Amplifier (DC Accurate)**

The summing amplifier is easily made by adding additional inputs to the basic inverting amplifier configuration. The LT1223 has no  $l_{OS}$  spec because there is no correlation between the two input bias currents. Therefore, we will not improve the DC accuracy of the inverting amplifier by putting in the extra resistor in the noninverting input.

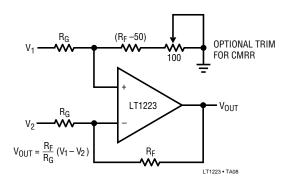

## **Difference Amplifier**

The LT1223 difference amplifier delivers excellent performance if the source impedance is very low. This is because the common mode input resistance is only equal to  $R_{\text{F}} + R_{\text{G}}$ .

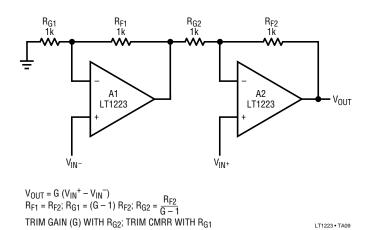

### **Video Instrumentation Amplifier**

This instrumentation amplifier uses two LT1223s to increase the input resistance to well over 1M. This makes an excellent "loop through" or cable sensing amplifier if the

inverting input (A1) senses the shield and the non-inverting input (A2) senses the center conductor. Since this amplifier does not load the cable (take care to minimize stray capacitance) and it rejects common mode hum and noise, several amplifiers can sense the signal with only one termination at the end of the cable. The design equations are simple. Just select the gain you need (it should be two or more) and the value of the feedback resistor (typically 1k) and calculate R<sub>G1</sub> and R<sub>G2</sub>. The gain can be tweaked with  $R_{G2}$  and the CMRR with  $R_{G1}$  if needed. The bandwidth of the noninverting input signal is not reduced by the presence of the other amplifier, however, the inverting input signal bandwidth is reduced since it passes two amplifiers. The CMRR is good at high frequencies because the bandwidth of the amplifiers are about the same even though they do not necessarily operate at the same gain.

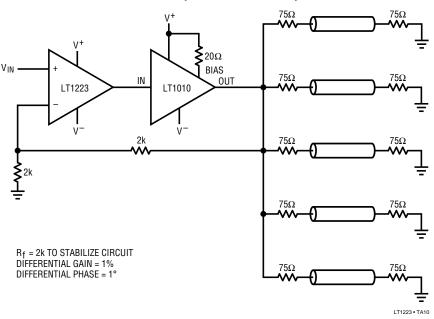

#### Cable Driver

The cable driver circuit is shown on the front page. When driving a cable it is important to properly terminate both ends if even modest high frequency performance is required. The additional advantage of this is that it isolates the capacitive load of the cable from the amplifier so it can operate at maximum bandwidth.

# TYPICAL APPLICATION

## 150mA Output Current Video Amp

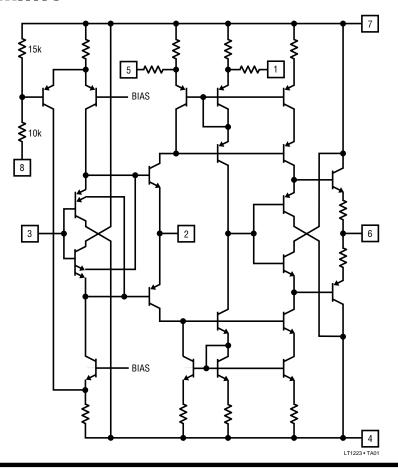

# SIMPLIFIED SCHEMATIC

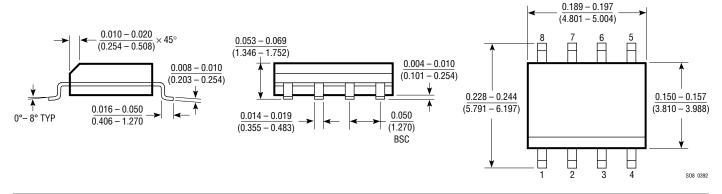

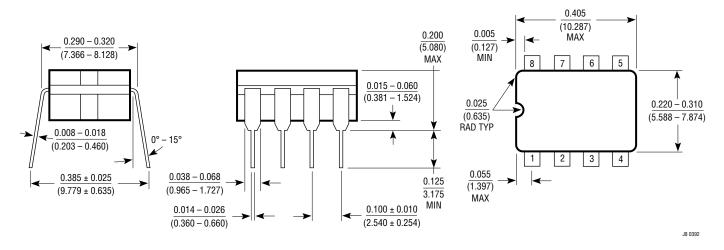

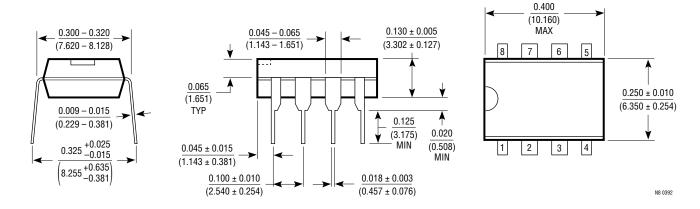

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

#### J8 Package 8-Lead Ceramic DIP

### N8 Package 8-Lead Plastic DIP

#### S8 Package 8-Lead Plastic SOIC