# OGY 14-Bit DC Accurate Clock-Tunable, 8th Order Elliptic or Linear Phase Lowpass Filter

#### **FEATURES**

DC Gain Linearity: 14 Bits

Maximum DC Offset: ±1.5mV

DC Offset TempCo: 7uV/°C

■ Device Fully Tested at f<sub>CUTOFF</sub> = 80kHz

Maximum Cutoff Frequency: 120kHz ( $V_S = \pm 8V$ )

■ Drives  $1k\Omega$  Load with 0.02% THD or Better

Signal-to-Noise Ratio: 90dB

Input Impedance: 500MΩ

Selectable Elliptic or Linear Phase Response

■ Operates from Single 5V up to ±8V Power Supplies

#### **APPLICATIONS**

- Instrumentation

- Data Acquisition Systems

- Anti-Aliasing Filters

- Smoothing Filters

- Audio Signal Processing

#### DESCRIPTION

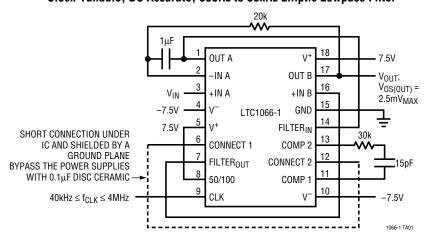

The LTC1066-1 is an 8th order elliptic lowpass filter which simultaneously provides clock-tunability and DC accuracy. The unique and proprietary architecture of the filter allows 14 bits of DC gain linearity and a maximum of 1.5mV DC offset. An external RC is required for DC accurate operation. With  $\pm 7.5 \text{V}$  supplies, a 20k resistor and a  $1 \mu \text{F}$  capacitor, the cutoff frequency can be tuned from 800Hz to 100kHz. A clock-tunable 10Hz to 100kHz operation can also be achieved (see Typical Application section).

The filter does not require any external active components such as input/output buffers. The input/output impedance is  $500M\Omega/0.1\Omega$  and the output of the filter can source or sink 40mA. When pin 8 is connected to V+, the clock-to-cutoff frequency ratio is 50:1 and the input signal is sampled twice per clock cycle to lower the risk of aliasing. For frequencies up to  $0.75f_{CUTOFF}$ , the passband ripple is  $\pm 0.15dB$ . The gain at  $f_{CUTOFF}$  is -1dB and the filter's stopband attenuation is 80dB at  $2.3f_{CUTOFF}$ . Linear phase operation is also available with a clock-to-cutoff frequency ratio of 100:1 when pin 8 is connected to ground.

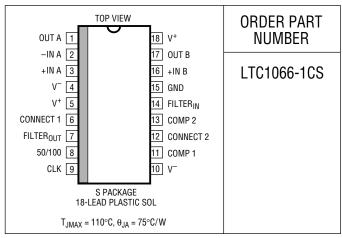

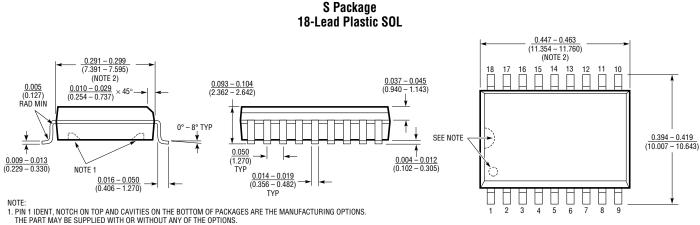

The LTC1066-1 is available in an 18-pin SOL package.

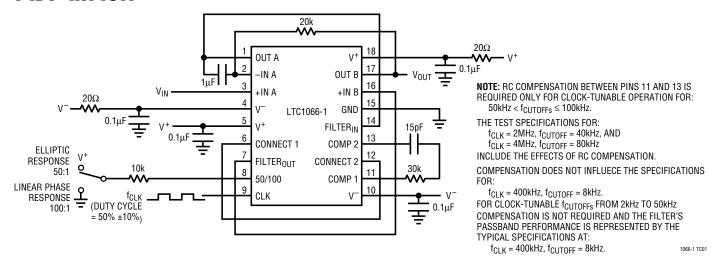

# TYPICAL APPLICATION

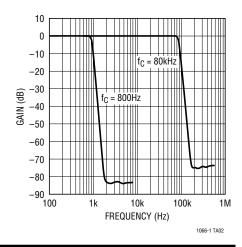

Clock-Tunable, DC Accurate, 800Hz to 80kHz Elliptic Lowpass Filter

#### Amplitude Response

# **ABSOLUTE MAXIMUM RATINGS**

| Total Supply Voltage (V + to V -) 16                         | 5.5V |

|--------------------------------------------------------------|------|

| Power Dissipation                                            | mW   |

| Burn-In Voltage 16                                           | 5.5V |

| Voltage at Any Input $(V^ 0.3V) \le V_{IN} \le (V^+ + 0.4V)$ | 3V)  |

| Maximum Clock Frequency                                      |      |

| $V_S = \pm 8V$ 6.1N                                          | ЛHz  |

| $V_{S} = \pm 7.5 \text{V}$                                   | ЛHz  |

| $V_S = \pm 5V$ 4.1N                                          | ЛHz  |

| V <sub>S</sub> = Single 5V 1.8N                              | ЛHz  |

| Operating Temperature Range* 0°C to 7                        | 0°C  |

| Storage Temperature Range −65°C to 15                        | 0°C  |

| Lead Temperature (Soldering, 10 sec)30                       | 0°C  |

<sup>\*</sup> For an extended operating temperature range contact LTC Marketing for details.

# PACKAGE/ORDER INFORMATION

Consult factory for other package options and for Industrial and Military grade parts.

# **ELECTRICAL CHARACTERISTICS** (See Test Circuit)

$V_S = \pm 7.5 V$ ,  $R_L = 1 k$ ,  $T_A = 25 ^{\circ} C$ ,  $f_{CLK}$  signal level is TTL or CMOS (maximum clock rise or fall time  $\leq 1 \mu s$ ) unless otherwise specified. All AC gain measurements are referenced to passband gain.

| PARAMETER                                                                                 | CONDITIONS                                             |   | MIN            | TYP            | MAX            | UNITS    |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------|---|----------------|----------------|----------------|----------|

| Passband Gain (0.01f <sub>CUTOFF</sub> to 0.25f <sub>CUTOFF</sub> )                       | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 2kHz    | • | -0.18          | 0.16           | 0.36           | dB       |

| Passband Ripple (0.01 $f_{CUTOFF}$ to 0.75 $f_{CUTOFF}$ ) for $f_{CLK}/f_{CUTOFF} = 50:1$ | f <sub>CUTOFF</sub> ≤ 50kHz (See Note on Test Circuit) |   |                | ±0.15          |                | dB       |

| Gain at 0.50f <sub>CUTOFF</sub> for f <sub>CLK</sub> /f <sub>CUTOFF</sub> = 50:1          | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 4kHz    | • | -0.09<br>-0.14 | 0.02<br>0.05   | 0.09<br>0.14   | dB<br>dB |

|                                                                                           | f <sub>CLK</sub> = 2MHz, f <sub>TEST</sub> = 20kHz     | • | -0.16<br>-0.22 | -0.05<br>-0.10 | 0.02<br>0.02   | dB<br>dB |

| Gain at 0.75f <sub>CUTOFF</sub> for f <sub>CLK</sub> /f <sub>CUTOFF</sub> = 50:1          | $f_{CLK} = 400kHz, f_{TEST} = 6kHz$                    | • | -0.18<br>-0.22 | -0.05<br>-0.10 | 0.05<br>0.05   | dB<br>dB |

|                                                                                           | f <sub>CLK</sub> = 2MHz, f <sub>TEST</sub> = 30kHz     | • | -0.36<br>-0.45 | -0.20<br>-0.30 | 0.05<br>0.05   | dB<br>dB |

|                                                                                           | f <sub>CLK</sub> = 4MHz, f <sub>TEST</sub> = 60kHz     | • | -0.65<br>-0.85 | -0.30<br>-0.40 | 0.25<br>0.75   | dB<br>dB |

| Gain at 1.00f <sub>CUTOFF</sub> for f <sub>CLK</sub> /f <sub>CUTOFF</sub> = 50:1          | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 8kHz    | • | -1.50<br>-1.80 | -1.10<br>-1.20 | -0.05<br>-0.05 | dB<br>dB |

|                                                                                           | f <sub>CLK</sub> = 2MHz, f <sub>TEST</sub> = 40kHz     | • | -2.10<br>-2.30 | -1.60<br>-1.60 | -1.20<br>-1.20 | dB<br>dB |

|                                                                                           | f <sub>CLK</sub> = 4MHz, f <sub>TEST</sub> = 80kHz     | • | -2.20<br>-2.50 | -1.60<br>-1.60 | -0.05<br>0.25  | dB<br>dB |

| Gain at 2.00f <sub>CUTOFF</sub> for f <sub>CLK</sub> /f <sub>CUTOFF</sub> = 50:1          | $f_{CLK} = 400kHz$ , $f_{TEST} = 16kHz$                | • | -56<br>-54     | -58<br>-57     | -64<br>-64     | dB<br>dB |

|                                                                                           | f <sub>CLK</sub> = 2MHz, f <sub>TEST</sub> = 80kHz     | • | -53<br>-51     | -56<br>-55     | -62<br>-62     | dB<br>dB |

|                                                                                           | f <sub>CLK</sub> = 4MHz, f <sub>TEST</sub> = 160kHz    | • | -50<br>-48     | -52<br>-51     | -60<br>-60     | dB<br>dB |

# ELECTRICAL CHARACTERISTICS (See Test Circuit)

$V_S$  =  $\pm 7.5V$ ,  $R_L$  = 1k,  $T_A$  = 25°C,  $f_{CLK}$  signal level is TTL or CMOS (maximum clock rise or fall time  $\leq 1 \mu s$ ) unless otherwise specified. All AC gain measurements are referenced to passband gain.

| PARAMETER                                                                 |                                  | CONDITIONS                                                              |   | MIN              | TYP              | MAX              | UNITS      |

|---------------------------------------------------------------------------|----------------------------------|-------------------------------------------------------------------------|---|------------------|------------------|------------------|------------|

| Gain at $f_{CUTOFF}$ for $f_{CLK} = 20$ kHz, $V_S = \pm 7.5$ V            |                                  | f <sub>CLK</sub> /f <sub>CUTOFF</sub> = 50:1, f <sub>TEST</sub> = 400Hz | • | -1.75            | -1.25            | -0.50            | dB         |

| Gain at $f_{CUTOFF}$ for $V_S = \pm 2.375V$ , $f_{CLK}/f_{CUTOFF} = 50:1$ |                                  | f <sub>CLK</sub> = 1MHz, f <sub>TEST</sub> = 20kHz                      | • | -1.75            | -0.70            | 0.10             | dB         |

| Gain at 70kHz for $V_S = \pm 5$                                           | $V, f_{CLK}/f_{CUTOFF} = 50:1$   | f <sub>CLK</sub> = 4MHz, f <sub>TEST</sub> = 70kHz                      | • |                  | 1.00             | 1.40             | dB         |

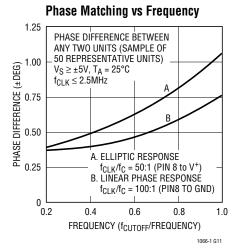

| Linear Phase Response f <sub>CLK</sub> /f <sub>CUTOFF</sub> = 100:1,      | Phase at 0.25f <sub>CUTOFF</sub> | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 1kHz                     | • | -48.5<br>-48.0   | -50.0<br>-50.0   | -51.5<br>-52.0   | Deg<br>Deg |

| Pin 8 at GND                                                              | Gain at 0.25f <sub>CUTOFF</sub>  | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 1kHz                     | • | -0.65            | -0.25            | 0.25             | dB         |

|                                                                           | Phase at 0.50f <sub>CUTOFF</sub> | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 2kHz                     | • | -97.5<br>-97.0   | -99.5<br>-99.5   | -101.5<br>-102.0 | Deg<br>Deg |

|                                                                           | Gain at 0.50f <sub>CUTOFF</sub>  | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 2kHz                     | • | -0.75            | -0.50            | -0.10            | dB         |

|                                                                           | Phase at 0.75f <sub>CUTOFF</sub> | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 3kHz                     | • | -148.0<br>-147.5 | -150.5<br>-150.5 | -152.5<br>-153.0 | Deg<br>Deg |

|                                                                           | Gain at 0.75f <sub>CUTOFF</sub>  | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 3kHz                     | • | -1.40            | -1.00            | -0.60            | dB         |

|                                                                           | Phase at f <sub>CUTOFF</sub>     | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 4kHz                     | • | -208.0<br>-207.5 | -210.0<br>-210.0 | -212.5<br>-213.0 | Deg<br>Deg |

|                                                                           | Gain at f <sub>CUTOFF</sub>      | f <sub>CLK</sub> = 400kHz, f <sub>TEST</sub> = 4kHz                     | • | -2.10            | -1.80            | -1.60            | dB         |

| Input Bias Current                                                        |                                  | $V_S = \pm 2.375V$                                                      | • |                  | 60<br>70         | 135              | nA<br>nA   |

| Input Offset Current                                                      |                                  | $V_S = \pm 2.375V$<br>$V_S \ge \pm 5V$ (Note 2)                         | • |                  | ±10<br>±10       | ±40<br>±45       | nA<br>nA   |

| Input Offset Current Temp                                                 | Со                               | $\pm 2.375 \text{V} \le \text{V}_{\text{S}} \le \pm 7.5 \text{V}$       |   |                  | 40               |                  | pA/°C      |

| Output Voltage Offset Tem                                                 | прСо                             | $\pm 2.375 \text{V} \le \text{V}_{\text{S}} \le \pm 7.5 \text{V}$       |   |                  | 7                |                  | μV/°C      |

| Output Offset Voltage                                                     |                                  | $V_S = \pm 2.375V$ , $f_{CLK} = 400$ kHz                                | • |                  | ±0.5<br>±1.0     | ±1.5             | mV<br>mV   |

|                                                                           |                                  | $V_S \ge \pm 5V$ (Note 2)                                               | • |                  | ±0.5<br>±1.0     | ±1.5             | mV<br>mV   |

| Common-Mode Rejection                                                     |                                  | $V_S = \pm 7.5V$<br>$V_{CM} = -5V \text{ to } 5V$                       | • | 90<br>84         | 96<br>90         |                  | dB<br>dB   |

| Power Supply Rejection                                                    |                                  | $V_S = \pm 2.5 V \text{ to } \pm 7.5 V$                                 | • | 80<br>78         | 84<br>82         |                  | dB<br>dB   |

| Input Voltage Range and (                                                 | Output Voltage Swing             | $V_S = \pm 2.375V, R_L = 1k$                                            | • | ±1.2<br>±1.1     | ±1.4             |                  | V          |

|                                                                           |                                  | $V_S = \pm 5V$ , $R_L = 1k$                                             | • | ±3.4<br>±3.2     | ±3.6             |                  | V          |

|                                                                           |                                  | $V_S = \pm 7.5 V, R_L = 1 k$                                            | • | ±5.4<br>±5.0     | ±5.8             |                  | V          |

| Output Short-Circuit Curre                                                | ent                              | $\pm 2.375 \text{V} \le \text{V}_{\text{S}} \le \pm 7.5 \text{V}$       |   |                  |                  | ±40              | mA         |

| Power Supply Current (No                                                  | ote 1)                           | $V_S = \pm 2.375V$                                                      | • |                  | 14<br>16         | 16<br>19         | mA<br>mA   |

|                                                                           |                                  | $V_S = \pm 5V$                                                          | • |                  | 22<br>23         | 26<br>29         | mA<br>mA   |

|                                                                           |                                  | $V_{S} = \pm 7.5 V$                                                     | • |                  | 25<br>26         | 30<br>33         | mA<br>mA   |

| Power Supply Range                                                        |                                  |                                                                         |   | ±2.375           |                  | ±8               | V          |

The lacktriangle denotes specifications which apply over the full operating temperature range.

**Note 1:** The maximum current over temperature is at  $0^{\circ}$ C. At  $70^{\circ}$ C the maximum current is less than its maximum value at  $25^{\circ}$ C.

Note 2: Guaranteed by design and test correlation.

# TYPICAL PERFORMANCE CHARACTERISTICS

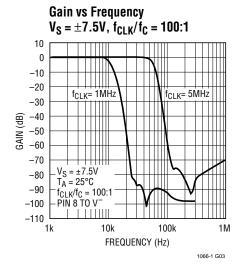

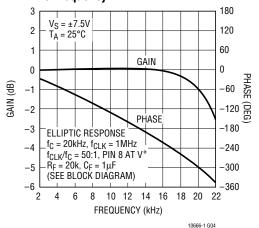

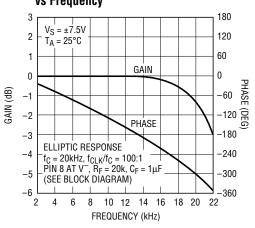

Passband Gain and Phase vs Frequency

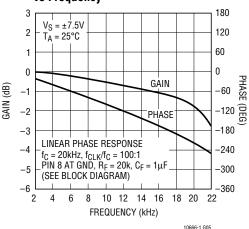

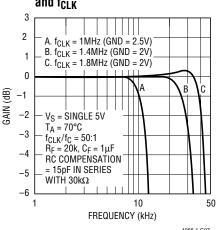

Passband Gain and Phase vs Frequency

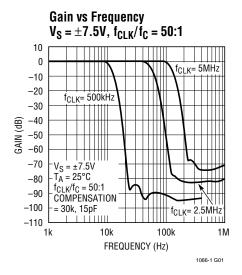

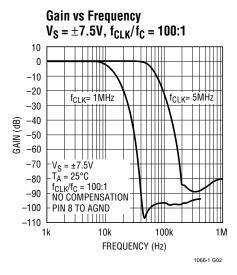

Passband Gain vs Frequency and  $f_{CLK}$

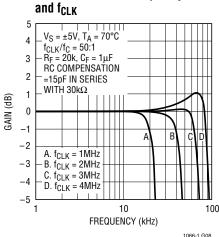

Passband Gain vs Frequency

1000-1 G0

## TYPICAL PERFORMANCE CHARACTERISTICS

#### **Passband Gain vs Frequency** $V_S = \pm 7.5 V$ , $T_A = 70 ^{\circ} C$ 4 $f_{CLK}/f_{C} = 50:1$ $R_F=20k,\,C_F=1\mu F$ RC COMPENSATION 2 = 15pF IN SERIES WITH 30kΩ 1 0 -2 A. f<sub>CLK</sub> = 2MHz -3 · B. f<sub>CLK</sub> = 3MHz C. f<sub>CLK</sub> = 4MHz -4 D. f<sub>CLK</sub> = 5MHz -5 1 10 100 200 FREQUENCY (kHz) 1066-1 G09

# TYPICAL PERFORMANCE CHARACTERISTICS

Power Supply Current vs Power Supply Voltage

30

27

24

21

18

15

15

10

2 4 6 8 10 12 14 16 18 20

TOTAL POWER SUPPLY VOLTAGE (V)

Table 1. Elliptic Response,  $f_C$  = 10kHz,  $f_{CLK}/f_{CUTOFF}$  = 50:1,  $V_S$  =  $\pm 7.5 V,~R_F$  = 20k,  $C_F$  = 1 $\mu F,~No~RC$  Compensation,  $T_A$  = 25°C

| FREQUENCY<br>(kHz) | GAIN<br>(dB) | PHASE<br>(DEG) | GROUP DELAY<br>(μs) |

|--------------------|--------------|----------------|---------------------|

| 2.000              | 0.117        | -50.09         | 70.52               |

| 3.000              | 0.118        | -75.75         | 72.04               |

| 4.000              | 0.116        | -101.96        | 74.32               |

| 5.000              | 0.112        | -129.25        | 77.59               |

| 6.000              | 0.104        | -157.82        | 82.04               |

| 7.000              | 0.074        | 171.68         | 88.56               |

| 8.000              | -0.014       | 138.41         | 97.80               |

| 9.000              | -0.278       | 101.26         | 110.33              |

| 10.000             | -0.986       | 58.98          | 124.91              |

Table 2. Elliptic Response,  $f_C$  = 50kHz,  $f_{CLK}/f_{CUTOFF}$  = 50:1,  $V_S$  =  $\pm 7.5 V,~R_F$  = 20k,  $C_F$  = 1 $\mu F,~No~RC$  Compensation,  $T_A$  = 25°C

| FREQUENCY<br>(kHz) | GAIN<br>(dB) | PHASE<br>(DEG) | GROUP DELAY<br>(µs) |

|--------------------|--------------|----------------|---------------------|

| 10.000             | 0.104        | -50.91         | 14.32               |

| 15.000             | 0.105        | -76.95         | 14.61               |

| 20.000             | 0.107        | -103.51        | 15.05               |

| 25.000             | 0.109        | -131.13        | 15.70               |

| 30.000             | 0.107        | -160.03        | 16.57               |

| 35.000             | 0.089        | 169.22         | 17.85               |

| 40.000             | 0.014        | 135.72         | 19.66               |

| 45.000             | -0.231       | 98.44          | 22.10               |

| 50.000             | -0.905       | 56.15          | 24.93               |

Table 3. Linear Phase Response,  $f_C$  = 10kHz,  $f_{CLK}/f_{CUTOFF}$  = 100:1,  $V_S$  =  $\pm 7.5 V,\ R_F$  = 20k,  $C_F$  = 1 $\mu F$ , No RC Compensation,  $T_A$  = 25°C

| не сетренешнен, тд = с |              |                |                     |  |  |

|------------------------|--------------|----------------|---------------------|--|--|

| FREQUENCY<br>(kHz)     | GAIN<br>(dB) | PHASE<br>(DEG) | GROUP DELAY<br>(µs) |  |  |

| 2.000                  | -0.020       | - 39.96        | 55.25               |  |  |

| 3.000                  | -0.181       | - 59.76        | 55.03               |  |  |

| 4.000                  | -0.383       | - 79.60        | 54.98               |  |  |

| 5.000                  | -0.601       | - 99.34        | 55.28               |  |  |

| 6.000                  | -0.811       | -119.40        | 56.34               |  |  |

| 7.000                  | -1.004       | -139.91        | 58.56               |  |  |

| 8.000                  | -1.196       | -161.56        | 62.34               |  |  |

| 9.000                  | -1.451       | 175.21         | 67.29               |  |  |

| 10.000                 | -1.910       | 149.99         | 72.31               |  |  |

|                        |              |                |                     |  |  |

Table 4. Linear Phase Response,  $f_C$  = 50kHz,  $f_{CLK}/f_{CUTOFF}$  = 100:1,  $V_S$  =  $\pm 7.5 V,~R_F$  = 20k,  $C_F$  =  $1 \mu F,~No~RC$  Compensation,  $T_A$  =  $25^{\circ}C$

| The tree compensation, T <sub>A</sub> =0 0 |              |                |                     |  |

|--------------------------------------------|--------------|----------------|---------------------|--|

| FREQUENCY<br>(kHz)                         | GAIN<br>(dB) | PHASE<br>(DEG) | GROUP DELAY<br>(µs) |  |

| 10.000                                     | 0.039        | - 40.72        | 11.30               |  |

| 15.000                                     | -0.068       | - 61.01        | 11.31               |  |

| 20.000                                     | -0.202       | - 81.42        | 11.36               |  |

| 25.000                                     | -0.345       | -101.88        | 11.48               |  |

| 30.000                                     | -0.479       | -122.74        | 11.73               |  |

| 35.000                                     | -0.594       | -144.09        | 12.20               |  |

| 40.000                                     | -0.701       | -166.68        | 12.99               |  |

| 45.000                                     | -0.860       | 169.15         | 14.06               |  |

| 50.000                                     | -1.214       | 142.72         | 15.19               |  |

#### PIN FUNCTIONS

#### Power Supply Pins (5, 18, 4, 10)

The power supply pins should be bypassed with a  $0.1\mu F$  capacitor to an adequate analog ground. The bypass capacitors should be connected as close as possible to the power supply pins. The V<sup>+</sup> pins (5, 18) and the V<sup>-</sup> pins (4, 10) should always be tied to the same positive supply and negative supply value respectively. Low noise linear supplies are recommended. Switching power supplies are not recommended as they will lower the filter dynamic range.

When the LTC1066-1 is powered up with dual supplies and, if V<sup>+</sup> is applied prior to a floating V<sup>-</sup>, connect a signal diode (1N4148) between pin 10 and ground to prevent power supply reversal and latch-up. A signal diode (1N4148) is also recommended between pin 5 and ground if the negative supply is applied prior to the positive supply and the positive supply is floating. Note, in most laboratory supplies, reversed biased diodes are always connected between the supply output terminals and ground, and the above precautions are not necessary. However, when the filter is powered up with conventional 3-terminal regulators, the diodes are recommended.

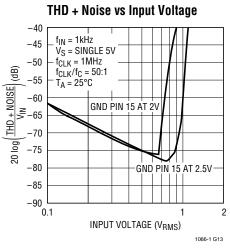

#### **Analog Ground Pin (15)**

The filter performance depends on the quality of the analog signal ground. For either dual or single supply operation, an analog ground plane surrounding the package is recommended. The analog ground plane should be connected to any digital ground at a single point. For dual supply operation, pin 15 should be connected to the analog ground plane. For single supply operation pin 15 should be biased at 1/2 supply and should be bypassed to the analog ground plane with at least a 1 $\mu$ F capacitor (see Typical Applications). For single 5V operation and for f<sub>CLK</sub>  $\geq$  1.4MHz, pin 15 should be biased at 2V. This minimizes passband gain and phase variations.

## Clock Input Pin (9)

Any TTL or CMOS clock source with a square-wave output and 50% duty cycle ( $\pm 10\%$ ) is an adequate clock source for the device. The power supply for the clock source should not be the filter's power supply. The analog ground for the filter should be connected to clock's ground at a single point only. Table 5 shows the clock's low and high

level threshold values for a dual or single supply operation. Sine waves are not recommended for clock input frequencies less than 100kHz, since excessively slow clock rise or fall times generate internal clock jitter (maximum clock rise or fall time  $\leq 1 \mu s$ ). The clock signal should be routed from the left side of the IC package and perpendicular to it to avoid coupling to any input or output analog signal path. A  $200\Omega$  resistor between clock source and pin 9 will slow down the rise and fall times of the clock to further reduce charge coupling.

Table 5. Clock Source High and Low Threshold Levels

| POWER SUPPLY             | HIGH LEVEL | LOW LEVEL |

|--------------------------|------------|-----------|

| Dual Supply = ±7.5V      | ≥ 2.18V    | ≤ 0.5V    |

| Dual Supply = $\pm 5V$   | ≥ 1.45V    | ≤ 0.5V    |

| Dual Supply = $\pm 2.5V$ | ≥ 0.73V    | ≤-2.0V    |

| Single Supply = 12V      | ≥ 7.80V    | ≤ 6.5V    |

| Single Supply = 5V       | ≥ 1.45V    | ≤ 0.5V    |

#### 50:1/100:1 Pin (8)

The DC level at pin 8 determines the ratio of the clock to the filter cutoff frequency. When pin 8 is connected to V $^+$  the clock-to-cutoff frequency ratio ( $f_{\text{CLK}}/f_{\text{CUTOFF}}$ ) is 50:1 and the filter response is elliptic. The design of the internal switched-capacitor filter was optimized for a 50:1 operation.

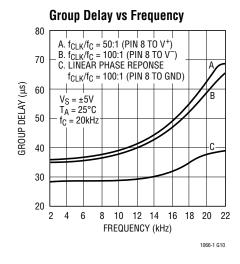

When pin 8 is connected to ground (or 1/2 supply for single supply operation), the  $f_{CLK}/f_{CUTOFF}$  ratio is equal to 100:1 and the filter response is pseudolinear phase (see Group Delay vs Frequency in Typical Performance Characteristic section).

When pin 8 is connected to  $V^-$  (or ground for single supply operation), the  $f_{CLK}/f_{CUTOFF}$  ratio is 100:1 and the filter response is transitional Butterworth elliptic. The Typical Performance Characteristics provide all the necessary information.

If the DC level at pin 8 is mechanically switched, a 10k resistor should be connected between pin 8 and the DC source.

#### Input Pins (2, 3, 14, 16)

Pin 3 (+IN A) and pin 2 (-IN A) are the positive and negative inputs of an internal high performance op amp A

## PIN FUNCTIONS

(see Block Diagram). Input bias current flows out of pins 2 and 3. Pin 16 (+IN B) is the positive input of a high performance op amp B which is internally connected as a unity-gain follower. Op amp B buffers the switched-capacitor network output. The input capacitance of both op amps is 10pF.

Pin 14 (FILTER<sub>IN</sub>) is the input of a switched-capacitor network. The input impedance of pin 14 is typically 11k.

#### **Output Pins (1, 7, 17)**

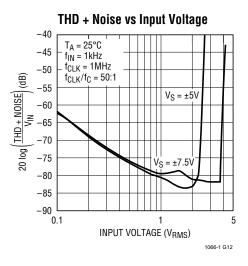

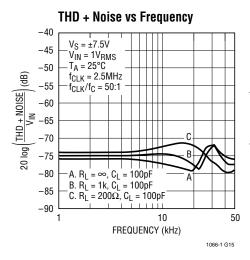

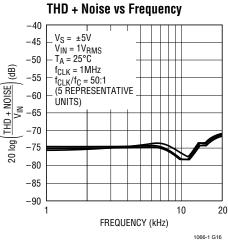

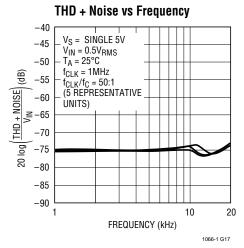

Pins 1 and 17 are the outputs of the internal high performance op amps A and B. Pin 1 is usually connected to the internal switched-capacitor filter network input pin 14. Pin 17 is the buffered output of the filter and it can drive loads as heavy as  $200\Omega$  (see THD + Noise curves under Typical Performance Characteristics). Pin 7 is the internal switched-capacitor network output and it can typically sink or source 1mA.

#### Compensation Pins (11, 13)

Pins 11 and 13 are the AC compensation pins. If compensation is needed, an external 30k resistor in series with a

15pF capacitor should be connected between pins 11 and 13. Compensation is recommended for the following cases shown in Table 6.

Table 6. Cases Where an RC Compensation (15pF in Series with  $30k\Omega$  pins 11, 13) is Recommended,  $f_{CLK}/f_{CUTOFF} = 50:1$

| V <sub>S</sub> = Single 5V (AGND = 2V) | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 70°C | f <sub>CUTOFF</sub> ≥ 28kHz<br>f <sub>CUTOFF</sub> ≥ 24kHz       |

|----------------------------------------|------------------------------------------------|------------------------------------------------------------------|

| $V_S = \pm 5V$                         | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 70°C | $f_{CUTOFF} \ge 60 \text{kHz}$<br>$f_{CUTOFF} \ge 50 \text{kHz}$ |

| $V_S = \pm 7.5V$                       | T <sub>A</sub> = 25°C<br>T <sub>A</sub> = 70°C | $f_{CUTOFF} \ge 70 \text{kHz}$<br>$f_{CUTOFF} \ge 60 \text{kHz}$ |

#### Connect Pins (6, 12)

Pin 6 (CONNECT 1) and pin 12 (CONNECT 2) should be shorted. In a printed circuit board the connection should be done under the IC package through a short trace surrounded by the analog ground plane. Pin 6 should be 0.2 inches away from any other circuit trace.

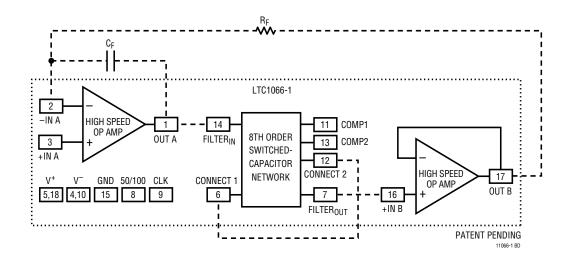

# **BLOCK DIAGRAM**

## **TEST CIRCUIT**

## APPLICATIONS INFORMATION

#### DC PERFORMANCE

The DC performance of the LTC1066-1 is dictated by the DC characteristics of the input precision op amp.

- 1. DC input voltages in the vicinity of the filter's half of the total power supply are processed with exactly 0dB (or 1V/V) of gain.

- 2. The typical DC input voltage ranges are equal to:

$$\begin{split} V_{IN} &= \pm 5.8 \text{V}, \ V_S = \pm 7.5 \text{V} \\ V_{IN} &= \pm 3.6 \text{V}, \ V_S = \pm 5 \text{V} \\ V_{IN} &= \pm 1.4 \text{V}, \ V_S = \pm 2.5 \text{V} \end{split}$$

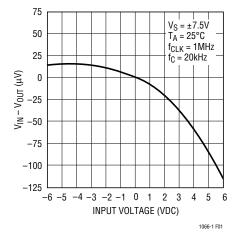

With an input DC voltage range of  $V_{IN}$  =  $\pm 5V$ , ( $V_S$  =  $\pm 7.5V$ ), the measured CMRR was 100dB. Figure 1 shows the DC gain linearity of the filter exceeding the requirements of a 14-bit, 10V full scale system.

3. The filter output DC offset  $V_{OS(OUT)}$  is measured with the input grounded and with dual power supplies. The  $V_{OS(OUT)}$  is typically  $\pm 0.1 mV$  and it is optimized for the filter connection shown in the test circuit figure. The filter output offset is equal to:

$$V_{OS(OUT)} = V_{OS}$$

(op amp A)  $-I_{BIAS} \times R_F = 0.1 \text{mV}$  (Typ)

- 4. The  $V_{OS(OUT)}$  temperature drift is typically  $7\mu V/^{\circ}C$  ( $T_A > 25^{\circ}C$ ), and  $-7\mu V/^{\circ}C$  ( $T_A < 25^{\circ}C$ ).

- 5. The  $V_{OS(OUT)}$  temperature drift can be improved by using an input resistor  $R_{IN}$  equal to the feedback resis-

Figure 1. DC Gain Linearity

tor  $R_F$ , however, the absolute value of  $V_{OS(OUT)}$  will increase. For instance, if a 20k resistor is added in series with pin 3 (see Test Circuit), the output  $V_{OS}$  drift will be improved by  $2\mu V/^{\circ}C$  to  $3\mu V/^{\circ}C$ , however, the  $V_{OS(OUT)}$  may increase by  $1mV_{(MAX)}$ .

6. The filter DC output offset voltage  $V_{OS(OUT)}$  is independent from the filter clock frequency ( $f_{CLK} \le 250 \text{kHz}$ ).

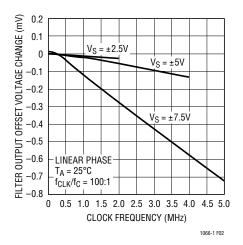

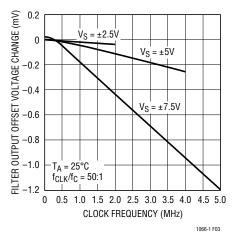

Figures 2 and 3 show the  $V_{OS(OUT)}$  variation for three different power supplies and for clock frequencies up to 5MHz. Both figures were traced with the LTC1066-1 soldered into the PC board. Power supply decoupling is very important, especially with  $\pm 7.5 \text{V}$  supplies. If necessary connect a small resistor (20 $\Omega$ ) between pins 5

#### APPLICATIONS INFORMATION

and 18, and between pins 10 and 4, to isolate the precision op amp supply pin from the switched-capacitor network supply (see the Test Circuit).

Figure 2. Output Offset Change vs Clock (Relative to Offset for  $f_{CLK} = 250kHz$ )

Figure 3. Output Offset Change vs Clock (Relative to Offset for  $f_{CLK} = 250kHz$ )

#### **AC PERFORMANCE**

#### AC (Passband) Gain

The passband gain of the LTC1066-1 is equal to the passband gain of the internal switched-capacitor lowpass filter, and it is measured at  $f = 0.25f_{CUTOFF}$ . Unlike conventional monolithic filters, the LTC1066-1 starts with an

absolutely perfect 0dB DC gain and phases into an "imperfect" AC passband gain, typically  $\pm 0.1$ dB.

The filter's low passband ripple, typically 0.05dB, is measured with respect to the AC passband gain.

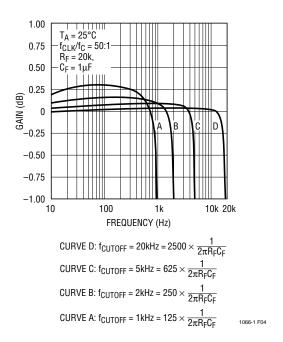

The LTC1066-1 DC stabilizing loop slightly warps the filter's passband performance if the -3dB frequency of the feedback passive elements  $(1/2\pi R_F C_F)$  is more than the cutoff frequency of the internal switched-capacitor filter divided by 250. The LTC1066-1 clock tunability directly relates to the above constraint. Figure 4 illustrates the passband behavior of the LTC1066-1 and it demonstrates the clock tunability of the device. A typical LTC1066-1 device was used to trace all four curves of Figure 4. Curve D, for instance, has nearly zero ripple and 0.04dB passband gain. Curve D's 20kHz cutoff is much higher than the 8Hz cutoff frequency of the R<sub>F</sub>C<sub>F</sub> feedback network, so its passband is free from any additional error due to R<sub>F</sub>C<sub>F</sub> feedback elements. Curve B illustrates the passband error when the 1MHz clock of curve D is lowered to 100kHz. A 0.1dB error is added to the filter's original AC gain of 0.04dB.

Figure 4. Passband Behavior

## APPLICATIONS INFORMATION

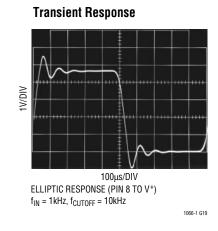

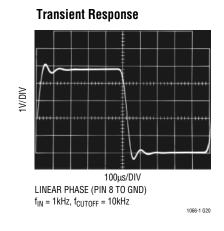

#### **Transient Response and Settling Time**

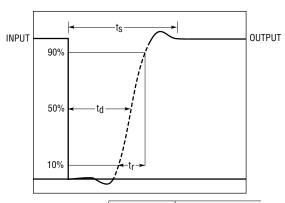

The LTC1066-1 exhibits two different transient behaviors. First, during power-up the DC correcting loop will settle after the voltage offset of the internal switched-capacitor network is stored across the feedback capacitor  $C_F$  (see Block Diagram). It takes approximately five time constants  $(5R_FC_F)$  for settling to 1%. Second, following DC loop settling, the filter reaches steady state. The filter transient response is then defined by the frequency characteristics of the internal switched-capacitor lowpass filter. Figure 5 shows details.

DC loop settling is also observed if, at steady state, the DC offset of the internal switched-capacitor network suddenly changes. A sudden change may occur if the clock frequency is instantaneously stepped to a value above 1MHz.

|                                 | 50:1 ELLIPTIC            | 100:1 LINEAR PHASE                      |

|---------------------------------|--------------------------|-----------------------------------------|

| RISE TIME (t <sub>r</sub> )     | 0.43 ±5%                 | 0.43 ±5%                                |

| THOL THAL (ty)                  | f <sub>CUTOFF</sub> ±070 | f <sub>CUTOFF</sub> ±3 /6               |

| SETTLING TIME (t <sub>s</sub> ) | 3.4 ±5%                  | 2.05 ±5%                                |

|                                 | fcutoff                  | f <sub>CUTOFF</sub> f <sub>CUTOFF</sub> |

| DELAY TIME (t <sub>d</sub> )    | 0.709 +5%                | 0.556 ±5%                               |

| DELAT THRE (rd)                 | f <sub>CUTOFF</sub> 1070 | f <sub>CUTOFF</sub> ±3 76               |

Figure 5. Transient Response

#### **Clock Feedthrough**

Clock feedthrough is defined as the RMS value of the clock frequency and its harmonics that are present at the filter's output pin (9). The clock feedthrough is tested with the input pin (2) grounded and depends on PC board layout

and on the value of the power supplies. With proper layout techniques the values of the clock feedthrough are shown on Table 7.

Table 7. Clock Feedthrough

| POWER SUPPLY |                           | 50:1                                                                | 100:1                                                               |  |  |

|--------------|---------------------------|---------------------------------------------------------------------|---------------------------------------------------------------------|--|--|

|              | Single 5V<br>±5V<br>±7.5V | 70μV <sub>RMS</sub><br>100μV <sub>RMS</sub><br>160μV <sub>RMS</sub> | 90μV <sub>RMS</sub><br>200μV <sub>RMS</sub><br>650μV <sub>RMS</sub> |  |  |

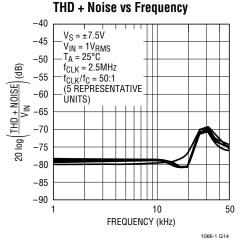

#### **Wideband Noise**

The wideband noise of the filter is the total RMS value of the device's noise spectral density and is used to determine the operating signal-to-noise ratio. Most of its frequency contents lie within the filter passband and cannot be reduced with post filtering. For instance, the LTC1066-1 wideband noise at  $\pm 5 \text{V}$  supply is  $100 \mu \text{V}_{RMS}$ ,  $95 \mu \text{V}_{RMS}$  of which have frequency contents from DC up to the filter's cutoff frequency. The total wideband noise  $(\mu \text{V}_{RMS})$  is nearly independent of the value of the clock. The clock feedthrough specifications are not part of the wideband noise. Table 8 lists the typical wideband noise for each supply.

Table 8. Wideband Noise

| POWER SUPPLY | 50:1                 | 100:1 (Pin 8 to GND) |

|--------------|----------------------|----------------------|

| Single 5V    | 90μV <sub>RMS</sub>  | 80μV <sub>RMS</sub>  |

| ±5V          | 100 $\mu$ V $_{RMS}$ | 85μV <sub>RMS</sub>  |

| ±7.5V        | 106μV <sub>RMS</sub> | 90μV <sub>RMS</sub>  |

#### **Speed Limitations**

To avoid op amp slew rate limiting at maximum clock frequencies, the signal amplitude should be kept below a specified level as shown in Table 9.

Table 9. Maximum V<sub>IN</sub>

| INPUT FREQUENCY | MAXIMUM V <sub>IN</sub> |

|-----------------|-------------------------|

| ≥250kHz         | 0.50V <sub>RMS</sub>    |

| ≥700kHz         | 0.25V <sub>RMS</sub>    |

## APPLICATIONS INFORMATION

#### **Aliasing**

In a sampled-data system the sampling theorem says that if an input signal has any frequency components greater than one half the sampling frequency, aliasing errors will appear at the output. In practice, aliasing is not always a serious problem. High order switched-capacitor lowpass filters are inherently band limited and significant aliasing occurs only for input signals centered around the clock frequency and its multiples.

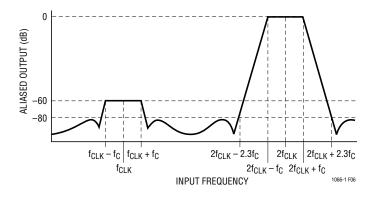

Figure 6 shows the LTC1066-1 aliasing response when operated with a clock-to-cutoff frequency ratio of 50:1. With a 50:1 ratio LTC1066-1 samples its input twice during one clock period and the sampling frequency is equal to two times the clock frequency.

The figure also shows the maximum aliased output generated for inputs in the range of  $2f_{CLK}\pm f_C.$  For instance, if the LTC1066-1 is programmed to produce a cutoff frequency of 20kHz with 1MHz clock, a 10mV, 1.02MHz input signal will cause a 10µV aliased signal at 20kHz. This signal will be buried in the noise. Maximum aliasing will occur only for input signals in the narrow range of 2MHz  $\pm$ 20kHz or multiples of 2MHz.

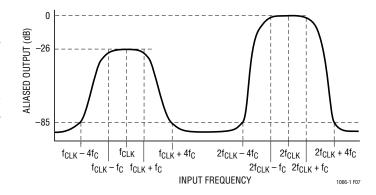

Figure 7 shows the LTC1066-1 aliased response when operated with a clock-to-cutoff frequency ratio of 100:1 (linear phase response with pin 8 to ground).

Figure 6. Aliasing vs Frequency  $f_{CLK}/f_C = 50:1$  (Pin 8 to V <sup>+</sup>) Clock is a 50% Duty Cycle Square Wave

Figure 7. Aliasing vs Frequency f<sub>CLK</sub>/f<sub>C</sub> = 100:1 (Pin 8 to Ground) Clock is a 50% Duty Cycle Square Wave

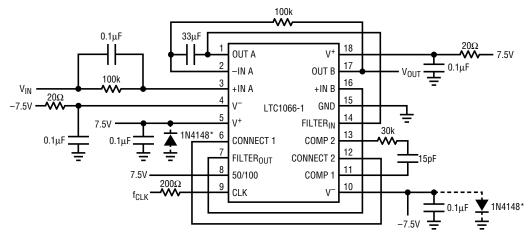

# Dual Supply Operation DC Accurate, 10Hz to 100kHz, Clock-Tunable, 8th Order Elliptic Lowpass Filter $f_{CLK}/f_C = 50:1$

MAXIMUM OUTPUT VOLTAGE OFFSET =  $\pm 5.5$ mV, DC LINEARITY =  $\pm 0.0063\%$ , T<sub>A</sub> =  $25^{\circ}$ C. THE PINS 6 TO 12 CONNECTION SHOULD BE UNDER THE IC AND SHIELDED BY AN ANALOG SYSTEM GROUND PLANE.

RC COMPENSATION BETWEEN PINS 11 AND 13 REQUIRED ONLY FOR  $f_{CUTOFF} \ge 60 \text{kHz}$ . The  $33 \mu F$  capacitor is a nonpolarized, aluminum electrolytic,  $\pm 20\%$ , 16V (NICHICON UUPIC 330MCRIGS OR NIC NACEN 33M16V  $6.3 \times 5.5$  Or Equivalent). \* PROTECTION DIODES, 1N4148 ARE OPTIONAL. SEE PIN DESCRIPTIONS.

1066-1 TA03

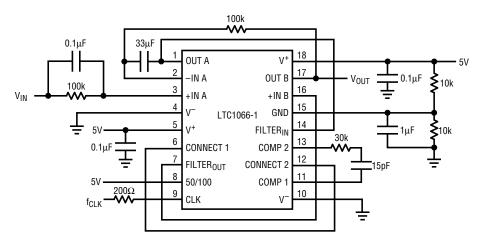

# Single 5V Supply Operation DC Accurate, 10Hz to 36kHz, Clock-Tunable, 8th Order Elliptic Lowpass Filter $f_{CLK}/f_C=50{:}1$

INPUT LINEAR RANGE = 1.4V to 3.6V. DC LINEARITY = ±0.0063%.

THE PINS 6 TO 12 CONNECTION SHOULD BE UNDER THE IC AND SHIELDED BY AN ANALOG SYSTEM GROUND PLANE.

RC COMPENSATION BETWEEN PINS 11 AND 13 REQUIRED ONLY FOR  $f_{CUTOFF} \ge 24 \text{kHz}$ . THE  $33 \mu F$  CAPACITOR IS A NONPOLARIZED, ALUMINUM ELECTROLYTIC,  $\pm 20\%$ , 16V (NICHICON UUPIC 330MCRIGS OR NIC NACEN 33M16V  $6.3 \times 5.5$ )

1066-1 TA04

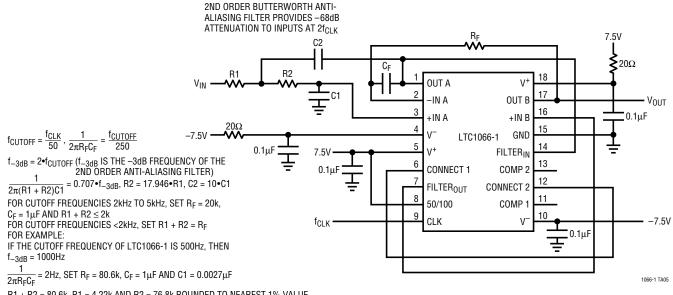

#### DC Accurate Lowpass Filter with Input Anti-Aliasing $(f_{CLK} \le 250kHz)$

$R1+R2=80.6k,\,R1=4.22k$  and R2=76.8k rounded to nearest 1% value. C2 =  $0.027\mu F$  rounded to nearest standard value.

**NOTE:** R<sub>F</sub> SHOULD BE ≤100k TO MINIMIZE DC OFFSET TO ±5.5mV

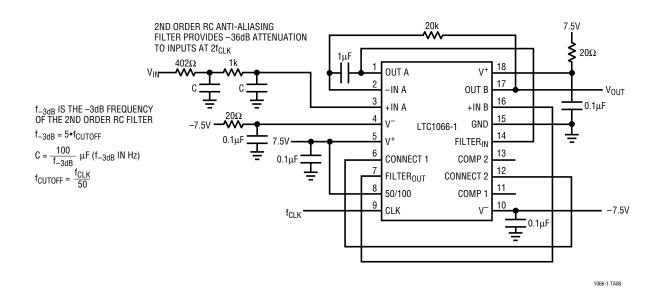

#### DC Accurate Lowpass Filter with Input Anti-Aliasing $(f_{CLK} > 250kHz)$

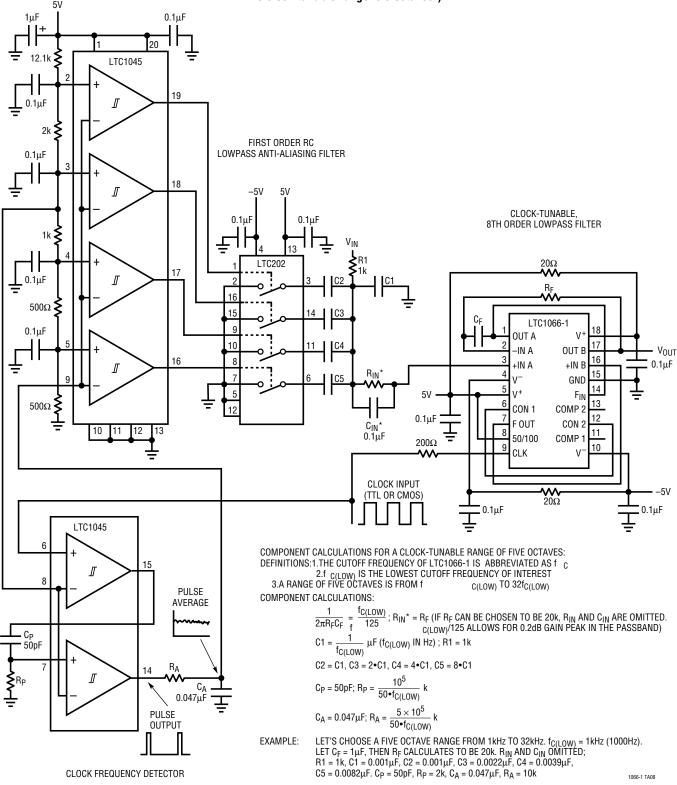

DC Accurate Clock-Tunable Lowpass Filter with Tunable Input Anti-Aliasing Filter (Circuit provides at least –20dB attenuation to input frequencies at 2f<sub>CLK</sub>.

The clock-tunable range is 5 octaves.)

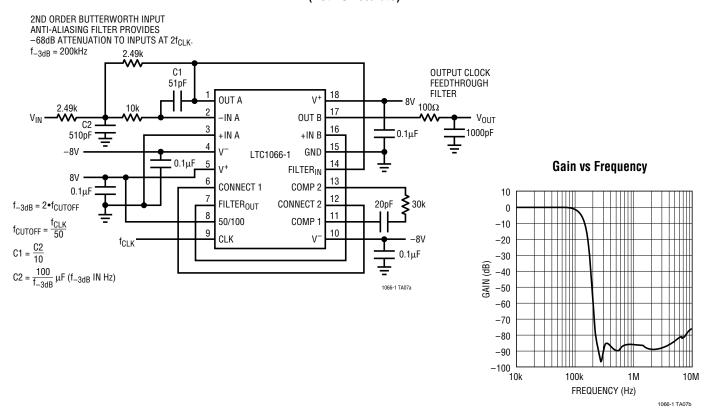

# 100kHz Elliptic Lowpass Filter with Input Anti-Aliasing and Output Clock Feedthrough Filters (Not DC Accurate)

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.006 INCH (0.15mm).