#### FEATURES

- Micropower 1.5μW (1 Sample/Second)

- Wide Supply Range 2.8V to 16V

- High Accuracy Guaranteed SET POINT Error ± 0.5mV Max. Guaranteed Deadband ± 0.1% of Value Max.

- Wide Input Voltage Range V<sup>+</sup> to Ground

- TTL Outputs with 5V Supply

- Two Independent Ground-Referred Control Inputs

- Small Size 8-Pin MiniDIP

#### **APPLICATIONS**

- Temperature Control (Thermostats)

- Motor Speed Control

- Battery Charger

- Any ON-OFF Control Loop

#### **BANG-BANG Controller**

#### DESCRIPTION

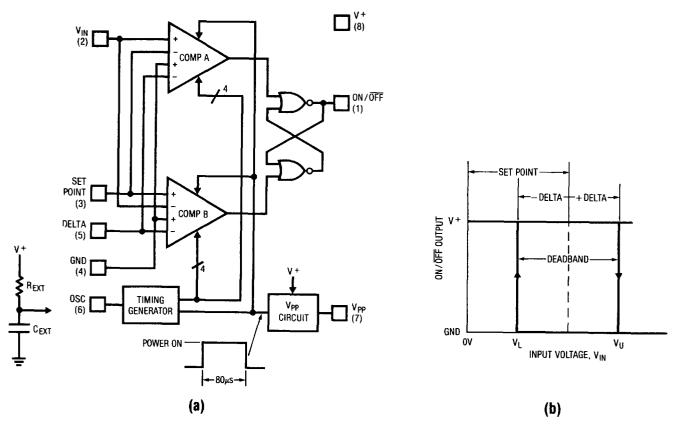

The LTC1041 is a monolithic CMOS BANG-BANG controller manufactured using Linear Technology's enhanced LTCMOS<sup>TM</sup> silicon gate process. BANG-BANG loops are characterized by turning the control element fully ON or fully OFF to regulate the average value of the parameter to be controlled. The SET POINT input determines the average control value and the DELTA input sets the deadband. The deadband is always 2 × DELTA and is centered around the SET POINT. Independent control of the SET POINT and deadband, with no interaction, is made possible by the unique sampling input structure of the LTC1041.

An external RC connected to the OSC pin sets the sampling rate. At the start of each sample, internal power to the analog section is switched on for  $\approx 80 \mu s$ . During this time the analog inputs are sampled and compared. After the comparison is complete, power is switched off. This achieves extremely low average power consumption at low sampling rates. CMOS logic holds the output continuously while consuming virtually no power.

To keep system power at an absolute minimum, a switched power output ( $V_{PP}$ ) is provided. External loads, such as bridge networks and resistive dividers, can be driven by this switched output.

The output logic sense (i.e.,  $ON = V^+$ ) can be reversed (i.e., ON = GND) by interchanging the  $V_{IN}$  and SET POINT inputs. This has no other effect on the operation of the LTC1041.

#### Ultra Low Power 50°F to 100°F (2.4 $\mu$ W) Thermostat

# 26VAC 2 WIRE THERMOSTAT 4.32k 4.99k 4.99k 5k 10M 1s 4.00n 400n 400n 49.9Ω ALL RESISTORS 1%. 1yellow Springs instrument co., inc. P/N 44007

DRIVING THERMISTOR WITH VPP ELIMINATES 3.8°F

ERROR DUE TO SELF-HEATING.

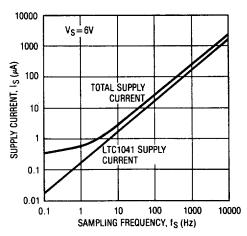

#### **Supply Current vs Sampling Frequency**

LTCMOS TM is a trademark of Linear Technology Corporation.

#### **ABSOLUTE MAXIMUM RATINGS**

####

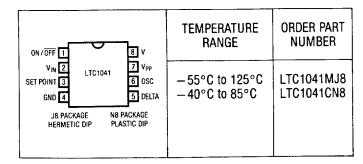

## PACKAGE/ORDER INFORMATION

#### **ELECTRICAL CHARACTERISTICS**

Test Conditions:  $V^+ = 5V$ ,  $T_{MIN} \le T_A \le T_{MAX}$  unless otherwise specified.

| SYMBOL              | PARAMETER                           | CONDITIONS                                                                                              |   | LTC1041M/LTC1041C<br>Min typ Max |           |        | UNITS          |

|---------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------|---|----------------------------------|-----------|--------|----------------|

|                     | SET POINT Error (Note 2)            | V+ = 2.8V to 6V (Note 1)                                                                                |   |                                  | ± 0.3     | ± 0.5  | mV             |

|                     | ,                                   | , ,                                                                                                     |   |                                  | +         | +      |                |

|                     |                                     |                                                                                                         |   |                                  | ±0.05     | ± 0.1  | % of DELTA     |

|                     |                                     | $V^{+} = 6V$ to 15V (Note 1)                                                                            | 1 |                                  | ±1        | ±3     | mV             |

|                     |                                     |                                                                                                         |   |                                  | +         | +      |                |

|                     |                                     |                                                                                                         |   |                                  | ± 0.05    | ±0.1   | % of DELTA     |

|                     | Deadband Error (Note 3)             | $V^{+} = 2.8V$ to 6V (Note 1)                                                                           |   |                                  | $\pm 0.6$ | ±1     | mV             |

|                     |                                     |                                                                                                         |   |                                  | +         | +      |                |

|                     |                                     |                                                                                                         |   |                                  | ± 0.1     | ±0.2   | % of DELTA     |

|                     |                                     | $V^{+} = 6V$ to 15V (Note 1)                                                                            |   |                                  | ± 2       | ±6     | mV             |

|                     |                                     |                                                                                                         | • |                                  | +         | +      | 04 4 8 5 1 7 4 |

|                     |                                     |                                                                                                         |   |                                  | ± 0.1     | ±0.2   | % of DELTA     |

| I <sub>OS</sub>     | Input Current                       | V <sup>+</sup> = 5V, T <sub>A</sub> = 25°C, OSC = GND<br>(V <sub>IN</sub> , SET POINT and DELTA Inputs) |   |                                  | ±0.3      |        | nA             |

| R <sub>IN</sub>     | Equivalent Input Resistance         | f <sub>S</sub> = 1kHz (Note 4)                                                                          | • | 10                               | 15        |        | MΩ             |

|                     | Input Voltage Range                 |                                                                                                         | • | GND                              |           | ٧+     | ٧              |

| PSR                 | Power Supply Range                  |                                                                                                         | • | 2.8                              |           | 16     | V              |

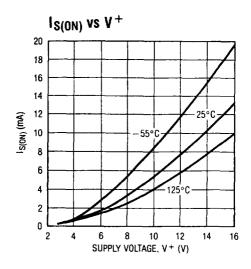

| I <sub>S(ON)</sub>  | Power Supply ON<br>Current (Note 5) | $V^+ = 5V$ , $V_{PP}$ $0N$                                                                              | • |                                  | 1.2       | 3      | mA             |

| I <sub>S(0FF)</sub> | Power Supply OFF                    | $V^+ = 5V$ , $V_{PP}$ OFF LTC1041C                                                                      | • |                                  | 0.001     | 0.5    | μА             |

|                     | Current (Noté 5)                    | LTC1041M                                                                                                |   |                                  | 0.001     | 5      | μΑ             |

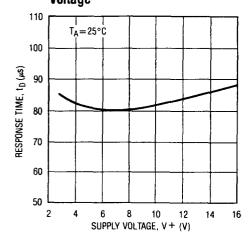

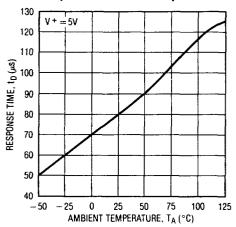

| t <sub>D</sub>      | Response Time (Note 6)              | V + = 5V                                                                                                |   | 60                               | 80        | 100    | μS             |

|                     | ON/OFF Output (Note 7)              |                                                                                                         |   |                                  |           |        |                |

| $V_{OH}$            | Logical "1" Output Voltage          | $V^{+} = 4.75V$ , $I_{OUT} = -360\mu A$                                                                 |   | 2.4                              | 4.4       |        | V              |

| V <sub>OL</sub>     | Logical "0" Output Voltage          | $V^+ = 4.75V$ , $I_{OUT} = 1.6mA$                                                                       |   |                                  | 0.25      | 0.4    | V              |

| R <sub>EXT</sub>    | External Timing Resistor            | Resistor Connected between V + and OSC Pin                                                              | • | 100                              |           | 10,000 | kΩ             |

| f <sub>S</sub>      | Sampling Frequency                  | $V^{+} = 5V$ , $T_{A} = 25^{\circ}C$ ,                                                                  |   |                                  | 5         |        | Hz             |

|                     |                                     | $R_{EXT} = 1M \hat{C}_{EXT} = 0.1 \mu F$                                                                |   |                                  |           |        |                |

The ● denotes the specifications which apply over the full operating temperature range. The shaded electrical specifications indicate those parameters which have been improved or guaranteed test limits provided for the first time.

**Note 1:** Applies over input voltage range limit and includes gain uncertainty.

Note 2: SET POINT error  $\equiv \left(\frac{V_U + V_L}{2}\right)$  - SET POINT where  $V_U =$  upper band limit and  $V_L =$  lower band limit.

Note 3: Deadband error  $\equiv$   $(V_U - V_L) - 2 \times DELTA$  where  $V_U = upper$  band limit and  $V_L = lower$  band limit.

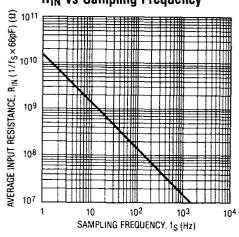

**Note 4:**  $R_{IN}$  is guaranteed by design and is not tested.  $R_{IN} = 1/(f_S \times 66pF)$ .

Note 5: Average supply current =  $t_D \times I_{S(0N)} \times f_S + (1 - t_D \times f_S) I_{S(0FF)}$ .

**Note 6:** Response time is set by an internal oscillator and is independent of overdrive voltage.  $t_D = V_{PP}$  pulse width.

**Note 7:** Output also capable of meeting EIA/JEDEC standard B series CMOS drive specifications.

#### TYPICAL PERFORMANCE CHARACTERISTICS

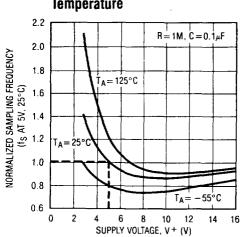

# Normalized Sampling Frequency vs V + , Temperature

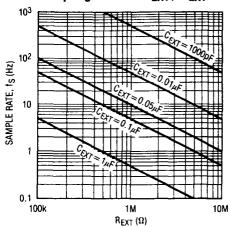

#### Sampling Rate vs R<sub>EXT</sub>, C<sub>EXT</sub>

# Response Time vs Supply Voltage

#### Response Time vs Temperature

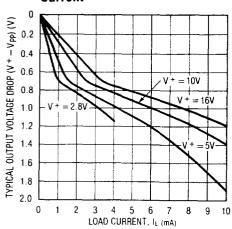

# **V<sub>PP</sub>** Output Voltage vs Load Current

#### **RIN** vs Sampling Frequency

#### **APPLICATIONS INFORMATION**

The LTC1041 uses sampled data techniques to achieve its unique characteristics. It consists of two comparators, each of which has two differential inputs (Figure 1). When the sum of the voltages on a comparator's inputs is positive, the output is high and when the sum is negative, the output is low. The inputs are interconnected such that the RS flip-flop is reset  $(ON/\overline{OFF} = GND)$  when  $V_{IN} > (SET\ POINT + DELTA)$  and is set  $(ON/\overline{OFF} = V^+)$  when  $V_{IN} < (SET\ POINT - DELTA)$ . This makes a very precise hysteresis loop of  $2 \times DELTA$  centered around the SET POINT. See Figure 1(b).

#### For Rs $< 10k\Omega$

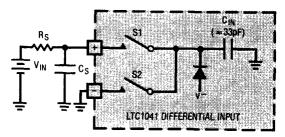

The dual differential input structure is made with CMOS switches and a precision capacitor array. Input impedance characteristics of the LTC1041 can be determined from the equivalent circuit shown in Figure 2. The input capacitance will charge with a time constant of Rs  $\times$  ClN . The ability to fully charge ClN from the signal source during the controller's active time is critical in determining errors caused by the input charging current. For source resistances less than  $10k\Omega$ , ClN fully charges and no error is caused by the charging current.

Figure 1. LTC1041 Block Diagram

Figure 2. Equivalent Input Circuit

#### APPLICATIONS INFORMATION

#### For R<sub>S</sub> $> 10k\Omega$

For source resistances greater than  $10k\Omega$ ,  $C_{IN}$  cannot fully charge, causing voltage errors. To minimize these errors, an input bypass capacitor,  $C_S$ , should be used. Charge is shared between  $C_{IN}$  and  $C_S$ , causing a small voltage error. The magnitude of this error is  $\Delta V = V_{IN} \times C_{IN} / (C_{IN} + C_S)$ . This error can be made arbitrarily small by increasing  $C_S$ .

The averaging effect of the bypass capacitor, Cs, causes another error term. Each time the input switches cycle between the plus and minus inputs, ClN is charged and discharged. The average input current due to this is  $I_{AVG} = V_{IN} \times C_{IN} \times f_S$ , where  $f_S$  is the sampling frequency. Because the input current is directly proportional to the differential input voltage, the LTC1041 can be said to have an average input resistance of  $R_{IN} = V_{IN} \, / \, I_{AVG} = I/(f_S \times C_{IN})$ .

Since two comparator inputs are connected in parallel,  $R_{IN}$  is one half of this value (see typical curve of  $R_{IN}$  versus  $f_S$ ). This finite input resistance causes an error due to the voltage divider between  $R_S$  and  $R_{IN}$ .

The input voltage error caused by both of these effects is  $V_{ERROR} = V_{IN} \left[ \frac{2C_{IN}}{(2C_{IN} + C_S)} + \frac{R_S}{(R_S + R_{IN})} \right]$ .

Example: assume  $f_S=10$ Hz,  $R_S=1$ M,  $C_S=1\mu$ F,  $V_{IN}=1$ V,  $V_{ERROR}=1$ V( $66\mu$ V+ $660\mu$ V)= $726\mu$ V. Notice that most of the error is caused by  $R_{IN}$ . If the sampling frequency is reduced to 1Hz, the voltage error from the input impedance effects is reduced to  $136\mu$ V.

#### **Input Voltage Range**

The input switches of the LTC1041 are capable of switching either to the  $V^+$  supply or ground. Consequently, the input voltage range includes both supply rails. This is a further benefit of the sampling input structure.

#### **Error Specifications**

The only measurable errors on the LTC1041 are the deviations from "ideal" of the upper and lower switching levels [Figure 1(b)]. From a control standpoint, the error

in the SET POINT and deadband is critical. These errors may be defined in terms of  $V_{U}$  and  $V_{L}$ .

SET POINT error

$$\equiv \left(\frac{V_U + V_L}{2}\right) - SET POINT$$

deadband error

$$\equiv (V_U - V_L) - 2 \times DELTA$$

The specified error limits (see electrical characteristics) include error due to offset, power supply variation, gain, time and temperature.

#### Pulsed Power (VPP) Output

It is often desirable to use the LTC1041 with resistive networks such as bridges and voltage dividers. The power consumed by these resistive networks can far exceed that of the LTC1041 itself.

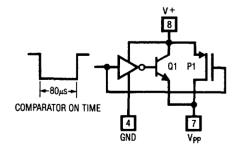

At low sample rates the LTC1041 spends most of its time off. A switched power output, Vpp, is provided to drive the input network, reducing its average power as well. Vpp is switched to V $^+$  during the controller's active time (  $\approx 80 \mu s$ ) and to a high impedance (open circuit) when internal power is switched off.

Figure 3 shows the VPP output circuit. The VPP output voltage is not precisely controlled when driving a load (see typical curve of VPP output voltage versus load current). In spite of this, high precision can be achieved in two ways: (1) driving ratiometric networks and (2) driving fast settling references.

Figure 3. VPP Output Switch

#### **APPLICATIONS INFORMATION**

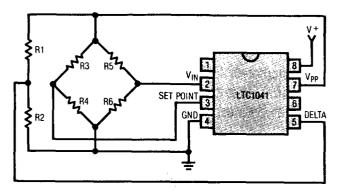

In ratiometric networks (Figure 4) all the inputs are proportional to Vpp. Consequently, the absolute value of Vpp does not affect accuracy.

Figure 4. Ratiometric Network Driven by Vpp

If the best possible performance is needed, the inputs to the LTC1041 must completely settle within  $4\mu$ s of the start of the comparison cycle (Vpp high impedance to V+ transition). Also, it is critical that the input voltages do not change during the  $80\mu$ s active time. When driving resistive input networks with Vpp, capacitive loading should be minimized to meet the  $4\mu$ s settling time requirement. Further, care should be exercised in layout when driving networks with source impedances, as seen by the LTC1041, of greater than  $10k\Omega$  (see For Rs  $> 10k\Omega$ ).

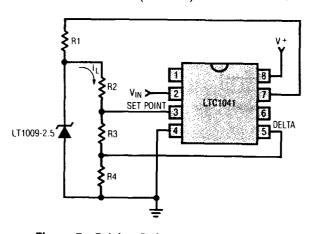

In applications where an absolute reference is required, the Vpp output can be used to drive a fast settling reference. The LTC1009 2.5V reference settles in  $\approx 2\mu s$  and is ideal for this application (Figure 5). The current through R1 must be large enough to supply the LT1009 minimum bias current ( $\approx$  1mA) and the load current. It.

Figure 5. Driving Reference with VPP Output

#### Internal Oscillator

An internal oscillator allows the LTC1041 to strobe itself. The frequency of the oscillation, and hence the sampling rate, is set with an external RC network (see typical curve, OSC frequency versus Rext, Cext). Rext and Cext are connected as shown in Figure 1. To assure oscillation, Rext must be between 100k $\Omega$  and 10M $\Omega$ . There is no limit to the size of Cext.

At low sampling rates,  $R_{EXT}$  is very important in determining the power consumption.  $R_{EXT}$  consumes power continuously. The average voltage at the OSC pin is approximately  $V^+/2$ , giving a power dissipation of  $P_{REXT} = (V^+/2)^2/R_{EXT}$ .

Example: assume  $R_{EXT} = 1M\Omega$ ,  $V^+ = 5V$ ,  $P_{REXT} = (2.5)^2 / 10^6 = 6.25 \mu W$ . This is approximately four times the power consumed by the LTC1041 at  $V^+ = 5V$  and  $f_S = 1$  sample / second. Where power is a premium,  $R_{EXT}$  should be made as large as possible. Note that the power dissipated by  $R_{EXT}$  is *not* a function of  $f_S$  or  $C_{EXT}$ .

If high sampling rates are needed and power consumption is of secondary importance, a convenient way to get the maximum possible sampling rate is to make  $R_{EXT}=100k\Omega$  and  $C_{EXT}=0$ . The sampling rate, set by the controller's active time, will nominally be  $\approx 10kHz$ .

To synchronize the sampling of the LTC1041 to an external frequency source, the OSC pin can be driven by a CMOS gate. A CMOS gate is necessary because the input trip points of the oscillator are close to the supply rails and TTL does not have enough output swing. Externally driven, there will be a delay from the rising edge of the OSC input and the start of the sampling cycle of approximately  $5\mu s$ .

## TYPICAL APPLICATIONS

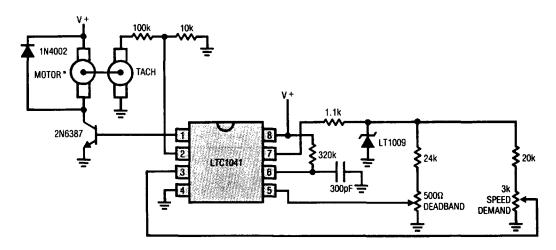

#### **Motor Speed Controller**

\*CANNON CKT26-T5-3SAE

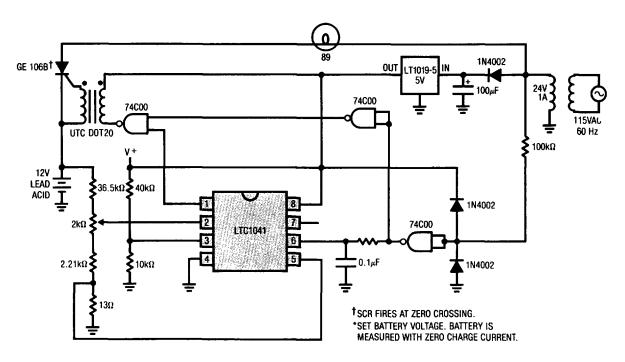

#### **Battery Charger**

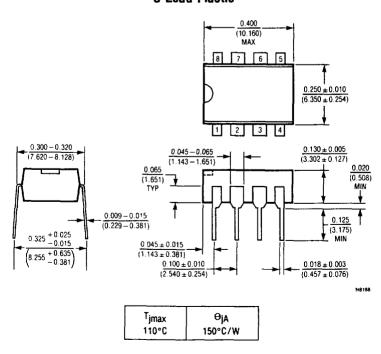

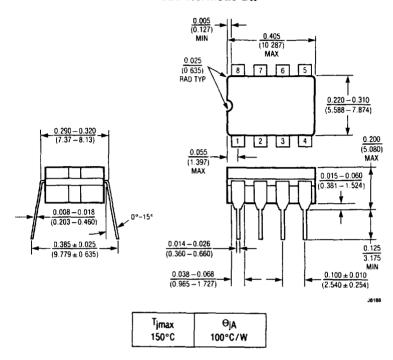

# PACKAGE DESCRIPTION Dimensions in inches (millimeters) unless otherwise noted.

J Package 8 Lead Hermetic DIP

N Package 8 Lead Plastic