# Hitachi Single-Chip Microcomputer H8S/2355 Series

# **HITACHI**

## **Notice**

When using this document, keep the following in mind:

- 1. This document may, wholly or partially, be subject to change without notice.

- 2. All rights are reserved: No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without Hitachi's permission.

- 3. Hitachi will not be held responsible for any damage to the user that may result from accidents or any other reasons during operation of the user's unit according to this document.

- 4. Circuitry and other examples described herein are meant merely to indicate the characteristics and performance of Hitachi's semiconductor products. Hitachi assumes no responsibility for any intellectual property claims or other problems that may result from applications based on the examples described herein.

- 5. No license is granted by implication or otherwise under any patents or other rights of any third party or Hitachi, Ltd.

- 6. MEDICAL APPLICATIONS: Hitachi's products are not authorized for use in MEDICAL APPLICATIONS without the written consent of the appropriate officer of Hitachi's sales company. Such use includes, but is not limited to, use in life support systems. Buyers of Hitachi's products are requested to notify the relevant Hitachi sales offices when planning to use the products in MEDICAL APPLICATIONS.

## **Preface**

Hitachi's H8S Series of single-chip microcomputers comprises new series which offer the high performance and low power consumption of the existing H8 Series, which is widely used for machine control, etc., together with significantly greater ease of use,

This initial series—the H8S/2000 Series—offers CPU object-level compatibility with the H8/300H Series, H8/300 Series, and H8/300L Series within the H8 Series.

| Series   | Features                                                                                                                                                       |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H8S/2000 | Upward-compatible with the H8/300H Series and H8/300 Series; twice the performance at the same frequency; multiply-and-accumulate instructions                 |

| H8/300H  | 16-Mbyte linear address space; upward-compatible with the H8/300 Series; concise instruction set; powerful word-size and longword-size arithmetic instructions |

| H8/300   | 64-kbyte address space; general register system; concise instruction set; powerful bit manipulation instructions                                               |

| H8/300L  | Same CPU as the H8/300 Series; consumer application oriented peripheral functions; low voltage, low power consumption                                          |

This document gives an outline of the H8S/2355 Series, which is suitable for single chip application in the H8S Series.

## **Intended Readership**

This Overview is intended for readers who require a basic understanding of microcomputers, or are looking for information on the features and functions of the H8S/2355 Series. Readers undertaking system design using these products, or requiring more detailed information on their use, should refer to the H8S/2355 Hardware Manual and H8S/2000 Series Programming Manual.

#### **Related Documents**

| Contents                                  | Document Title and No.                                           |

|-------------------------------------------|------------------------------------------------------------------|

| On H8S/2355 hardware                      | H8S/2355 Hardware Manual<br>ADE-602-112                          |

| On H8S/2000 Series execution instructions | H8S/2600 Series, H8S/2000 Series Programming Manual ADE-602-083A |

## Contents

| Section | on 1 H8S/2355 Series Features        | 6   |

|---------|--------------------------------------|-----|

| 1.1     | H8S/2355 Series Functions            | 6   |

| 1.2     | Pin Description                      | 10  |

| 1.3     | Block Diagram                        | 14  |

| Section | on 2 CPU                             | 15  |

| 2.1     | Features                             | 15  |

| 2.2     | Register Configuration               | 18  |

| 2.3     | Data Formats                         | 22  |

| 2.4     | Addressing Modes                     | 24  |

| 2.5     | Instruction Set                      | 26  |

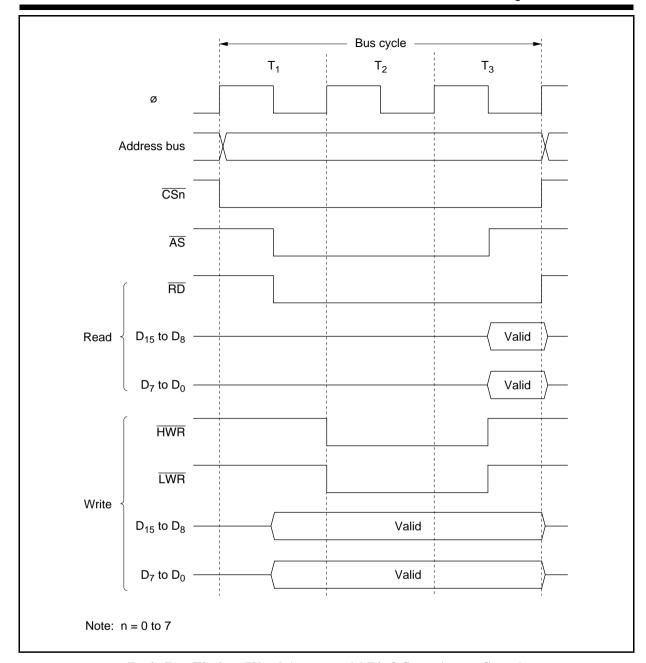

| 2.6     | Basic Bus Timing                     | 42  |

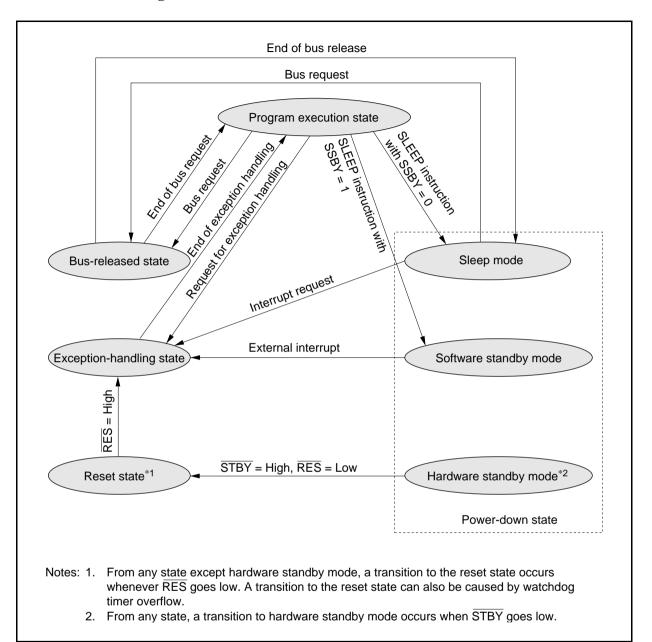

| 2.7     | Processing States                    | 46  |

| 2.8     | Exception Handling                   | 48  |

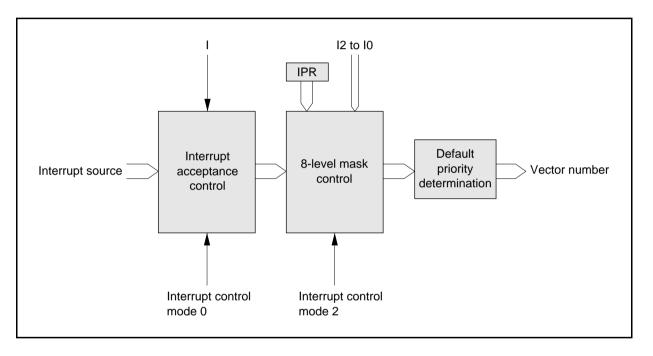

| 2.9     | Interrupts                           | 50  |

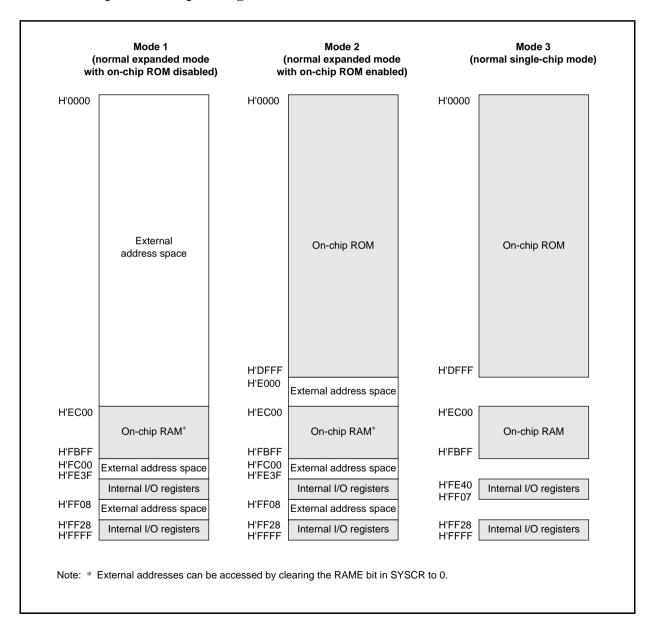

| 2.10    | Operating Modes                      | 54  |

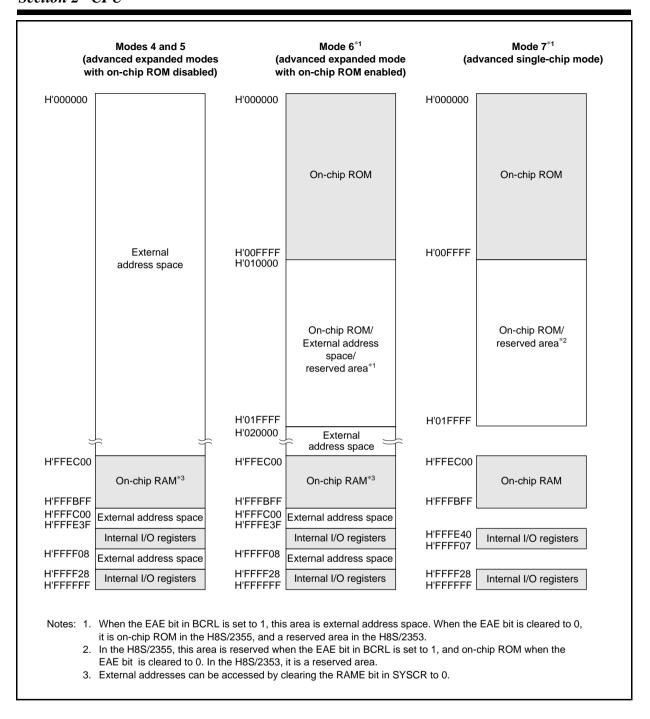

| 2.11    | Address Map                          | 56  |

| Section | on 3 Peripheral Functions            | 58  |

| 3.1     | Bus Controller (BSC)                 | 58  |

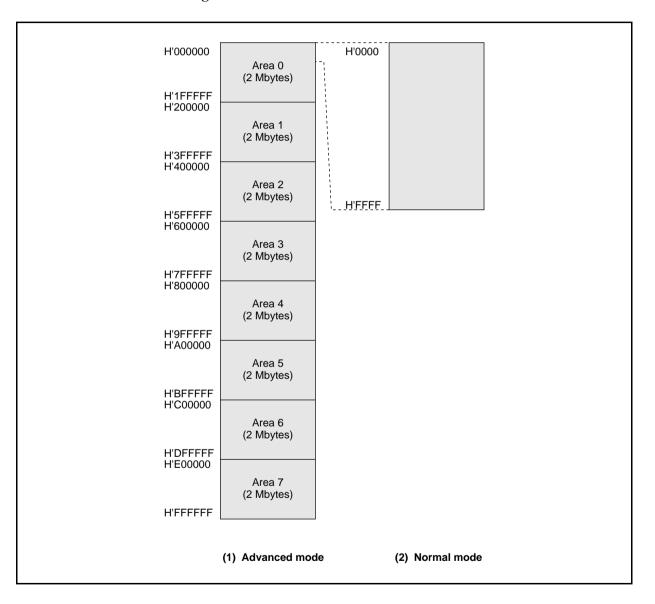

|         | 3.1.1 Area Partitioning              | 60  |

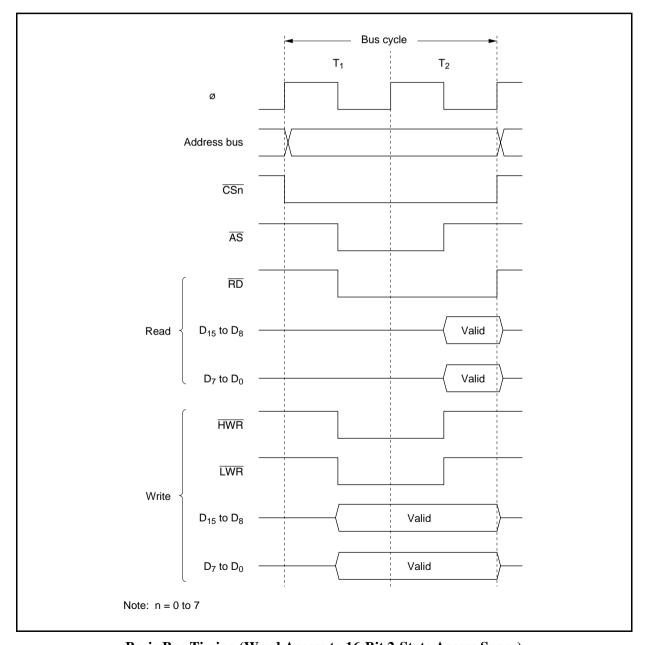

|         | 3.1.2 Basic Bus Interface            | 62  |

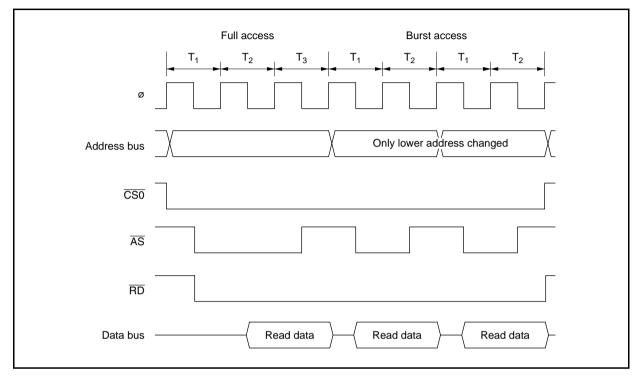

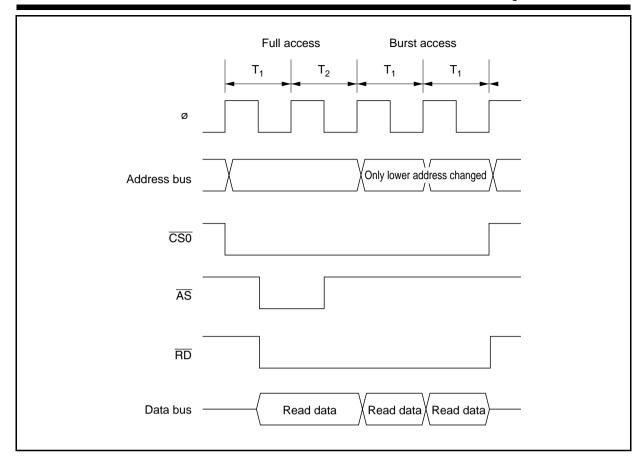

|         | 3.1.3 Burst ROM Interface            | 64  |

| 3.2     | Data Transfer Controller (DTC)       | 66  |

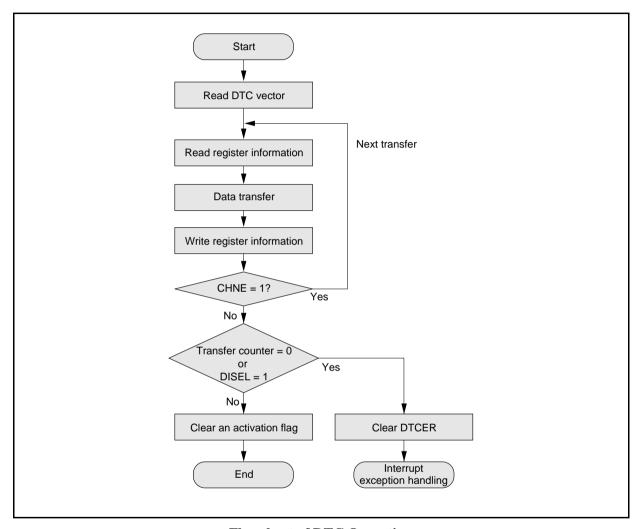

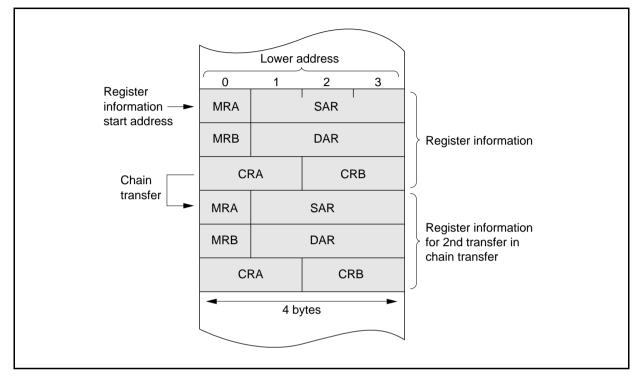

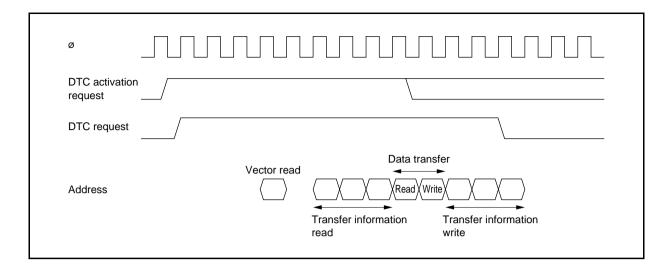

| J.2     | 3.2.1 Data Transfer Operation        | 68  |

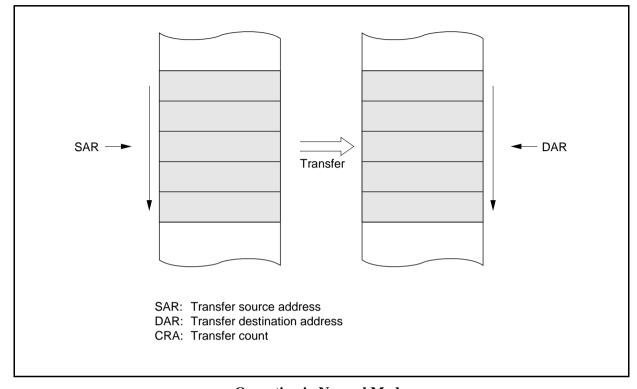

|         | 3.2.2 Transfer Modes                 | 72  |

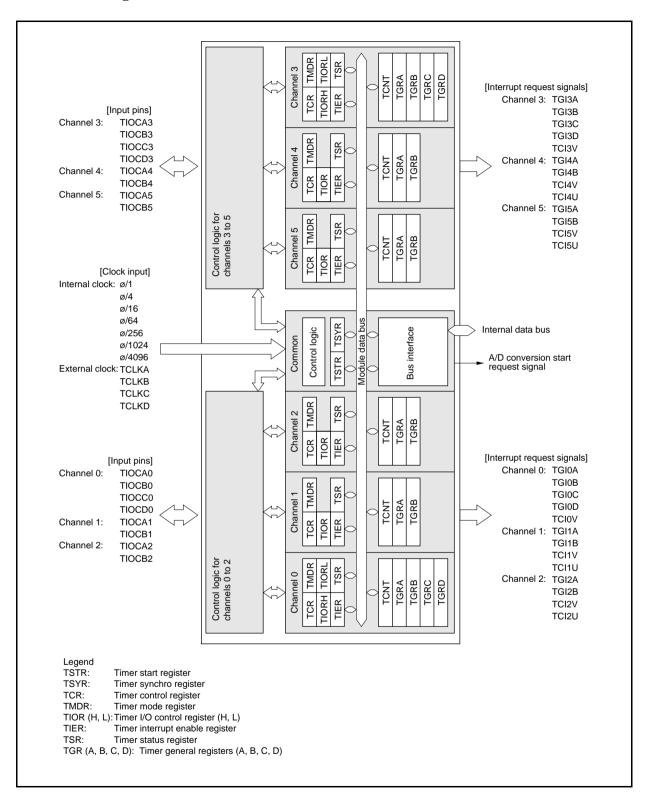

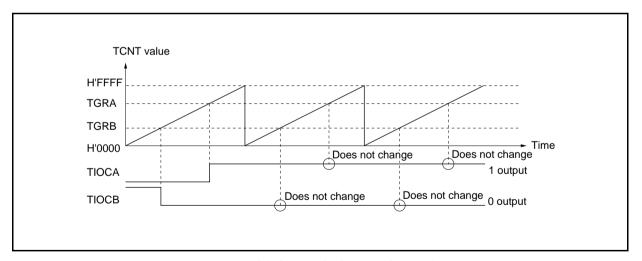

| 3.3     | 16-Bit Timer Pulse Unit (TPU)        | 76  |

| 3.4     | 8-Bit Timer                          | 88  |

| 3.5     | Watchdog Timer                       | 91  |

| 3.6     | Serial Communication Interface (SCI) | 95  |

|         | 3.6.1 SCI Asynchronous Mode          | 98  |

|         |                                      | 100 |

| 3.7     | Smart Card Interface                 |     |

| 3.8     | A/D Converter                        |     |

| 3.9     | D/A Converter                        |     |

| 3.10    | I/O Ports                            |     |

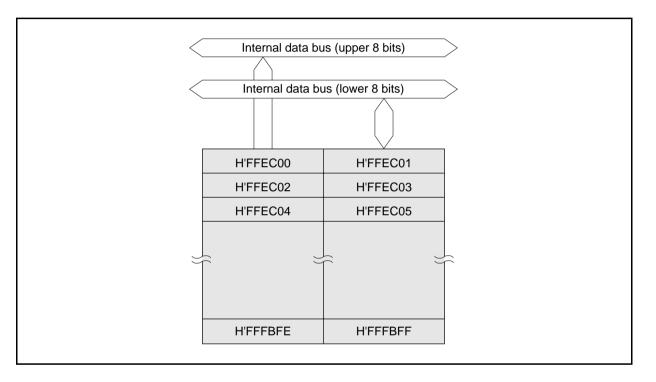

| 3.11    | RAM                                  |     |

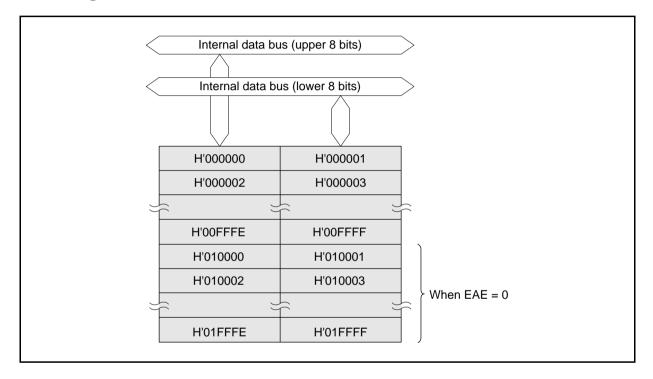

| 3.12    | ROM (PROM)                           |     |

| Section | on 4 Power-Down State                | 116 |

|         | Power Down State                     | 116 |

| Appendix |    |

|----------|----|

| D1       | 12 |

| Package. | 12 |

## Section 1 H8S/2355 Series Features

#### 1.1 H8S/2355 Series Functions

H8S/2355 Series microcomputers are designed for faster instruction execution, using a realtime control oriented CPU with an internal 32-bit architecture, and can run programs based on the C high-level language efficiently. As well as large-capacity ROM and RAM, these microcomputers include on-chip peripheral functions needed for control systems. These functions simplify the implementation of sophisticated, high-performance systems.

#### High-Performance H8S/2000 CPU

- General-register architecture

- Sixteen 16-bit general registers (also usable as sixteen 8-bit registers or eight 32-bit registers)

- High-speed operation suitable for realtime control

- 20 MHz maximum operating frequency (20 MHz oscillation frequency)

- High-speed arithmetic operations

8/16/32-bit register-register add/subtract: 50 ns  $16 \times 16$ -bit register-register multiply: 1000 ns  $32 \div 16$ -bit register-register divide: 1000 ns

- Instruction set suitable for high-speed operation

- Sixty-five basic instructions

- 8/16/32-bit move/arithmetic and logic instructions

- Unsigned/signed multiply and divide instructions

- Powerful bit-manipulation instructions

- Two CPU operating modes

- Normal mode: H8/300 Series compatible, maximum 64-kbyte address space

- Advanced mode: Maximum 16-Mbyte address space

#### **On-Chip Byte PROM (Mask ROM)**

• 64 kbytes or 128 kbytes

### **On-Chip High-Speed Static RAM**

• 2 kbytes or 4 kbytes

#### 6 HITACHI

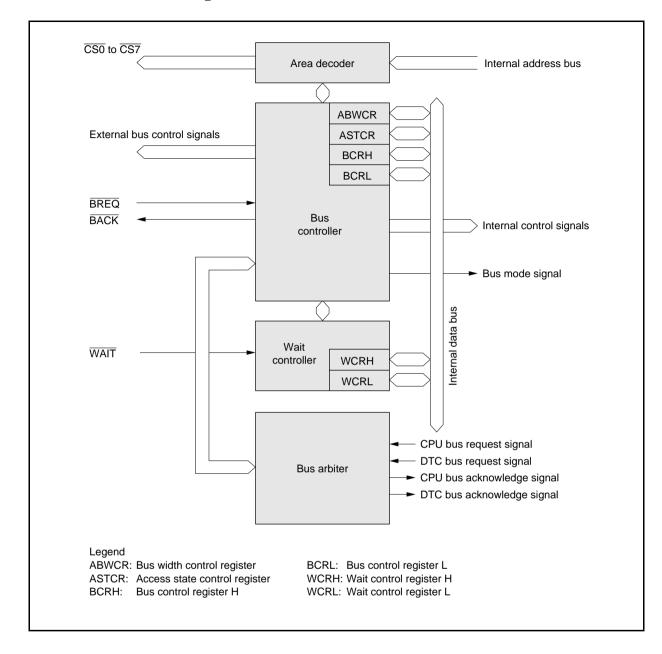

#### **On-Chip Bus Controller**

- Address space divided into 8 areas, with bus specifications settable independently for each area

- Chip select output possible for each area

- Selection of 8-bit or 16-bit access space for each area

- 2-state or 3-state access space can be designated for each area

- Number of program wait states can be set for each area

- Burst ROM directly connectable

- · External bus release function

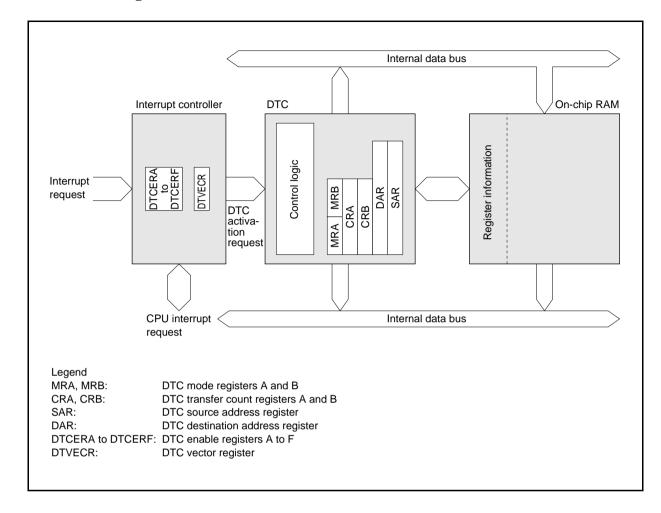

#### **Data Transfer Controller (DTC)**

- Activated by interrupt or software

- Multiple transfers or multiple types of transfer possible for one activation source

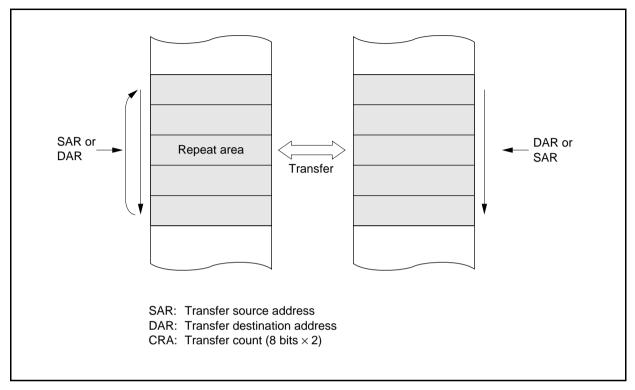

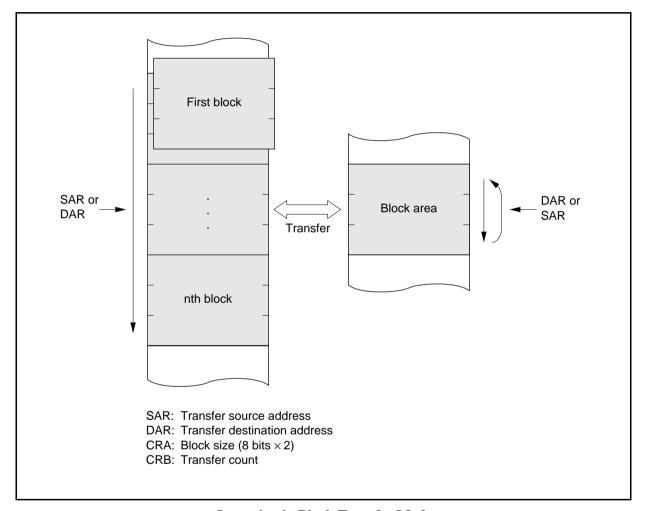

- Transfer possible in repeat mode, block transfer mode, etc.

- Request can be sent to CPU for interrupt that activated DTC

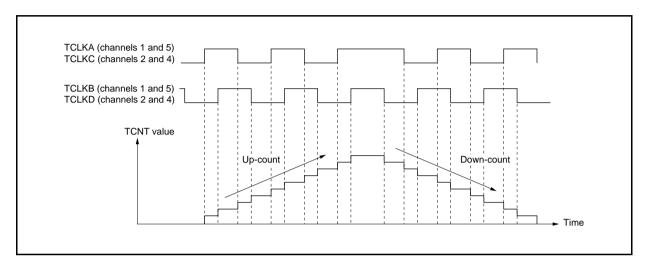

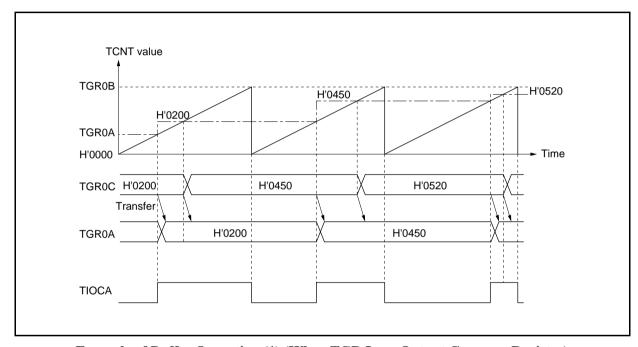

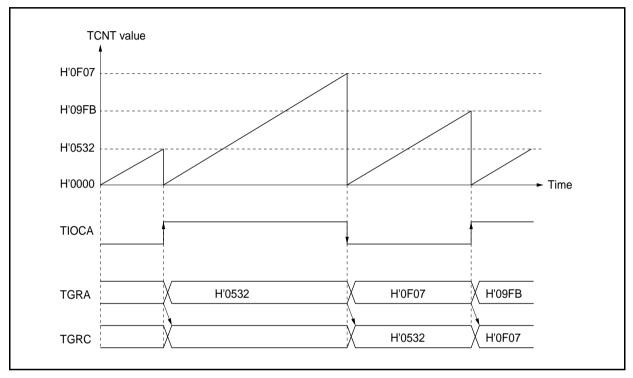

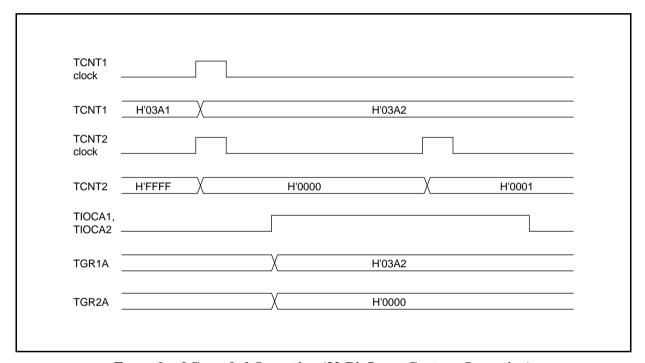

#### 16-Bit Timer-Pulse Unit (TPU)

- Six-channel 16-bit timer on-chip

- Pulse I/O processing capability for up to 16 pins'

- Automatic 2-phase encoder count capability

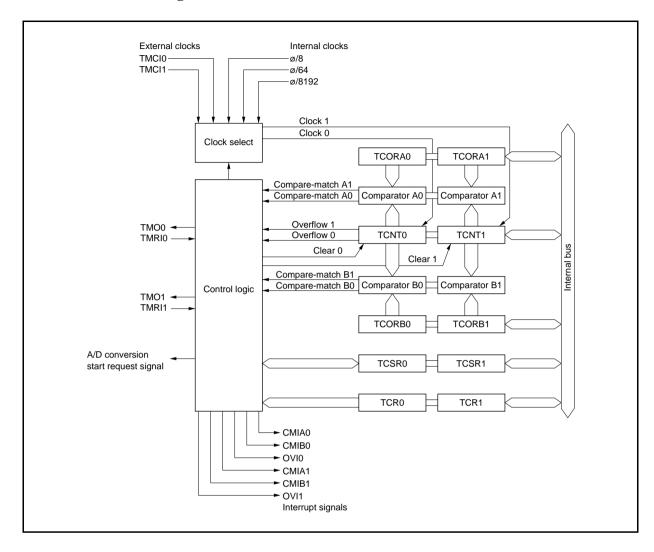

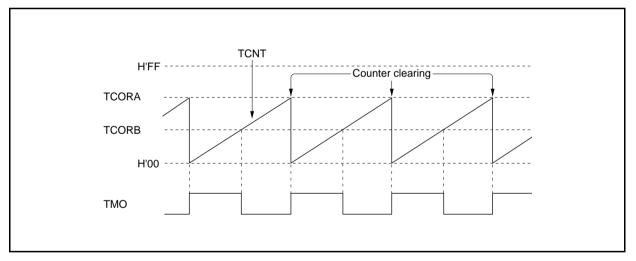

#### **Two On-Chip 8-Bit Timer Channels**

- 8-bit up-counter (external event count capability)

- Two time constant registers

- Two-channel connection possible

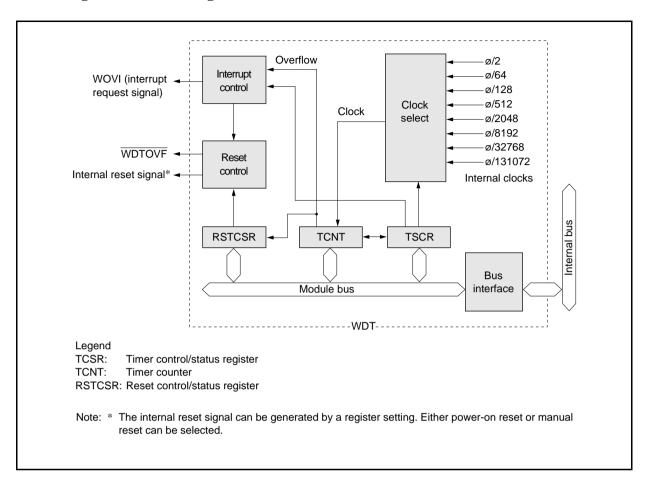

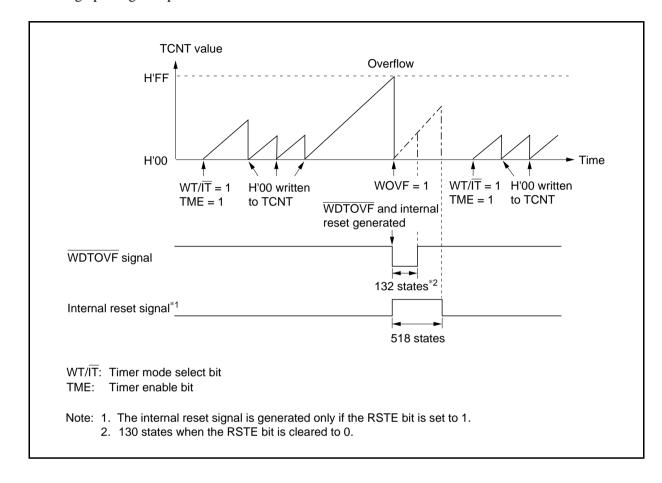

#### **On-Chip Watchdog Timer (WDT)**

• Watchdog timer or interval timer selectable

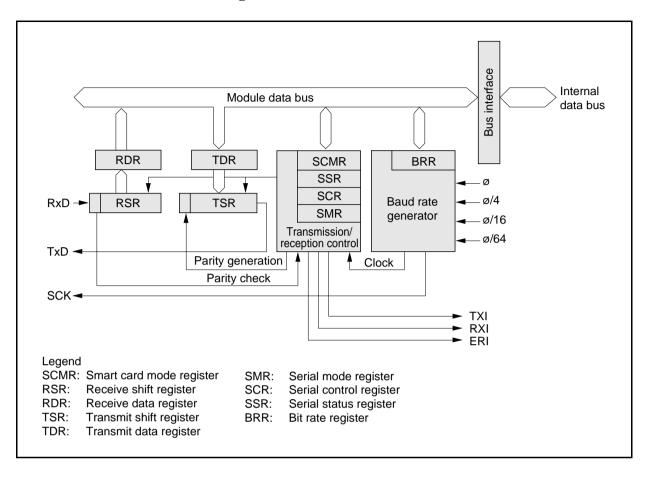

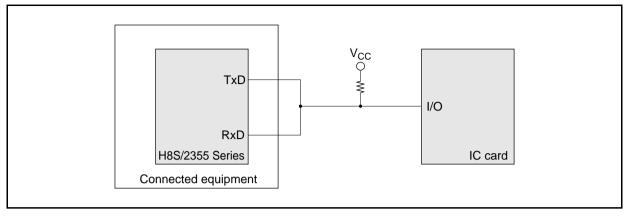

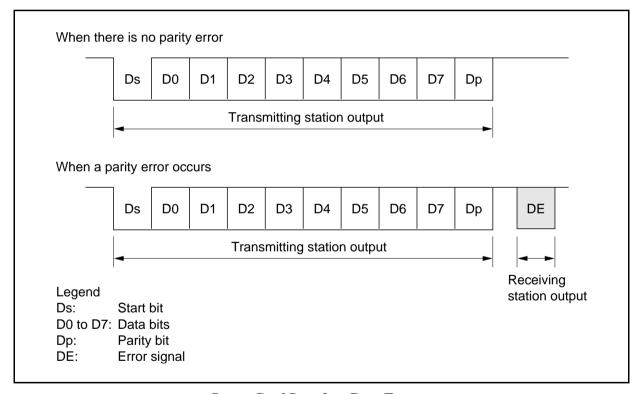

#### Three On-Chip Serial Communication Interface (SCI) Channels

- Asynchronous mode or synchronous mode selectable

- Multiprocessor communication function

- Smart card interface function

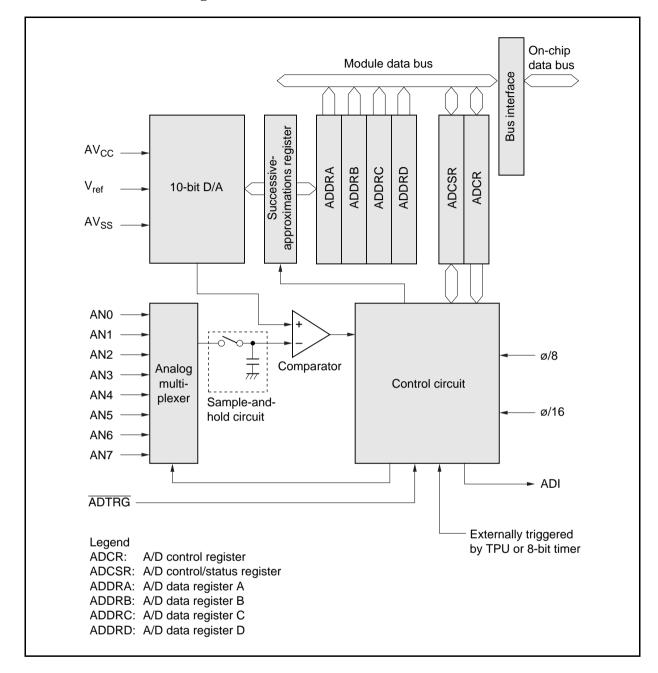

#### On-Chip A/D Converter

- Resolution: 10 bits

- Input: 8 channels

- High-speed conversion : 6.7 µs minimum conversion time (at 20 MHz operation)

- Single or scan mode selectable

- Sample and hold circuit

- A/D conversion can be activated by external trigger or timer trigger

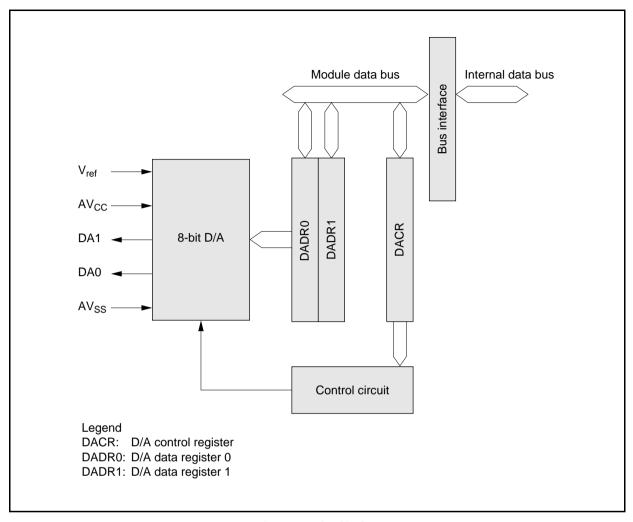

#### On-Chip D/A Converter

- Resolution: 8 bits

- Output: 2 channels

#### Thirteen I/O Ports

• 87 I/O pins, 8 input-only pins

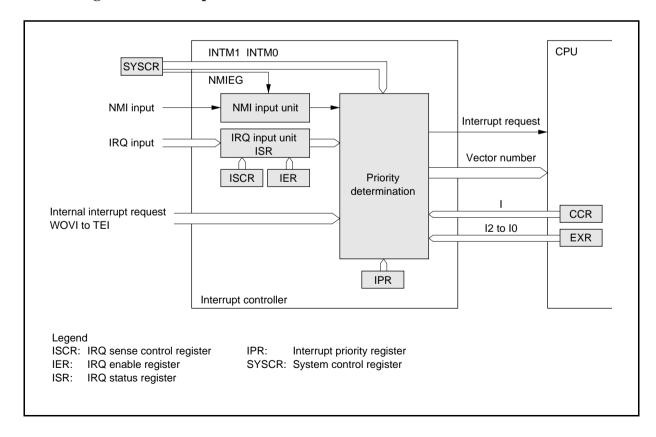

## **On-Chip Interrupt Controller**

- Nine external interrupt pins (NMI,  $\overline{IRQ0}$  to  $\overline{IRQ7}$ )

- 47 internal interrupt sources

- Selection of two interrupt control modes

#### **Power-Down State**

- Medium-speed mode

- Sleep mode

- Module stop mode

- Software standby mode

- Hardware standby mode

## **Seven MCU Operating Modes**

|      | CPU Operating |                                     |             | Exteri        | nal Data Bus  |

|------|---------------|-------------------------------------|-------------|---------------|---------------|

| Mode | Mode          | Description                         | On-Chip ROM | Initial Value | Maximum Value |

| 1    | Normal        | On-chip ROM disabled expansion mode | Disabled    | 8 bits        | 16 bits       |

| 2    | _             | On-chip ROM enabled expansion mode  | Enabled     | 8 bits        | 16 bits       |

| 3    | _             | Single-chip mode                    | Enabled     | _             |               |

| 4    | Advanced      | On-chip ROM disabled expansion mode | Disabled    | 16 bits       | 16 bits       |

| 5    | _             | On-chip ROM disabled expansion mode | Disabled    | 8 bits        | 16 bits       |

| 6    | _             | On-chip ROM enabled expansion mode  | Enabled     | 8 bits        | 16 bits       |

| 7    | _             | Single-chip mode                    | Enabled     | _             |               |

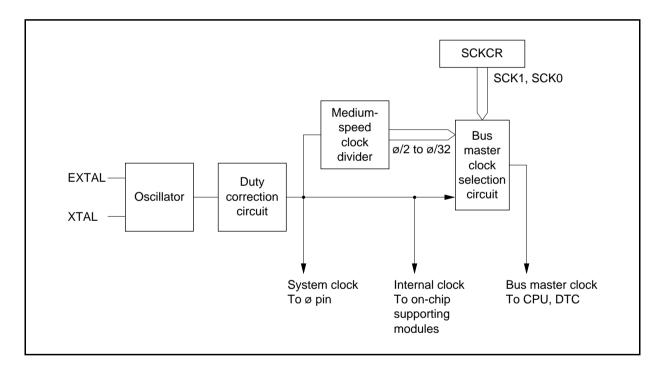

## **On-Chip Clock Pulse Generator (1:1 Oscillation)**

• Built-in duty correction circuit

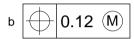

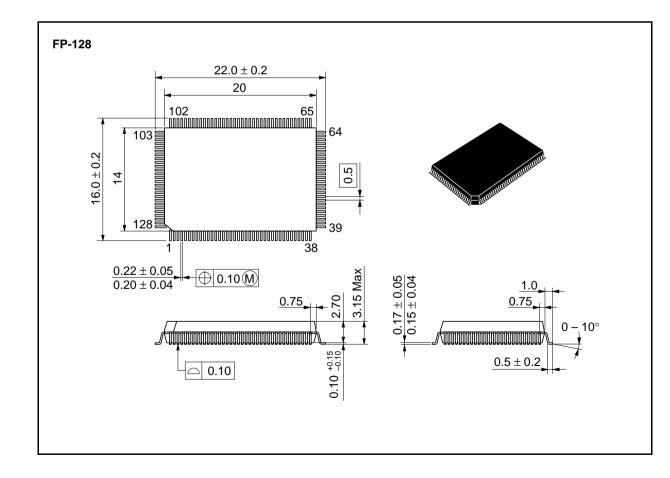

## **Packages**

- 120-pin plastic TQFP (TFP-120)

- 128-pin plastic QFP (FP-128)

## **Product Lineup**

#### Model

| Mask ROM<br>Version | ZTAT™<br>Version | ROM/RAM (Bytes) | Packages          |

|---------------------|------------------|-----------------|-------------------|

| HD6432355           | HD6472355        | 128 k/4 k       | TFP-120<br>FP-128 |

| HD6432353*          | _                | 64 k/2 k        | TFP-120<br>FP-128 |

Note: \* In the planning stage ZTAT™ is a trademark of Hitachi Ltd.

HITACHI 9

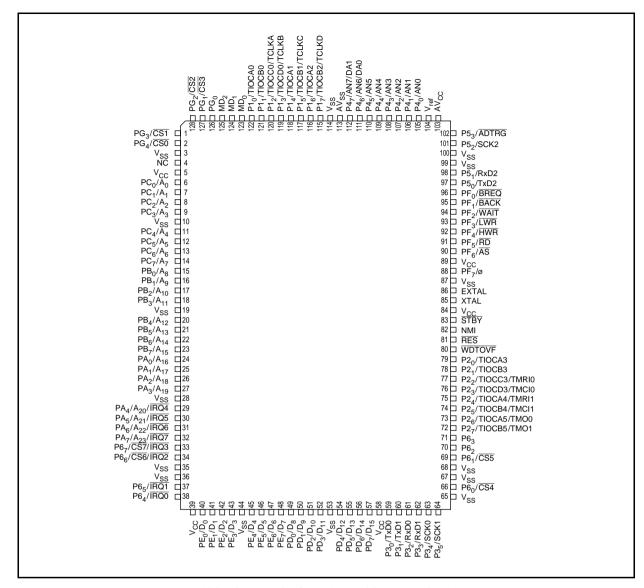

#### **Pin Description** 1.2

#### **Pin Arrangement**

```

120 PG4/CS0

110 PG4/CS0

1110 PG3/CS0

1110 PG3/CS0

1110 PG3/CS0

1111 PG4/CS0

1111 PG2/CCCA

1111 PG4/CS0

1111 PG2/CSCCA

1111 PG3/CSCCA

1111 PG3/CSCCA

1111 PG4/CS0

1111 PG3/CSCCA

1111 PG3/CSCCA

1111 PG3/CSCCA

1111 PG4/CS0

1111 PG3/CSCCA

1111 PG3

V_{CC}

PC<sub>0</sub>/A<sub>0</sub> PC<sub>1</sub>/A<sub>1</sub> PC<sub>1</sub> PC<sub></sub>

PC_2/A_2

PC<sub>3</sub>/A<sub>3</sub> □ V<sub>SS</sub> □

PC<sub>4</sub>/A<sub>4</sub>

PC_5/A_5

82 | PF<sub>6</sub>/AS

81 | V<sub>CC</sub>

80 | PF<sub>7</sub>/ø

PC<sub>6</sub>/A<sub>6</sub>

PC<sub>7</sub>/A<sub>7</sub>

PB<sub>0</sub>/A<sub>8</sub> □ 11

79 | V<sub>SS</sub>

78 | EXTAL

77 | XTAL

76 | V<sub>CC</sub>

75 | STBY

PB<sub>1</sub>/A<sub>9</sub> □ 12

V<sub>SS</sub> □ 15

74 | NMI

73 | RES

PB<sub>6</sub>/A<sub>14</sub> □

72 WDTOVF

71 P2<sub>0</sub>/TIOCA3

70 P2<sub>1</sub>/TIOCB3

69 P22/TIOCC3/TMRI0

68

P23/TIOCD3/TMCI0

V<sub>SS</sub> 24

67 P24/TIOCA4/TMRI1

PA<sub>4</sub>/A<sub>20</sub>/<del>IRQ4</del> 25

66 P2<sub>5</sub>/TIOCB4/TMCI1

65 P2<sub>6</sub>/TIOCA5/TMO0

PA<sub>6</sub>/A<sub>22</sub>/<del>IRQ6</del> □ 27

64 P2<sub>7</sub>/TIOCB5/TMO1

63 P6<sub>3</sub>

62 P6<sub>2</sub>

PA<sub>7</sub>/A<sub>23</sub>/IRQ7 □

P6<sub>7</sub>/CS7/IRQ3 □

P6<sub>6</sub>/CS6/IRQ2 □ 30

P6<sub>1</sub>/CS5

```

120-Pin Plastic TQFP (TFP-120: Top View)

128-Pin Plastic QFP (FP-128: Top View)

## **Pin Functions**

| Туре                   | Symbol                             | I/O    | Name and Function                                                                     |  |  |  |  |  |  |

|------------------------|------------------------------------|--------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Power                  | $V_{CC}$                           | Input  | Power supply                                                                          |  |  |  |  |  |  |

|                        | $V_{SS}$                           | Input  | Ground: All $V_{SS}$ pins should be connected to the system power supply (0 V).       |  |  |  |  |  |  |

| Clock                  | XTAL                               | Input  | Connects to a crystal oscillator.                                                     |  |  |  |  |  |  |

|                        | EXTAL                              | Input  | Connects to a crystal oscillator, or external clock input.                            |  |  |  |  |  |  |

|                        | Ø                                  | Output | System clock                                                                          |  |  |  |  |  |  |

| Operating mode control | $\mathrm{MD}_2$ to $\mathrm{MD}_0$ | Input  | Mode pins                                                                             |  |  |  |  |  |  |

| System control         | RES                                | Input  | Reset input                                                                           |  |  |  |  |  |  |

|                        | STBY                               | Input  | Standby                                                                               |  |  |  |  |  |  |

|                        | BREQ                               | Input  | Bus request                                                                           |  |  |  |  |  |  |

|                        | BACK                               | Output | Bus request acknowledge                                                               |  |  |  |  |  |  |

| Interrupts             | NMI                                | Input  | Nonmaskable interrupt                                                                 |  |  |  |  |  |  |

|                        | IRQ7 to IRQ0                       | Input  | Interrupt request 7 to 0                                                              |  |  |  |  |  |  |

| Address bus            | A <sub>23</sub> to A <sub>0</sub>  | Output | Address bus                                                                           |  |  |  |  |  |  |

| Data bus               | D <sub>15</sub> to D <sub>0</sub>  | I/O    | Data bus                                                                              |  |  |  |  |  |  |

| Bus control            | CS7 to CS0                         | Output | Chip select/low address strobe (CS5 to CS2)                                           |  |  |  |  |  |  |

|                        | ĀS                                 | Output | Address strobe                                                                        |  |  |  |  |  |  |

|                        | RD                                 | Output | Read                                                                                  |  |  |  |  |  |  |

|                        | HWR                                | Output | High write/write enable                                                               |  |  |  |  |  |  |

|                        | LWR                                | Output | Low write                                                                             |  |  |  |  |  |  |

|                        | WAIT                               | Input  | Wait                                                                                  |  |  |  |  |  |  |

| 16-bit timer-pulse     | TCLKA to TCLKD                     | Input  | Clock input A to D                                                                    |  |  |  |  |  |  |

| unit (TPU)             | TIOCA0, TIOCB0,<br>TIOCC0, TIOCD0  | I/O    | Input capture/output compare match A0 to D0                                           |  |  |  |  |  |  |

|                        | TIOCA1, TIOCB1                     | I/O    | Input capture/output compare match A1 and B1                                          |  |  |  |  |  |  |

|                        | TIOCA2, TIOCB2                     | I/O    | Input capture/output compare match A2 and B2                                          |  |  |  |  |  |  |

|                        | TIOCA3, TIOCB3,<br>TIOCC3, TIOCD3  | I/O    | Input capture/output compare match A3 to D3                                           |  |  |  |  |  |  |

|                        | TIOCA4, TIOCB4                     | I/O    | Input capture/output compare match A4 and B4                                          |  |  |  |  |  |  |

|                        | TIOCA5, TIOCB5                     | I/O    | Input capture/output compare match A5 and B5                                          |  |  |  |  |  |  |

| 8-bit timer            | TMO0, TMO1                         | Output | Compare match output: The compare match output pins.                                  |  |  |  |  |  |  |

|                        | TMCI0, TMCI1                       | Input  | Counter external clock input: Input pins for the external clock input to the counter. |  |  |  |  |  |  |

|                        | TMRI0, TMRI1                       | Input  | Counter external reset input: The counter reset input pins.                           |  |  |  |  |  |  |

| Watchdog timer (WDT)   | WDTOVF                             | Output | Watchdog timer overflows                                                              |  |  |  |  |  |  |

| Serial communication                 | TxD2, TxD1,<br>TxD0                | Output | Transmit data (channel 2, 1, 0)                                                  |

|--------------------------------------|------------------------------------|--------|----------------------------------------------------------------------------------|

| interface (SCI) Smart Card interface | RxD2, RxD1,<br>RxD0                | Input  | Receive data (channel 2, 1, 0)                                                   |

|                                      | SCK2, SCK1,<br>SCK0                | I/O    | Serial clock (channel 2, 1, 0)                                                   |

| A/D converter                        | AN7 to AN0                         | Input  | Analog input                                                                     |

|                                      | ADTRG                              | Input  | A/D conversion external trigger input                                            |

| D/A converter                        | DA1, DA0                           | Output | Analog output                                                                    |

| A/D converter and D/A converters     | AV <sub>CC</sub>                   | Input  | This is the power supply pin for the A/D converter and D/A converter.            |

|                                      | AV <sub>SS</sub>                   | Input  | This is the ground pin for the A/D converter and D/A converter.                  |

|                                      | V <sub>ref</sub> Input             |        | This is the reference voltage input pin for the A/D converter and D/A converter. |

| I/O ports                            | P1 <sub>7</sub> to P1 <sub>0</sub> | I/O    | Port 1                                                                           |

|                                      | P2 <sub>7</sub> to P2 <sub>0</sub> | I/O    | Port 2                                                                           |

|                                      | P3 <sub>5</sub> to P3 <sub>0</sub> | I/O    | Port 3                                                                           |

|                                      | P4 <sub>7</sub> to P4 <sub>0</sub> | Input  | Port 4                                                                           |

|                                      | P5 <sub>3</sub> to P5 <sub>0</sub> | I/O    | Port 5                                                                           |

|                                      | P6 <sub>7</sub> to P6 <sub>0</sub> | I/O    | Port 6                                                                           |

|                                      | PA <sub>7</sub> to PA <sub>0</sub> | I/O    | Port A                                                                           |

|                                      | PB <sub>7</sub> to PB <sub>0</sub> | I/O    | Port B                                                                           |

|                                      | PC <sub>7</sub> to PC <sub>0</sub> | I/O    | Port C                                                                           |

|                                      | PD <sub>7</sub> to PD <sub>0</sub> | I/O    | Port D                                                                           |

|                                      | PE <sub>7</sub> to PE <sub>0</sub> | I/O    | Port E                                                                           |

|                                      | PF <sub>7</sub> to PF <sub>0</sub> | I/O    | Port F                                                                           |

|                                      | PG <sub>4</sub> to PG <sub>0</sub> | I/O    | Port G                                                                           |

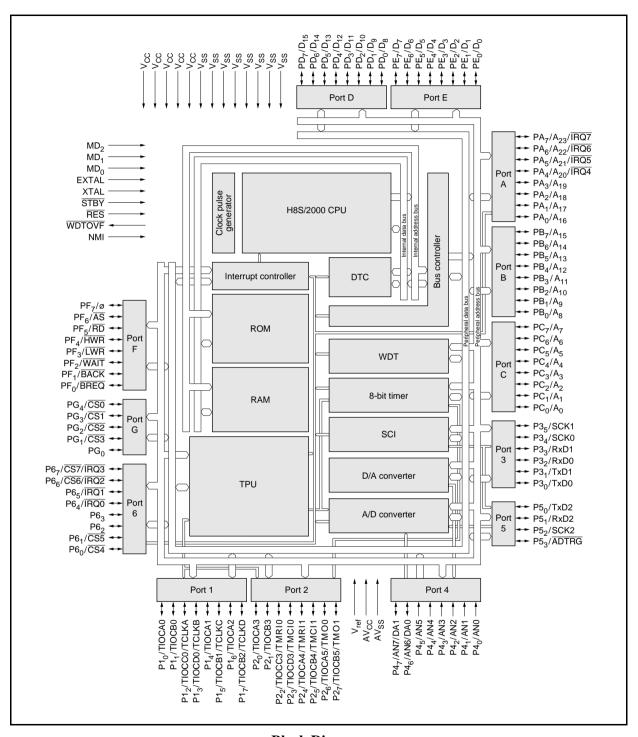

## 1.3 Block Diagram

**Block Diagram**

## Section 2 CPU

#### 2.1 Features

The H8S/2000 CPU is a high-speed central processing unit with an internal 32-bit architecture, and is upward compatible with the H8/300 and H8/300H CPUs.

The H8S/2000 CPU has sixteen 16-bit general registers, can address a 16-Mbyte (architecturally 4-Gbyte) linear access space, and is ideal for realtime control.

#### **Feature**

- Upward-compatible with H8/300 and H8/300H CPUs

- Can execute H8/300 and H8/300H object programs

- General-register architecture

- Sixteen 16-bit general registers (also usable as sixteen 8-bit registers or eight 32-bit registers)

- Sixty-five basic instructions

- 8/16/32-bit arithmetic and logic instructions

- Multiply and divide instructions

- Powerful bit-manipulation instructions

- Eight addressing modes

- Register direct (Rn)

- Register indirect (@ERn)

- Register indirect with displacement (@(d:16,ERn) or @(d:32,ERn))

- Register indirect with post-increment or pre-decrement (@ERn+ or @-ERn)

- Absolute address (@aa:8, @aa:16, @aa:24, or @aa:32)

- Immediate (#xx:8, #xx:16, or #xx:32)

- Program-counter relative (@(d:8,PC) or @(d:16,PC))

- Memory indirect (@@aa:8)

- 16-Mbyte address space

- Program: 16 Mbytes

- Data: 16 Mbytes (4 Gbytes architecturally)

- · High-speed operation

- All frequently-used instructions execute in one or two states

— Maximum clock frequency: 20 MHz

— 8/16/32-bit register-register add/subtract: 50 ns

—  $8 \times 8$ -bit register-register multiply: 600 ns

—  $16 \div 8$ -bit register-register divide: 600 ns

—  $16 \times 16$ -bit register-register multiply: 1000 ns

$-32 \div 16$ -bit register-register divide: 1000 ns

- Two CPU operating modes

- Normal mode/advanced mode

- Low-power state

- Transition to power-down state by SLEEP instruction

- CPU clock speed selectable

#### Differences between the H8S/2600 CPU and the H8S/2000 CPU

- Register configuration

- The MAC register is supported only by the H8S/2600 CPU.

- · Basic instructions

- The MAC, CLRMAC, LDMAC, and STMAC instructions are supported only by the H8S/2600 CPU.

- Number of states required for execution

- The number of states required for execution of the MULXU and MULXS instructions

#### Differences from H8/300 CPU

In comparison with the H8/300 CPU, the H8S/2000 CPU has the following enhancements.

- More general registers and control registers

- Eight 16-bit registers and one 8-bit control registers added

- Expanded address space

- Normal mode supports the same 64-kbyte address space as the H8/300 CPU

- Advanced mode supports a maximum 16-Mbyte address space

- Enhanced addressing

- For effective use of the 16-Mbyte address space

- · Enhanced instructions

- Addressing modes of bit-manipulation instructions enhanced

- Signed multiply and divide instructions added

- Two-bit shift instructions added

- Instructions for saving and restoring multiple registers added

- Test-and-set instruction added

- · Higher speed

- Basic instructions execute twice as fast

#### Differences from H8/300H CPU

In comparison with the H8/300H CPU, the H8S/2000 CPU has the following enhancements.

- · Additional control register

- One 8-bit control register added

- Enhanced instructions

- Addressing modes of bit-manipulation instructions enhanced

- Two-bit shift instructions added

- Instructions for saving and restoring multiple registers added

- Test-and-set instruction added

- · Higher speed

- Basic instructions execute twice as fast

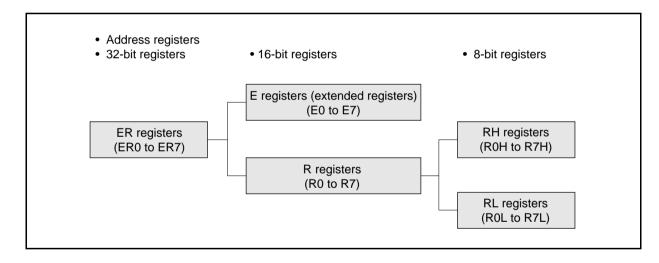

## 2.2 Register Configuration

The H8S/2000 CPU has general registers and control registers.

The eight 32-bit general registers all have identical functions and can be used as either address registers or data registers. The control registers are the 24-bit program counter (PC), 8-bit extend register (EXR), and 8-bit condition code register (CCR).

## **CPU Internal Register Configuration**

| 15       |    | 0 | 7        | 0 7 0                             |

|----------|----|---|----------|-----------------------------------|

| ER0      | E0 |   | R0H      | R0L                               |

| ER1      | E1 |   | R1H      | R1L                               |

| ER2      | E2 |   | R2H      | R2L                               |

| ER3      | E3 |   | R3H      | R3L                               |

| ER4      | E4 |   | R4H      | R4L                               |

| ER5      | E5 |   | R5H      | R5L                               |

| ER6      | E6 |   | R6H      | R6L                               |

| ER7 (SP) | E7 |   | R7H      | R7L                               |

|          |    |   | PC<br>EX | 7 6 5 4 3 2 1 0<br>R T - 12 11 10 |

|          |    |   | EX       |                                   |

#### **General Registers**

The CPU has eight 32-bit general registers. These general registers are all functionally alike and can be used as either address registers or data registers.

When a general register is used as a data register, it can be accessed as a 32-bit, 16-bit, or 8-bit register.

When the general registers are used as 32-bit registers or address registers, they are designated by the letters ER (ER0 to ER7).

The ER registers divide into 16-bit general registers designated by the letters E (E0 to E7) and R (R0 to R7). These registers are functionally equivalent, providing a maximum sixteen 16-bit registers. The E registers (E0 to E7) are also referred to as extended registers.

The R registers divide into 8-bit general registers designated by the letters RH (R0H to R7H) and RL (R0L to R7L). These registers are functionally equivalent, providing a maximum sixteen 8-bit registers.

The figure below illustrates the usage of the general registers. The usage of each register can be selected independently.

## **Usage of General Registers**

## **Control Registers**

The control registers are the 24-bit program counter (PC), 8-bit extend register (EXR), and 8-bit condition code register (CCR).

**Program Counter (PC):** This 24-bit counter indicates the address of the next instruction the CPU will execute. The length of all CPU instructions is 2 bytes (one word) or a multiple of 2 bytes, so the least significant PC bit is ignored. When an instruction is fetched, the least significant PC bit is regarded as 0.

**Extend Register (EXR):** This 8-bit register comprises a trace bit (T) and interrupt mask bits (I2 to I0).

• Bit 7—Trace Bit (T)

Specifies whether or not trace mode is set. When this bit is cleared to 0, instructions are executed sequentially. When set to 1, trace exception handling is started each time an instruction is executed.

- Bits 6 to 3—Reserved

- Bits 2 to 0—Interrupt Mask Bits (I2 to I0)

These bits specify the interrupt request mask level (0 to 7). See section 2.9, Interrupts, for details.

EXR can be manipulated by the LDC, STC, ANDC, ORC, and XORC instructions. Except in the case of STC, interrupts (including NMI) are not accepted for 3 states after the instruction is executed.

**Condition Code Register (CCR):** This 8-bit register contains internal CPU status information, including the interrupt mask bit (I), and the half-carry (H), negative (N), zero (Z), overflow (V), and carry (C) flags.

• Bit 7—Interrupt Mask Bit (I)

Masks interrupts other than NMI when set to 1. NMI is accepted regardless of the I bit setting. The I bit is set to 1 at the start of an exception-handling sequence. See section 2.9, Interrupts for details.

• Bit 6—User Bit or Interrupt Mask Bit (UI)

Can be written or read by software using the LDC, STC, ANDC, ORC, and XORC instructions. In this IC, this bit cannot be used as an interrupt mask.

• Bit 5—Half-Carry Flag (H)

When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or NEG.B instruction is executed, this flag is set to 1 if there is a carry or borrow at bit 3, and cleared to 0 otherwise. When the ADD.W, SUB.W, CMP.W, or NEG.W instruction is executed, the H flag is set to 1 if there is a carry or borrow at bit 11, and cleared to 0 otherwise. When the ADD.L, SUB.L, CMP.L, or NEG.L instruction is executed, the H flag is set to 1 if there is a carry or borrow at bit 27, and cleared to 0 otherwise.

• Bit 4—User Bit (U)

Can be written and read by software using the LDC, STC, ANDC, ORC, and XORC instructions.

• Bit 3—Negative Flag (N)

Stores the value of the most significant bit (sign bit) of data.

• Bit 2—Zero Flag (Z)

Set to 1 to indicate zero data, and cleared to 0 to indicate non-zero data.

• Bit 1—Overflow Flag (V)

Set to 1 when an arithmetic overflow occurs, and cleared to 0 at other times.

• Bit 0—Carry Flag (C)

Set to 1 when a carry occurs, and cleared to 0 otherwise. Used by:

- Add instructions, to indicate a carry

- Subtract instructions, to indicate a borrow

- Shift and rotate instructions, to store the value shifted out of the end bit

The carry flag is also used as a bit accumulator by bit-manipulation instructions.

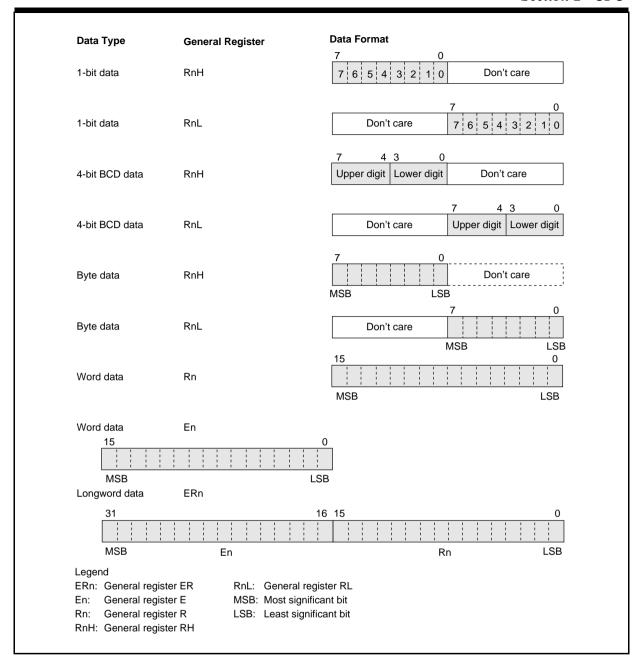

## 2.3 Data Formats

The CPU can process 1-bit, 4-bit (BCD), 8-bit (byte), 16-bit (word), and 32-bit (longword) data.

Bit-manipulation instructions operate on 1-bit data by accessing bit n (n = 0, 1, 2, ..., 7) of byte operand data.

The DAA and DAS decimal-adjust instructions treat byte data as two digits of 4-bit BCD data.

## **General Register Data Formats**

## **Memory Data Formats**

## Section 2 CPU

| Data Type     | Data Format                                                 |

|---------------|-------------------------------------------------------------|

|               | Address                                                     |

| 1-bit data    | Address L 7 6 5 4 3 2 1 0                                   |

| Byte data     | Address L MSB LSB                                           |

| Word data     | Address 2M MSB LSB                                          |

| Longword data | Address 2N MSB Address 2N + 1 Address 2N + 2 Address 2N + 3 |

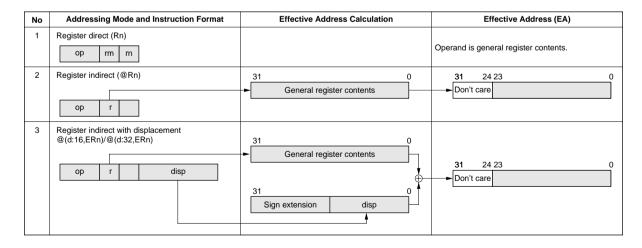

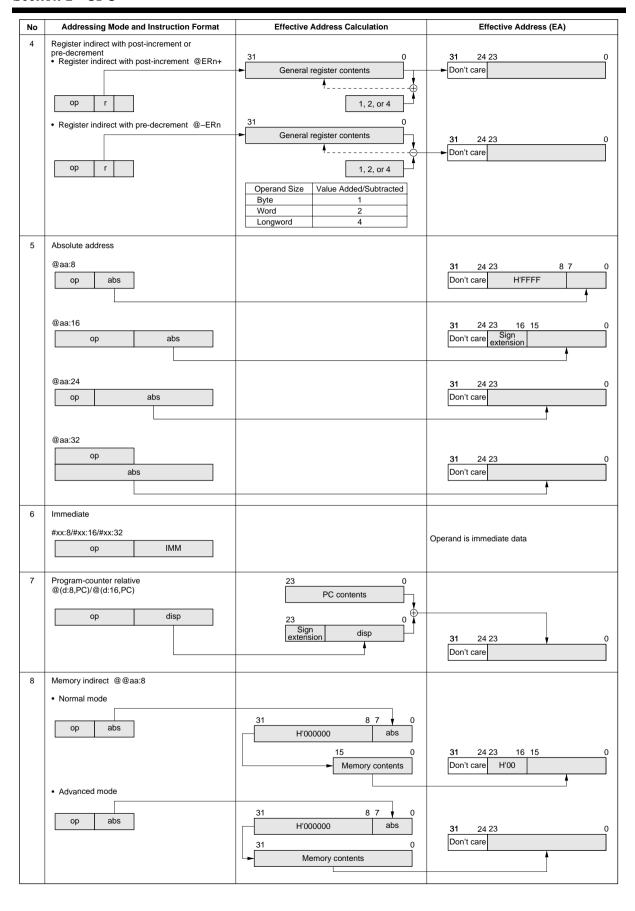

#### 2.4 **Addressing Modes**

The H8S/2000 CPU supports eight addressing modes.

## **Addressing Modes**

| No. | Addressing Mode                       | Symbol                     |

|-----|---------------------------------------|----------------------------|

| 1   | Register direct                       | Rn                         |

| 2   | Register indirect                     | @ERn                       |

| 3   | Register indirect with displacement   | @(d:16,ERn)/@(d:32,ERn)    |

| 4   | Register indirect with post-increment | @ERn+                      |

|     | Register indirect with pre-decrement  | @-ERn                      |

| 5   | Absolute address                      | @aa:8/@aa:16/@aa:24/@aa:32 |

| 6   | Immediate                             | #xx:8/#xx:16/#xx:32        |

| 7   | Program-counter relative              | @(d:8,PC)/@(d:16,PC)       |

| 8   | Memory indirect                       | @@aa:8                     |

## Effective Address (EA) Calculation

In normal mode, the upper 8 bits of the effective address are ignored in order to generate a 16-bit effective address.

#### **Instruction Set** 2.5

The H8S/2000 CPU has 65 types of instructions.

#### **Features**

- Upward-compatible at object level with H8/300H and H8/300 CPUs.

- General register architecture

- 8/16/32-bit transfer instructions and arithmetic and logic instructions

- Byte (B), word (W), and longword (L) formats for transfer instructions and basic arithmetic and logic instructions

- Unsigned and signed multiply and divide instructions

- Powerful bit-manipulation instructions

- Instructions for saving and restoring multiple registers

#### **Assembler Format**

The ADD instruction format is shown below as an example.

## **Instruction Set Table**

## 1. Data transfer instructions

| Mnemonic |                       |              | A | Addressing Mode/Instruction<br>Length (Bytes) |      |          |             |     |         |       | n |                               |   | Condition Code |          |          |   |   | No. of<br>States <sup>*1</sup> |

|----------|-----------------------|--------------|---|-----------------------------------------------|------|----------|-------------|-----|---------|-------|---|-------------------------------|---|----------------|----------|----------|---|---|--------------------------------|

|          |                       | Operand Size |   | Rn                                            | @ERn | @(d,ERn) | @-ERn/@ERn+ | @aa | @(d,PC) | @ @aa | _ | Operation                     | ı | н              | N        | z        | v | С | Normal<br>Advanced             |

| MOV      | MOV.B #xx:8,Rd        | В            | 2 |                                               |      |          |             |     |         |       |   | #xx:8→Rd8                     | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 1                              |

|          | MOV.B Rs,Rd           | В            |   | 2                                             |      |          |             |     |         |       |   | Rs8→Rd8                       | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 1                              |

|          | MOV.B @ERs,Rd         | В            |   |                                               | 2    |          |             |     |         |       |   | @ERs→Rd8                      | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 2                              |

|          | MOV.B @(d:16,ERs),Rd  | В            |   |                                               |      | 4        |             |     |         |       |   | @(d:16,ERs)→Rd8               | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.B @(d:32,ERs),Rd  | В            |   |                                               |      | 8        |             |     |         |       |   | @(d:32,ERs)→Rd8               | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 5                              |

|          | MOV.B @ERs+,Rd        | В            |   |                                               |      |          | 2           |     |         |       |   | @ERs→Rd8,ERs32+1→ERs32        | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.B @aa:8,Rd        | В            |   |                                               |      |          |             | 2   |         |       |   | @aa:8→Rd8                     | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 2                              |

|          | MOV.B @aa:16,Rd       | В            |   |                                               |      |          |             | 4   |         |       |   | @aa:16→Rd8                    | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.B @aa:32,Rd       | В            |   |                                               |      |          |             | 6   |         |       |   | @aa:32→Rd8                    | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 4                              |

|          | MOV.B Rs,@ERd         | В            |   |                                               | 2    |          |             |     |         |       |   | Rs8→@ERd                      | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 2                              |

|          | MOV.B Rs,@(d:16,ERd)  | В            |   |                                               |      | 4        |             |     |         |       |   | Rd8→@(d:16,ERd)               | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.B Rs,@(d:32,ERd)  | В            |   |                                               |      | 8        |             |     |         |       |   | Rd8→@(d:32,ERd)               | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 5                              |

|          | MOV.B Rs,@-ERd        | В            |   |                                               |      |          | 2           |     |         |       |   | ERd32–1→ERd32,Rs8→@ERd        | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.B Rs,@aa:8        | В            |   |                                               |      |          |             | 2   |         |       |   | Rs8→@aa:8                     | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 2                              |

|          | MOV.B Rs,@aa:16       | В            |   |                                               |      |          |             | 4   |         |       |   | Rs8→@aa:16                    | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.B Rs,@aa:32       | В            |   |                                               |      |          |             | 6   |         |       |   | Rs8→@aa:32                    | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 4                              |

|          | MOV.W #xx:16,Rd       | W            | 4 |                                               |      |          |             |     |         |       |   | #xx:16→Rd16                   | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 2                              |

|          | MOV.W Rs,Rd           | W            |   | 2                                             |      |          |             |     |         |       |   | Rs16→Rd16                     | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 1                              |

|          | MOV.W @ERs,Rd         | W            |   |                                               | 2    |          |             |     |         |       |   | @ERs→Rd16                     | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 2                              |

|          | MOV.W @(d:16,ERs),Rd  | W            |   |                                               |      | 4        |             |     |         |       |   | @(d:16,ERs)→Rd16              | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.W @(d:32,ERs),Rd  | W            |   |                                               |      | 8        |             |     |         |       |   | @(d:32,ERs)→Rd16              | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 5                              |

|          | MOV.W @ERs+,Rd        | W            |   |                                               |      |          | 2           |     |         |       |   | ERs→Rd16,ERs32+2→ERs32        | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.W @aa:16,Rd       | W            |   |                                               |      |          |             | 4   |         |       |   | @aa:16→Rd16                   | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.W @aa:32,Rd       | W            |   |                                               |      |          |             | 6   |         |       |   | @aa:32→Rd16                   | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 4                              |

|          | MOV.W Rs,@ERd         | W            |   |                                               | 2    |          |             |     |         |       |   | Rs16→@ERd                     | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 2                              |

|          | MOV.W Rs,@(d:16,ERd)  | W            |   |                                               |      | 4        |             |     |         |       |   | Rs16→@(d:16,ERd)              | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.W Rs,@(d:32,ERd)  | W            |   |                                               |      | 8        |             |     |         |       |   | Rs16→@(d:32,ERd)              | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 5                              |

|          | MOV.W Rs,@-ERd        | W            |   |                                               |      |          | 2           |     |         |       |   | ERd32–2→ERd32,Rs16→@ERd       | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.W Rs,@aa:16       | W            |   |                                               |      |          |             | 4   |         |       |   | Rs16→@aa:16                   | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.W Rs,@aa:32       | W            |   |                                               |      |          |             | 6   |         |       |   | Rs16→@aa:32                   | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 4                              |

|          | MOV.L #xx:32,ERd      | L            | 6 |                                               |      |          |             |     |         |       |   | #xx:32→ERd32                  | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 3                              |

|          | MOV.L ERs,ERd         | L            |   | 2                                             |      |          |             |     |         |       |   | ERs32→ERd32                   | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 1                              |

|          | MOV.L @ERs,ERd        | L            |   |                                               | 4    |          |             |     |         |       |   | @ERs→ERd32                    | _ | _              | <b>†</b> | <b>†</b> | 0 | _ | 4                              |

|          | MOV.L @(d:16,ERs),ERd | L            |   |                                               |      | 6        |             |     |         |       |   | @(d:16,ERs)→ERd32             | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 5                              |

|          | MOV.L @(d:32,ERs),ERd | L            |   |                                               |      | 10       |             |     |         |       |   | @(d:32,ERs)→ERd32             | _ | _              | <b>↑</b> | <b>↑</b> | 0 | _ | 7                              |

|          | MOV.L @ERs+,ERd       | L            |   |                                               |      |          | 4           |     |         |       |   | @ERs→ERd32,ERs32+4→<br>@ERs32 | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 5                              |

|          | MOV.L @aa:16,ERd      | L            |   |                                               |      |          |             | 6   |         |       |   | @aa:16→ERd32                  | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 5                              |

|          | MOV.L @aa:32,ERd      | L            |   |                                               |      |          |             | 8   |         |       |   | @aa:32→ERd32                  | _ | _              | <b>‡</b> | <b>‡</b> | 0 | _ | 6                              |

|        |                       |              | A    | ddre |      | •        | Mod<br>th (E |     |         | ıctic  | n    |                                                               |   | Con | diti     | on (     | Cod | е | No. of<br>States <sup>*1</sup> |

|--------|-----------------------|--------------|------|------|------|----------|--------------|-----|---------|--------|------|---------------------------------------------------------------|---|-----|----------|----------|-----|---|--------------------------------|

|        | Mnemonic              | Operand Size | #xx# | Rn   | @ERn | @(d,ERn) | @-ERn/@ERn+  | @aa | @(d,PC) | @ @ aa |      | Operation                                                     | ı | н   | N        | z        | v   | С | Normal<br>Advanced             |

| MOV    | MOV.L ERs,@ERd        | L            |      |      | 4    |          |              |     |         |        |      | ERs32→@ERd                                                    | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 4                              |

|        | MOV.L ERs,@(d:16,ERd) | L            |      |      |      | 6        |              |     |         |        |      | ERs32→@(d:16,ERd)                                             | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 5                              |

|        | MOV.L ERs,@(d:32,ERd) | L            |      |      |      | 10       |              |     |         |        |      | ERs32→@(d:32,ERd)                                             | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 7                              |

|        | MOV.L ERs,@-ERd       | L            |      |      |      |          | 4            |     |         |        |      | ERd32–4→ERd32,ERs32→@ERd                                      | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 5                              |

|        | MOV.L ERs,@aa:16      | L            |      |      |      |          |              | 6   |         |        |      | ERs32→@aa:16                                                  | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 5                              |

|        | MOV.L ERs,@aa:32      | L            |      |      |      |          |              | 8   |         |        |      | ERs32→@aa:32                                                  | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 6                              |

| POP    | POP.W Rn              | W            |      |      |      |          |              |     |         |        | 2    | @SP→Rn16,SP+2→SP                                              | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 3                              |

|        | POP.L ERn             | L            |      |      |      |          |              |     |         |        | 4    | @SP→ERn32,SP+4→SP                                             | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 5                              |

| PUSH   | PUSH.W Rn             | W            |      |      |      |          |              |     |         |        | 2    | SP–2→SP,Rn16→@SP                                              | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 3                              |

|        | PUSH.L ERn            | L            |      |      |      |          |              |     |         |        | 4    | SP-4→SP,ERn32→@SP                                             | _ | _   | <b>‡</b> | <b>‡</b> | 0   | _ | 5                              |

| LDM    | LDM @SP+,(ERm-ERn)    | L            |      |      |      |          |              |     |         |        | 4    | (@SP→ERn32,SP+4→SP)<br>Repeated for each register<br>restored | _ | _   | _        | _        | _   | _ | 7/9/11 [1]                     |

| STM    | STM (ERm-ERn),@-SP    | L            |      |      |      |          |              |     |         |        | 4    | (SP-4→SP,ERn32→@SP)<br>Repeated for each register saved       | _ | _   | _        | _        | _   | _ | 7/9/11 [1]                     |

| MOVFPE | MOVFPE @aa:16,Rd      | Ca           | nnot | t be | use  | d in     | the          | H89 | 3/23    | 55 8   | Seri | es                                                            |   |     |          |          |     |   | [2]                            |

| MOVTPE | MOVTPE Rs,@aa:16      |              |      |      |      |          |              |     |         |        |      |                                                               |   |     |          |          |     |   | [2]                            |

## 2. Arithmetic instructions

|       |                  |              | A   | ddre |      | ng N<br>engt |             |     |         | ıctio | on |                                           |                | Con      | diti     | on (     | Cod      | e        | No. of<br>States <sup>*1</sup> |

|-------|------------------|--------------|-----|------|------|--------------|-------------|-----|---------|-------|----|-------------------------------------------|----------------|----------|----------|----------|----------|----------|--------------------------------|

|       | Mnemonic         | Operand Size | xx# | Rn   | @ERn | @(d,ERn)     | @-ERn/@ERn+ | @aa | @(d,PC) | @ @aa | 1  | Operation                                 | ı              | н        | N        | z        | v        | С        | Normal<br>Advanced             |

| ADD   | ADD.B #xx:8,Rd   | В            | 2   |      |      |              |             |     |         |       |    | Rd8+#xx:8→Rd8                             | _              | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | ADD.B Rs,Rd      | В            |     | 2    |      |              |             |     |         |       |    | Rd8+Rs8→Rd8                               | -              | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | ADD.W #xx:16,Rd  | W            | 4   |      |      |              |             |     |         |       |    | Rd16+#xx:16→Rd16                          | -              | [3]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 2                              |

|       | ADD.W Rs,Rd      | W            |     | 2    |      |              |             |     |         |       |    | Rd16+Rs16→Rd16                            | _              | [3]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | ADD.L #xx:32,ERd | L            | 6   |      |      |              |             |     |         |       |    | ERd32+#xx:32→ERd32                        | _              | [4]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 3                              |

|       | ADD.L ERs,ERd    | L            |     | 2    |      |              |             |     |         |       |    | ERd32+ERs32→ERd32                         | -              | [4]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

| ADDX  | ADDX #xx:8,Rd    | В            | 2   |      |      |              |             |     |         |       |    | Rd8+#xx:8+C→Rd8                           | _              | <b>‡</b> | <b>‡</b> | [5]      | <b>‡</b> | <b>‡</b> | 1                              |

|       | ADDX Rs,Rd       | В            |     | 2    |      |              |             |     |         |       |    | Rd8+Rs8+C→Rd8                             | _              | <b>‡</b> | <b>‡</b> | [5]      | <b>‡</b> | <b>‡</b> | 1                              |

| ADDS  | ADDS #1,ERd      | L            |     | 2    |      |              |             |     |         |       |    | ERd32+1→ERd32                             | _              | _        | _        | _        | _        | _        | 1                              |

|       | ADDS #2,ERd      | L            |     | 2    |      |              |             |     |         |       |    | ERd32+2→ERd32                             | _              | _        | _        | _        | _        | _        | 1                              |

|       | ADDS #4,ERd      | L            |     | 2    |      |              |             |     |         |       |    | ERd32+4→ERd32                             | 1_             | _        | _        | _        | _        | _        | 1                              |

| INC   | INC.B Rd         | В            |     | 2    |      |              |             |     |         |       |    | Rd8+1→Rd8                                 | _              | _        | <b>‡</b> | <b>‡</b> | <b>‡</b> | _        | 1                              |

|       | INC.W #1,Rd      | W            |     | 2    |      |              |             |     |         |       |    | Rd16+1→Rd16                               | _              | _        | <b>‡</b> | <b>‡</b> | <b>‡</b> | _        | 1                              |

|       | INC.W #2,Rd      | W            |     | 2    |      |              |             |     |         |       |    | Rd16+2→Rd16                               | _              | _        | <b>‡</b> | <b>‡</b> | <b>‡</b> | _        | 1                              |

|       | INC.L #1,ERd     | L            |     | 2    |      |              |             |     |         |       |    | ERd32+1→ERd32                             | _              | _        | <b>‡</b> | <b>‡</b> | <b>‡</b> | _        | 1                              |

|       | INC.L #2,ERd     | L            |     | 2    |      |              |             |     |         |       |    | ERd32+2→ERd32                             | _              | _        | <b>‡</b> | <b>‡</b> | <b>‡</b> | _        | 1                              |

| DAA   | DAA Rd           | В            |     | 2    |      |              |             |     |         |       |    | Rd8 decimal adjust → Rd8                  | 1_             | *        | <b>‡</b> | <b>‡</b> | *        | <b>‡</b> | 1                              |

| SUB   | SUB.B Rs,Rd      | В            |     | 2    |      |              |             |     |         |       |    | Rd8–Rs8→Rd8                               | _              | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | SUB.W #xx:16,Rd  | W            | 4   |      |      |              |             |     |         |       |    | Rd16–#xx:16→Rd16                          | _              | [3]      | <b>1</b> | <b>‡</b> | <b>1</b> | <b>‡</b> | 2                              |

|       | SUB.W Rs,Rd      | w            |     | 2    |      |              |             |     |         |       |    | Rd16-Rs16→Rd16                            | 1_             | [3]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | SUB.L #xx:32,ERd | L            | 6   |      |      |              |             |     |         |       |    | ERd32-#xx:32→ERd32                        | _              | [4]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 3                              |

|       | SUB.L ERs,ERd    | L            |     | 2    |      |              |             |     |         |       |    | ERd32–ERs32→ERd32                         | 1_             | [4]      | <b>1</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

| SUBX  | SUBX #xx:8,Rd    | В            | 2   |      |      |              |             |     |         |       |    | Rd8-#xx:8-C→Rd8                           | 1_             | <b>‡</b> | <b>‡</b> | [5]      | <b>‡</b> | <b>‡</b> | 1                              |

|       | SUBX Rs,Rd       | В            |     | 2    |      |              |             |     |         |       |    | Rd8–Rs8–C→Rd8                             | 1_             | <b>†</b> | <b></b>  | [5]      |          | <b>†</b> | 1                              |

| SUBS  | SUBS #1,ERd      | L            |     | 2    |      |              |             |     |         |       |    | ERd32–1→ERd32                             | 1_             | _        | Ė        | _        | _        | _        | 1                              |

|       | SUBS #2,ERd      | L            |     | 2    |      |              |             |     |         |       |    | ERd32–2→ERd32                             |                | _        | _        | _        | _        | _        | 1                              |

|       | SUBS #4,ERd      | L            |     | 2    |      |              |             |     |         |       |    | ERd32–4→ERd32                             | 1_             | _        | _        | _        | _        | _        | 1                              |

| DEC   | DEC.B Rd         | В            |     | 2    |      |              |             |     |         |       |    | Rd8–1 →Rd8                                | 1_             | _        | <b>‡</b> | <b>‡</b> | <b>‡</b> | _        | 1                              |

|       | DEC.W #1,Rd      | W            |     | 2    |      |              |             |     |         |       |    | Rd16–1→Rd16                               | 1_             |          | <b>‡</b> | <b>‡</b> | 1        | _        | 1                              |

|       | DEC.W #2,Rd      | W            |     | 2    |      |              |             |     |         |       |    | Rd16–2→Rd16                               |                |          | <b>‡</b> | <b>‡</b> | <b>‡</b> |          | 1                              |

|       | DEC.L #1,ERd     | L            |     | 2    |      |              |             |     |         |       |    | ERd32–1→ERd32                             |                |          | <b>‡</b> | <b></b>  | <b>‡</b> |          | 1                              |

|       | DEC.L #2,ERd     | L            |     | 2    |      |              |             |     |         |       |    | ERd32–2→ERd32                             | E              |          | <b>‡</b> | <b>‡</b> | <b>‡</b> |          | 1                              |

| DAS   | DAS Rd           | В            |     | 2    |      |              |             |     |         |       |    | Rd8 decimal adjust → Rd8                  | <del>  -</del> | *        | <b>↓</b> | <b>‡</b> | *        | _        | 1                              |

| MULXU | MULXU.B Rs,Rd    | В            |     | 2    |      |              |             |     |         |       |    | Rd8×Rs8→Rd16 (unsigned multiplication)    | -              | -        | _        | _        | -        | _        | 12                             |

|       | MULXU.W Rs,ERd   | W            |     | 2    |      |              |             |     |         |       |    | Rd16×Rs16→ERd32 (unsigned multiplication) | -              | _        | _        | _        | _        | _        | 20                             |

| MULXS | MULXS.B Rs,Rd    | В            |     | 4    |      |              |             |     |         |       |    | Rd8×Rs8→Rd16 (signed multiplication)      | _              | _        | <b>‡</b> | <b>‡</b> | _        | _        | 13                             |

|       | MULXS.W Rs,ERd   | W            |     | 4    |      |              |             |     |         |       |    | Rd16×Rs16→ERd32 (signed multiplication)   | _              | _        | <b>‡</b> | <b>‡</b> | _        | _        | 21                             |

|       |                  |              | Ad   | ddre | essi<br>Le | ng N<br>engti |             |     |         | ıctio  | n |                                                                                                   |   | Con      | diti     | on (     | Cod      | е        | No. of<br>States <sup>*1</sup> |

|-------|------------------|--------------|------|------|------------|---------------|-------------|-----|---------|--------|---|---------------------------------------------------------------------------------------------------|---|----------|----------|----------|----------|----------|--------------------------------|

|       | Mnemonic         | Operand Size | #xx# | Rn   | @ERn       | @(d,ERn)      | @-ERn/@ERn+ | @aa | @(d,PC) | @ @ aa | 1 | Operation                                                                                         | ı | Н        | N        | z        | v        | С        | Normal<br>Advanced             |

| DIVXU | DIVXU.B Rs,Rd    | В            |      | 2    |            |               |             |     |         |        |   | Rd16÷Rs8→Rd16<br>(RdH: remainder, RdL: quotient)<br>(unsigned division)                           | - | _        | [6]      | [7]      | _        | _        | 12                             |

|       | DIVXU.W Rs,ERd   | W            |      | 2    |            |               |             |     |         |        |   | ERd32÷Rs16→ERd32<br>(Ed: remainder, Rd: quotient)<br>(unsigned division)                          | _ | _        | [6]      | [7]      | _        | _        | 20                             |

| DIVXS | DIVXS.B Rs,Rd    | В            |      | 4    |            |               |             |     |         |        |   | Rd16+Rs8→Rd16<br>(RdH: remainder, RdL: quotient)<br>(signed division)                             | _ | _        | [8]      | [7]      | _        | _        | 13                             |

|       | DIVXS.W Rs,ERd   | W            |      | 4    |            |               |             |     |         |        |   | ERd32÷Rs16→ERd32<br>(Ed: remainder, Rd: quotient)<br>(signed division)                            | - | _        | [8]      | [7]      | _        | _        | 21                             |

| CMP   | CMP.B #xx:8,Rd   | В            | 2    |      |            |               |             |     |         |        |   | Rd8-#xx:8                                                                                         | _ | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | CMP.B Rs,Rd      | В            |      | 2    |            |               |             |     |         |        |   | Rd8-Rs8                                                                                           | _ | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | CMP.W #xx:16,Rd  | W            | 4    |      |            |               |             |     |         |        |   | Rd16-#xx:16                                                                                       | _ | [3]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 2                              |

|       | CMP.W Rs,Rd      | W            |      | 2    |            |               |             |     |         |        |   | Rd16-Rs16                                                                                         | _ | [3]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | CMP.L #xx:32,ERd | L            | 6    |      |            |               |             |     |         |        |   | ERd32-#xx:32                                                                                      | _ | [4]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 3                              |

|       | CMP.L ERs,ERd    | L            |      | 2    |            |               |             |     |         |        |   | ERd32-ERs32                                                                                       | _ | [4]      | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

| NEG   | NEG.B Rd         | В            |      | 2    |            |               |             |     |         |        |   | 0–Rd8→Rd8                                                                                         | _ | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | NEG.W Rd         | W            |      | 2    |            |               |             |     |         |        |   | 0–Rd16→Rd16                                                                                       | _ | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

|       | NEG.L ERd        | L            |      | 2    |            |               |             |     |         |        |   | 0–ERd32→ERd32                                                                                     | _ | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                              |

| EXTU  | EXTU.W Rd        | W            |      | 2    |            |               |             |     |         |        |   | $0 \rightarrow$ ( <bits 15="" 8="" to=""> of Rd16)</bits>                                         | _ | _        | 0        | <b>‡</b> | 0        | _        | 1                              |

|       | EXTU.L ERd       | L            |      | 2    |            |               |             |     |         |        |   | $0 \rightarrow$ ( <bits 16="" 31="" to=""> of ERd32)</bits>                                       | _ | _        | 0        | <b>‡</b> | 0        | _        | 1                              |

| EXTS  | EXTS.W Rd        | W            |      | 2    |            |               |             |     |         |        |   | ( <bit 7=""> of Rd16) <math>\rightarrow</math> (<bits 15="" 8="" to=""> of Rd16)</bits></bit>     | _ | _        | <b>‡</b> | <b>‡</b> | 0        | _        | 1                              |

|       | EXTS.L ERd       | L            |      | 2    |            |               |             |     |         |        |   | ( <bit 15=""> of ERd32) <math>\rightarrow</math> (<bits 16="" 31="" to=""> of ERd32)</bits></bit> | _ | _        | <b>‡</b> | <b>‡</b> | 0        | -        | 1                              |

| TAS   | TAS @ERd         | В            |      |      | 4          |               |             |     |         |        |   | @ERd-0 $\rightarrow$ CRR set, (1) $\rightarrow$ ( <bit 7=""> of @ERd)</bit>                       | _ | -        | \$       | <b>‡</b> | 0        | -        | 4                              |

## Logical instructions

|     |                  |              | A   | ddre |      | ng Mo |             |                | uctior |                |      |   | Con | diti     | on C              | ode | е | No. of<br>States*1 |

|-----|------------------|--------------|-----|------|------|-------|-------------|----------------|--------|----------------|------|---|-----|----------|-------------------|-----|---|--------------------|

|     | Mnemonic         | Operand Size | xx# | Rn   | @ERn | ERn)  | @-ERn/@ERn+ | @aa<br>@(d.PC) | @ @aa  | Opera<br>[     | tion | ı | н   | N        | z                 | v   | С | Normal<br>Advanced |

| AND | AND.B #xx:8,Rd   | В            | 2   |      |      |       |             |                |        | Rd8∧#xx:8→Rd8  |      | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | AND.B Rs,Rd      | В            |     | 2    |      |       |             |                |        | Rd8∧Rs8→Rd8    |      | _ | _   | <b>‡</b> | $\leftrightarrow$ | 0   | _ | 1                  |

|     | AND.W #xx:16,Rd  | W            | 4   |      |      |       |             |                |        | Rd16∧#xx:16→Rd | 16   | _ | _   | <b>‡</b> | $\leftrightarrow$ | 0   | _ | 2                  |

|     | AND.W Rs,Rd      | W            |     | 2    |      |       |             |                |        | Rd16∧Rs16→Rd1  | 6    | _ | _   | <b>‡</b> | $\leftrightarrow$ | 0   | _ | 1                  |

|     | AND.L #xx:32,ERd | L            | 6   |      |      |       |             |                |        | ERd32∧#xx:32→E | Rd32 | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 3                  |

|     | AND.L ERs,ERd    | L            |     | 4    |      |       |             |                |        | ERd32∧ERs32→E  | Rd32 | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 2                  |

| OR  | OR.B #xx:8,Rd    | В            | 2   |      |      |       |             |                |        | Rd8∨#xx:8→Rd8  |      | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | OR.B Rs,Rd       | В            |     | 2    |      |       |             |                |        | Rd8∨Rs8→Rd8    |      | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | OR.W #xx:16,Rd   | W            | 4   |      |      |       |             |                |        | Rd16∨#xx:16→Rd | 16   | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 2                  |

|     | OR.W Rs,Rd       | W            |     | 2    |      |       |             |                |        | Rd16∨Rs16→Rd1  | 6    | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | OR.L #xx:32,ERd  | L            | 6   |      |      |       |             |                |        | ERd32∨#xx:32→E | Rd32 | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 3                  |

|     | OR.L ERs,ERd     | L            |     | 4    |      |       |             |                |        | ERd32√ERs32→E  | Rd32 | _ | _   | <b>‡</b> | $\leftrightarrow$ | 0   | _ | 2                  |

| XOR | XOR.B #xx:8,Rd   | В            | 2   |      |      |       |             |                |        | Rd8⊕#xx:8→Rd8  |      | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | XOR.B Rs,Rd      | В            |     | 2    |      |       |             |                |        | Rd8⊕Rs8→Rd8    |      | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | XOR.W #xx:16,Rd  | W            | 4   |      |      |       |             |                |        | Rd16⊕#xx:16→Rd | 116  | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 2                  |

|     | XOR.W Rs,Rd      | W            |     | 2    |      |       |             |                |        | Rd16⊕Rs16→Rd1  | 6    | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | XOR.L #xx:32,ERd | L            | 6   |      |      |       |             |                |        | ERd32⊕#xx:32→E | Rd32 | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 3                  |

|     | XOR.L ERs,ERd    | L            |     | 4    |      |       |             |                |        | ERd32⊕ERs32→E  | Rd32 | _ | _   | <b>‡</b> | <b></b>           | 0   | _ | 2                  |

| NOT | NOT.B Rd         | В            |     | 2    |      |       |             |                |        | ¬ Rd8→Rd8      |      | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | NOT.W Rd         | W            |     | 2    |      |       |             |                |        | ¬ Rd16→Rd16    |      | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

|     | NOT.L ERd        | L            |     | 2    |      |       |             |                |        | ¬ Rd32→Rd32    |      | _ | _   | <b>‡</b> | <b>‡</b>          | 0   | _ | 1                  |

## Shift instructions

|       |                |              | Add |           | sing<br>Leng     |             |     |         | uctio  | on |              | ( | Con | diti     | on (     | Cod      | е        | No. of<br>States*1 |

|-------|----------------|--------------|-----|-----------|------------------|-------------|-----|---------|--------|----|--------------|---|-----|----------|----------|----------|----------|--------------------|

|       | Mnemonic       | Operand Size | xx# | Rn<br>⊙== | @EKn<br>@(d.ERn) | @-ERn/@ERn+ | @aa | @(d,PC) | @ @ aa | ı  | Operation    | ı | Н   | N        | z        | v        | С        | Normal<br>Advanced |

| SHAL  | SHAL.B Rd      | В            |     | 2         |                  |             |     |         |        |    |              | _ | _   | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                  |

|       | SHAL.B #2,Rd   | В            |     | 2         |                  |             |     |         |        |    | •            | _ | _   | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                  |

|       | SHAL.W Rd      | W            |     | 2         |                  |             |     |         |        |    | -0           | _ | _   | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                  |

|       | SHAL.W #2,Rd   | W            |     | 2         |                  |             |     |         |        |    | C MSB ← LSB  | _ | _   | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                  |

|       | SHAL.L ERd     | L            |     | 2         |                  |             |     |         |        |    |              | _ | _   | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                  |

|       | SHAL.L #2,ERd  | L            |     | 2         |                  |             |     |         |        |    | -            | _ | _   | <b>‡</b> | <b>‡</b> | <b>‡</b> | <b>‡</b> | 1                  |

| SHAR  | SHAR.B Rd      | В            |     | 2         |                  |             |     |         |        |    |              | _ | _   | <b>‡</b> | <b>‡</b> | 0        | <b>‡</b> | 1                  |

|       | SHAR.B #2,Rd   | В            |     | 2         |                  |             |     |         |        |    |              | _ | _   | <b>‡</b> | <b>‡</b> | 0        | <b>‡</b> | 1                  |

|       | SHAR.W Rd      | w            |     | 2         |                  |             |     |         |        |    | -            | _ | _   | <b>‡</b> | <b>‡</b> | 0        | <b>‡</b> | 1                  |

|       | SHAR.W #2,Rd   | W            |     | 2         |                  |             |     |         |        |    | MSB → LSB C  | _ | _   | <b>‡</b> | <b>‡</b> | 0        | <b>‡</b> | 1                  |

|       | SHAR.L ERd     | L            |     | 2         |                  |             |     |         |        |    | -            | _ | _   | <b>‡</b> | <b>‡</b> | 0        | <b>‡</b> | 1                  |

|       | SHAR.L #2,ERd  | L            |     | 2         |                  |             |     |         |        |    | _            | _ | _   | <b>‡</b> | <b>‡</b> | 0        | <b>‡</b> | 1                  |

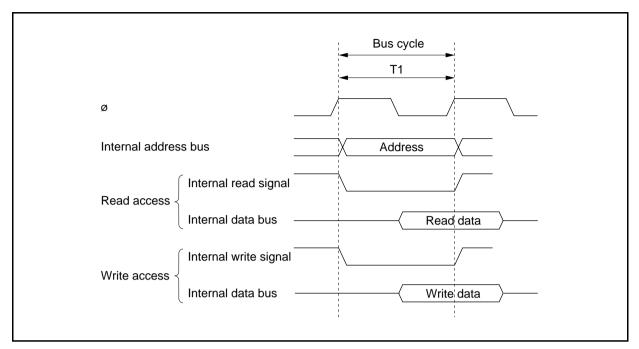

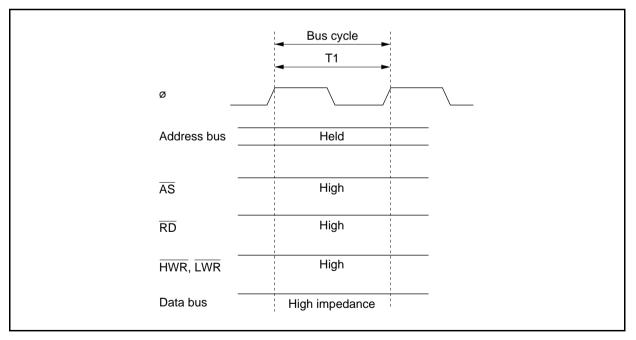

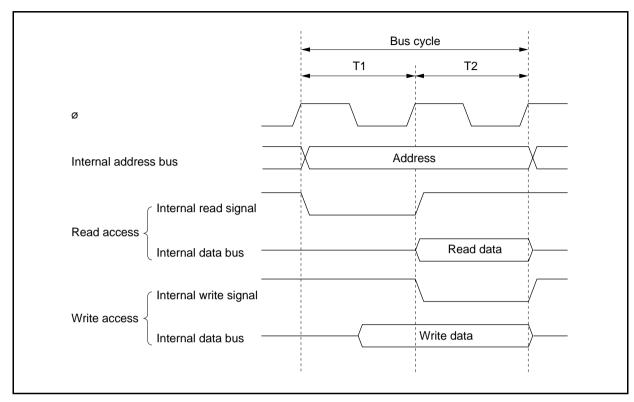

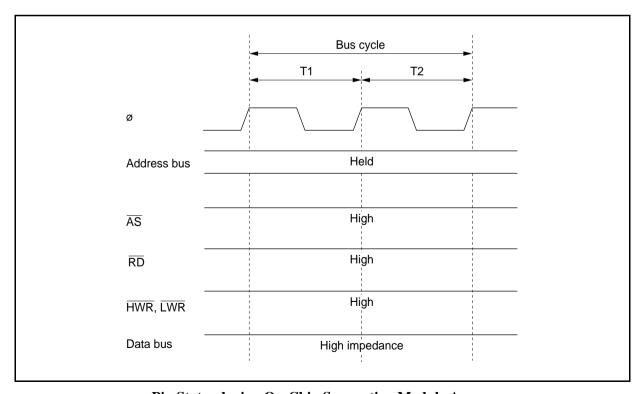

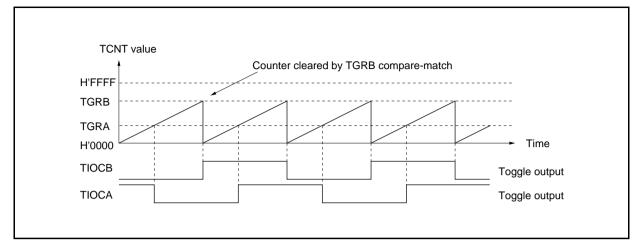

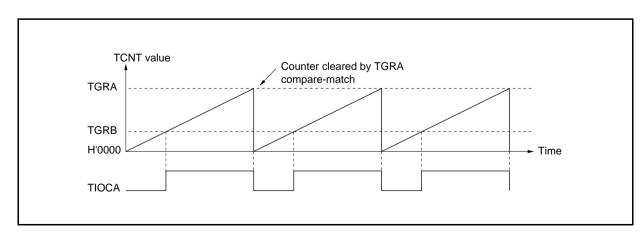

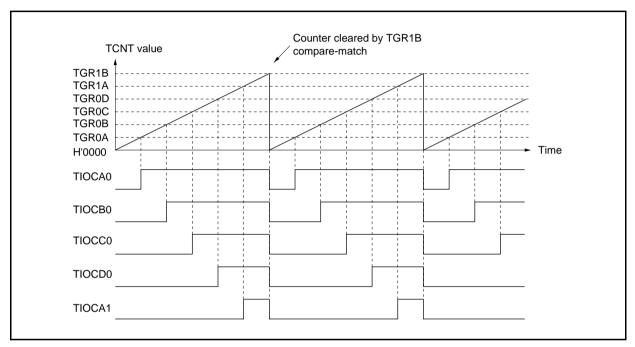

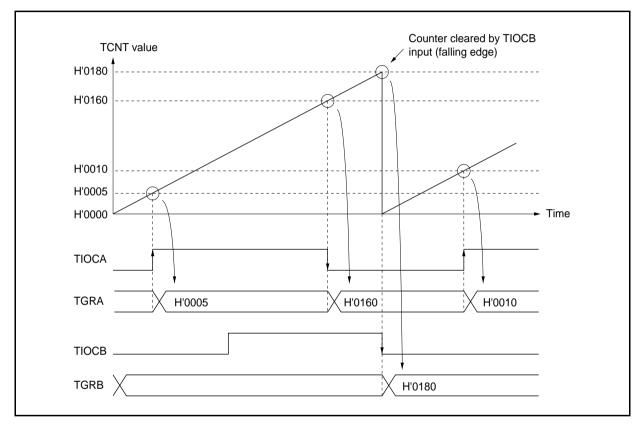

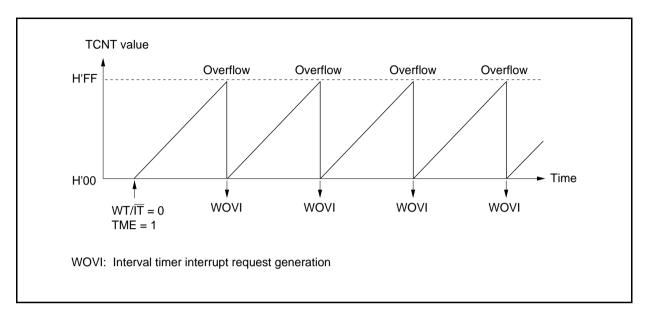

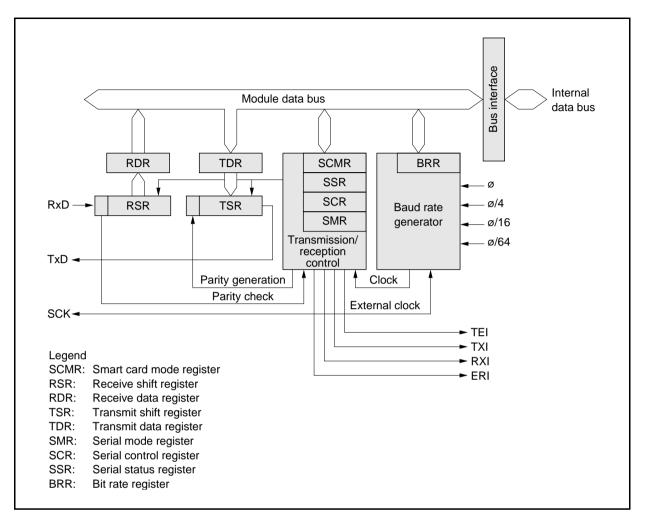

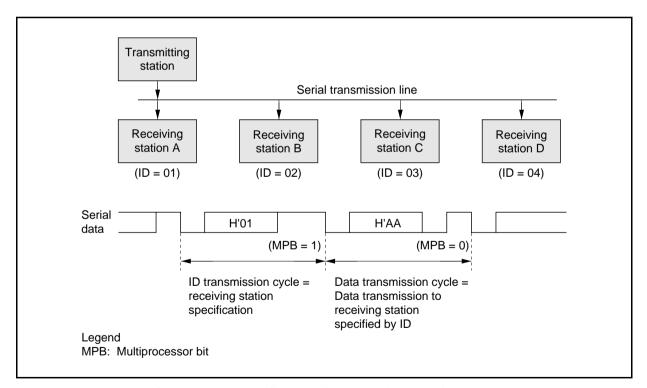

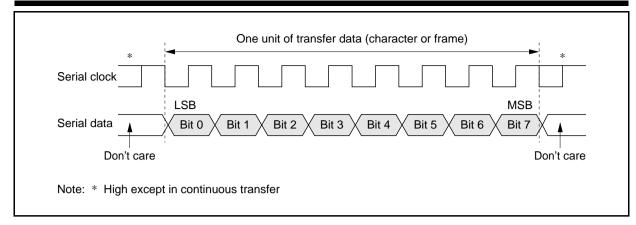

| SHLL  | SHLL.B Rd      | В            |     | 2         |                  |             |     |         |        |    |              | _ | _   | <b>‡</b> | <b>‡</b> | 0        | <b>‡</b> | 1                  |