## H8/3867 Series

**Application Note**

ADE-502-068 Rev. 1.0 8/30/1999 Hitachi, Ltd.

#### **Cautions**

- 1. Hitachi neither warrants nor grants licenses of any rights of Hitachi's or any third party's patent, copyright, trademark, or other intellectual property rights for information contained in this document. Hitachi bears no responsibility for problems that may arise with third party's rights, including intellectual property rights, in connection with use of the information contained in this document.

- Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.

- 3. Hitachi makes every attempt to ensure that its products are of high quality and reliability. However, contact Hitachi's sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation, traffic, safety equipment or medical equipment for life support.

- 4. Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installation conditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.

- 5. This product is not designed to be radiation resistant.

- 6. No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.

- 7. Contact Hitachi's sales office for any questions regarding this document or Hitachi semiconductor products.

## **Preface**

The H8/300L Series of single-chip microcomputers are based on the high-speed H8/300L CPU, and integrate all peripheral functions necessary for system configuration.

The H8/300L CPU uses an instruction set which is compatible with the H8/300 CPU.

The H8/3867 Series and H8/3827 Series are provided with such peripheral functions for system configuration as an LCD controller/driver, six different timers, a 14-bit pulse width modulator (PWM), a two-channel serial communication interface, and an A/D converter. These models can be used as microcomputers for embedded systems where LCD display is required.

The H8/3867 Series models are equipped with a booster constant-voltage (5 V) power supply as an LCD driver power supply, providing a constant 5 V regardless of  $V_{\rm cc}$ .

These H8/3867 Series application notes include a "Basic Operation" section with operation examples when using the built-in peripheral functions of the H8/3867 Series independently. They are provided in the hope that they will be of use for software and hardware design.

Operation of the programs and circuits described in these application notes has been verified, but their operation should be confirmed by the user as well before actually being used.

## Contents

| Secti | ion 1 Guide to Using the H8/3867 Series Application Notes | 1   |

|-------|-----------------------------------------------------------|-----|

| 1.1   | Contents of Basic Operation                               | 2   |

| Secti | ion 2 Basic Operation                                     | 5   |

| 2.1   | Internal Power Supply Step-Down Circuit Settings          | 5   |

| 2.2   | Asynchronous Event Counter Operation                      | 10  |

| 2.3   | LCD Display with Static Duty                              | 35  |

| 2.4   | LCD Display with 1/4 Duty                                 | 58  |

| 2.5   | LCD Display with Segment External Expansion               | 83  |

| 2.6   | Oscillation Stabilization Time Settings                   | 108 |

| 2.7   | Module Standby Mode Settings                              | 117 |

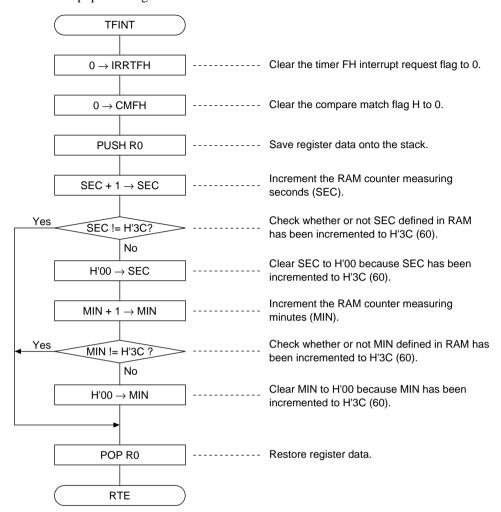

| 2.8   | Clock Operation Using Timer F                             | 124 |

# Section 1 Guide to Using the H8/3867 Series Application Notes

These application notes consist of two sections, as follows.

Figure 1 Contents of these Application Notes

#### Guide to Using the H8/3867 Series Application Notes

Explains how to use the H8/3867 Series application notes.

## **Basic Operation**

Explains how to use the built-in peripheral functions of the H8/3867 Series through simple task examples.

## 1.1 Contents of Basic Operation

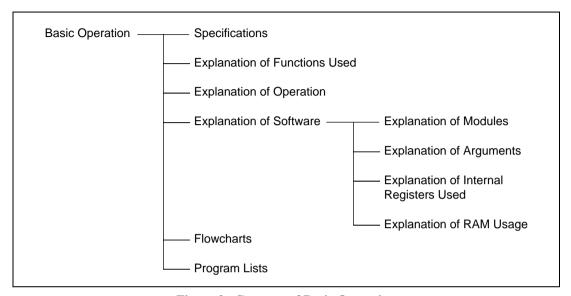

Basic Operation includes the sections shown below, explaining use of the built-in peripheral functions.

Figure 2 Contents of Basic Operation

#### **Specifications**

Explains system specifications for task examples.

#### **Explanation of Functions Used**

Explains the features of peripheral functions used in task examples, and allocation of the peripheral functions.

## **Explanation of Operation**

Explains operation of task examples using timing charts.

#### **Explanation of Software**

1. Explanation of Modules

Explains the software modules used for operation in task examples.

2. Explanation of Arguments

Explains input arguments necessary for module execution, and arguments output following execution

3. Explanation of Internal Registers Used

Explains internal registers such as a timer control register and serial mode register of peripheral functions used in modules.

4. Explanation of RAM Usage

Explains RAM label names and functions used in modules.

#### **Flowcharts**

Uses flowcharts to explain the software executed in task examples.

#### **Program Lists**

Gives program lists for software executed in task examples.

## Section 2 Basic Operation

## 2.1 Internal Power Supply Step-Down Circuit Settings

| <b>Internal Power Supply Step-Down</b> | MCU:           | <b>Functions Used:</b>          |

|----------------------------------------|----------------|---------------------------------|

| Circuit Settings                       | H8/3867 Series | Internal Power Supply Step-Down |

|                                        |                | Circuit                         |

#### **Usage**

The H8/3867 Series incorporates an internal power supply step-down circuit. Below the features and usage of the internal power supply step-down circuit are explained, together with important notes and the power supply voltage and operating range.

#### Features of the internal power supply step-down circuit

- 1. By using the internal power supply step-down circuit, the internal power supply voltage can be held constant at approximately 1.5 V without depending on the voltage of the power supply connected to the external  $V_{\rm CC}$  pin.

- 2. Current consumed when an external power supply at 1.8 V or higher is used can be held to approximately the same low current as at 1.5 V.

- 3. It is also possible to use the same level of an external power supply voltage and internal power supply voltage, without using the internal power supply step-down circuit.

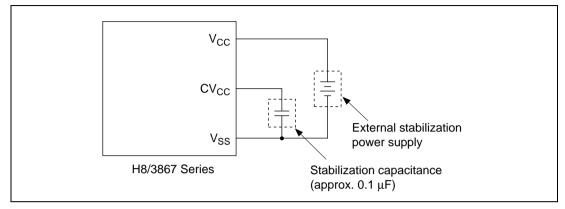

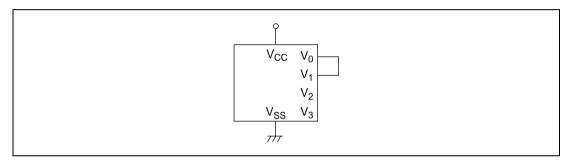

#### Power supply connection when using the internal power supply step-down circuit

An external power supply is connected to the  $V_{cc}$  pin as shown in figure 1, and a capacitance of approximately 1  $\mu F$  is inserted between  $CV_{cc}$  and  $V_{ss}$ . By adding this external circuit, the internal step-down circuit becomes operative.

Figure 1 Power Supply Connection When Using the Internal Power Supply Step-down Circuit

#### Notes on operation using the internal power supply step-down circuit

- 1. The interface to the external circuit uses as reference levels the voltage of the power supply connected to the  $V_{cc}$  pin and the level of the ground connected to the  $V_{ss}$  pin. For example, the high and low port input/output levels become the  $V_{cc}$  level and the  $V_{ss}$  level, respectively.

- 2. When the internal power supply step-down circuit is used, the operating frequency  $f_{osc}$  range is, for a  $V_{CC}$  of 2.2 to 5.5 V,  $f_{osc} = 0.4$  MHz to 2 MHz; otherwise, it is  $f_{osc} = 0.4$  MHz to 1 MHz.

- 3. The LCD power supply and A/D converter analog power supply are not affected by internal step-down processing.

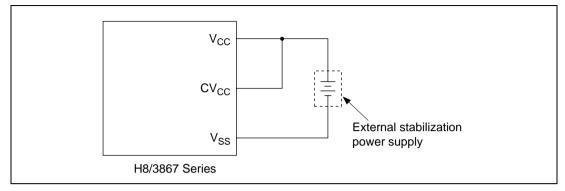

## Power supply connection when not using the internal power supply step-down circuit

The external power supply is connected across the  $V_{cc}$  and  $CV_{cc}$  pins, as shown in figure 2. The external power supply is input directly to the internal power supply circuit.

Figure 2 Power Supply Connection When Not Using the Internal Power Supply Step-down Circuit

#### Note on operation not using the internal power supply step-down circuit

Power supply voltages between 1.8 V and 5.5 V can be used. Operation cannot be guaranteed if a voltage outside this range (less than 1.8 V or more than 5.5 V) is input.

#### Power supply voltage and oscillator frequency ranges

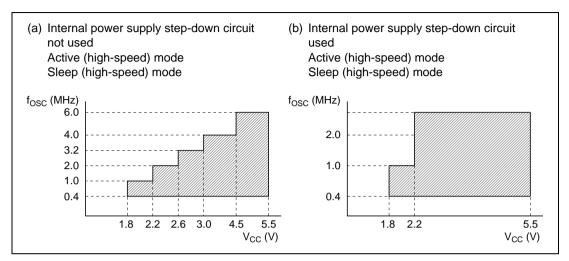

Figure 3 shows the ranges of the power supply voltage and the oscillator frequency (shaded regions).

Figure 3 Power Supply Voltage and Oscillator Frequency Ranges

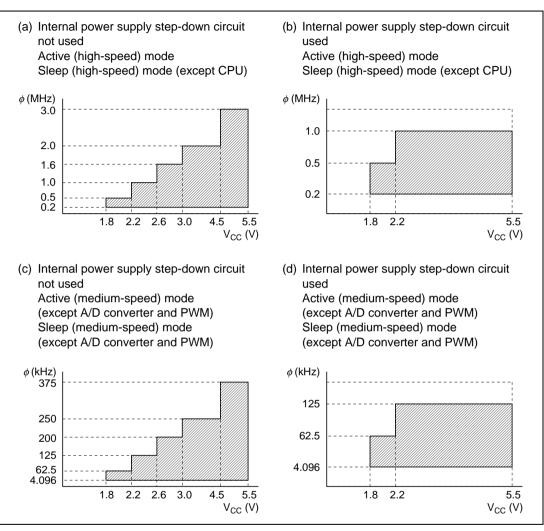

#### Power supply voltage and operating frequency ranges

Figure 4 shows the ranges of the power supply voltage and operating frequency (shaded regions).

Figure 4 Power Supply Voltage and Operating Frequency Ranges

## 2.2 Asynchronous Event Counter Operation

| <b>Asynchronous Event Counter</b> | MCU:           | <b>Functions Used:</b>           |

|-----------------------------------|----------------|----------------------------------|

| Operation                         | H8/3867 Series | Asynchronous Event Counter (AEC) |

## **Specifications**

- 1. Using an asynchronous event counter, once every 524.288 ms there is a transition from subactive mode to active (high-speed) mode, reversal of the port output in active (high-speed) mode, and a transition back to subactive mode.

- 2. The 2-MHz event input is applied to the asynchronous event input L pin (AEVL).

- 3. In this task example, the circuit is used as a 16-bit asynchronous event counter.

#### **Explanation of Functions Used**

- 1. In this task example, an asynchronous event counter (AEC) is used to induce transitions between subactive and active modes and to invert the port output. The features of the AEC are as follows.

- Input external events can be counted asynchronously, independently of basic clock operation.

- The counter has a 16-bit configuration, and can count up to 65,536 events.

- The circuit can also be used as two independent 8-bit event counter channels.

- The counter can be reset or halted under software control.

- Event counter overflow can be detected to automatically generate an interrupt.

- A module standby mode can be employed to set standby mode in module units when not in

use.

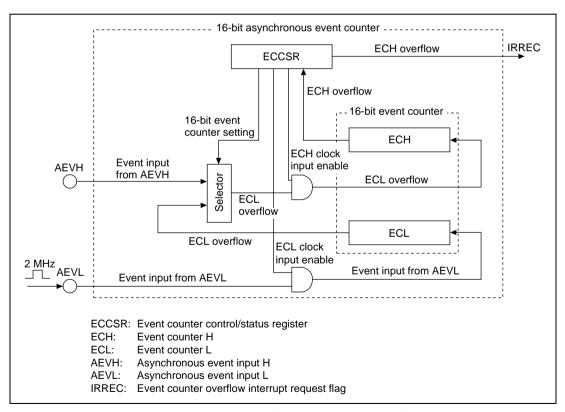

- 2. Figure 1 is a block diagram of the 16-bit asynchronous event counter used in this task example.

Figure 1 Block Diagram of Asynchronous Event Counter

3. Functions of the 16-bit asynchronous event counter are explained in table 1 below.

## Table 1 Functions of the 16-bit Asynchronous Event Counter

Asynchronous event counter interrupt enable (IENEC)

| Table 1   | runctions of the 10-bit Asynchronous Event Counter                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Event cou | nter control/status register (ECCSR)                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Function  | ECCSR is an 8-bit read/write register which is used to detect counter overflow, reset the counter, and halt counting-up operation. Upon reset, ECCSR is initialized to H'00.                                                                                                                                                                                                                                                                                  |

| Event cou | nter H (ECH)                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Function  | ECH is an 8-bit readable up-counter which operates either as an independent 8-bit event counter, or, in combination with ECL, as the counter for the upper eight bits of a 16-bit event counter. As the input clock signal, either the external asynchronous event AEVH pin, or the overflow signal from the lower 8-bit counter ECH can be selected by the CH2 bit of ECCSR. ECH can be cleared to H'00 by software. Upon reset, ECH is initialized to H'00. |

| Event cou | nter L (ECL)                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Function  | ECL is an 8-bit readable up-counter which operates either as an independent 8-bit event counter, or, in combination with ECH, as the counter for the lower eight bits of a 16-bit event counter. As the input clock signal, the event clock from the external asynchronous event AEVL pin is used by the CH2 bit of ECCSR. ECL can be cleared to H'00 by software. Upon reset, ECL is initialized to H'00.                                                    |

| Asynchro  | nous event input H (AEVH)                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Function  | AEVH is the event input pin for input to the event counter H (ECH).                                                                                                                                                                                                                                                                                                                                                                                           |

| Asynchro  | nous event input L (AEVL)                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Function  | AEVL is the event input pin for input to the event counter L (ECL).                                                                                                                                                                                                                                                                                                                                                                                           |

| Asynchro  | nous event counter interrupt request flag (IRREC)                                                                                                                                                                                                                                                                                                                                                                                                             |

| Function  | When an asynchronous event counter interrupt request occurs, IRREC is set to 1. Even when the interrupt is accepted, IRREC is not automatically cleared. To clear IRREC, use software to write 0.                                                                                                                                                                                                                                                             |

|           | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Enables or disables asynchronous event counter interrupt requests.

Function

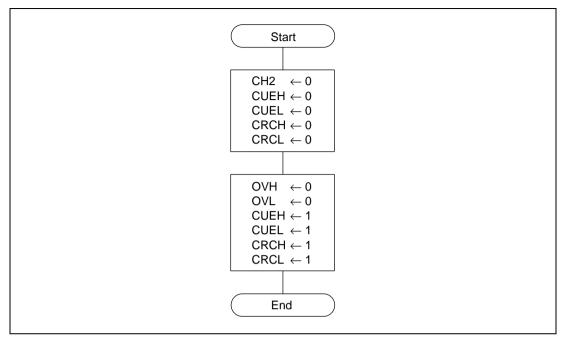

4. Figure 2 shows an example of settings when using the circuit as a 16-bit asynchronous event counter.

Figure 2 Example of Settings for 16-bit Asynchronous Event Counter

Upon reset, CH2 is cleared to 0, so that after reset ECH and ECL operate as a 16-bit event counter. In addition, the circuit will also operate as a 16-bit event counter by using the settings shown in figure 2. The operating clock source is the asynchronous event input from the AEVL pin. When the next clock pulse is input after the count values for both ECH and ECL reach H'FF, ECH and ECL overflow, the OVH flag of ESSSR is set to 1, the count values of ECH and ECL are both returned to H'00, and counting-up is restarted. Upon occurrence of overflow, the IRREC bit of IRR2 is set to 1. At this time, if the IENEC bit of IENR2 is 1, an interrupt request is sent to the CPU.

5. Asynchronous event counter operating modes are indicated in table 2.

Table 2

Asynchronous Event Counter Operating Modes

| Operating<br>Mode |       | Active    | Sleep      | Watch      | Subactive | Subsleep  | Standby    | Module<br>Standby |

|-------------------|-------|-----------|------------|------------|-----------|-----------|------------|-------------------|

| ECCSR             | Reset | Functions | Functions  | Held*      | Functions | Functions | Held*      | Held              |

| ECH               | Reset | Functions | Functions* | Functions* | Functions | Functions | Functions* | Halted            |

| ECL               | Reset | Functions | Functions* | Functions* | Functions | Functions | Functions* | Halted            |

Note: \*When an asynchronous external event is input, the counter is incremented, but the count overflow H/L flags are not affected.

#### 6. Notes on the 16-bit asynchronous event counter

- a. Before reading the values of ECH and ECL, the CUEH and CUEL bits of ECCSR are cleared to 0, to prevent asynchronous events from being input to the counter. If the counter is incremented during reading, the correct value cannot be read. When clearing the CUEH and CUEL bits of ECCSR to 0, ECH and ECL may each be incremented by one.

- b. When the internal power supply step-down circuit is not being used, the maximum clock frequency for input to the AEVH and AEVL pins is 6 MHz when  $V_{\rm cc}$  is 4.5 to 5.5 V, is 4 MHz when  $V_{\rm cc}$  is 3.0 to 5.5 V, and is 3.2 MHz when  $V_{\rm cc}$  is 2.6 to 5.5 V. When the internal power supply step-down circuit is being used or not being used, the maximum clock frequency is 2 MHz when  $V_{\rm cc}$  is 2.2 to 5.5 V, and otherwise is 1 MHz. In addition, the clock high and low widths should be a minimum of 83 ns.

- c. When the AEC is used in 16-bit mode, either the CUEH bit in ECCSR should be set to 1 and then CRCH set to 1, or else after CUEH and CRCH are set simultaneously the clock pulse should be input. Thereafter, the value of CUEH should not be modified during use in 16-bit mode. If, while in 16-bit mode, CUEH is changed, ECH may be erroneously incremented.

- d. Table 3 shows operating modes and event input frequencies.

Table 3 Relation between Operating Modes and AEVH/AEVL Pin Event Input Frequencies

| Mode                                                           |                                          | Maximum AEVH/AEVL Pin Input Clock Frequency                                                                                                                    |

|----------------------------------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-bit mode 8-bit mode Active (high-speed), Sleep (high-speed) |                                          | Internal step-down circuit not used: $V_{cc} = 4.5$ to 5.5 V/6 MHz $V_{cc} = 3.0$ to 5.5 V/8 MHz $V_{cc} = 2.6$ to 5.5 V/3.2 MHz $V_{cc} = 2.2$ to 5.5 V/2 MHz |

|                                                                |                                          | Other than above/1 MHz Internal step-down circuit used: $V_{cc} = 2.2$ to 5.5 V/2 MHz Other than above/1 MHz                                                   |

| 8-bit mode                                                     |                                          |                                                                                                                                                                |

| Active (medium-speed), Sleep (medium-speed)                    | (φ/16)<br>(φ/32)<br>(φ/64)               | $2 \cdot f_{osc}$ $f_{osc}$ $1/2 \cdot f_{osc}$                                                                                                                |

| $f_{osc} = 400 \text{ kHz to } 4 \text{ MHz}$                  | $(\phi/128)$                             | 1/4 · f osc                                                                                                                                                    |

| 8-bit mode                                                     |                                          |                                                                                                                                                                |

| Watch, Subactive, Subsleep, Standby                            | $(\phi_{\rm w}/2)$<br>$(\phi_{\rm w}/4)$ | 1000 kHz<br>500 kHz                                                                                                                                            |

| $f_{osc} = 32.768 \text{ kHz or } 38.4 \text{ kHz}$            | $(\phi_{\text{w}}^{\text{v}}/8)$         | 250 kHz                                                                                                                                                        |

7. Table 4 indicates function allocation in this task example.

**Table 4** Function Allocation

| Function | Function Allocation                                                                                                                    |

|----------|----------------------------------------------------------------------------------------------------------------------------------------|

| ECCSR    | Sets 16-bit asynchronous event counter functions, detects counter overflow, enables/disables input to ECH, ECL of the event clock.     |

| ECH      | Functions as the upper 8-bit up-counter of a 16-bit event counter, taking the ECL overflow signal as the input clock.                  |

| ECL      | Functions as the lower 8-bit up-counter of a 16-bit event counter, taking the external asynchronous event AEVL pin as the input clock. |

| AVEL     | Functions as the input pin for 2-MHz external asynchronous event input.                                                                |

| IRREC    | Indicates whether there has been an asynchronous event counter interrupt request.                                                      |

| IENEC    | Enables/disables asynchronous event counter interrupt requests.                                                                        |

## **Explanation of Operation**

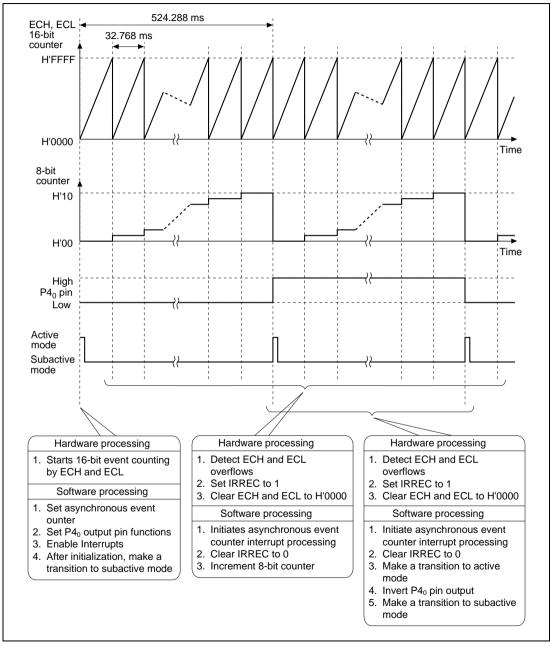

1. Figure 3 illustrates the principle of operation. Asynchronous event counter operation is based on the hardware and software processing indicated in the figure.

Figure 3 Principle of Operation of Asynchronous Event Counter

## **Explanation of Software**

## 1. Explanation of Modules

Table 5 explains the modules in this task example.

**Table 5** Explanation of Modules

| Module Name                                             | Label Name | Function                                                                                                                                                                                                                                                                                                        |

|---------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Main routine                                            | MAIN       | Initializes the stack pointer, RAM, port 4 <sub>0</sub> , asynchronous event counter, and system control register; enables interrupts; executes direct transitions to subactive mode; after 524.288 ms, controls port output and executes direct transitions to active (high-speed) mode and to subactive mode. |

| Asynchronous event counter interrupt processing routine | AECINT     | By routine for processing asynchronous event counter interrupts, clears an interrupt request flag, increments and initializes an 8-bit counter, and after 524.288 ms, sets a flag in RAM.                                                                                                                       |

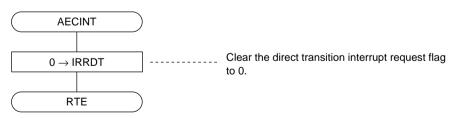

| Direct transition interrupt processing routine          | DTINT      | By routine for processing direct transition interrupts, clears the interrupt request flag                                                                                                                                                                                                                       |

## 2. Explanation of Arguments

In this task example, no arguments are used.

## 3. Explanation of Internal Registers Used

Table 6 gives explanations of the internal registers used in this task example.

Table 6 Explanation of Internal Registers Used

|          | _    |                                                                                                                                                                                                                                                                                                                                                                                                               |                 |         |

|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|

| Register | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                   | RAM<br>Address  | Setting |

| ECCSR    | OVH  | Event counter control/status register (Counter overflow H)  A status flag indicating overflow of ECH.  When OVH = 0, indicates no overflow of ECH  When OVH = 1, indicates ECH overflow                                                                                                                                                                                                                       | H'FF95<br>Bit 7 | 0       |

| ECCSR    | OVL  | Event counter control/status register (Counter overflow L)  A status flag indicating overflow of ECL.  When OVL = 0, indicates no overflow of ECL.  When OVL = 1, indicates ECL overflow                                                                                                                                                                                                                      | H'FF95<br>Bit 6 | 0       |

| ECCSR    | CH2  | <ul> <li>Event counter control/status register (Channel selection)</li> <li>Selects whether to use ECH and ECL as a single-channel 16-bit event counter, or as two independent 8-bit event counter channels.</li> <li>When CH2 = 0, ECH and ECL function as a single concatenated 16-bit event counter</li> <li>When CH2 = 1, ECH and ECL function as two independent 8-bit event counter channels</li> </ul> | H'FF95<br>Bit 4 | 0       |

| ECCSR    | CUEH | <ul> <li>Event counter control/status register (Count-up enable H)</li> <li>Enables or disables the event clock input to ECH.</li> <li>When CUEH = 0, disables the event clock input to ECH</li> <li>When CUEH = 1, enables the event clock input to ECH</li> </ul>                                                                                                                                           |                 | 0       |

Table 6

Explanation of Internal Registers Used (cont)

| Register Name |      | Description                                                                                                           | RAM<br>Address | Setting |

|---------------|------|-----------------------------------------------------------------------------------------------------------------------|----------------|---------|

| ECCSR         | CUEL | Event counter control/status register (Count-up enable L)                                                             | H'FF95         | 0       |

|               |      | Enables or disables the event clock input to ECL.                                                                     | Bit 2          |         |

|               |      | ·                                                                                                                     |                |         |

|               |      | <ul> <li>When CUEL = 0, disables the event clock input<br/>to ECL</li> </ul>                                          |                |         |

|               |      | <ul> <li>When CUEL = 1, enables the event clock input<br/>to ECL</li> </ul>                                           |                |         |

| ECCSR         | CRCH | Event counter control/status register                                                                                 | H'FF95         | 0       |

|               |      | (Counter reset control H)                                                                                             | Bit 1          |         |

|               |      | Controls ECH reset.                                                                                                   |                |         |

|               |      | <ul> <li>When CRCH = 0, ECH is reset</li> </ul>                                                                       |                |         |

|               |      | <ul> <li>When CRCH = 1, ECH reset is canceled and<br/>count-up function is enabled</li> </ul>                         |                |         |

| ECCSR         | CRCL | Event counter control/status register                                                                                 | H'FF95         | 0       |

|               |      | (Counter reset control L)                                                                                             | Bit 0          |         |

|               |      | Controls ECL reset.                                                                                                   |                |         |

|               |      | <ul> <li>When CRCL = 0, ECL is reset</li> </ul>                                                                       |                |         |

|               |      | <ul> <li>When CRCL = 1, ECL reset is canceled and<br/>count-up function is enabled</li> </ul>                         |                |         |

| ECH           |      | Event counter H                                                                                                       | H'FF96         | H'00    |

|               |      | An 8-bit readable up-counter; by combining it with ECL, it can operate as the upper 8 bits of a 16-bit event counter. |                |         |

| ECL           |      | Event counter L                                                                                                       | H'FF97         | H'00    |

|               |      | An 8-bit readable up-counter; by combining it with ECH, it can operate as the lower 8 bits of a 16-bit event counter. |                |         |

Table 6

Explanation of Internal Registers Used (cont)

| Register | Name              | Description                                                                                                                                      | RAM<br>Address  | Setting |

|----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|

| TMA      | TMA3              | Timer mode register A (Internal clock selector 3)                                                                                                | H'FFB0<br>Bit 3 | 1       |

|          |                   | Selects the clock input to TCA.                                                                                                                  | 2 0             |         |

|          |                   | <ul> <li>When TMA3 = 0, PSS is selected as the TCA<br/>input clock source, and an interval timer<br/>function is selected for timer A</li> </ul> |                 |         |

|          |                   | <ul> <li>When TMA3 = 1, PSW is selected as the TCA<br/>input clock source, and a clock time base<br/>function is selected for timer A</li> </ul> |                 |         |

| PMR3     | AVEL              | Port mode register 3 (P3,/AEVL pin function switch)                                                                                              | H'FFCA<br>Bit 7 | 1       |

|          |                   | Determines whether the P3/AEVL pin is to be used as the P3, pin, or as the AEVL pin.                                                             | Dit 1           |         |

|          |                   | <ul> <li>When AEVL = 0, the P3<sub>7</sub>/AEVL pin functions<br/>as the P3<sub>7</sub> pin</li> </ul>                                           |                 |         |

|          |                   | <ul> <li>When AEVL = 1, the P3,/AEVL pin functions<br/>as the AEVL pin</li> </ul>                                                                |                 |         |

| PDR4     | P4 <sub>0</sub>   | Port data register 4<br>(P4 <sub>0</sub> )                                                                                                       | H'FFD7<br>Bit 0 | 0       |

|          |                   | Stores the P4 <sub>o</sub> pin data.                                                                                                             | Dit 0           |         |

|          |                   | <ul> <li>When P4<sub>0</sub> = 0, the P4<sub>0</sub> pin output level is low</li> </ul>                                                          |                 |         |

|          |                   | • When $P4_0 = 1$ , the $P4_0$ pin output level is high                                                                                          |                 |         |

| PCR4     | PCR4 <sub>0</sub> | Port control register 4                                                                                                                          | H'FFE7          | 1       |

|          |                   | (Port control register 4 <sub>0</sub> )                                                                                                          | Bit 0           |         |

|          |                   | Controls the P4 <sub>o</sub> pin input/output.                                                                                                   |                 |         |

|          |                   | <ul> <li>When PCR4<sub>0</sub> = 0, the P4<sub>0</sub> pin functions as<br/>an input pin</li> </ul>                                              |                 |         |

|          |                   | <ul> <li>When PCR4<sub>0</sub> = 1, the P4<sub>0</sub> pin functions as<br/>an output pin</li> </ul>                                             |                 |         |

Table 6

Explanation of Internal Registers Used (cont)

| Register Name |                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RAM<br>Address           | Setting                          |

|---------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------|

| SYSCR1        | SSBY                 | <ul> <li>System control register 1 (Software standby)</li> <li>Carries out transition to standby mode or watch mode.</li> <li>When SSBY = 0, after executing a SLEEP instruction in active mode, causes a transition to sleep mode, or after executing a SLEEP instruction in subactive mode, causes a transition to subsleep mode</li> <li>When SSBY = 1, after executing a SLEEP instruction in active mode, causes a transition to standby mode or to watch mode, or after executing a SLEEP instruction in subactive mode, causes a transition to watch mode</li> </ul>                                                                                                                                                          | H'FFF0<br>Bit 7          | 1                                |

| SYSCR1        | STS2<br>STS1<br>STS0 | System control register 1 (Standby timer select 2 to 0)  Specify the time for the CPU and peripheral functions to wait until the clock stabilizes when standby mode or watch mode is canceled and a transition is made to active mode due to a specific interrupt.  • When STS2 to STS1 = 000, standby time is 8,192 states  • When STS2 to STS1 = 001, standby time is 16,384 states  • When STS2 to STS1 = 010, standby time is 32,768 states  • When STS2 to STS1 = 011, standby time is 65,536 states  • When STS2 to STS1 = 100, standby time is 131,072 states  • When STS2 to STS1 = 101, standby time is 2 states  • When STS2 to STS1 = 111, standby time is 8 states  • When STS2 to STS1 = 111, standby time is 16 states | H'FFF0<br>Bit 6 to bit 4 | STS2 = 0<br>STS1 = 0<br>STS0 = 0 |

Table 6

Explanation of Internal Registers Used (cont)

| Register Name |       | Description                                                                                                                                                                                                  | RAM<br>Address  | Setting |

|---------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|

| SYSCR1        | LSON  | System control register 1 (Low speed on flag)                                                                                                                                                                | H'FFF0<br>Bit 3 | 1       |

|               |       | When watch mode is canceled, selects either the system clock ( $\phi$ ) or the subclock ( $\phi_{\rm sub}$ ) as the CPU operating clock.                                                                     | Dit 0           |         |

|               |       | <ul> <li>When LSON = 0, selects the system clock (φ)<br/>as the CPU operating clock</li> </ul>                                                                                                               |                 |         |

|               |       | • When LSON = 1, selects the subclock ( $\phi_{\rm sub}$ ) as the CPU operating clock                                                                                                                        |                 |         |

| SYSCR2        | NESEL | System control register 2                                                                                                                                                                                    | H'FFF1          | 1       |

|               |       | (Noise elimination sampling frequency selection)                                                                                                                                                             | Bit 4           |         |

|               |       | Selects the frequency at which the watch clock signal $(\phi_{w})$ generated by the subclock oscillator is sampled relative to the oscillator clock $(\phi_{osc})$ generated by the system clock oscillator. |                 |         |

|               |       | • When NESEL = 0, sampling rate is $\phi_{\rm osc}/16$                                                                                                                                                       |                 |         |

|               |       | • When NESEL = 1, sampling rate is $\phi_{\rm osc}$ /4                                                                                                                                                       |                 |         |

Table 6 Explanation of Internal Registers Used (cont)

| Register Name |      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | RAM<br>Address  | Setting |

|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|

| SYSCR2        | DTON | System control register 2 (Direct transfer on flag)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | H'FFF1<br>Bit 3 | 1       |

|               |      | Specifies whether or not to make direct transitions among active (high-speed) mode, active (medium-speed) mode, and subactive mode when a SLEEP instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20              |         |

|               |      | When DTON = 0, if a SLEEP instruction is<br>executed in active mode, a transition to<br>standby mode, watch mode or sleep mode<br>occurs; if a SLEEP instruction is executed in<br>subactive mode, a transition to watch mode or<br>subsleep mode occurs                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                 |         |

|               |      | <ul> <li>When DTON = 1, if a SLEEP instruction is executed in active (high-speed) mode, a direct transition occurs to active (medium-speed) mode (when SSBY = 1, MSON = 1, LSON = 0) or to subactive mode (when SSBY = 1, TMA3 = 1, LSON = 1); if a SLEEP instruction is executed in active (medium-speed) mode, a direct transition occurs to active (high-speed) mode (when SSBY = 0, MSON = 0, LSON = 0) or to subactive mode (when SSBY = 1, TMA3 = 1, LSON = 1); and if a SLEEP instruction is executed in subactive mode, a direct transition occurs to active (high-speed) mode (when SSBY = 1, TMA3 = 1, LSON = 0, MSON = 0) or to active (medium-speed) mode (when SSBY = 1, TMA3 = 1, LSON = 0, MSON = 1)</li> </ul> |                 |         |

Table 6

Explanation of Internal Registers Used (cont)

| Register Name |            | Description                                                                                                                                                                                                                                                                                                                                                                  | RAM<br>Address         | Setting |

|---------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------|

| SYSCR2        | MSON       | System control register 2 (Medium speed on flag)  Selects whether to operate in active (high-speed) mode or in active (medium-speed) mode after cancellation of standby mode, watch mode, or sleep mode.  • When MSON = 0, operates in active (high-speed) mode  • When MSON = 1, operates in active (medium-speed) mode                                                     | H'FFF1<br>Bit 2        | 0       |

| SYSCR2        | SA1<br>SA0 | System control register 1 (Subactive mode clock select 1, 0)  Select the CPU clock rate $(\phi_w/8, \phi_w/4, \phi_w/2)$ in subactive mode.  • When SA1 = 0 and SA0 = 0, $\phi_w/8$ is selected  • When SA1 = 0 and SA0 = 1, $\phi_w/4$ is selected  • When SA1 = 1 and SA0 = *, $\phi_w/2$ is selected  *: Don't care                                                       | H'FFF0<br>Bit 1, bit 0 | 1       |

| IRR2          | IRRDT      | <ul> <li>Interrupt request register 2         (Direct transition interrupt request flag)     </li> <li>Indicates whether there has been a direct transition interrupt request.</li> <li>When IRRDT = 0, indicates that no direct transition interrupt has been requested</li> <li>When IRRDT = 1, indicates that a direct transition interrupt has been requested</li> </ul> | H'FFF7<br>Bit 7        | 0       |

Table 6

Explanation of Internal Registers Used (cont)

| Register Name |       | Description                                                                                                           | RAM<br>Address  | Setting |

|---------------|-------|-----------------------------------------------------------------------------------------------------------------------|-----------------|---------|

| IRR2          | IRREC | Interrupt request register 2 (Asynchronous event counter interrupt request flag)                                      | H'FFF7<br>Bit 0 | 0       |

|               |       | Indicates whether there has been an asynchronous event counter interrupt request.                                     |                 |         |

|               |       | <ul> <li>When IRREC = 0, indicates that no<br/>asynchronous event counter interrupt has been<br/>requested</li> </ul> |                 |         |

|               |       | <ul> <li>When IRREC = 1, indicates that an<br/>asynchronous event counter interrupt has been<br/>requested</li> </ul> |                 |         |

| IENR2         | IENDT | Interrupt enable register 2 (Direct transition interrupt enable)                                                      | H'FFF4<br>Bit 7 | 1       |

|               |       | Enables or disables direct transition interrupt requests.                                                             | Dit 7           |         |

|               |       | <ul> <li>When IENDT = 0, disables direct transition<br/>interrupt requests</li> </ul>                                 |                 |         |

|               |       | <ul> <li>When IENDT = 1, enables direct transition<br/>interrupt requests</li> </ul>                                  |                 |         |

| IENR2         | IENEC | Interrupt enable register 2 (Asynchronous event counter interrupt enable)                                             | H'FFF4<br>Bit 0 | 1       |

|               |       | Enables or disables asynchronous event counter interrupt requests.                                                    |                 |         |

|               |       | <ul> <li>When IENEC = 0, disables asynchronous event<br/>counter interrupt requests</li> </ul>                        |                 |         |

|               |       | <ul> <li>When IENEC = 1, enables asynchronous event<br/>counter interrupt request</li> </ul>                          |                 |         |

## 4. Explanation of RAM Usage

Table 7 explains RAM usage for this task example.

Table 7 Explanation of RAM Usage

| Label Name | Function                                                                         | RAM Address | <b>Modules Used</b> |

|------------|----------------------------------------------------------------------------------|-------------|---------------------|

| FLAG       | Flag indicating 524.288 ms have elapsed.                                         | H'F780      | MAIN, AECINT        |

| CNT        | 8-bit counter to count the number of occurrences of a timer F interrupt request. | H'F781      | MAIN, AECINT        |

#### **Flowchart**

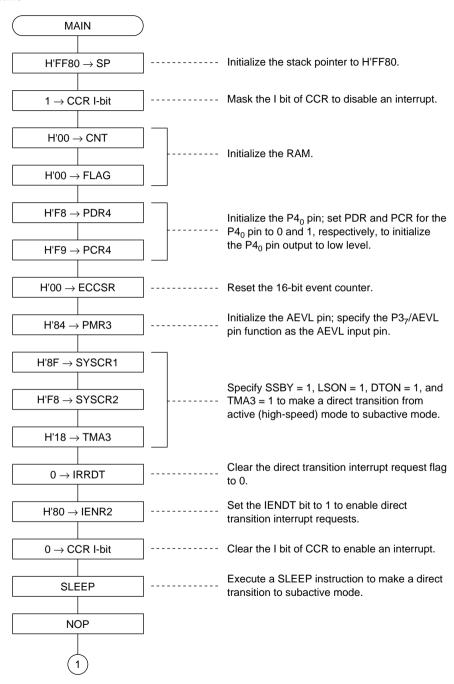

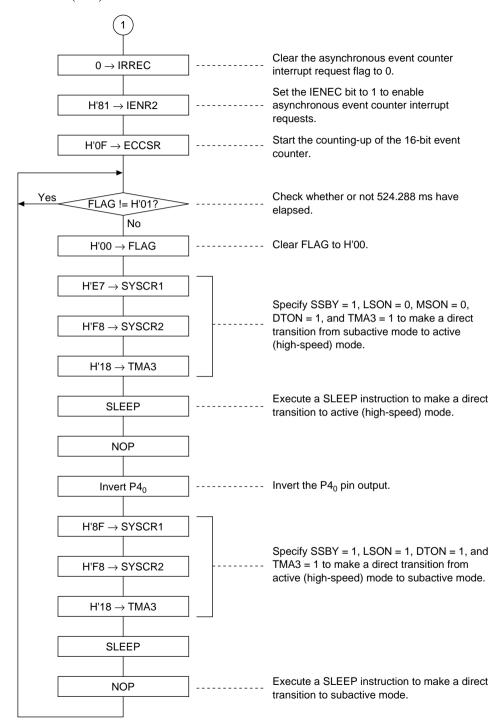

#### 1. Main routine

#### 1. Main routine (cont)

Rev. 1.0, 08/99, page 28 of 151

## HITACHI

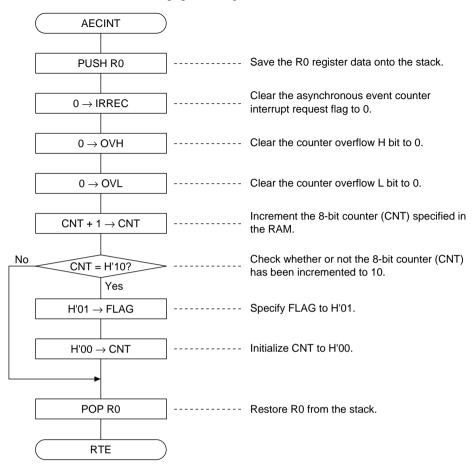

#### 2. Asynchronous event counter interrupt processing routine

## 3. Direct transition interrupt processing routine

#### **Program Lists**

```

H8/3867 Application Note

; *

; *

'Asynchronous Event Counter Control'

; *

Function : AEC(Asynvhronous Event Counter) *

; *

; *

External Clock : 6MHz

Internal Clock : 3MHz

; *

: 32.768kHz

; *

Sub Clock

.cpu 3001

Symbol Defnition

ECCSR

.equ

h'ff95

; Event Counter Control/Status Register

.equ h'ff96

;Event Counter H

ECH

ECL

.equ

h'ff97 ;Event Counter L

h'ffb0 ;Timer Mode Register A

TMA

.equ

h'ffca

PMR3

.equ

;Port Mode Register 3

h'ffd7

;Port Data Register 4

PDR4

.equ

h'ffe7

PCR4

.equ

;Port Control Register 4

.equ

SYSCR1

h'fff0

;System Control Register 1

SYSCR2 .equ h'fff1

;System Control Register 2

.equ h'fff4

IENR2

;Interrupt Enable Register 2

.equ h'fff7 ;Interrupt Request Register 2

IRR2

RAM Allocation

FLAG

.equ h'f780 ;Bit0 : Event Flag

.equ h'f781

;8-bit Counter

CNT

```

Rev. 1.0, 08/99, page 30 of 151

## HITACHI

```

Vector Address

h'0000

.org

.data.w MAIN

; No. 0 Reset Interrupt(H'0000-H'0001)

;

.org h'0008

; No.4 _IRQ0 Interrupt(H'0008-H'0009)

.data.w MAIN

.data.w MAIN

;No.5 _IRQ1 Interrupt(H'000A-H'000B)

.data.w MAIN

; No.6 _IRQ2 Interrupt(H'000C-H'000D)

.data.w MAIN

;No.7 _IRQ3 Interrupt(H'000E-H'000F)

;No.8 _IRQ4 Interrupt(H'0010-H'0011)

.data.w MAIN

.data.w MAIN

; No. 9 _WKP0-_WKP7 Interrupt(H'0012-H'0013)

;

h'0016

.org

; No.11 Timer A Interrupt (H'0016-H'0017)

.data.w MAIN

.data.w AECINT

;No.12 AEC Interrupt(H'0018-H'0019)

.data.w MAIN

; No.13 Timer C Interrupt (H'001A-H'001B)

.data.w MAIN

; No.14 Timer FL Interrupt(H'001C-H'001D)

.data.w MAIN

; No.15 Timer FH Interrupt(H'001E-H'001F)

.data.w MAIN

; No.16 Timer G Interrupt (H'0020-H'0021)

.data.w MAIN

;No.17 SCI31 Interrupt(H'0022-H'0023)

;No.18 SCI32 Interrupt(H'0024-H'0025)

.data.w MAIN

.data.w MAIN

; No.19 A/D Converter Interrupt(H'0026-H'0028)

; No. 20 Direct Transfer Interrupt (H'0028-H'0029)

.data.w DTINT

; *

MAIN: Main Routine

h'1000

.org

;

MAIN:

.equ

#h'ff80.sp ;Initialize Stack Pointer

mov.w

#h'80,ccr ;Interrupt Disable

orc

```

;

```

mov.b

#h'00,r01

;Initialize 8-bit Counter

mov.b

r01,@CNT

mov.b

r01,@FLAG ;Initialize Event Flag

;

#h'f8f9,r0

mov.w

mov.b

r0h,@PDR4

;Initialize P40 PDR

r01,@PCR4 ;Initialize P40 Terminall Function

mov.b

;

#h'00,r01

mov.b

r01,@ECCSR ; Reset 16-bit Event Counter

mov.b

mov.b

#h'84,r01

r01,@PMR3

; Initialize AEVL Terminal Function

mov.b

;

;SSBY="1", LSON="1"

mov.b

#h'8f,r01

r01,@SYSCR1 ;DTON="1", TMA3="1"

mov.b

mov.b

#h'F8,r01

r01,@SYSCR2

mov.b

#H'18,r01

mov.b

mov.b

r01,@TMA

;

bclr

#7,@IRR2

;Clear IRRDT

mov.b

#h'80,r01

mov.b

r01,@IENR2 ;Direct Transfer Interrupt Enable

andc

#h'7f,ccr

;Interrupt Enable

;

sleep

;Direct Transfer to Subactive Mode

nop

;

bclr

#0,@IRR2

;Clear IRREC

mov.b

#h'81,r01

r01,@IENR2 ;Asynchronous Event Counter Interrupt Enable

mov.b

;

#h'0f,r01

mov.b

mov.b

r01,@ECCSR ;16-bit Event counter count-up start

```

;

;

```

btst

#0,r01

;Event Flag = "1" ?

beq

EVTMN

; No.

;

#h'00,r01

mov.b

mov.b

r01,@FLAG ;Clear Event Flag

;

#h'e7f8,r0 ;SSBY="1", LSON="0"

mov.w

r0h,@SYSCR1 ;MSON="0", DTON="1"

mov.b

mov.b

r01,@SYSCR2 ;TMA3="1"

#h'18,r01 ;STS2-0="000"

mov.b

r01,@TMA

mov.b

;

;Direct Transfer to Active Mode

sleep

nop

;

mov.b

@PDR4,r01 ;Load PDR4

bnot

#0,r01

;Invert P40 PDR

r01,@PDR4

mov.b

;Store PDR4

#h'8ff8,r0 ;SSBY="1", LSON="1"

mov.w

r0h,@SYSCR1 ;DTON="1", TMA3="1"

mov.b

mov.b

r01,@SYSCR2

mov.b

#h'18,r01

r01,@TMA

mov.b

;

;Direct Transfer to Subavtive Mode

sleep

nop

;

bra

EVTMN

AECINT : AEC Interrupt Routine

AECINT:

.equ

$

push

r0

;Store r0

```

EVTMN:

mov.b

@FLAG,r01

```

;

bclr #0,@IRR2 ;Clear IRREC

bclr

#7,@ECCSR ;Clear OVH

bclr

#6,@ECCSR ;Clear OVL

;

mov.b

@CNT,r01

;Load CNT

r01

inc

;Increment CNT

cmp.b \#h'10,r01 ; CNT = h'10 ?

EVNT

;Yes. CNT Initialize

beq

mov.b

r01,@CNT ;Store CNT

bra

RNFI

EVNT:

mov.b

#h'01,r01

mov.b r01,@FLAG ;Set Event Flag

mov.b #h'00,r01

mov.b r01,@CNT ;Initialize 8-bit Counter

RNFI

r0

;Restore r0

pop

rte

DTINT : Direct Transfer Interrupt Routine

; ********************

DTINT:

.equ

bclr

#7,@IRR2 ;Clear IRRDT

rte

.end

```

# 2.3 LCD Display with Static Duty

| LCD Display with Static Duty | MCU:           | <b>Functions Used:</b> |

|------------------------------|----------------|------------------------|

|                              | H8/3867 Series | LCD Controller/Driver  |

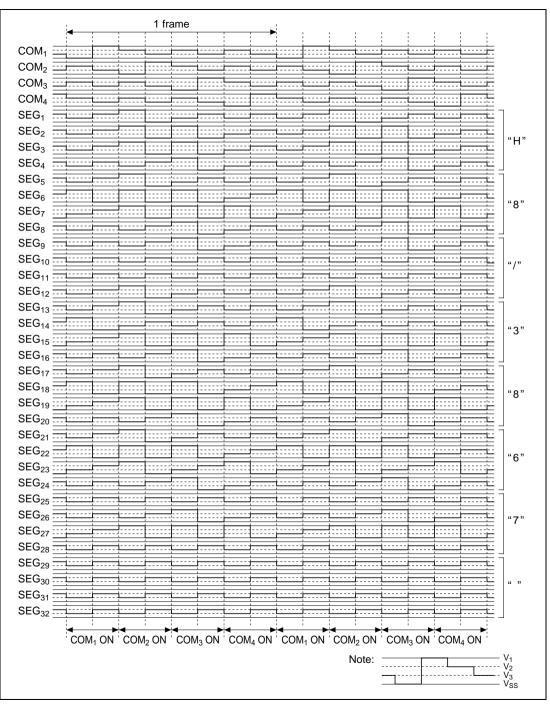

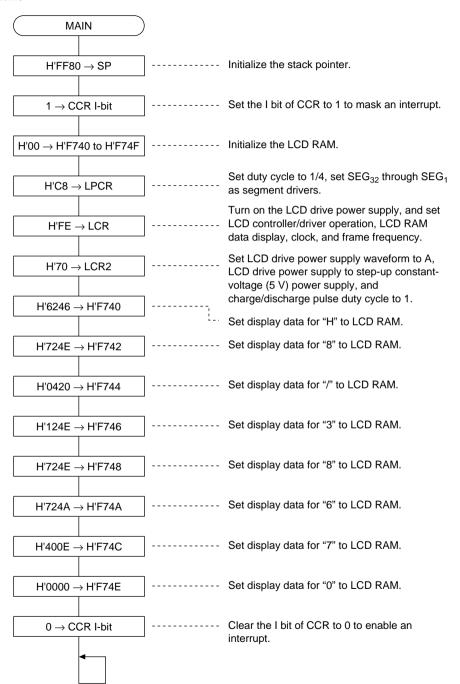

# **Specifications**

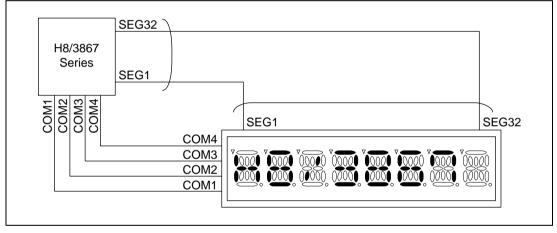

- 1. LCD display is performed using the segment-type LCD controller circuit, LCD driver, and power supply circuit of the H8/3867 Series.

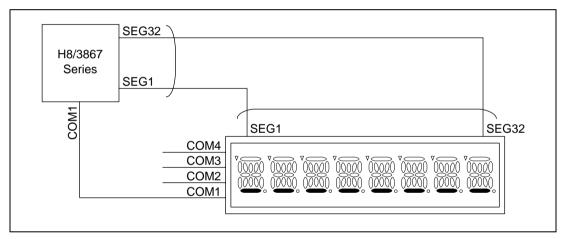

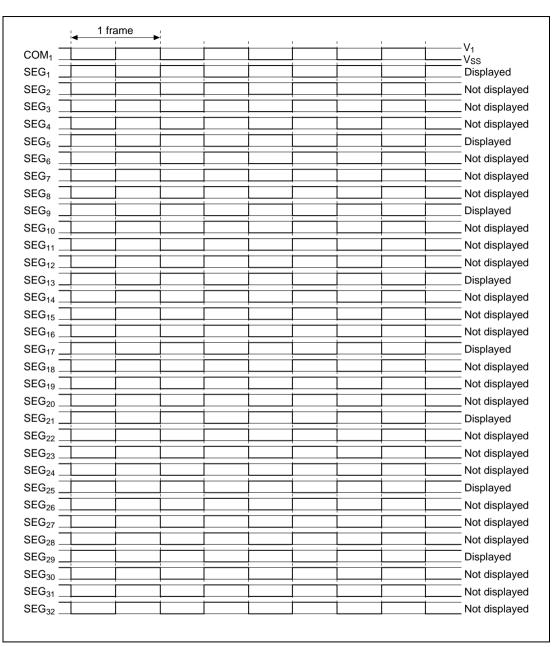

- 2. A single common signal and 32 segment signals are used for LCD display with static duty.

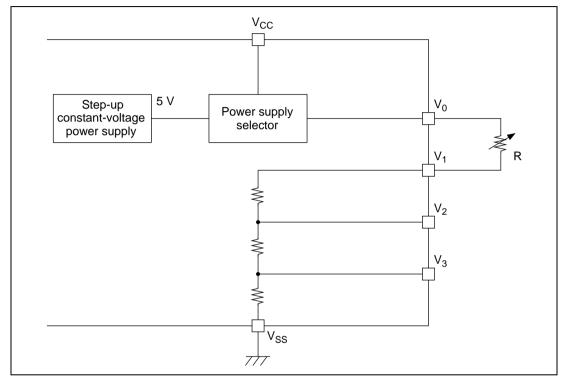

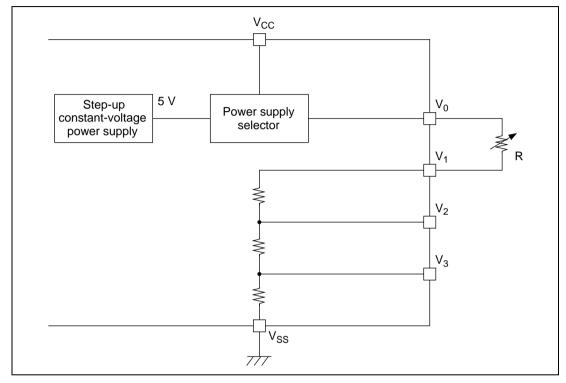

- 3. As the power supply driving the LCD, a step-up constant-voltage power supply (5 V) is used.

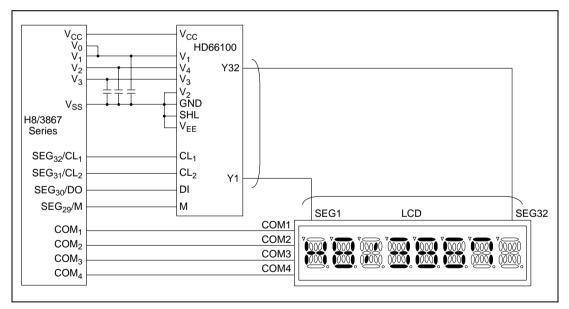

- 4. An example of LCD module connection and an LCD display example for this task example appear in figure 1.

Figure 1 LCD Display Example

## **Explanation of Functions Used**

- 1. In this task example, the LCD controller/driver is used for LCD display. The features of the LCD controller/driver are described below.

- · Display capacity

a. Duty cycle: static

Internal driver: 32 segments

Segment external-expansion driver: 256 segments

b. Duty cycle: 1/2

Internal driver: 32 segment

Segment external-expansion driver: 128 segments

c. Duty cycle: 1/3

Internal driver: 32 segment

Segment external-expansion driver: 64 segments

d. Duty cycle: 1/4

Internal driver: 32 segment

Segment external-expansion driver: 64 segments

- LCD RAM capacity: 8 bits × 32 bytes (256 bits)

- LCD RAM is word-accessible.

- All segment output pins can be used as port pins in eight-pin units.

- Depending on the duty cycle, the common output pins not used can be used for a common double-buffer (parallel connection).

- Display is possible in all operating modes other than standby mode.

- Frame frequency can be selected from among 11 values.

- A power supply split-resistance is built-in, for supply of LCD driver power.

- Use of module standby mode enables a module to be placed in standby mode independently when not used.

- An internal step-up constant-voltage (5 V) power supply enables LCD display even at low voltages.

- A or B waveform can be selected by software.

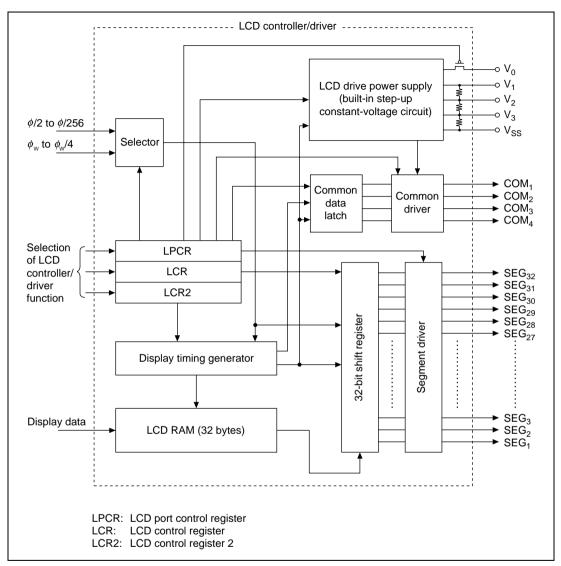

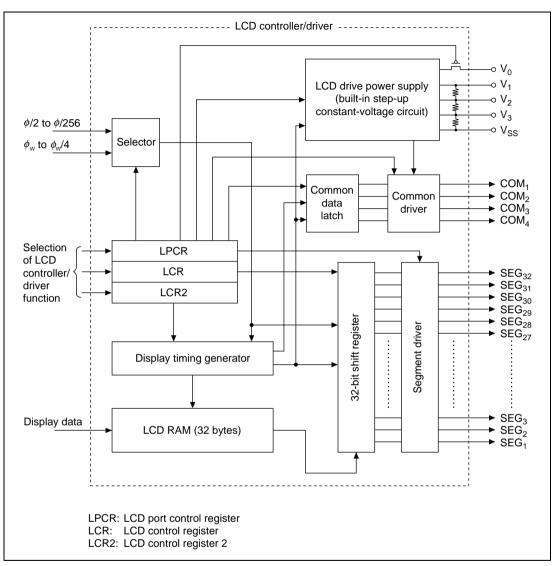

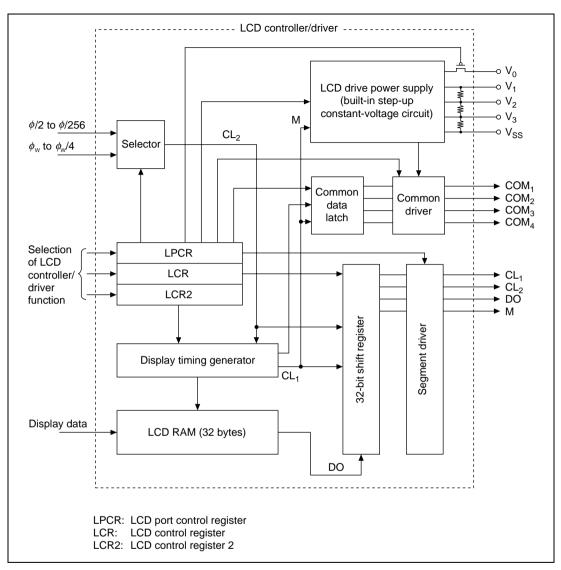

2. Figure 2 is a block diagram of the LCD controller/driver used in this task examples.

Figure 2 Block Diagram of LCD Controller/Driver (LCD Display with Static Duty)

3. Functions of the LCD controller/driver are explained in table 1.

| Table 1  | I CD   | Controller/ | Drivor  | Functions  |

|----------|--------|-------------|---------|------------|

| i anie i | 1 ( 1) | Controller/ | Tiriver | Filhetions |

| LCD port   | control register (LPCR)                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Function   | LPCR is an 8-bit read/write register which selects the duty cycle, the LCD driver and pin functions. LPCR is initialized to H'00 upon reset.                                                                                                                                                                                                                                                                                        |

| LCD contr  | ol register (LCR)                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Function   | LCR is an 8-bit read/write register which turns the LCD drive power supply on and off controls display data, and selects the frame frequency. LCR is initialized to H'80 upor reset.                                                                                                                                                                                                                                                |

| LCD contr  | ol register 2 (LCR2)                                                                                                                                                                                                                                                                                                                                                                                                                |

| Function   | LCR2 is an 8-bit read/write register which controls switching between A and B waveforms, selects the driver power supply, controls the step-up constant-voltage (5 V) power supply, and selects the duty cycle for charge/discharge pulses controlling disconnection of the power supply split-resistance from power supply circuit. LCR2 is initialized to H'60 upon reset.                                                        |

| Segment of | output pins (SEG₃₂ to SEG₁)                                                                                                                                                                                                                                                                                                                                                                                                         |

| Function   | These are pins used for LCD segment driving; all these pins are multiplexed as port pins, and their functions can be selected programmably.                                                                                                                                                                                                                                                                                         |

| Common     | output pins (COM, to COM,)                                                                                                                                                                                                                                                                                                                                                                                                          |

| Function   | These are LCD common driving output pins; under static or 1/2-duty driving, they car be configured in parallel.                                                                                                                                                                                                                                                                                                                     |

| Segment e  | external expansion signal pin (CL₁)                                                                                                                                                                                                                                                                                                                                                                                                 |

| Function   | This is a display data latch clock pin which is multiplexed as SEG <sub>32</sub> .                                                                                                                                                                                                                                                                                                                                                  |

| Segment e  | external expansion signal pin (CL <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                    |

| Function   | This is a display data shift clock pin which is multiplexed as SEG <sub>31</sub> .                                                                                                                                                                                                                                                                                                                                                  |

| Segment e  | external expansion signal pin (M)                                                                                                                                                                                                                                                                                                                                                                                                   |

| Function   | This is an LCD alternation signal pin which is multiplexed as SEG <sub>29</sub> .                                                                                                                                                                                                                                                                                                                                                   |

| Segment e  | external expansion signal pin (DO)                                                                                                                                                                                                                                                                                                                                                                                                  |

| Function   | This is a serial display data signal pin which is multiplexed as $SEG_{30}$ .                                                                                                                                                                                                                                                                                                                                                       |

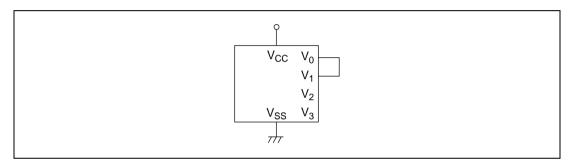

| LCD powe   | r supply pins ( $V_0$ to $V_3$ )                                                                                                                                                                                                                                                                                                                                                                                                    |

| Function   | These pins are used when connecting an external bypass capacitor or when using an external power supply circuit.                                                                                                                                                                                                                                                                                                                    |

| LCD RAM    |                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Function   | Sets the display data. The relation between the LCD RAM and the display segments differs depending on the duty cycle. After the registers necessary for display have been set, instructions similar to the instructions for normal RAM are used to write data corresponding to the duty, and when the display is turned on, display is started automatically. Word/byte access instructions can be used to set data in the LCD RAM. |

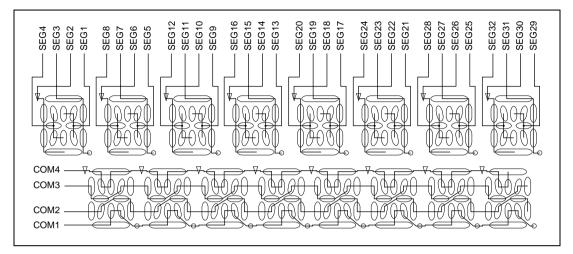

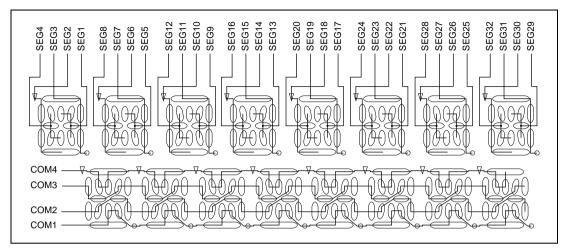

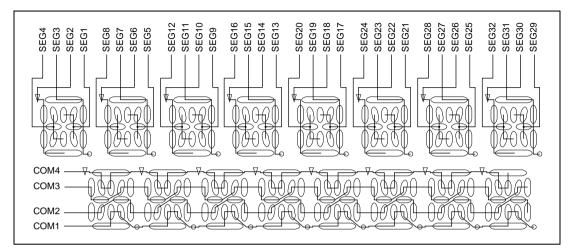

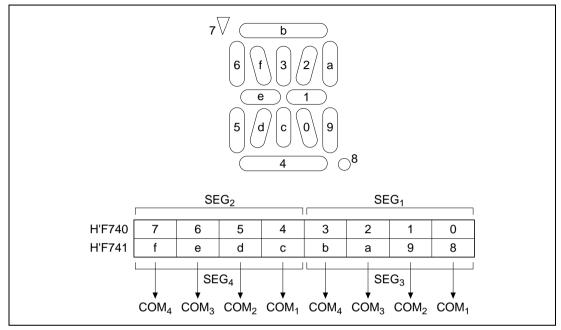

4. In this task example, a 16-line 8-character segment LCD is used for display under static driving. Figure 3 is a diagram showing connections for segment signals and common signals of 16-line 8-character segment LCD used in this task example.

Figure 3 Connections of Segment Signals and Common Signals of the 16-Line 8-Character Segment LCD Used in this Task Example

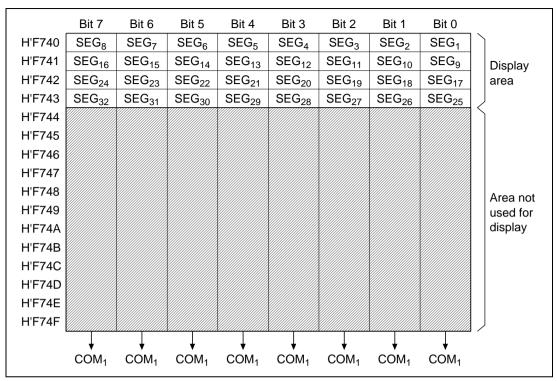

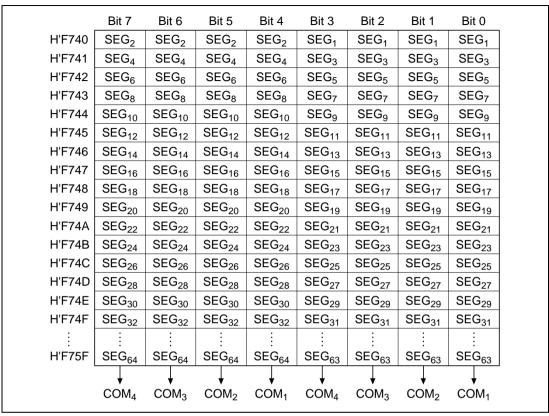

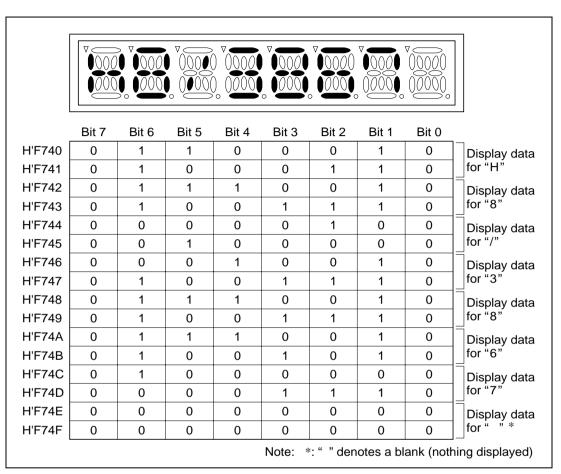

5. Figure 4 shows the LCD RAM mapping under static driving without segment external expansion.

Figure 4 LCD RAM Mapping under Static Driving without Segment External Expansion

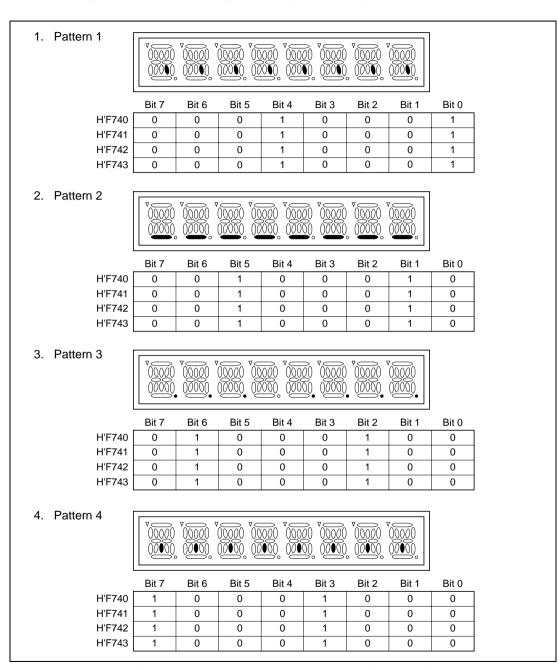

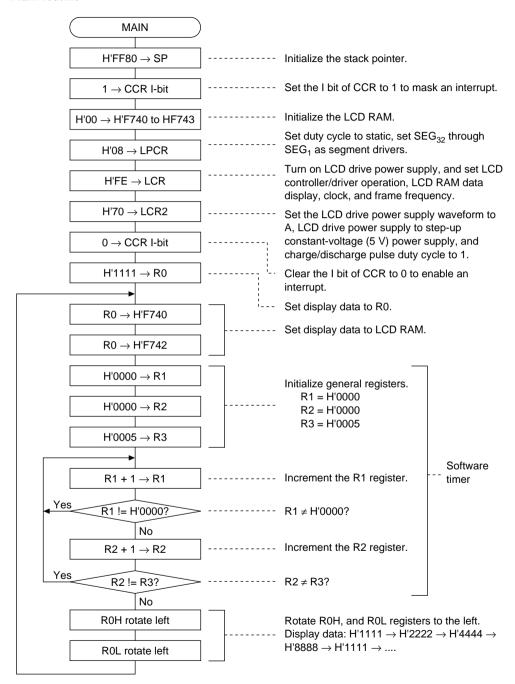

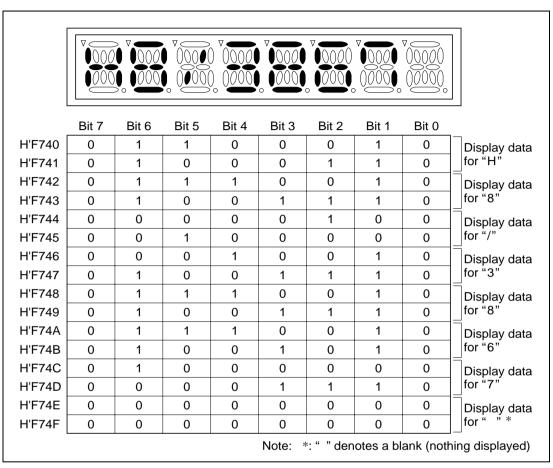

6. Figure 5 shows the relation between the 16-line 8-character segment LCD display and LCD RAM settings used in this task example. In this example, the LCD display is cycled through the series pattern 1 → pattern 2 → pattern 3 → pattern 4 → pattern 1 →.

Figure 5 Relation between LCD Display and LCD RAM Settings

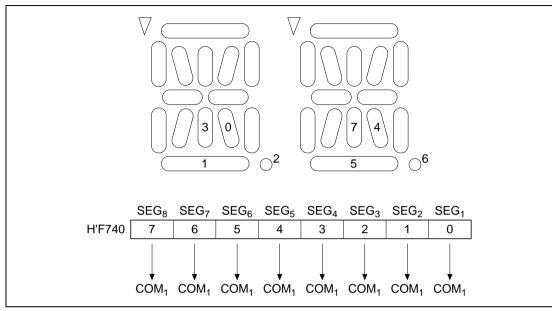

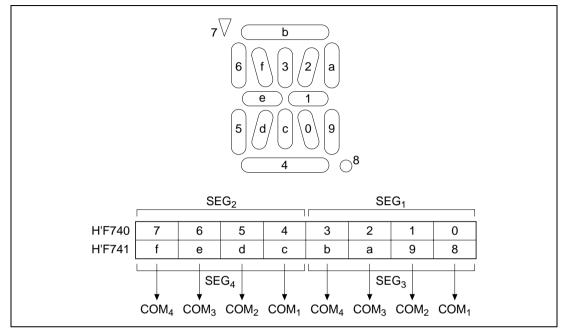

7. Figure 6 shows the relation between the LCD RAM addresses and the segments SEG<sub>1</sub> through SEG<sub>8</sub> of the 16-line 8-character segment LCD. As the figure indicates, when the LCD RAM bits corresponding to 0 through 7 are set to 1 the corresponding LCD areas are lit, and when cleared to 0 the corresponding areas are unlit.

Figure 6 Relation between LCD Lit/Unlit States and LCD RAM Settings

8. Table 2 indicates function allocations in this task example.

**Table 2** Function Allocations

| Function                              | Function Allocation                                                                                                                                                                                                                                       |

|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPCR                                  | Selects duty cycle, LCD driver, and pin functions.                                                                                                                                                                                                        |

| LCR                                   | Turns LCD drive power supply on and off, controls display data, and selects frame frequency.                                                                                                                                                              |

| LCR2                                  | Switches between A and B waveforms, selects drive power supply, controls step-up constant-voltage (5 V) power supply, selects duty cycle for charge/discharge pulses to control disconnection of power supply split-resistance from power supply circuit. |

| SEG <sub>32</sub> to SEG <sub>1</sub> | Used as segment drivers.                                                                                                                                                                                                                                  |

| COM <sub>1</sub>                      | Used as a common driver.                                                                                                                                                                                                                                  |

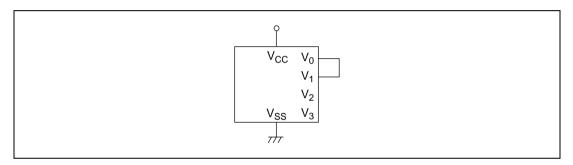

| V <sub>0</sub> , V <sub>1</sub>       | The $V_0$ and $V_1$ pins are shorted in order to use the step-up constant-voltage (5 V) power supply as the LCD drive power supply.                                                                                                                       |

| LCD RAM                               | Sets the LCD display data.                                                                                                                                                                                                                                |

## **Explanation of Functions Used**

- 1. Hardware settings for LCD display are explained below.

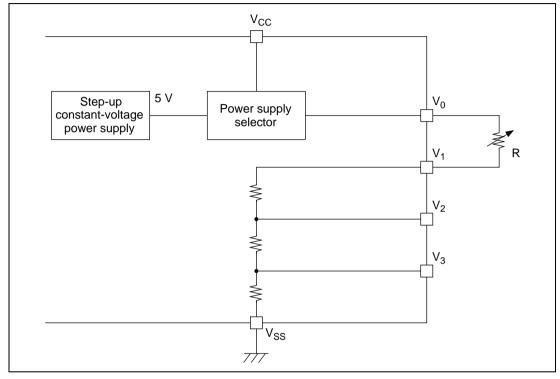

- a. LCD drive power supply settings