#### Introduction

The H8/300H series microcontrollers are high-performance Hitachi-original 16-bit microcontrollers that build in the optimum peripheral equipment for industrial machinery around high-speed H8/300 CPUs that have architecture upwardly compatible with H8/300 CPUs.

The microcontroller puts a CPU, RAM, direct memory access controller (DMAC), bus controller, timers, and a serial communication interface (SCI) on a single chip, making it suitable for a wide range of applications from small to large systems.

This microcontroller technical Q&A covers the H8/3001, H8/3002, H8/3003, H8/3042 series, H8/3032 series, and H8/3048 series.

Table 0-1 H8/300H Series

| Item                                         |              |                 | H8/3003 | H8/3002             | H8/3001           | H8/3042             | H8/3041             | H8/3040             |

|----------------------------------------------|--------------|-----------------|---------|---------------------|-------------------|---------------------|---------------------|---------------------|

| CPU                                          |              |                 | H8/300H | H8/300H             | H8/300H           | H8/300H             | H8/300H             | H8/300H             |

| Memory                                       | ROM          | Mask (byte)     | _       | _                   | _                 | 64 k                | 48 k                | 32 k                |

|                                              |              | ZTAT™*          | _       | _                   | _                 | Yes                 | _                   | _                   |

|                                              | RAM (b       | yte)            | 512     | 512                 | 512               | 2 k                 | 2 k                 | 2 k                 |

| Address sp                                   | ace (byte    | e)              | 16 M    | 16 M                | 16 M              | 16 M                | 16 M                | 16 M                |

| External da                                  | ata bus w    | idth (bit)      | 8/16    | 8/16                | 8/16              | 8/16                | 8/16                | 8/16                |

| Timers                                       | ITU (inte    | •               | 5 ch    | 5 ch                | 5 ch              | 5 ch                | 5 ch                | 5 ch                |

|                                              | Watchd       | og timer        | 1 ch    | 1 ch                | _                 | 1 ch                | 1 ch                | 1 ch                |

| DMA                                          | Memory ↔ I/O |                 | 8 ch    | 4 ch                | _                 | 4 ch                | 4 ch                | 4 ch                |

| controller                                   | Memory       | ∕ ↔ memory      | 4 ch    | 2 ch                | _                 | 2 ch                | 2 ch                | 2 ch                |

| Programmable timing pattern controller (TPC) |              | 16 bits         | 16 bits | 12 bits             | 16 bits           | 16 bits             | 16 bits             |                     |

| SCI (Asynchronous/clock-synchronous)         |              | 2 ch            | 2 ch    | 1 ch                | 2 ch              | 2 ch                | 2 ch                |                     |

| A/D                                          | Resolut      | ion             | 10 bits | 10 bits             | 10 bits           | 10 bits             | 10 bits             | 10 bits             |

| converter                                    | Input ch     | annel           | 8 ch    | 8 ch                | 4 ch              | 8 ch                | 8 ch                | 8 ch                |

|                                              | Externa      | l trigger input | Yes     | Yes                 | Yes               | Yes                 | Yes                 | Yes                 |

| D/A                                          | Resolut      | ion             | _       | _                   | _                 | 8 bits              | 8 bits              | 8 bits              |

| converter                                    | Input ch     | annel           | _       | _                   | _                 | 2 ch                | 2 ch                | 2 ch                |

| Refresh co                                   | ntroller     |                 | On-chip | On-chip             | _                 | On-chip             | On-chip             | On-chip             |

| Interrupts                                   | Externa      | l interrupts    | 9       | 7                   | 4                 | 7                   | 7                   | 7                   |

|                                              | Internal     | Interrupts      | 34      | 30                  | 20                | 30                  | 30                  | 30                  |

| I/O port                                     |              |                 | 58      | 46                  | 32                | 78                  | 78                  | 78                  |

| Package                                      |              |                 | QFP-112 | QFP-100<br>TQFP-100 | QFP-80<br>TQFP-80 | QFP-100<br>TQFP-100 | QFP-100<br>TQFP-100 | QFP-100<br>TQFP-100 |

| Miscellane                                   | ous          |                 | _       | _                   | _                 | _                   | _                   | _                   |

Note: ZTAT (Zero turn around time) is a trademark of Hitachi Ltd.

Table I-1 H8/300H Series (cont)

| Item                                         |                 |                     | H8/3048                          | H8/3047             | H8/3044           | H8/3032           | H8/3031           | H8/3030 |

|----------------------------------------------|-----------------|---------------------|----------------------------------|---------------------|-------------------|-------------------|-------------------|---------|

| CPU                                          |                 |                     | H8/300H                          | H8/300H             | H8/300H           | H8/300H           | H8/300H           | H8/300H |

| Memory                                       | ROM             | Mask (byte)         | 128 k                            | 96 k                | 32 k              | 64 k              | 32 k              | 16 k    |

|                                              |                 | ZTAT <sup>™</sup> * | Yes                              | _                   | _                 | Yes               | _                 | _       |

|                                              | RAM (b          | yte)                | 4 k                              | 4 k                 | 2 k               | 2 k               | 1 k               | 512     |

| Address sp                                   | pace (byte      | e)                  | 16 M                             | 16 M                | 16 M              | 1 M               | 1 M               | 1 M     |

| External da                                  | ata bus w       | idth (bit)          | 8/16                             | 8/16                | 8/16              | 8                 | 8                 | 8       |

| Timers                                       | ITU (inte       | •                   | 5 ch                             | 5 ch                | 5 ch              | 5 ch              | 5 ch              | 5 ch    |

|                                              | Watchd          | og timer            | 1 ch                             | 1 ch                | 1 ch              | 1 ch              | 1 ch              | 1 ch    |

| DMA                                          | Memory ↔ I/O    |                     | 4 ch                             | 4 ch                | 4 ch              | _                 | _                 | _       |

| controller                                   | Memory ↔ memory |                     | 2 ch                             | 2 ch                | 2 ch              | _                 | _                 | _       |

| Programmable timing pattern controller (TPC) |                 | 16 bits             | 16 bits                          | 16 bits             | 16 bits           | 16 bits           | 16 bits           |         |

| SCI (Asynchronous/clock-synchronous)         |                 | 2 ch                | 2 ch                             | 2 ch                | 1 ch              | 1 ch              | 1 ch              |         |

| A/D                                          | Resolution      |                     | 10 bits                          | 10 bits             | 10 bits           | 10 bits           | 10 bits           | 10 bits |

| converter                                    | Input ch        | annel               | 8 ch                             | 8 ch                | 8 ch              | 8 ch              | 8 ch              | 8 ch    |

|                                              | Externa         | l trigger input     | Yes                              | Yes                 | Yes               | Yes               | Yes               | Yes     |

| D/A                                          | Resolut         | ion                 | 8 bits                           | 8 bits              | 8 bits            | _                 | _                 | _       |

| converter                                    | Input ch        | annel               | 2 ch                             | 2 ch                | 2 ch              | _                 | _                 | _       |

| Refresh co                                   | ntroller        |                     | On-chip                          | On-chip             | On-chip           | _                 | _                 | _       |

| Interrupts                                   | Externa         | l interrupts        | 7                                | 7                   | 7                 | 6                 | 6                 | 6       |

|                                              | Internal        | Interrupts          | 30                               | 30                  | 30                | 21                | 21                | 21      |

| I/O port                                     |                 |                     | 78                               | 78                  | 78                | 63                | 63                | 63      |

| Package                                      |                 | QFP-100<br>TQFP-100 | QFP-100<br>TQFP-100              | QFP-100<br>TQFP-100 | QFP-80<br>TQFP-80 | QFP-80<br>TQFP-80 | QFP-80<br>TQFP-80 |         |

| Miscellaneous                                |                 |                     | rt card interfac<br>low-power pe |                     | _                 | _                 | _                 |         |

#### For Users of the Microcontroller Technical Q & A

This *Microcontroller Technical Q & A* was compiled from answers to technical questions we received from Hitachi microcontroller users. We hope that it will be a useful addition to the *H8/300H series user manuals*. Before starting design of products that use microcontrollers, read through the manual to deepen your understanding of microcontroller products and re-familiarize yourself with those areas of difficulty at the design stage.

# **Contents**

|      |                                                                          | Q&A No.                           | Page            |

|------|--------------------------------------------------------------------------|-----------------------------------|-----------------|

|      | tion 1 CPU                                                               |                                   |                 |

| (1)  | The Difference Between the CCR's V Flag and C Flag                       | QA300H-001A                       | 1               |

| (2)  | The Relationship Between Data Size and V Flag Changes                    | QA300H-002A                       | 2               |

| (3)  | Use of General Registers                                                 | QA300H-003A                       | 3               |

|      | •                                                                        |                                   |                 |

|      | Controller                                                               |                                   |                 |

| (1)  | Bus State While the CPU Is Operating                                     | QA300H-004                        | 4               |

| (2)  | Bus Modes                                                                | QA300H-005A                       | 5               |

| (3)  | Setting the Bus Controller in Area 7                                     | QA300H-006A                       | 6               |

| (4)  | External Installation of RAM to 8-Bit Bus Areas                          | QA300H-007A                       | 7               |

| (5)  | Changing the Number of Wait States Inserted Per Area                     | QA300H-008A                       | 8               |

| (6)  | Receiving BREQ in Power-Down Mode                                        | QA300H-009A                       | 10              |

| (7)  | Maximum Wait Time After BREQ Input                                       | QA300H-010A                       | 11              |

| Inte | rrupts                                                                   |                                   |                 |

| (1)  | Interrupt Sampling                                                       | QA300H-011A                       | 12              |

| (2)  | Holding External Interrupts                                              | QA300H-012A                       | 13              |

| (3)  | Receiving NMIs During NMI Processing                                     | QA300H-013A                       | 14              |

| (4)  | Edge Rise and Fall Times for Interrupt Pins                              | QA300H-014A                       | 15              |

| (5)  | Disable Timing for Interrupts                                            | QA300H-015A                       | 16              |

| (6)  | Exception Processing After a Reset                                       | QA300H-016A                       | 17              |

| (7)  | Using the Interrupt Controller                                           | QA300H-017A                       | 18              |

| (8)  | Receiving an External IRQ1 After Returning From<br>Hardware Standby Mode | QA300H-018A                       | 20              |

| (9)  | Interrupt Priority Within Groups                                         | QA300H-019A                       | 21              |

|      | Interrupts When the Bus Is Released                                      | QA300H-020A                       | 22              |

| Rese |                                                                          |                                   |                 |

| (1)  | NMI Sampling Timing and Receiving After Reset                            | QA300H-021A                       | 23              |

|      | Initializing SP After Reset                                              | QA300H-022A                       | 24              |

| (3)  | Pin State During Power-On Reset                                          | QA300H-023A                       | 25              |

| (4)  | RESO Pin Output From RES Pin Input                                       | QA300H-024A                       | 26              |

| (5)  | Connecting RES and RESO Pins                                             | QA300H-025A                       | 27              |

| (6)  | Cautions for Reset Input                                                 | QA300H-026A                       | 28              |

|      | er-Down Mode                                                             | <b>Q</b> - 10 0 0 0 1 0 1 0 1 0 1 |                 |

| (1)  | Executing Instructions When Switching to Hardware Standby Mode           | QA300H-027A                       | 29              |

| (2)  | Mode Pins During Hardware Standby Mode                                   | QA300H-028A                       | 30              |

| (3)  | Returning From Hardware Standby Mode                                     | QA300H-029A                       | 31              |

| (4)  | Interrupt Sampling and Receiving in Sleep Mode                           | QA300H-029A<br>QA300H-030A        | 32              |

| (5)  | Execution Time in Software Standby Mode                                  | QA300H-030A<br>QA300H-031A        | 33              |

| (6)  | Operation When an Interrupt is Requested During Execution or             | QA300H-031A<br>QA300H-032A        | 34              |

| (0)  | While Fetching a SLEEP Instruction                                       | QA500H-032A                       | J <del>'1</del> |

|      |                                                                          |                                   |                 |

|      |                                                                          |                                   |                 |

|      |                                                                                | Q&A No.      | Page |

|------|--------------------------------------------------------------------------------|--------------|------|

| Inst | ructions                                                                       |              |      |

| (1)  | Support for the DAA (DAS) Instruction with the INC (DEC) Instruction           | QA300H-033A  | 36   |

| (2)  | BRA and BRN Instructions                                                       | QA300H-034A  | 37   |

| (3)  | BRN Instruction                                                                | QA300H-035A  | 38   |

| (4)  | The SUBX Instruction                                                           | QA300H-036A  | 39   |

| (5)  | Odd Address Values During STC Instruction Execution                            | QA300H-037A  | 40   |

| (6)  | Interrupts and DMA Transfer Requests While the EEPMOV Instruction Is Executing | QA300H-038A  | 41   |

| (7)  | The Difference Between EEPMOV.B and EEPMOV.W                                   | QA300H-039A  | 42   |

| Mis  | cellaneous                                                                     |              |      |

| (1)  | Cautions on Stack Operation                                                    | QA300H-040A  | 43   |

| (2)  | On-Chip Peripheral LSI Access When the Bus Is Released                         | QA300H-041A  | 44   |

| (3)  | Areas That Can Be Used as ROM by the Vector Table                              | QA300H-042A  | 45   |

| (4)  | Pin State During the Oscillation Settling Time                                 | QA300H-043A  | 46   |

|      | tion 2 On-Chip Peripherals                                                     |              |      |

|      | A Controller                                                                   |              |      |

| (1)  | Receiving DMAC Startup Requests                                                | QA300H-101   | 47   |

| (2)  | Addresses During DMA Transfers                                                 | QA300H-102   | 49   |

| (3)  | TEND Signal Output Timing 1                                                    | QA300H-103   | 50   |

| (4)  | TEND Signal Output Timing 2                                                    | QA300H-104   | 51   |

| (5)  | The Relationship Between the DMAC's DTE and DTIE Bits                          | QA300H-105   | 52   |

| (6)  | DMAC Startup                                                                   | QA300H-106   | 53   |

| (7)  | The DMAC and Timer Interrupts                                                  | QA300H-107   | 54   |

| (8)  | Operation After a DMAC End Interrupt Is Generated 1                            | QA300H-108   | 55   |

| (9)  | Operation After a DMAC End Interrupt Is Generated 2                            | QA300H-109   | 56   |

|      | DMA Transfers Started up by Serial Transfers                                   | QA300H-110   | 57   |

|      | Time Until DMAC Startup by the $\overline{DREQ}$ Pin                           | QA300H-111   | 58   |

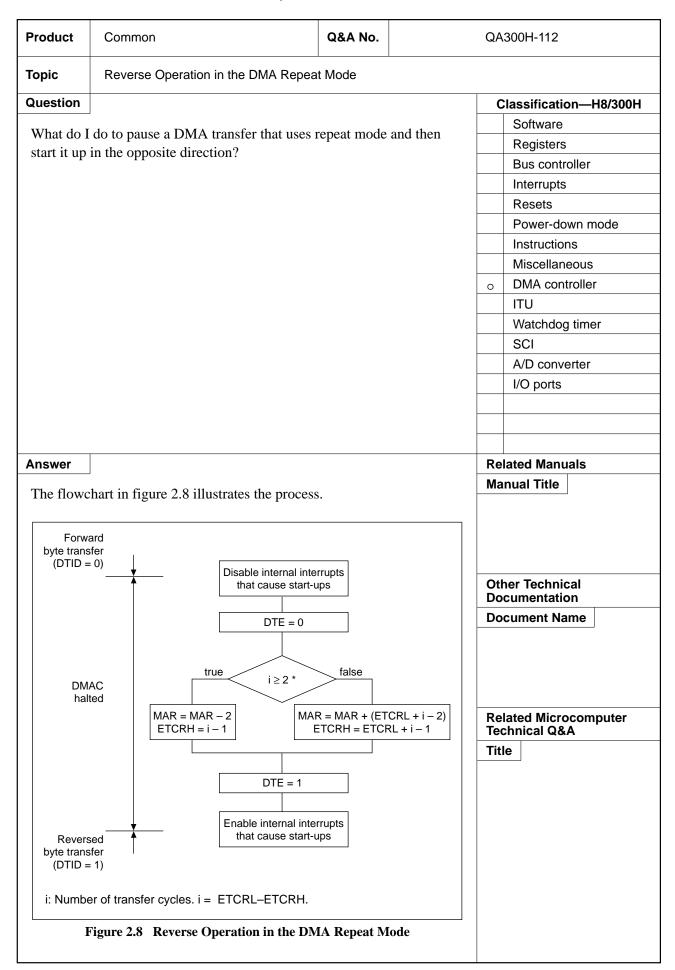

|      | Reverse Operation in the DMA Repeat Mode                                       | QA300H-112   | 59   |

| . ,  | Use of Dual-Function Pins                                                      | QA300H-113   | 60   |

| (14) | I/O Ports and the DREQ Pin                                                     | QA300H-114   | 61   |

| ITU  |                                                                                | O A 200H 115 | 60   |

| (1)  | PWM Mode and Interrupts                                                        | QA300H-115   | 62   |

| (2)  | Clearing the Counters                                                          | QA300H-116   | 63   |

| (3)  | Pulse Output From the ITU                                                      | QA300H-117   | 64   |

| (4)  | ITU Cascade Connections                                                        | QA300H-118   | 65   |

| (5)  | Setting the ITU's PWM Output                                                   | QA300H-119   | 66   |

| (6)  | ITU Output and Port Output                                                     | QA300H-120   | 67   |

| (7)  | ITU Settings                                                                   | QA300H-121   | 69   |

| (8)  | Independent Operation of TCNT4 Using Reset-Synchronized PWM Mode               | QA300H-122   | 72   |

| Wat  | chdog Timer                                                                    |              |      |

| (1)  | Halting the WDT's System Clock                                                 | QA300H-123   | 73   |

|      |                                                                                |              |      |

|                                                             | Q&A No.     | Page |

|-------------------------------------------------------------|-------------|------|

| Serial Communications Interface (SCI)                       |             |      |

| (1) Using the RDR and TDR When the SCI Is Not Being Used    | QA300H-124  | 74   |

| (2) I/O Settings of Clock Pins for the SCI                  | QA300H-125  | 75   |

| (3) Serial I/O Pin State                                    | QA300H-126  | 76   |

| (4) Simultaneous Transmission and Reception with the SCI    | QA300H-127  | 77   |

| (5) RDRF                                                    | QA300H-128  | 78   |

| (6) Setting for Asynchronous Transmission                   | QA300H-129  | 79   |

| (7) How Data Is Transferred to the TDR                      | QA300H-130  | 81   |

| (8) Timing of Setting RDRF                                  | QA300H-131A | 83   |

| (9) Timing of Setting TDRE                                  | QA300H-132A | 85   |

| (10) SCI Reception Errors                                   | QA300H-133  | 87   |

| (11) Operating the SCI in External Clock Mode               | QA300H-134  | 88   |

| (12) System Clocks and SCK Phases                           | QA300H-135  | 89   |

| A/D Converter                                               |             |      |

| (1) Changing the A/D Mode and Channel During A/D Conversion | QA300H-136  | 90   |

| I/O Ports                                                   |             |      |

| (1) Using General-Purpose Ports                             | QA300H-137  | 91   |

| (2) Processing Ports When Not in Use                        | QA300H-138  | 92   |

|                                                             |             |      |

|                                                             |             |      |

|                                                             |             |      |

|                                                             |             |      |

|                                                             |             |      |

|                                                             |             |      |

|                                                             |             |      |

# Section 1 CPU

| Product      | H8/300H                                                      | Q&A No.       |              | QA  | 300H-001A              |

|--------------|--------------------------------------------------------------|---------------|--------------|-----|------------------------|

| Topic        | The Difference Between the CCR's V                           | Flag and C F  | lag          |     |                        |

| Question     |                                                              |               |              |     | Classification—H8/300H |

| G: 41        |                                                              | 1             | .•           |     | Software               |

|              | CCR's V flag and C flag both flag a 1 v                      | when an ope   | ration       | 0   | Registers              |

| overnows     | , what is the difference?                                    |               |              |     | Bus controller         |

|              |                                                              |               |              |     | Interrupts             |

|              |                                                              |               |              |     | Resets                 |

|              |                                                              |               |              |     | Power-down mode        |

|              |                                                              |               |              |     | Instructions           |

|              |                                                              |               |              |     | Miscellaneous          |

|              |                                                              |               |              |     | DMA controller         |

|              |                                                              |               |              |     | ITU                    |

|              |                                                              |               |              |     | Watchdog timer         |

|              |                                                              |               |              |     | SCI                    |

|              |                                                              |               |              |     | A/D converter          |

|              |                                                              |               |              |     | I/O ports              |

|              |                                                              |               |              |     |                        |

|              |                                                              |               |              |     |                        |

|              |                                                              |               |              |     |                        |

| Answer       |                                                              |               |              | Re  | lated Manuals          |

|              |                                                              |               |              | Ma  | nual Title             |

|              | s V flag is accessed to see if an overflo                    |               |              |     |                        |

| -            | eration. In figure 1.1, which is a byte-si                   | _             | -            |     |                        |

|              | when the result is smaller than the negative maximum (H'7F). | ative minim   | um (H 80) or |     |                        |

| iaigei iliai | i die positive maximum (H /F).                               |               |              |     |                        |

|              | H'80 H'00                                                    | H'7F          |              | Otl | ner Technical          |

|              | V flag                                                       | <del></del>   |              |     | cumentation            |

|              | Overflow <                                                   | →Overf        | low          | Do  | cument Name            |

|              | Figure 1.1 V Flag Operati                                    | on            |              |     |                        |

|              |                                                              |               |              |     |                        |

|              | t, the CCR's C flag is accessed to see it                    |               |              |     |                        |

|              | n an unsigned operation. In figure 1.2,                      |               |              |     |                        |

|              | the flag is set to 1 when the result is si                   | naller than t | he minimum   | Re  | lated Microcomputer    |

| (H'00) or    | larger than the maximum (H'FF).                              |               |              |     | chnical Q&A            |

|              | H'00                                                         | H'FF          |              | Tit | ie                     |

|              | C flag                                                       |               |              |     |                        |

|              | Overflow◀                                                    | →Overf        | low          |     |                        |

|              | Figure 1.2 C Flag Operati                                    | on            |              |     |                        |

| References   |                                                              |               |              |     |                        |

| 1/616161166  | 2                                                            |               |              |     |                        |

|              |                                                              |               |              |     |                        |

| Product                | H8/300H                                                                                                  | Q&A No.                                                  | QA                     | 300H-002A                           |  |  |  |

|------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------|------------------------|-------------------------------------|--|--|--|

|                        |                                                                                                          |                                                          |                        |                                     |  |  |  |

| Topic                  | The Relationship Between Data Size and V Flag Changes                                                    |                                                          |                        |                                     |  |  |  |

| Question               |                                                                                                          |                                                          | Classification—H8/300H |                                     |  |  |  |

| Do the ch              | anges in the CCR's V flag vary                                                                           |                                                          | Software               |                                     |  |  |  |

| Do the ch              | unges in the CCR's V mag vary                                                                            | with data size.                                          | 0                      | Registers                           |  |  |  |

|                        |                                                                                                          |                                                          |                        | Bus controller                      |  |  |  |

|                        |                                                                                                          |                                                          |                        | Interrupts                          |  |  |  |

|                        |                                                                                                          |                                                          |                        | Resets                              |  |  |  |

|                        |                                                                                                          |                                                          |                        | Power-down mode                     |  |  |  |

|                        |                                                                                                          |                                                          |                        | Instructions                        |  |  |  |

|                        |                                                                                                          |                                                          |                        | Miscellaneous                       |  |  |  |

|                        |                                                                                                          |                                                          |                        | DMA controller                      |  |  |  |

|                        |                                                                                                          |                                                          |                        | ITU                                 |  |  |  |

|                        |                                                                                                          |                                                          |                        | Watchdog timer                      |  |  |  |

|                        |                                                                                                          |                                                          |                        | SCI                                 |  |  |  |

|                        |                                                                                                          |                                                          | A/D converter          |                                     |  |  |  |

|                        |                                                                                                          |                                                          | I/O ports              |                                     |  |  |  |

|                        |                                                                                                          |                                                          |                        |                                     |  |  |  |

|                        |                                                                                                          |                                                          |                        |                                     |  |  |  |

|                        |                                                                                                          |                                                          |                        |                                     |  |  |  |

| Answer                 |                                                                                                          |                                                          |                        | elated Manuals                      |  |  |  |

| signed ari<br>However, | 's V flag changes when an over-<br>thmetic operation. This operation<br>the timing of the changes in the | on is the same for all data size flag varies as follows: | of a                   | anual Title                         |  |  |  |

| •                      | : When the value is smaller than                                                                         | -                                                        |                        | Other Technical                     |  |  |  |

| • Word                 | d: When the value is smaller that                                                                        | in H'8000 or larger than H"/F                            |                        | ocumentation                        |  |  |  |

| _                      | gword: When the value is smalle<br>H'7FFFFFFF.                                                           | er than H'80000000 or larger                             | Do                     | ocument Name                        |  |  |  |

|                        |                                                                                                          |                                                          | Те                     | elated Microcomputer<br>chnical Q&A |  |  |  |

|                        |                                                                                                          |                                                          | Tit                    | tle                                 |  |  |  |

| Reference              | s                                                                                                        |                                                          |                        |                                     |  |  |  |

| Product                                                             | H8/300H                                                | Q&A No.         |               | QA3  | 300H-003A                                          |

|---------------------------------------------------------------------|--------------------------------------------------------|-----------------|---------------|------|----------------------------------------------------|

| Topic                                                               | Use of General Registers                               |                 |               |      |                                                    |

| Question                                                            |                                                        |                 |               | С    | Classification—H8/300H                             |

| C 1:66-                                                             |                                                        | 16 13 10        | <b>3</b> 1.14 |      | Software                                           |

|                                                                     | ent general registers be used as 8-bit, the same time? | 16-bit, and 3.  | 2-D1t         | 0    | Registers                                          |

| registers a                                                         | t the same time:                                       |                 |               |      | Bus controller                                     |

|                                                                     |                                                        |                 |               |      | Interrupts                                         |

|                                                                     |                                                        |                 |               |      | Resets                                             |

|                                                                     |                                                        |                 |               |      | Power-down mode                                    |

|                                                                     |                                                        |                 |               |      | Instructions                                       |

|                                                                     |                                                        |                 |               |      | Miscellaneous                                      |

|                                                                     |                                                        |                 |               |      | DMA controller                                     |

|                                                                     |                                                        |                 |               |      | ITU                                                |

|                                                                     |                                                        |                 |               |      | Watchdog timer                                     |

|                                                                     |                                                        |                 |               |      | SCI                                                |

|                                                                     |                                                        |                 |               |      | A/D converter                                      |

|                                                                     |                                                        |                 |               |      | I/O ports                                          |

|                                                                     |                                                        |                 |               |      |                                                    |

|                                                                     |                                                        |                 |               |      |                                                    |

|                                                                     |                                                        |                 |               |      |                                                    |

| Answer                                                              |                                                        |                 |               | Re   | lated Manuals                                      |

| Ves Regis                                                           | sters can be set freely for use as shown               | in figure 1 3   | <b>3</b>      | Ma   | nual Title                                         |

| ics. Regis                                                          | sters can be set freely for use as shown               | i ili liguic 1  | <b>,</b> .    |      |                                                    |

|                                                                     |                                                        |                 |               |      |                                                    |

|                                                                     | E0 R0H                                                 | R0L             |               |      |                                                    |

|                                                                     | ER1                                                    |                 |               |      |                                                    |

|                                                                     | ENI                                                    |                 |               |      | ner Technical                                      |

|                                                                     | E2 R2H                                                 | R2L             |               |      | cumentation                                        |

|                                                                     |                                                        | 1               |               | -    | cument Name                                        |

|                                                                     | ER3                                                    |                 |               | 1    | e section 2.4.2, General gisters, in the following |

|                                                                     | E4 I                                                   | <b>E</b> 4      |               |      | nuals:                                             |

|                                                                     |                                                        |                 |               | 1    | H8/3002 Hardware Manual                            |

|                                                                     | E5 I                                                   | E5              |               | 1    | 18/3003 Hardware Manual<br>18/3042 Series Hardware |

|                                                                     | E6 R6H                                                 | R6L             |               |      | Ianual                                             |

|                                                                     | LO KON                                                 | ROL             |               |      | lated Microcomputer                                |

|                                                                     | ER7 (SP)                                               |                 |               |      | chnical Q&A                                        |

| Not                                                                 | e: FR7 is used as the SP without any spe               | cial notice bei | na aiven      | Titl | le                                                 |

| Note: ER7 is used as the SP without any special notice being given. |                                                        |                 |               |      |                                                    |

|                                                                     | Figure 1.3 Use of General Re                           | egisters        |               |      |                                                    |

| References                                                          | <u>s</u>                                               |                 |               |      |                                                    |

|                                                                     |                                                        |                 |               |      |                                                    |

| Product     | H8/300H                                         |                  | Q&A No.   |          | QA                        | 300H-004                                                                                                                                                                                                |  |

|-------------|-------------------------------------------------|------------------|-----------|----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Торіс       | Bus State While the 0                           | CPU Is Operating |           |          |                           |                                                                                                                                                                                                         |  |

| Question    |                                                 |                  |           |          | Classification—H8/300H    |                                                                                                                                                                                                         |  |

| 1 11 11     |                                                 | CDIII. 1         |           |          |                           | Software                                                                                                                                                                                                |  |

| 1. What     | t is the bus state during                       | CPU internal pr  | ocessing? |          |                           | Registers                                                                                                                                                                                               |  |

| 2. What     | t is the bus state after $\overline{L}$         | REQ is receive   | d?        |          | 0                         | Bus controller                                                                                                                                                                                          |  |

|             | That is the bas state after Divide is received. |                  |           |          | Interrupts                |                                                                                                                                                                                                         |  |

| 3. What     | is the bus state after $\overline{E}$           | BREQ is received | d?        |          |                           | Resets                                                                                                                                                                                                  |  |

|             |                                                 |                  |           |          |                           | Power-down mode                                                                                                                                                                                         |  |

|             |                                                 |                  |           |          |                           | Instructions                                                                                                                                                                                            |  |

|             |                                                 |                  |           |          |                           | Miscellaneous                                                                                                                                                                                           |  |

|             |                                                 |                  |           |          |                           | DMA controller                                                                                                                                                                                          |  |

|             |                                                 |                  |           |          |                           | ITU                                                                                                                                                                                                     |  |

|             |                                                 |                  |           |          |                           | Watchdog timer                                                                                                                                                                                          |  |

|             |                                                 |                  |           |          |                           | SCI                                                                                                                                                                                                     |  |

|             |                                                 |                  |           |          |                           | A/D converter                                                                                                                                                                                           |  |

|             |                                                 |                  |           |          |                           | I/O ports                                                                                                                                                                                               |  |

|             |                                                 |                  |           |          |                           |                                                                                                                                                                                                         |  |

|             |                                                 |                  |           |          |                           |                                                                                                                                                                                                         |  |

|             |                                                 |                  |           |          |                           |                                                                                                                                                                                                         |  |

| Answer      |                                                 |                  |           |          |                           | lated Manuals                                                                                                                                                                                           |  |

| See table   | 1.1.                                            |                  |           |          | Ma                        | nual Title                                                                                                                                                                                              |  |

|             |                                                 |                  |           |          |                           |                                                                                                                                                                                                         |  |

| Table 1.1   | <b>Bus State While the C</b>                    | CPU Is Operating | 5         |          |                           |                                                                                                                                                                                                         |  |

| CPU Opera   | ation                                           | Address Bus      | Data l    | Bus      |                           |                                                                                                                                                                                                         |  |

| During inte | rnal CPU processing                             | Hold             | High i    | mpedance | Otl                       | her Technical                                                                                                                                                                                           |  |

| After DREC  | ī is received                                   | DMA address      | DMA       | data     |                           | cumentation                                                                                                                                                                                             |  |

| After BREC  | is received                                     | High impedance   | e High i  | mpedance | Do                        | cument Name                                                                                                                                                                                             |  |

|             |                                                 |                  |           |          | Rel ma • H • H • H • M Re | e figure 6.18, External Bus<br>lease State, in the following<br>nuals:<br>18/3002 Hardware Manual<br>18/3003 Hardware Manual<br>18/3042 Series Hardware<br>Manual<br>lated Microcomputer<br>chnical Q&A |  |

| References  | 3                                               |                  |           |          | 1                         |                                                                                                                                                                                                         |  |

| Product                       | H8/300H                                                                                                                                                                                                 | Q&A No.                                        | QA300H-005A                          |                                                                                                                                                                                                         |  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Topic                         | Bus Modes                                                                                                                                                                                               |                                                |                                      |                                                                                                                                                                                                         |  |  |

| of the AB                     | 2.1 of the H8/3003 Hardware Manual s<br>WCR is cleared to 0, the bus mode becall areas can be accessed in 16-bit mod                                                                                    | omes 16 bits                                   |                                      | Classification—H8/300H  Software  Registers  Bus controller  Interrupts  Resets  Power-down mode  Instructions  Miscellaneous  DMA controller  ITU  Watchdog timer  SCI  A/D converter  I/O ports       |  |  |

| Answer                        |                                                                                                                                                                                                         |                                                |                                      | Related Manuals                                                                                                                                                                                         |  |  |

| ABWCR bit is clear might bett | a a given bit ADWn (bus width control (bus width control register) is cleared to red can be accessed in 16-bit mode. The ter read, "When even one area is set as a OH CPU goes into 16-bit bus mode and | o 0, only that<br>e manual de<br>a 16-bit acce | at area whose scription essed space, | Manual Title                                                                                                                                                                                            |  |  |

|                               | e data bus. This means that I/O ports th                                                                                                                                                                |                                                |                                      | Other Technical                                                                                                                                                                                         |  |  |

| lower data<br>access spa      | a bus (D7–D0) cannot be used as genera                                                                                                                                                                  | al ports, eve                                  | n in an 8-bit                        | Document Name  See table 6.4, Address Space and Data Bus Used, in the following manuals:  • H8/3002 Hardware Manual  • H8/3003 Hardware Manual  • H8/3042 Series Hardware Manual  Related Microcomputer |  |  |

|                               |                                                                                                                                                                                                         |                                                |                                      | Technical Q&A                                                                                                                                                                                           |  |  |

| References                    | s l                                                                                                                                                                                                     |                                                |                                      | Title                                                                                                                                                                                                   |  |  |

| Product     | H8/300H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Q&A No.       |              | QA3   | 00H-006A                  |                            |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------|-------|---------------------------|----------------------------|

| Торіс       | Setting the Bus Controller in Area 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |              |       |                           |                            |

| Question    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |              | С     | lassification             | on—H8/300H                 |

| a.          | 7 . 1: DAM 1: 4 11/6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               | 1 ' 1        |       | Software                  |                            |

|             | 17 mixes on-chip RAM and internal I/O he bus widths and access states set by the states are the | -             |              |       | Registers                 |                            |

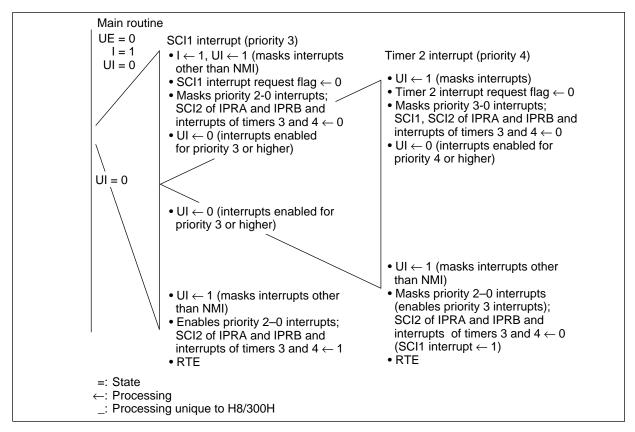

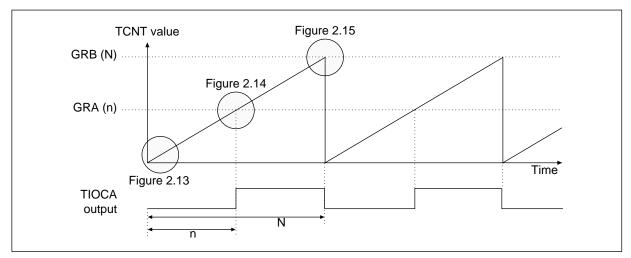

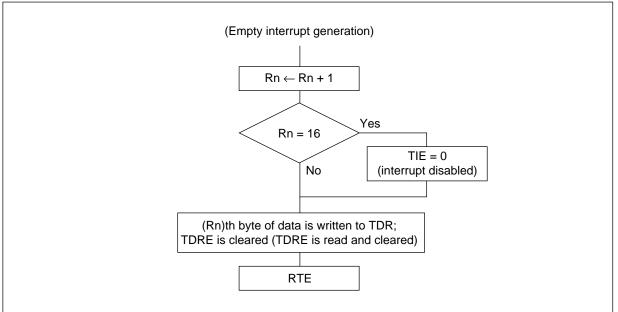

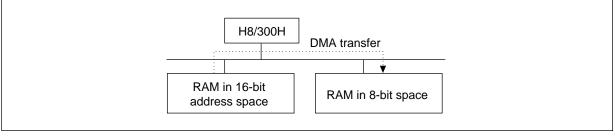

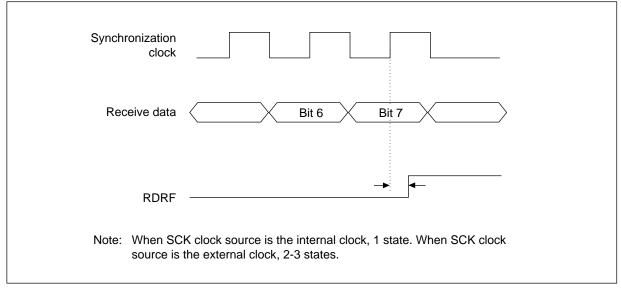

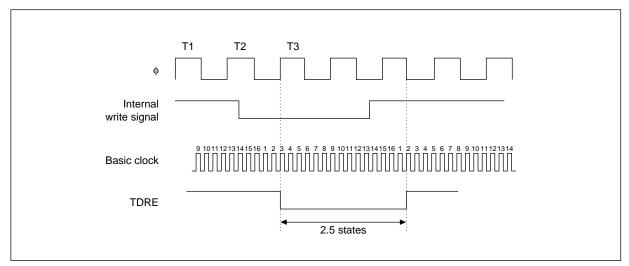

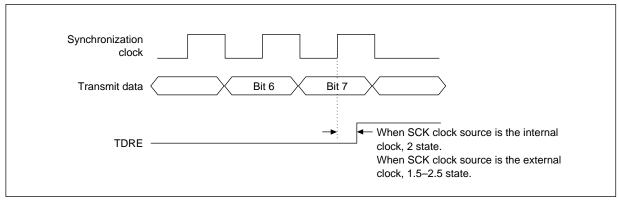

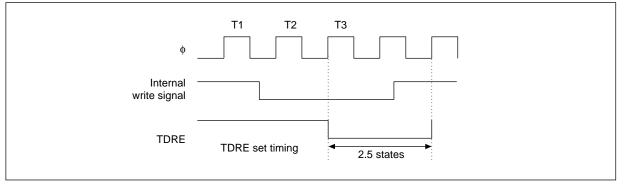

| aleas ale i | the bus widths and access states set by t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ine ous conti | ioner vanu:  | 0     | Bus contr                 | oller                      |