# **Consumer Microcircuits Limited**

PRODUCT INFORMATION

# **FX709** Voice Store Retrieve CVSD Codec

Publication D/709/6 July 1994

## Features/Applications

- CVSD Encode + Decode

- Programmable Clock Rates

- Programmable Voice Filters

- Voice Power Output

- Voice Spectrum Monitor

- 8-bit Memory/Instruction I/O

- Processor Interface

- Voice Message Mailbox

- Status Annunciators

- Re-try Message Forward

- Voice Security Scrambling

- Voice Data Communications

- Time/Frequency Companding

- Audio Delay Functions

**FX709**

# **Brief Description**

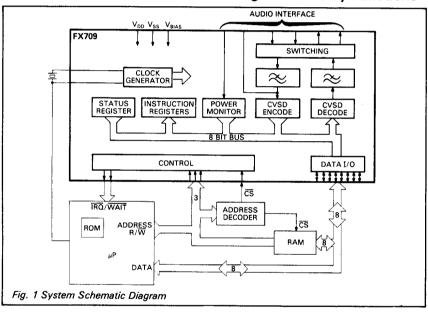

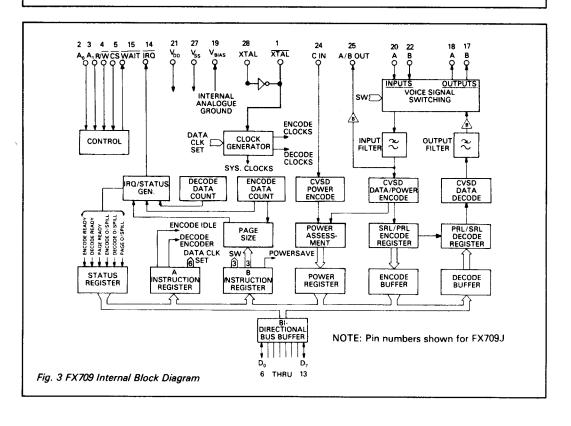

The FX709 is an audio-digital interface codec for microprocessor controlled Voice Store and Retrieve applications.

In encode, audio input signals are bandlimited by a lowpass filter and digitised by a CVSD 1-bit serial encoder. After conversion to 8-bit parallel format, encoded data is read to the I/O bus for storage in memory. In decode, memory contents written into the I/O port are converted back to 1-bit serial form and decoded by a CVSD decoder. The decoder output is lowpass filtered and output as retrieved audio.

The audio encode/decode functions are independently controlled, permitting concurrent or asynchronous VSR operations

to be performed. Time and frequency companding is available via independently programmable encode/decode data rates and filter cut-offs.

Support for VOX functions and 'Pause' memory management is provided by the power assessment register.

This contains two 4-bit numbers representing the average signal levels into the data encoder and a replica encoder over a programmable averaging period.

The device instruction set includes input/output signal switching and a standby powerdown function. The FX709 is a

lowpower CMOS circuit and uses a single

5 volt supply.

# **Function**

| FX709J/LH                          | Will Control of the c |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                  | Xtal: Output of clock oscillator inverter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 3 4                                | A <sub>0</sub> : A <sub>1</sub> : These pins determine which register may be addressed via the I/0 port. R/W:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                    | A, R/W Register 0 0 0 0 'A' instruction 1 0 0 'B' instruction 0 1 0 Decoder 1 1 0 No Register 0 0 1 Status 1 0 1 Power 0 1 1 Encoder 1 1 No Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5                                  | $\overline{\text{CS}}$ : Chip Select input, this input has a 1 M $\Omega$ pullup to $V_{DD}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6<br>7<br>8<br>9<br>10<br>11<br>12 | D <sub>0</sub> : D <sub>1</sub> : D <sub>2</sub> : D <sub>3</sub> : V0 Port D <sub>4</sub> : D <sub>5</sub> : D <sub>6</sub> : D <sub>7</sub> :                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 14                                 | <b>IRQ:</b> Interrupt Request Output, this pin is the output of the interrupt request generator. This device can be "wire OR'd" with other active-low components. See section on Interrupt Requests. (100k $\Omega$ internal pullup to $V_{DD}$ ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

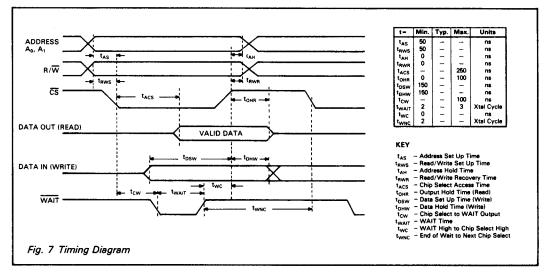

| 15                                 | WAIT Output: The circuit requires a minimum Chip Select time of t <sub>ACS</sub> . If the host μP has a CS time of less than this the WAIT output must be used to delay the μP when accessing the FX709. (See Figure 7). (100kΩ internal pullup to V <sub>DD</sub> ).  NOTE: If the WAIT output is to be used, then to prevent spurious operation of this function during Power-Up, it is recommended that:  a: Power-Up of the FX709 is delayed until μP Power-Up is complete, or, b: The Chip Select input is held open-circuit during the FX709 Power-Up sequence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16                                 | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

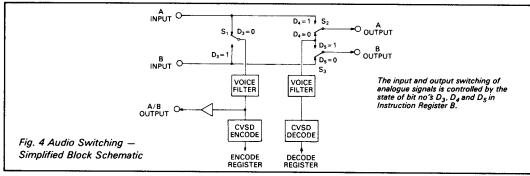

| 17                                 | Analogue Output B: (See Figure 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 18                                 | Analogue Output A: (See Figure 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 19                                 | $V_{\text{pias}}$ : The bias or analogue ground pin and is internally set to $V_{\text{po}}/2$ . It should be decoupled to $V_{\text{ss}}$ with a capacitor of 1.0 $\mu$ F (min.).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 20                                 | Analogue Input A: (See Figure 2, Note 4 and Figure 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 21                                 | V <sub>pp</sub> : Positive Supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 22                                 | Analogue Input B: (See Figure 2, Note 4 and Figure 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 23                                 | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 24                                 | Analogue Input C: This is the analogue input to the power encoder.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 25                                 | Analogue Output A/B: (See Figure 4).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 26                                 | No connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 27                                 | V <sub>ss</sub> : Negative supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 28                                 | Xtal/Clock Input: This is the input to the clock oscillator inverter. A 1.0 MHz Xtal input or externally derived clock is injected at this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

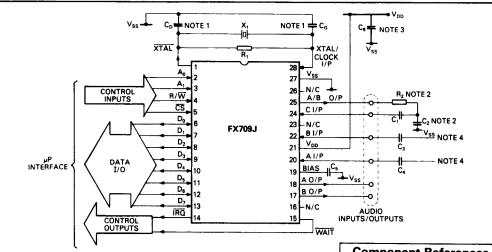

#### NOTES:

- C<sub>G</sub> used to reduce voltage overshoot. Refer to CML Crystal application Applications Note D/XT/1 April 86.

- R<sub>2</sub> C<sub>2</sub> forms a lowpass filter input to 'C' input power assessment circuit. The values shown represent a 820Hz lowpass although other cutoff frequencies may be selected depending on the application — see page 9.

- Additional decoupling may be necessary for noisy supplies.

- 4. To prevent unwanted internal oscillations at the Encoder input pins, the source impedance to these inputs must be less than 100Ω. Output idle channel noise levels will improve with even lower source impedances.

| Compor           | ent Ref       | erences   |

|------------------|---------------|-----------|

|                  | Unit          | Tolerance |

| Component        | Value         | 1         |

| R <sub>1</sub>   | >1M           | ] ±10%    |

| R <sub>2</sub>   | 5. <b>6</b> k | ] =10%    |

| C <sub>G</sub>   | 68p           | Note 1    |

| [ C <sub>D</sub> | 33p           | Note 1    |

| C <sub>1</sub>   | 0.1μ          | רו        |

| C <sub>2</sub>   | 33n           |           |

| C <sub>3</sub>   | 0.1μ          | +20%      |

| C₄               | 0.1μ          | 120%      |

| C <sub>5</sub>   | 1.0µ min      | 11        |

| C <sub>6</sub>   | 0.1μ          | ا ا       |

Fig. 2 External Component Connections

## **Analogue Switching**

### Frequency and Data Rate Control

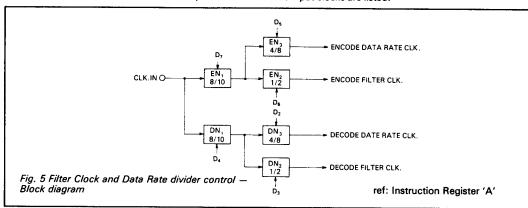

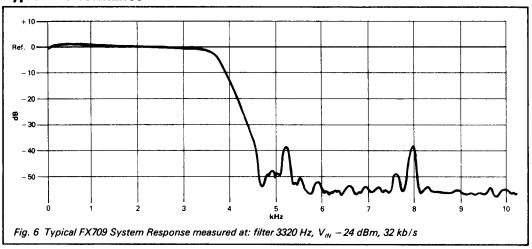

Six bits of instruction Register A  $(D_2-D_7)$  control the data rates of the encoder and decoder and the bandwidths of the filters for the encoder and decoder. The configuration of the frequency dividers is as shown in the diagrams below and obtainable combinations of frequencies with various input clocks are listed.

|                                 | CLOCK    | N1          | N2          | FILTER<br>CLOCK<br>(Hz) | LOWPASS<br>FILTER BW<br>PB. ± 1dB | N3 | DATA<br>CLOCK<br>(kbs) |

|---------------------------------|----------|-------------|-------------|-------------------------|-----------------------------------|----|------------------------|

|                                 | 2MHz     | 8           | 2           | 125k                    | 3320                              | 4  | 62.5                   |

|                                 | "        | 8           | 2<br>2      | 125k                    | 3320                              | 8  | 31.25                  |

|                                 | **       | 10          | 2           | 100k                    | 2656                              | 4  | 50.0                   |

|                                 | "        | 10          | 2           | 100k                    | 2656                              | 8  | 25.0                   |

|                                 | 1MHz     | 8           | 1           | 125k                    | 3320                              | 4  | 31.25                  |

|                                 | "        | 8<br>8<br>8 | 1           | 125k                    | 3320                              | 8  | 15.625                 |

|                                 | **       | 8           | 2           | 62.5k                   | 1660                              | 4  | 31.25*                 |

|                                 | "        | 8           | 2           | 62.5k                   | 1660                              | 8  | 15.625*                |

|                                 | ,,       | 10          | 1           | 100k                    | 2656                              | 4  | 25.0                   |

|                                 | **       | 10          | 1           | 100k                    | 2656                              | 8  | 12.5                   |

|                                 | ,,       | 10          | 2<br>2      | 50k                     | 1328                              | 4  | 25.0*                  |

| *Caution: Although possible,    | ,,       | 10          | 2           | 50k                     | 1328                              | 8  | 12.5*                  |

| the Codec insertion loss is not | 2.048MHz | 8           | 2           | 128k                    | 3400                              | 4  | 64.0                   |

| according to the specification  | ,,       | 8           | 2           | 128k                    | 3400                              | 8  | 32.0                   |

| at these settings.              | ,,       | 10          | 2<br>2<br>2 | 102.4k                  | 2720                              | 4  | 51.2                   |

| (see Page 10).                  | "        | 10          | 2           | 102.4k                  | 2720                              | 8  | 25.6                   |

| 1000 / Ugo 10/.                 | 1.024MHz | 8           | 1           | 128k                    | 3400                              | 4  | 32.0                   |

|                                 | **       | 8           | 1           | 128k                    | 3400                              | 8  | 16.0                   |

|                                 | ,,       | 8<br>8<br>8 | 2           | 64k                     | 1700                              | 4  | 32.0*                  |

|                                 | ,,       | 8           | 2           | 64k                     | 1700                              | 8  | 16.0*                  |

|                                 | "        | 10          | 1           | 102.4k                  | 2720                              | 4  | 25.6                   |

|                                 | **       | 10          | 1           | 102.4k                  | 2720                              | 8  | 12.6                   |

|                                 | "        | 10          | 2           | 51.2k                   | 1360                              | 4  | 25.6*                  |

|                                 | **       | 10          | 2           | 51.2k                   | 1360                              | 8  | 12.6*                  |

|                                 | 614.4kHz | 8           | 1           | 76.8k                   | 2040                              | 8  | 9.6*                   |

|                                 | 768.0kHz | 10          | 1           | 76.8k                   | 2040                              | 8  | 9.6*                   |

Table 1 Possible combinations of clock input frequency, filter cutoff (Hz) and Data Clock (kbs)

# **Register Truth Tables**

The following tables describe the function of each bit within each register. 'Address Input' logic states are shown in the top right hand corner of each table. The following registers are described below:

Instruction Register 'A' [IRA] pages 5 and 6 Instruction Register 'B' [IRB] pages 6 and 7 Status Register [SR] pages 8 and 9 Power Register [PR] page 9

| IRA            |                                           | ı              | NSTRUCTION        | REGISTER 'A' $A_0 = 0$ $A_1 = 0$ $R\overline{W} = 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-------------------------------------------|----------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit            | Function<br>Name                          | Logic<br>State | References        | NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D <sub>0</sub> | Encoder<br>Idle                           | 1              | SRD₃              | D <sub>o</sub> sets the encoder idle/normal mode of operation.  FORCED: Forces the encode register to fill with a 1010101 idle pattern. Note: incoming encoded data is still available for the power assessment circuits.                                                                                                                                                                                                                                                                                            |

|                |                                           | 0              |                   | NORMAL: Allows the encode register to fill with encoded data. Data is transferred to the encode buffer during the last bit of the encode byte.                                                                                                                                                                                                                                                                                                                                                                       |

| D <sub>1</sub> | Decoder<br>Data<br>Source In<br>Overspill | 0              | SRD₄              | D <sub>1</sub> determines the source of data for the decoder.  ENCODER: Internally connects the output of the encode register to the input of the decode register. This condition effectively connects the audio straight through. The encoded data may still be accessed via the encode buffer, and I/O port.  Fills the decode register with idle pattern. In either case data may be loaded into the decode register via the I/O port. This automatically overwrites the current contents of the decode register. |

| D <sub>2</sub> | Decode<br>Data Rate<br>Clock<br>Divider   | 1<br>0         | Fig. 5<br>Table 1 | $D_2$ sets the Decode data rate divider. $ \div \ 8 \\ \div \ 4$                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| D <sub>3</sub> | Decode<br>Filter<br>Clock<br>Divider      | 1<br>0         | Fig. 5<br>Table 1 | D <sub>3</sub> sets the Decode Filter Clock Divider and hence the Filter Cut-off Frequency.  + 2 + 1                                                                                                                                                                                                                                                                                                                                                                                                                 |

| D₄             | Decode<br>Master<br>Clock<br>Divider      | 1<br>0         | Fig. 5<br>Table 1 | D <sub>4</sub> sets the Decode Master clock divider.  + 10 + 8                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| IRA            |                                      | ı              | NSTRUCTION        | REGISTER 'A' $ \begin{array}{ccc} A_0 &= 0 \\ A_1 &= 0 \\ R/\overline{W} &= 0 \end{array} $          |

|----------------|--------------------------------------|----------------|-------------------|------------------------------------------------------------------------------------------------------|

| Bit            | Function<br>Name                     | Logic<br>State | References        | NOTES                                                                                                |

| D <sub>5</sub> | Encode<br>Data Rate<br>Divider       | 1<br>0         | Fig. 5<br>Table 1 | $D_{\text{5}}$ sets the Encode Data Rate Divider. $ \div \ 8 \\  \div \ 4$                           |

| D <sub>6</sub> | Encode<br>Filter<br>Clock<br>Divider | 1 0            | Fig. 5<br>Table 1 | D <sub>6</sub> sets the Encode Filter Clock Divider and hence the filter cut-off frequency.  + 2 + 1 |

| D <sub>7</sub> | Encode<br>Master<br>Clock<br>Divider | 1 0            | Fig. 5<br>Table 1 | D <sub>7</sub> sets the Encode Master Clock Divider.<br>÷ 10<br>÷ 8                                  |

| IRB            |                  | REGISTER 'B'   |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------|------------------|----------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit            | Function<br>Name | Logic<br>State | References | NOTES                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| D <sub>0</sub> | Page             |                |            | $D_0 - D_2$ set the "page size" in Encode Data bytes. (one byte = 8 serial data bits) in accordance with the table below:                                                                                                                                                                                                                                                                                                                                                        |

|                | Size             | See N          | <br>Notes  | D2         D1         D0         : PAGE BYTES         Page Period @32kbs           0         0         0         : 32         8ms                                                                                                                                                                                                                                                                                                                                                |

| D <sub>2</sub> | Set              |                |            | 0 0 0 : 32 8ms 0 0 1 : 64 16ms 0 1 0 : 96 24ms 0 1 1 : 128 32ms 1 0 0 : 160 40ms 1 0 : 192 48ms 1 1 0 : 224 56ms 1 1 1 : 256 64ms  Page Period (secs) = 8 x Page Bytes/Data Rate (b/s)                                                                                                                                                                                                                                                                                           |

| D <sub>3</sub> | "A/B"<br>Encode  | 0              | Fig. 4     | D <sub>3</sub> defines which audio input A or B is connected to the encoder via the encode filter. (See fig. 4).  AUDIO INPUT "A": Internally connects the "A" audio input to the encode filter input.  The "A/B OUT" pin outputs filtered audio "A". Audio input "B" set to V <sub>DD</sub> /2.  AUDIO INPUT "B": Internally connects the "B" audio input to the encode filter input.  The "A/B OUT" pin outputs filtered audio "B". Audio input "A" set to V <sub>DD</sub> /2. |

| IRB            |                                  | ı              | NSTRUCTION | REGISTER 'B' $ \begin{array}{ccc} A_0 & = 1 \\ A_1 & = 0 \\ R/\overline{W} & = 0 \end{array} $                                                                                                                                                                                                                                                                                          |

|----------------|----------------------------------|----------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit            | Function<br>Name                 | Logic<br>State | References | NOTES                                                                                                                                                                                                                                                                                                                                                                                   |

| D₄             | Switch<br>Audio<br>Output<br>"A" | 1<br>O         | Fig. 4     | D <sub>4</sub> controls the Output Audio Switch to determine which source audio is connected to Audio Output "A" pin.  Input "A" to Output "A" (direct). Decoder to Output "A".                                                                                                                                                                                                         |

| D <sub>6</sub> | Switch<br>Audio<br>Output<br>"B" | 1<br>0         | Fig. 4     | D <sub>5</sub> controls the Output Audio Switch to determine which source audio is connected to Audio Output "B" pin.  Decoder to Output "B" Input "B" to Output "B" (direct).                                                                                                                                                                                                          |

| D <sub>6</sub> | Powersave                        | 1              |            | $D_6$ controls the enablement and disablement of all analogue circuit elements.<br><b>POWERSAVE MODE:</b> Disables the circuit elements, thereby effectively reducing current consumption.<br><b>OPERATING MODE:</b> All circuit elements enabled.<br><b>NOTE:</b> During POWERSAVE, inputs are biased $V_{DD}/2$ . Outputs are biased $V_{DD}/2$ if IRB $D_4/D_5$ are set to "direct". |

| D,             | Power<br>Sensitivity             | 1              |            | D <sub>7</sub> determines the sensitivity range of the power measuring circuits.  HIGH: Low power input, assessment circuits have + 12dB gain over LOW Setting.  LOW: Normal power assessment sensitivity range.  NOTE: High input levels in the HIGH condition may lead to overflow, producing an ambiguous reading.                                                                   |

| _ | _ |

|---|---|

| c | o |

| S | н |

# **STATUS REGISTER**

$\begin{array}{ccc} a_0 & = 0 \\ a_1 & = 0 \end{array}$

|                |                         |                |            | R/W = 1                                                                                                                                                                                                                                                      |

|----------------|-------------------------|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit            | Function<br>Name        | Logic<br>State | References | NOTES                                                                                                                                                                                                                                                        |

| D <sub>o</sub> | Encode<br>Data          |                |            | $D_0$ indicates that a byte of data has been encoded and can be read from the encode buffer.                                                                                                                                                                 |

|                | Ready                   | 1              |            | READ BYTE: Set high during the last bit of the byte shifted into the encode register. This condition causes an interrupt request.                                                                                                                            |

|                |                         | 0              |            | NOT READY/OVERSPILL: This condition occurs when:  1. The last data byte in the encode data register has been read.  2. Encode data overspill bit = 1                                                                                                         |

|                |                         |                |            | ie. SRD <sub>3</sub> =1.                                                                                                                                                                                                                                     |

| D <sub>1</sub> | Decode<br>Data<br>Ready |                |            | D, indicates that a byte of data has been decoded and a new byte should be written to the decode buffer.                                                                                                                                                     |

|                |                         | 1              | SRD₄       | WRITE BYTE: This condition occurs when the decode register has been loaded from its buffer, i.e. after the last bit of the previous byte has been clocked out of the register.                                                                               |

|                |                         | 0              |            | NOT READY/OVERSPILL: This condition occurs when data has been written into the decode buffer or the decode data overspill condition is valid (SRD <sub>4</sub> =1).                                                                                          |

| D <sub>2</sub> | Page<br>Ready           |                |            | This bit indicates that a page of bytes has been encoded.                                                                                                                                                                                                    |

|                |                         | . 1            |            | READ PAGE: This condition occurs when the page counter has completed the last byte of a page. This is after power measurements have been written into PRD <sub>0</sub> to PRD <sub>7</sub> inclusive.                                                        |

|                |                         | 0              | SRD₅       | NOT READY/OVERSPILL: This condition occurs when Power Register "PR" has been read or the page overspill condition is valid.                                                                                                                                  |

| D <sub>3</sub> | Encode<br>Overspill     | 1              |            | OVERSPILL: Indicates that the encode data was not read between two consecutive "encode data ready" flags. Encoded data bytes have been lost, and no further bytes will be transferred to the encode buffer.                                                  |

|                |                         | 0              |            | NORMAL: This condition occurs when data has been read from the encode buffer, following a data ready flag, SRD <sub>0</sub> =1, or by writing to the decode buffer if both encode and decode overspill bits are set. (See 'Interrupts' page 9).              |

| D₄             | Decode<br>Overspill     | 1              |            | OVERSPILL: When this bit is set data transfer from the decode buffer to the decode register is inhibited. If the "DECODER/ENCODER BUS" (IRAD <sub>1</sub> ) is not set then the decode register will fill with idle pattern.                                 |

|                |                         | 0              |            | NORMAL: This condition occurs when data has been written to the decode buffer following a data ready flag, SRD <sub>1</sub> = 1 or by reading the contents of the encode buffer if both encode and decode overspill bits are set. (See 'Interrupts' page 9). |

| SR             |                     |                | STATUS R   | EGISTER                                                                                                                                                 |

|----------------|---------------------|----------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit            | Function<br>Name    | Logic<br>State | References | NOTES                                                                                                                                                   |

| D <sub>5</sub> | Page<br>Overspill 1 |                |            | OVERSPILL: This state indicates that the power register was not read before the next page was completed.  NORMAL: Power register "read" or IRB written. |

| PR                                                          |                                          |                | POWER REGISTER                                                                                                                                                               | A <sub>0</sub> = 1<br>A <sub>1</sub> = 0<br>R/W = 1    |

|-------------------------------------------------------------|------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Bit                                                         | Function<br>Name                         | Logic<br>State | NOTE                                                                                                                                                                         | ES                                                     |

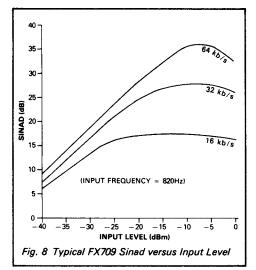

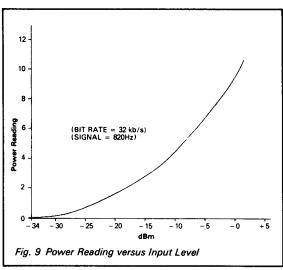

| D <sub>0</sub> D <sub>1</sub> D <sub>2</sub> D <sub>3</sub> | "A/B" Power<br>LSB<br>"A/B" Power<br>MSB |                | $D_0 - D_3$ represent the average page of data in the range from 1kHz) for the A or B input. The relationship between bina frequency dependant and exhaustics. (see fig. 9). | m +6dBm to -24dBm (at<br>ary value and signal level is |

| D <sub>4</sub> D <sub>5</sub> D <sub>6</sub> D <sub>7</sub> | "C" Power<br>LSB<br>"C" Power<br>MSB     |                | $D_4 - D_7$ represent the average page of data in the range fror 1kHz) for the C input.                                                                                      |                                                        |

#### Interrupts

Three conditions can cause interrupt requests to the host microprocessor.

- (i) The encode buffer contains an unread byte of data which is the most recent byte encoded.

- (ii) The decode buffer is ready to receive the next consecutive byte for decoding.

- (iii) The power register contains a power assessment for the most recent whole page encoded.

The status register indicates which of the above conditions are true.

If an interrupt condition remains unserviced and the condition becomes irrecoverably untrue, the status bit is cleared, the corresponding overspill bit is set and further interrupts are automatically inhibited. Also the encode and decode data buffers retain the data present when the data bit was set, i.e. register-buffer update is inhibited. The power register is updated at all times.

Condition (i) is serviced by a valid address to the encode buffer. Condition (ii) is serviced by a valid address to the decode buffer. If conditions (i) and (ii) have both become UNTRUE, servicing either buffer resets both to a cleared start position. Condition (iii) is serviced by reading the Power Register.

#### The C Input

By careful selection of the audio frequency filtering to the C input the A/B and C power words can be used in the processor to provide frequency as well as power information. This facility could be used for word, pause or voice recognition.

## **Specification**

#### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

#### **Operating Limits**

All characteristics measured using the following parameters unless otherwise specified:

$V_{DD} = 5V$ ,  $T_{amb} = 25^{\circ}C$ ,  $\emptyset = f_{in} = 1kHz$ .

| Characteristics                                       | See Note | Min | Тур | Max  | Unit     |

|-------------------------------------------------------|----------|-----|-----|------|----------|

| Static Characteristics                                |          |     |     |      |          |

| Supply voltage                                        |          | 4.5 | 5.0 | 5.5  | V        |

| Supply Current                                        |          | _   | 6   | _    | mA       |