## **CML Semiconductor Products**

PRODUCT INFORMATION

# FX429 Band III FFSK Modem for Trunked Radio Systems

Publication D/429/6 July 1994

#### Features/Applications

- Band III and General Purpose Trunked Radio Applications

- Full-Duplex 1200 Baud Operation

- High Intelligence

Error Checking in Receive

- Error Check Word Generation

- Frame SYNC and SYNT Detection

- Preamble Generation

- μProcessor Compatible Interface

- Carrier Detection On-Chip

- Low Power Consumption

- General Purpose Timer

## **Brief Description**

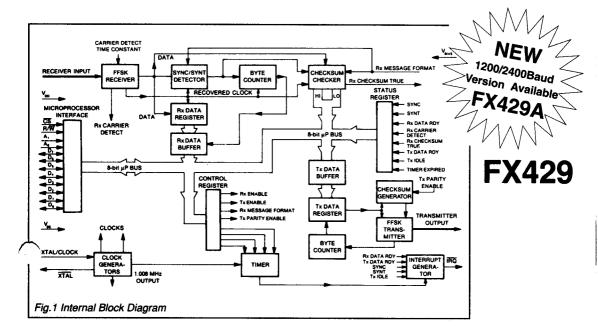

The FX429 is a single-chip CMOS 1200 baud FFSK Modem, designed primarily for use in trunked radio systems but may also be employed in other general purpose radio or line data communication applications.

The device has been designed to conform to the UK Band III trunked radio protocols MPT 1317/1327.

The FX429 is full duplex at 1200 baud and includes an 8-bit parallel microprocessor interface and a programmable timer which may be set for interrupt periods of 8 to 120 bits.

Preamble and an error-check word are automatically generated in the transmit mode.

Error checking is performed and the 16-bit SYNC or SYNT words are detected in the receive mode.

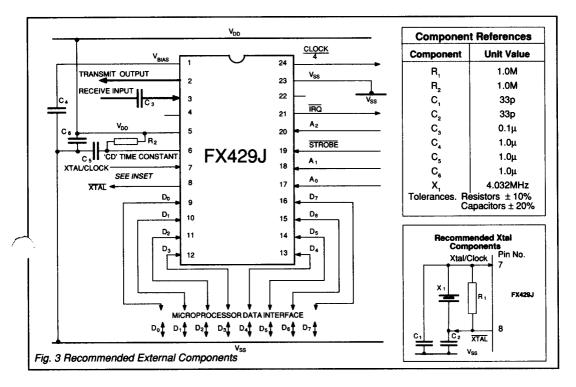

An on-chip Xtal/clock generator requiring an external 4.032MHz Xtal or clock input provides all microcircuit filter sampling clocks and modem timings whilst also supplying a "Clock + 4" output (1.008MHz).

The FX429, which has a powersaving facility, requires a single 5-volt power supply and is available in both cerdip DIL and plastic SMD packages.

| Pin N                                 | lumber                                | Function                                                   |                                                                                                                     |                                                            |                                           |                                                        |

|---------------------------------------|---------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------|

| DIL<br>FX429J                         | Quad<br>FX429LG/LS                    |                                                            |                                                                                                                     |                                                            |                                           |                                                        |

| 1                                     | 1                                     | J C <sub>4</sub> , see Figure 3. W                         | circuitry bias line, held a<br><b>arning Note</b> – In order<br>nen both Tx and Rx are                              | to reduce current c                                        | et be decoupled to<br>consumption, the p  | V <sub>ss</sub> by capacitor<br>potential at this pin  |

| 2                                     | 2                                     | Transmit Output :<br>Control Register ( D                  | The 1200 baud, 1200H;<br>o) its output impedance                                                                    | z/1800Hz FFSK Tx<br>is set high.                           | output. When not                          | enabled by the                                         |

| 3                                     | 4                                     | Receiver Input: The must be a.c. couple                    | ne 1200 baud received f<br>d via capacitor C <sub>3</sub> , see f                                                   | FFSK signal input. 1<br>Figure 3.                          | Гhe 1200Hz/1800                           | Hz audio to this pin                                   |

| 5                                     | 5                                     | V <sub>DD</sub> : Positive Suppl<br>rail be decoupled to   | y. A single +5V regulate $V_{ss}$ by capacitor $C_{\rm e}$ , see                                                    | d supply is required<br>Figure 3.                          | d. It is recommend                        | ded that this power                                    |

| 6                                     | 6                                     | Carrier Detect Time external component Figure 3.           | B Constant: The on-ch<br>s on this pin. A capacito                                                                  | ip Carrier Detect in:<br>r, $C_{s}$ , to $V_{ss}$ , togeth | tegration function<br>er with a resistor, | requires two R <sub>2</sub> , to V <sub>DD</sub> . See |

| 7                                     | 7                                     | Xtal/Clock: The inp                                        | out to the clock oscillator<br>e connected here. See                                                                | r inverter. A 4.032 N<br>Figure 3.                         | /IHz Xtal or extern                       | nally derived clock                                    |

| 8                                     | 8                                     | Xtal : The output of                                       | the 4.032 MHz clock os                                                                                              | cillator.                                                  |                                           |                                                        |

| 9<br>10<br>11<br>12<br>13<br>14<br>15 | 9<br>10<br>11<br>12<br>13<br>14<br>15 | D <sub>1</sub> : D <sub>2</sub> : D <sub>3</sub> : These 8 | rocessor Data Interfaces B lines are used by the $\mathbf{c}_{2}$ , $\mathbf{A}_{0}$ and $\mathbf{A}_{1}$ inputs de | levice to communic                                         | ate with a microp<br>selection.           | rocessor                                               |

| 17<br>18                              | 17<br>18                              | A <sub>o</sub> : Register Select                           | t <b>ion.</b> These inputs, with<br>the data bus as sh                                                              | the A <sub>2</sub> input, select<br>own in Table 1 (bel    | the required regisow).                    | ster to                                                |

|                                       |                                       | Table 1                                                    | Register Control Status Rx Data Tx Data Syndrome Low Syndrome High                                                  | A <sub>2</sub><br>0<br>1<br>1<br>0<br>1                    | A <sub>0</sub> 1 1 0 0 0 1                | A, 1 1 1 1 1 0 0 0                                     |

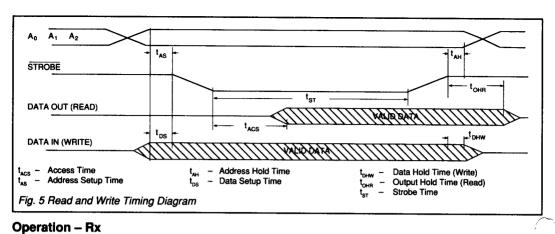

| 19                                    | 19                                    | or out. It should be g                                     | e dual functions of sele<br>enerated by gating high<br>obe = logic "0." See Figu                                    | -order address bits                                        | Read or Write an with a read/write        | d strobing data in<br>clock. The FX429                 |

| 20                                    | 20                                    | A <sub>2</sub> : Used in conjunct<br>data interface pins ( | tion with $A_1$ and $A_0$ to de $D_0 - D_7$ ) during Strobe                                                         | termine which inter<br>see Table 1 and Fi                  | nal registers are gure 5).                | connected to the                                       |

| 21                                    | 21                                    | interrupts are indicate                                    | est. This line will go to a<br>or active low component<br>ed at the Status Registe<br>or Expired                    | s (100kΩ pullup to '                                       | $V_{aa}$ ). The condition                 | ens that cause the                                     |

| 23                                    | 22                                    | V <sub>ss</sub> : Negative Supply                          | y (GND).                                                                                                            | 22                                                         |                                           |                                                        |

| 24                                    | 23                                    | Clock + 4 : A 1.008 I<br>source impedance ar               | MHz (X, + 4) clock is available source current limits.                                                              | ailable at this outpu                                      | t for external circu                      | uit use, note the                                      |

| 4, 22                                 | 3, 24                                 | 1                                                          | onnected internally, leav                                                                                           | e open circuit.                                            |                                           |                                                        |

## Modems in Mobile Data Signalling ..... An Introduction

#### **Digital Code Format**

The recommended Digital Code Format for use over Land Mobile Radio Systems is detailed in the Department of Trade and Industry, Radio Regulatory Division's publications MPT 1317 and MPT 1327, and is as described briefly below.

| Prea                                                                  | mble         | SYNC or SYNT                  |                      |                              |

|-----------------------------------------------------------------------|--------------|-------------------------------|----------------------|------------------------------|

| For bit sync.<br>10101010 bit reversals<br>Minimum 16 bits, ending in |              | SYNC Word<br>1100010011010111 | Address Code<br>Word | Optional Data                |

| logi                                                                  | c'0'         | SYNT Word<br>0011101100101000 | 64 Bits              | Code Words                   |

| ſ                                                                     |              |                               | 1                    |                              |

| <b>*</b>                                                              | Address Code | Word Structure                | (Bit                 | number 1 is transmitted fire |

| Bit No.                                                               | Address Code | Word Structure 2 to 8         | (Bit                 | number 1 is transmitted fire |

| -                                                                     | Address Code |                               |                      | 1                            |

#### Operation

The FX429 can be used for Full-Duplex operation with the host microprocessor only having to operate on the data whilst the modem (FX429) handles all other signalling routines and requirements.

In the Tx mode the FX429 will :-

- Internally generate and transmit a preamble bit reversals, for system bit synchronization.

- (2) Accept from the host, and transmit, a 16-bit 'SYNC' or 'SYNT' word.

- (3) Accept from the host, and transmit, 6 bytes of data (Address Code Word).

- (a) Upon a software command, internally calculate and transmit a 2-byte checksum based on the previous 6 data bytes.

or —

- (b) Upon a software command, disable internal checksum generation and allow continuous data transmission.

- Transmit 1 'hang bit' and go idle when all loaded data traffic has been sent (followed by a "Tx Idle" interrupt).

In the Rx mode the FX429 will :-

- (1) Detect and achieve bit synchronization within 16 bits.

- (2) Search for and detect the 16-bit 'SYNC'/'SYNT' word.

- (3) Output all received data after 'SYNC/SYNT,' in byte form.

(4) Upon a software command (Rx Message Format), use the

- (4) Upon a software command (Rx Message Format), use the received checksum to calculate the presence (if any) of errors, and advise the host with an interrupt and a 16-bit Syndrome word.

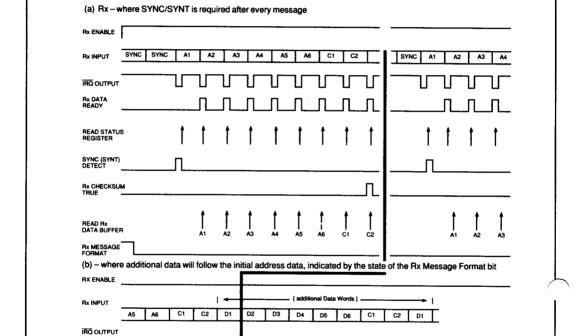

Note – In Rx a software command is used to determine whether a 'SYNC'/SYNT' word is required after every 8 (6 data + 2 checksum) received bytes, or "data" is received continually.

Normally the 'SYNC' word is used on the Control data channel and the 'SYNT' word is used on the Traffic data channel.

#### Non MPT Application - Full-Duplex

The functions described in this section, to allow the FX429 modem to operate as a general purpose device, are obtained using the commands and indications detailed in the "Register Instructions" pages.

Tx — When enabled the device transmits a "101010......10" preamble until data for transmission is loaded by the host microprocessor.

Transmits 6 bytes of the loaded data followed by a 2-byte checksum based on that data. As long as Tx data is loaded the transmitter will transmit, the 2-byte checksum being produced after every 6 bytes (8 byte packages). Automatic checksum generation can be inhibited by a software command to allow transmission of continuous data streams.

Rx — When enabled requires the 16-bit SYNC or SYNT word (see notes) before outputting data bytes. The modern receiver will then output continuous bytes of data, after every 6 bytes received a 2-byte checksum word will be output and can be ignored or used for error checking. **Control Register**

$A_1 = 1$

$A_0 = 1$

$A_2 = 0$

Write Only

The Control Register, when selected, directs the modem's operation as described below.

|                         | ontrol Hegister, when | selected, direct                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3 1116 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ioueiii:                          | s operat               | on as des                                                                                | cribeu b                 | CIUW.     |                          |                                                                                     |

|-------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------------|------------------------------------------------------------------------------------------|--------------------------|-----------|--------------------------|-------------------------------------------------------------------------------------|

| Bit                     | Description           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   | Set = lo               | gic '1' (Hig                                                                             | h) Clea                  | r = logic | '0' (Low)                |                                                                                     |

| Bit 0<br>D <sub>o</sub> | Tx Enable *           | Set $-D_0$ enables the transmitter for operation. A '0 $-$ 1' transition causes bit synchronization and the start of 101010 preamble pattern transmission. At least one byte of preamble will be transmitted. If data is loaded into the Tx Data Buffer before one byte has been sent then that data will follow, otherwise whole bytes of preamble will continue until data is loaded. Clear $-$ The Transmitter Output pin is set to a high impedance and no transmitter interrupts are produced. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |                        |                                                                                          |                          |           |                          |                                                                                     |

| Bit 1<br>D,             | Tx Parity Enable      | modern. A '0 –<br>Tx Data Buffer<br>loaded until thi<br>after the last o<br>occurs before<br>cease after on<br>No checksum<br>Clear – No che                                                                                                                                                                                                                                                                                                                                                        | Set – D <sub>1</sub> indicates to the transmitter that 2-byte checksums are to be generated by the modem. A '0 – 1' transition starts checksum generation on the next six bytes loaded from the Tx Data Buffer into the Tx Data Register. Checksum generation continues for every 6 bytes loaded until this bit is cleared. The transmitter will send the generated checksum (2 bytes) after the last of each 6 bytes have been sent. If an underrun (no more data loaded) condition occurs before 6 bytes have been loaded checksum generation will abort, the transmission will cease after one 'hang' bit has been sent and Bit 4 in the Status Register (Tx Idle) will be set. No checksum will be transmitted.  Clear – No checksum generation is carried out and the host may supply the checksum bytes. The output is then "as written". |                                   |                        |                                                                                          |                          |           |                          |                                                                                     |

| Bit 2<br>D <sub>2</sub> | Rx Enable *           | Set - D <sub>2</sub> enablinterrupts) unti<br>Clear - The re                                                                                                                                                                                                                                                                                                                                                                                                                                        | l a 'SY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | NC' or '                          | SYNT' v                | vord is fou                                                                              | nd in the                | receive   | d bit strea              |                                                                                     |

| Bit 3<br>D,             | Rx Message<br>Format  | way the receiv<br>bytes are data                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | er hand<br>and with<br>ceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | dles the<br>ill start<br>will sto | error che<br>p data tr | ng data bit<br>ecking acc<br>ansfer to t                                                 | s. If 'set'<br>cordingly | the rece  | iver will a              | host to control the<br>ssume that the next 6<br>um bytes until another              |

| Bit 4<br>D <sub>4</sub> | Timer LSB             | These four b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | its cont<br>D <sub>6</sub><br>0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rol the D 5                       | timer as<br>D 4<br>0   | follows :-  Reset counter and disable timer interrup  Count and interrupt every - 8 bits |                          |           |                          |                                                                                     |

|                         |                       | Ö                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ŏ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                 | ö                      |                                                                                          | ,                        | *         | "                        | 16 bits                                                                             |

|                         |                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                 | 1                      |                                                                                          | •                        |           | *                        | 24 bits                                                                             |

| Bit 5                   | Timer                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                 | 0                      |                                                                                          | •                        | •         | •                        | 32 bits                                                                             |

| D,                      |                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                 | 1                      |                                                                                          | "                        | •         | **                       | 40 bits                                                                             |

|                         |                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                 | 0                      |                                                                                          | *                        | •         | *                        | 48 bits                                                                             |

|                         |                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                 | 1                      |                                                                                          | •                        | •         | •                        | 56 bits                                                                             |

|                         |                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                 | 0                      |                                                                                          | •                        |           | •                        | 64 bits                                                                             |

|                         |                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                 | 1                      |                                                                                          | •                        |           | **                       | 72 bits                                                                             |

| Bit 6                   | Timer                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                 | 0                      |                                                                                          | •                        | •         | •                        | 80 bits                                                                             |

| D,                      |                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                 | 1                      |                                                                                          |                          |           | -                        | 88 bits                                                                             |

|                         |                       | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                 | 0                      |                                                                                          |                          | -         | -                        | 96 bits                                                                             |

|                         |                       | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0                                 | 1                      |                                                                                          |                          |           |                          | 104 bits                                                                            |

|                         |                       | 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1                                 | 0                      |                                                                                          | -                        | -         | -                        | 112 bits                                                                            |

| Bit 7<br>D,             | Timer MSB             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ext time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | r perio                           | d will be              | correct wi                                                                               | thout fire               | st having | to reset ti              | 120 bits<br>ne last timer interrupt<br>he timer, otherwise                          |

| * Note                  | -                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                   |                        |                                                                                          |                          |           |                          |                                                                                     |

| Enabli                  | ing Times             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit peri                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | iods. If                          | one sec                | •                                                                                        |                          |           |                          | sections are initially<br>ly enabled this time is                                   |

| Tx En                   | able                  | preamble leng<br>after a Tx Ena                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | th, the<br>ble con<br>hat the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | device<br>nmand.<br>Timer         | may oci<br>User se     | casionally<br>oftware sh                                                                 | produce<br>ould har      | a Tx Da   | ta Ready .<br>occurrence | timer setting the<br>interrupt immediately<br>e by either:<br>t appropriate to load |

|                         |                       | (b) Not using t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | he Tim<br>byte of p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | er. i.e.<br>oreamb                | le. This               | resets any                                                                               | y interruj               |           |                          | tus Register and<br>reamble transmitted is                                          |

Status Register

A, = 1

$A_0 = 1$

A<sub>2</sub> = 1

Read Only

When an interrupt is generated the  $\overline{\text{IRQ}}$  Output goes Low with the Status Register bits indicating the sources of the interrupt.

| Bit                     | Description          | Function Set = logic '1' (High) Clear = logic '0' (Low)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit 0<br>D <sub>o</sub> | Rx Data Ready        | Do when set, causes an interrupt indicating that received data is ready to be read from the Rx Data Buffer. This data must be read within 8 bit periods.  Set – when a byte of data is loaded into the Rx Data Buffer, if a frame (SYNC/SYNT) word has been received.  Bit and Interrupt Cleared – (i) by a read of the Status Register followed by a read of the Rx Data Buffer or (ii) by Rx Enable going Low.                                                                                                                                                                        |

| Bit 1<br>D,             | Rx Checksum<br>True  | D <sub>1</sub> when set, indicates that the error checking on the previous 6 bytes agreed with the received checksum. This function, which is valid when the Rx Data Ready bit (D <sub>0</sub> ) is set for the second byte of the received checksum, does not cause an interrupt.  Set – by a correct comparison between the received and generated checksums.  Cleared – (i) by a read of the Status Register followed by a read of the Rx Data Buffer, o r (ii) by Rx Enable going Low.                                                                                              |

| Bit 2<br>D <sub>2</sub> | Rx Carrier<br>Detect | D <sub>2</sub> is a "Real Time" indication from the modem receiver's carrier detect circuit and does not cause an interrupt. When FFSK tones are present at the receiver input this bit goes High, for no FFSK input this bit goes Low. When the Rx Enable bit (D <sub>2</sub> - Control Register) is Low Rx Carrier Detect will go Low.                                                                                                                                                                                                                                                |

| Bit 3<br>D <sub>3</sub> | Tx Data<br>Ready     | <ul> <li>D<sub>3</sub> when set, causes an interrupt to indicate that a byte of data should be written to the Tx Data Buffer within 8 bit periods.</li> <li>Set — (i) when the contents of the Tx Data Buffer are transferred to the Tx Data Register, or (ii) when the Tx Enable is set — No interrupt is generated in this case.</li> <li>Bit Cleared — (i) by a read of the Status Register followed by a write to the Tx Data Buffer, or (ii) by Tx Enable going Low.</li> <li>Interrupt Cleared — (i) by a read of the Status Register, or (ii) by Tx Enable going Low.</li> </ul> |

| Bit 4<br>D <sub>4</sub> | Tx idle              | D <sub>4</sub> causes an interrupt when set, to indicate that all loaded data and one 'hang' bit have been transmitted.  Set – one bit period after the last byte is transmitted. This last byte could be either "checksum" or " loaded data" depending upon the Tx Parity Enable state (Control Register D <sub>1</sub> ).  Bit Cleared – (i) by a write to the Tx Data Buffer, or (ii) by Tx Enable going Low.  Interrupt Cleared – (i) by a read of the Status Register, or (ii) by Tx Enable going Low.                                                                             |

| Bit 5                   | Timer<br>Interrupt   | ${f D_s}$ , when set, causes an interrupt to indicate that the set timer period has expired. (Control Register ${f D_s} - {f D_p}$ ). Set – by the timer. Bit and interrupt Cleared – by a read of the Status Register.                                                                                                                                                                                                                                                                                                                                                                 |

| Bit 6<br>D <sub>s</sub> | Rx SYNC<br>Detect *  | D <sub>e</sub> , when set, causes an interrupt to indicate that a 16-bit 'SYNC' word (1100010011010111) has been detected in the received bit stream.  Set – on receipt of the 16th bit of a 'SYNC' word.  Bit and Interrupt Cleared – (i) By a read of the Status Register, or (ii) by Rx Enable going Low.                                                                                                                                                                                                                                                                            |

| Bit 7<br>D,             | Rx SYNT<br>Detect *  | D <sub>2</sub> , when set, causes an interrupt to indicate that a 16-bit 'SYNT' word (0011101100101000 ) has been detected in the received bit stream.  Set – on receipt of the 16th bit of a 'SYNT' word.  Bit and Interrupt Cleared – (i) By a read of the Status Register,  or (ii) by Rx Enable going Low.                                                                                                                                                                                                                                                                          |

| * Not                   | 9 –                  | 'SYNC' and 'SYNT' Detection is disabled whilst the checksum checker is running.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rx Data Buffer | A, = 1 | $A_0 = 0$ | A <sub>2</sub> = 1 | Read Only |

|----------------|--------|-----------|--------------------|-----------|

These 8 bits are the last byte of data received with bit 7 being received first. Note the relative positions of the MSB and LSB presented in this bit stream, the position may be different to the convention used in other µProcessor peripherals.

| D <sub>o</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>s</sub> | D <sub>6</sub> | D,  |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----|

| LSB            | -              | -              | -              | -              | -              | -              | MSB |

| Tx Data Buffer | A, = 1 | $A_0 = 0$ | $A_2 = 0$ | Write Only |

|----------------|--------|-----------|-----------|------------|

These 8 bits loaded to the Tx Data Buffer are the next byte of data that will be transmitted, with bit 7 being transmitted first. Note the relative positions of the MSB and LSB presented in this bit stream, the position may be different to the convention used in other µProcessor peripherals. If the the Tx Parity Enable bit

(Control Register D, ) is set, a 2-byte checksum will be inserted and transmitted by the modern after every 6 transmitted "message" bytes.

| D <sub>o</sub> | D, | D <sub>2</sub> | D <sub>3</sub> | D <sub>4</sub> | D <sub>5</sub> | D <sub>6</sub> | D,  |

|----------------|----|----------------|----------------|----------------|----------------|----------------|-----|

| LSB            | -  | -              | •              | -              | •              | •              | MSB |

### The Syndrome Word

This 16-bit word (both Low and High bytes) may be used to correct errors.

Bits  $S_1$  to  $S_{15}$  are the 15 bits remaining in the polynomial divider of the checksum checker at the end of 6 bytes of "received message." For a <u>correct</u> message all 15 bits  $(S_1$  to  $S_{15}$ ) will be zero.

The 2 Syndrome bytes are valid when the Rx Data Ready bit (Status Register D<sub>o</sub>) is set for the second byte of the receivedchecksum and should be read, if required, before 8 byte periods.

| Syndron | ne Lo          | w Byte         | A <sub>1</sub> = 0 | <b>A</b> <sub>0</sub> = | 0              | A <sub>2</sub> = 1 | Rea            | d Only |

|---------|----------------|----------------|--------------------|-------------------------|----------------|--------------------|----------------|--------|

|         | D <sub>0</sub> | D <sub>1</sub> | D <sub>2</sub>     | D <sub>3</sub>          | D <sub>4</sub> | D <sub>s</sub>     | D <sub>6</sub> | D,     |

| 8       | S1             | S2             | S3                 | S4                      | S5             | S6                 | <b>S</b> 7     | S8     |

| Syndrome H     | drome High Byte |                | <b>A</b> <sub>0</sub> = | 1 / | \ <sub>2</sub> = 1 | Read Only      |        |  |

|----------------|-----------------|----------------|-------------------------|-----|--------------------|----------------|--------|--|

| D <sub>o</sub> | D,              | D <sub>2</sub> | D <sub>3</sub>          | D,  | D <sub>s</sub>     | D <sub>6</sub> | D,     |  |

| S9             | S10             | S11            | S12                     | S13 | S14                | S15            | PARITY |  |

$D_7$  – This is a "Parity Error Bit" – Indicating an error between the received parity bit and the parity bit internally generated from the incoming message. Thus for a correctly received message all 16 bits of the Syndrome Word ( $S_1$  to  $S_{15}$  and Parity Error) will be zero.

#### **Carrier Detect Time Constant**

The value of the Carrier Detect capacitor,  $C_s$ , determines the carrier detect time constant. A long time constant (larger value  $C_s$ ), results in improved noise immunity but increased response time.  $C_s$  may be varied to optimise noise immunity/reponse time.

## **Timing Information**

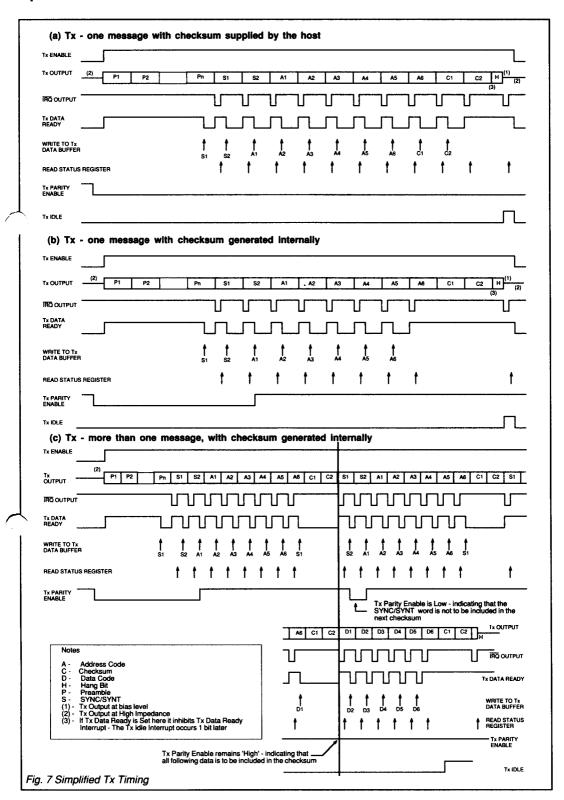

## **Operation - Tx**

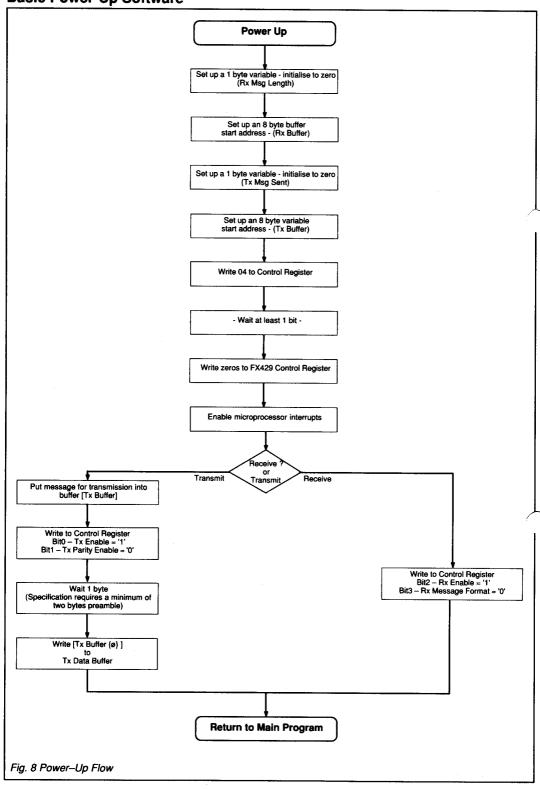

**Basic Power-Up Software**

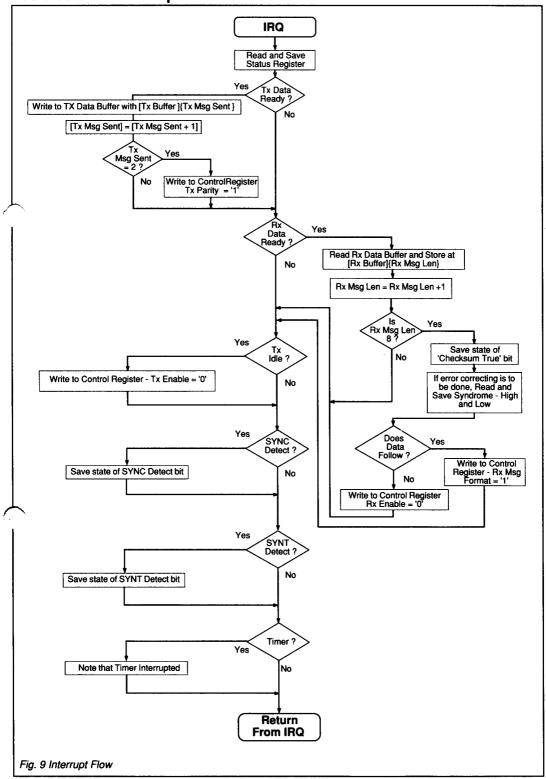

**Basic Software Interrupt Flow**

#### Specification

#### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

Supply voltage

Input voltage at any pin (ref V<sub>ss</sub> = 0V) Sink/source current (supply pins)

(other pins)

Total device dissipation @ T<sub>AMB</sub> 25°C

Operating temperature range: FX429J

FX429LG/LS

Storage temperature range:

FX429J FX429LG/LS -0.3 to 7.0V

-0.3 to  $(V_{DD} + 0.3V)$

+/- 30mA

+/- 20mA

800mW Max. 10mW/°C

-30°C to +85°C (ceramic)

-30°C to +70°C (plastic) -55°C to +125°C (ceramic)

-40°C to +85°C (plastic)

#### **Operating Limits**

All characteristics are measured using the following parameters unless otherwise specified:

$V_{DD}$  = 5.0V,  $T_{AMB}$  = 25°C. Xtal/Clock  $f_0$  = 4.032 MHz. Audio level 0dB ref: = 300mV rms.

Bit Rate Bandwidth = 1200Hz.

| Characteristics                                                | See Note | Min. | Тур.  | Max. | Unit      |

|----------------------------------------------------------------|----------|------|-------|------|-----------|

| Static Values                                                  |          |      |       |      |           |

| Supply Voltage                                                 |          | 4.5  | _     | 5.5  | V         |

| Supply Current Ranges                                          |          |      |       |      |           |

| Rx and Tx Enabled                                              |          | _    | _     | 7.0  | mA        |

| Rx Enabled, Tx Disabled                                        |          | _    | 4.0   | 6.0  | mA        |

| Rx Disabled, Tx Enabled                                        |          | _    | -     | 7.0  | mA        |

| Rx and Tx Disabled                                             | 10       | _    | 1.5   | 2.5  | mA        |

| Dynamic Values                                                 |          |      |       |      |           |

| Modem Internal Delay                                           |          | -    | 1.5   | _    | ms        |

| Interface Levels                                               |          |      |       |      |           |

| Output Logic '1' Source Current                                | 2        | _    | _     | 120  | μА        |

| Output Logic '0' Sink Current                                  | 3        | _    | _     | 360  | μA        |

| Three State Output Leakage Current                             |          | _    | _     | 4.0  | μA        |

| D <sub>o</sub> – D <sub>7</sub> Data In/Out                    | 1        |      |       |      | •         |

| Logic '1' Level                                                |          | 3.5  | _     | _    | ٧         |

| Logic '0' Level                                                |          | _    | _     | 1.5  | V         |

| A <sub>1</sub> , A <sub>0</sub> , A <sub>2</sub> , STROBE, IRQ | 4        |      |       |      |           |

| Logic '1' Level                                                |          | 4.0  | _     | _    | V         |

| Logic '0' Level                                                |          | -    | _     | 1.0  | V         |

| Analogue Impedances                                            |          |      |       |      | /         |

| Rx Input                                                       |          | 100  | _     | _    | kΩ        |

| Tx Output (Enabled)                                            |          | _    | 10    | -    | kΩ        |

| Tx Output (Disabled)                                           |          | -    | 5     |      | MΩ        |

| On-Chip Xtal Oscillator                                        |          |      |       |      |           |

| R <sub>IN</sub>                                                |          | 10   | -     | -    | $M\Omega$ |

| R <sub>out</sub>                                               | 5        | 5.0  | -     | 15   | kΩ        |

| Oscillator Gain                                                |          | _    | 15    | _    | dB        |

| Xtal frequency                                                 |          | -    | 4.032 | _    | MHz       |

| Timing - (Fig. 5)                                              |          |      |       |      |           |

| Access Time – (t <sub>ACS</sub> )                              |          | _    | _     | 135  | ns        |

| Address Hold Time - (t <sub>AH</sub> )                         |          | 0    | -     | _    | ns        |

| Address Set-up Time - (t <sub>AS</sub> )                       |          | 0    | _     | -    | ns        |

| Data Hold Time (Write) - (t <sub>DHW</sub> )                   |          | 85   | -     | -    | ns        |

| Data Set-up Time (Write) - (t <sub>ne</sub> )                  |          | 0    | -     | -    | ns        |

| Output Hold Time (Read) - (t <sub>OHR</sub> )                  |          | 15   | _     | 105  | ns        |

| Strobe Time – (t <sub>st</sub> )                               |          | 140  | _     | -    | ns        |

## Specification .....

| Characteristics                           | See Note | Min.            | Тур. | Max.  | Unit |

|-------------------------------------------|----------|-----------------|------|-------|------|

| Dynamic Values                            |          |                 |      |       |      |

| Receiver                                  |          |                 |      |       |      |

| Signal Input Levels                       | 6        | <del>9</del> .0 | -2.0 | +10.5 | dB   |

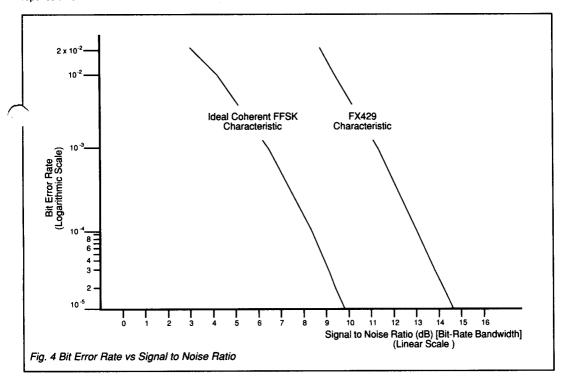

| Bit Error Rate                            | 7        |                 |      |       |      |

| @ 12dB Signal/Noise Ratio                 |          | _               | 7.0  | -     | 10-4 |

| @ 20dB Signal/Noise Ratio                 |          | _               | 1.0  | _     | 10⁻8 |

| Synchronization @ 12dB Signal/Noise Ratio | 8        |                 |      |       |      |

| Probability of Bit16 being correct        |          | _               | 99.5 | _     | %    |

| Carrier Detect Response Time              | 8        | -               | 13.0 | -     | ms   |

| Transmitter                               |          |                 |      |       |      |

| Output Level                              |          | -               | 8.25 | _     | dB   |

| Output Level Variation                    |          | -1.0            | _    | +1.0  | dB   |

| Output Distortion                         |          | _               | 3.0  | 5.0   | %    |

| 3rd Harmonic Distortion                   |          | _               | 2.0  | 3.0   | %    |

| Logic '1' Frequency                       | 9        | _               | 1200 | _     | Hz   |

| Logic '0' Frequency                       | 9        | _               | 1800 | _     | Hz   |

| Isochronous Distortion                    |          |                 |      |       |      |

| 1200Hz – 1800Hz                           |          | _               | 25   | 40    | μs   |

| 1800Hz 1200Hz                             |          |                 | 20   | 40    | μs   |

#### **Notes**

- 1. With each data line loaded as, C = 50pf and R = 10k $\Omega$ .

- 2.  $V_{OUT} = 4.6V$ .

- 3.  $V_{OUT} = 0.4V$

- Sink/Source currents ≤ 0.1mA.

- 5. Both Xtal and Xtal + 4 Outputs.

- 6. With 50dB Signal/Noise Ratio.

- 7. See Figure 3, Bit Error Rate.

- 8. This Response Time is measured using a 10101010101....01 pattern input signal at a level of 230mV rms (-2.3dB) with no noise.

- 9. Dependent upon Xtal tolerance.

- 10. Powersave is only active when both Rx and Tx functions are disabled.

#### **Checksum Generation and Checking**

Generation - The checksum generator takes the 48 bits from the 6 bytes loaded into the Tx Data Buffer and divides them modulo-2, by the generating polynomial;-

$$X^{15} + X^{14} + X^{13} + X^{11} + X^{4} + X^{2} + 1$$

It then takes the 15-bit remainder from the polynomial divider, inverts the last bit and appends an EVEN parity bit generated from the initial 48 bits and the 15 bit remainder (with the last bit inverted). This 16-bit word is used as the "Checksum."

Checking - The checksum checker does two things:

It takes the first 63 bits of a received message, inverts bit 63, and divides them modulo-2, by the generating polynomial;- $X^{15} + X^{14} + X^{13} + X^{11} + X^{4} + X^{2} + 1$

The 15 bits remaining in the polynomial divider are checked for all zero.

Secondly, it generates an EVEN parity bit from the first 63 bits of a received message and compares this bit with the received parity bit (bit 64).

If the 15 bits in the polynomial divider are all zero, and the two parity bits are equal, then the Rx Checksum True bit (SR D,) bit is set.

### **Package Outlines**

The FX429 is available in the package styles outlined below. Mechanical package diagrams and specifications are detailed in Section 10 of this document. Pin 1 identification marking is shown on the relevant diagram and pins on all package styles number anti-clockwise when viewed from the top.

## **Handling Precautions**

The FX429 is a CMOS LSI circuit which includes input protection. However precautions should be taken to prevent static discharges which may cause damage.

FX429J 24-pin cerdip DIL (J4)

**FX429LG** 24-pin quad plastic encapsulated bent and cropped (L1)

FX429LS 24-lead plastic leaded chip carrier

## **Ordering Information**

FX429J 24-pin cerdip DIL (J4)

**FX429LG** 24-pin quad plastic

encapsulated bent and cropped

(L1)

FX429LS 24-lead plastic leaded chip

carrier (L2)