# **CML Semiconductor Products**

# **Cordless Telephone Scrambler**

**FX128**

D/128/1 October 1997

Provisional Information

#### **Features**

- Full-Duplex Audio Processing

- On-Chip Filters

- Carrier Rejection >55dB

- Uses IF (10.24MHz) Clock

- Requires No Extra Crystal

- Excellent Audio Quality

- Low Power Operation (3.0V)

- ECPA\* Qualified Voice Protection

- Battery Powered Portability

- Cordless Telephones and Wireless PBX Applications

#### 1.1 Brief Description

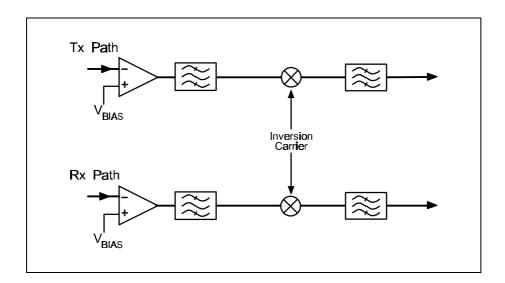

The FX128 is a full-duplex frequency inversion scrambler designed to provide secure conversations for 46/49 MHz cordless telephone users. The Rx and Tx audio paths consist of the following:

- 1. A switched-capacitor balanced modulator with high baseband and carrier rejection.

- 2. A 3.3kHz inversion carrier (injection tone).

- 3. A 3100Hz lowpass filter.

- 4. Input op-amps with externally adjustable gain.

The FX128 uses mixed signal CMOS switched-capacitor filter technology and operates from a single supply in the range of 3.0 to 5.5 volts. The inversion carrier's frequency and filter switching clock are generated on-chip using an external 10.24MHz or 3.58/3.6864 MHz crystal or clock input (selectable).

This device is available in 16-pin SOIC (FX128D4) and 16-pin plastic DIL (FX128P3) packages.

\*Electronics Communications Privacy Act (Title 18, US Code 2510 etc.).

#### **CONTENTS**

| <u>Page</u>                   | <u>Page</u> |

|-------------------------------|-------------|

| 1.1 Brief Description1        | 1           |

| 1.2 Block Diagram3            | 3           |

| 1.3 Signal List4              | 4           |

| 1.4 External Components5      | 5           |

| 1.5 Application6              | 6           |

| 1.6 Application Notes6        | 6           |

| 1.7 Performance Specification | 7           |

**Note:** As this product is still in development, it is likely that a number of changes and additions will be made to this specification. Items marked TBD or left blank will be included in later issues. Information in this data sheet should not be relied upon for final product design.

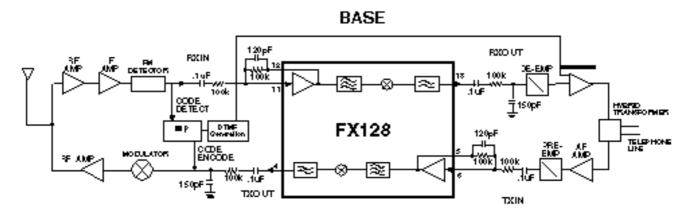

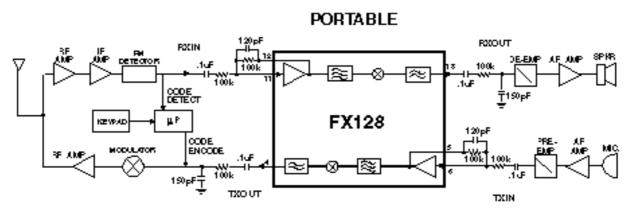

## 1.2 Block Diagram

Figure 1 Block Diagram

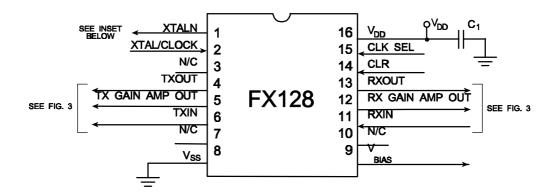

# 1.3 Signal List

| Package<br>D4/P3 | Signal             |       | Description                                                                                                                                                          |  |  |  |

|------------------|--------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin No.          | Name               | Туре  |                                                                                                                                                                      |  |  |  |

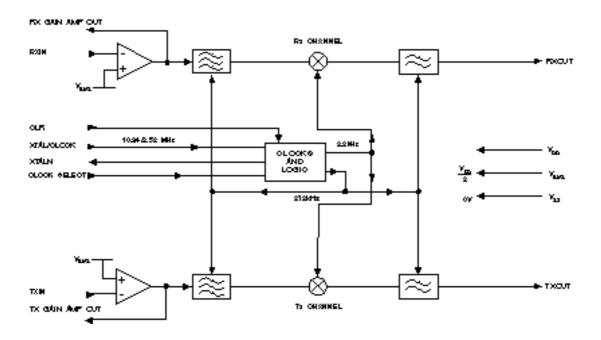

| 1                | XTALN              | O/P   | This is the output of the clock oscillator inverter.                                                                                                                 |  |  |  |

| 2                | XTAL/CLOCK         | I/P   | 10.24MHz or 3.58/3.6864 MHz or an externally derived clock is injected at this pin. See Figure 2.                                                                    |  |  |  |

| 3                | -                  | N/C   | No connection should be made to this pin.                                                                                                                            |  |  |  |

| 4                | TXOUT              | O/P   | This is the analogue output of the transmit channel. It is internally biased at VDD/2.                                                                               |  |  |  |

| 5                | TX GAIN AMP<br>OUT | O/P   | This is the output pin of the transmit gain adjusting opamp. See Figure 3 for gain setting components.                                                               |  |  |  |

| 6                | TXIN               | I/P   | This is the analogue signal input to the transmit channel. This input goes to a gain adjusting op-am whose gain is set by external components.  See Figure 3.        |  |  |  |

| 7                | -                  | N/C   | No connection should be made to this pin.                                                                                                                            |  |  |  |

| 8                | VSS                | Power | Negative supply (GND)                                                                                                                                                |  |  |  |

| 9                | VBIAS              | O/P   | This is an internally generated bias voltage output (VDD/2)                                                                                                          |  |  |  |

| 10               | -                  | N/C   | No connection should be made to this pin.                                                                                                                            |  |  |  |

| 11               | RXIN               | I/P   | This is the analogue signal input to the receive channel. This input goes to a gain adjusting op-amp whose gain is set by external components.  See Figure 3.        |  |  |  |

| 12               | RX GAIN AMP<br>OUT | O/P   | This is the output pin of the receive gain adjusting opamp. See Figure 3 for gain setting components.                                                                |  |  |  |

| 13               | RXOUT              | O/P   | This is the analogue output of the receive channel. It is internally biased at VDD/2.                                                                                |  |  |  |

| 14               | CLR                | I/P   | A logic 1 on this input selects the invert mode. A logic 0 selects the clear (not inverted) mode.                                                                    |  |  |  |

| 15               | CLOCK<br>SELECT    | I/P   | Selects either 10.24 or 3.58/3.6864 MHz clock frequency. A logic "1" selects 10.24MHz and a logic "0" selects 3.58/3.6864 MHz. This input is internally pulled high. |  |  |  |

| 16               | VDD                | Power | Positive supply of 3.0 to 5.5V.                                                                                                                                      |  |  |  |

Notes: I/P = Input

O/P = Output

N/C = No Connection

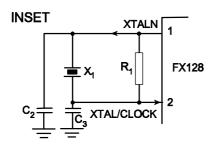

### 1.4 External Components

| Component  | Value              | Value              |

|------------|--------------------|--------------------|

| X1         | 10.24MHz           | 3.58/3.6864 MHz    |

| R1         | $1.0 { m M}\Omega$ | $1.0 { m M}\Omega$ |

| C1         | 0.47µF             | 0.47µF             |

| C2         | 22.0pF             | 33.0pF             |

| C3         | 22.0pF             | 47.0pF             |

| Tolerance: | $R = \pm 10\%$     | $C = \pm 20\%$     |

Note: Xtal circuitry shown is in accordance with CML's Xtal Application Note.

Figure 2 Recommended External Components

### 1.5 Application

Note: Components shown set a gain of 0tB

Figure 3 Block Diagram of a Typical Application of the FX128 (Cordless Phone)

#### 1.6 Application Notes

Formulae for calculating the carrier frequency, upper cutoff frequency and lower cutoff frequency with clock select pin high are as follows:

Carrier Frequency = (3.2995kHz / 10.24MHz) \* XTAL frequency Upper Cutoff Frequency = (2.800kHz / 10.24MHz) \* XTAL frequency Lower Cutoff Frequency = (400Hz / 10.24MHz) \* XTAL frequency

Formulae for calculating the carrier frequency, upper cutoff frequency and lower cutoff frequency with clock select pin low are as follows:

Carrier Frequency = (3.2995kHz / 3.415MHz) \* XTAL frequency Upper Cutoff Frequency = (2.800kHz / 3.415MHz) \* XTAL frequency Lower Cutoff Frequency = (400Hz / 3.415MHz) \* XTAL frequency

## 1.7 Performance Specification

#### 1.7.1 Electrical Performance

#### **Absolute Maximum Ratings**

Exceeding these maximum ratings can result in damage to the device.

| General                                         | Min   | Max              | Units |

|-------------------------------------------------|-------|------------------|-------|

| Supply (V <sub>DD</sub> - V <sub>SS</sub> )     | - 0.3 | 7.0              | V     |

| Voltage on any pin to V <sub>ss</sub>           | -0.3  | $(V_{DD} + 0.3)$ | V     |

| Current in or out of $V_{DD}$ and $V_{SS}$ pins | -30   | +30              | mA    |

| Current in or out of any other pin              | -20   | +20              | mA    |

| D4 and P3 Packages                              |       |                  |       |

| Total Device Dissipation at Tamb = 25°C         |       | 800              | mW    |

| Derating                                        |       | 10               | mW/°C |

| Storage Temperature                             | -55   | +125             | °C    |

| Operating Temperature                           | -40   | +85              | °C    |

#### **Operating Limits**

Correct operation of the device outside these limits is not implied.

|                                             | Min. | Max.  | Units |

|---------------------------------------------|------|-------|-------|

| Supply (V <sub>DD -</sub> V <sub>SS</sub> ) | 3.0  | 5.5   | V     |

| Operating Temperature                       | -40  | +85   | °C    |

| Clock Frequency                             |      | 10.24 | MHz   |

#### **Operating Characteristics**

For the following conditions unless otherwise specified:  $V_{DD} = 3.3V$  at Tamb = 25°C Clock Frequency = 10.24MHz

Audio Level 0dB ref. at 1kHz =  $(V_{DD} - 1) \times 150 \text{vrms}$  e.g.  $V_{DD} = 3.3 \text{V}$  0dB = 345mVrms

|                                                                  | Notes  | Min.       | Тур.            | Max.       | Units             |

|------------------------------------------------------------------|--------|------------|-----------------|------------|-------------------|

| Static Values Supply Current                                     |        | -          | 2.0             | 3.0        | mA                |

| <b>Input Impedance</b> Digital Amplifiers                        | 2<br>2 | 100<br>1.0 | -<br>10.0       | -<br>-     | kΩ<br>MΩ          |

| Output Impedance (RXOUT, TXOUT)                                  |        | -          | 1.0             | -          | $k\Omega$         |

| Input Logic '1' Voltage<br>Input Logic '0' Voltage               | 1<br>1 | 70%<br>-   | -<br>-          | -<br>30%   | $V_{DD} \ V_{DD}$ |

| Dynamic Values                                                   |        |            |                 |            |                   |

| General Analog Signal Input Levels Analog Output Noise           | 4      | -16.0<br>- | -<br>2.5        | 3<br>5.0   | dB<br>mVrms       |

| Clear Mode Passband -3dB Cutoff Frequencies Low High             |        | -<br>3000  | -               | 300<br>-   | Hz<br>Hz          |

| Passband Ripple (300-3000Hz) Rx Channel Tx Channel               |        | 0<br>0     | -<br>-          | 3.6<br>2.9 | dB<br>dB          |

| Passband Ripple (500-2750Hz <b>)</b><br>Rx Channel<br>Tx Channel |        | 0<br>0     | -<br>-          | 2.2<br>2.0 | dB<br>dB          |

| Filter Attenuation at 3.3kHz Rx and Tx Channel                   |        | -          | 30              | -          | dB                |

| Filter Attenuation at 3.6kHz<br>Rx and Tx Channel                |        | -          | 45              | -          | dB                |

| Passband Gain (@ 1kHz ref.) Rx and Tx Channel                    |        | -1.5       | -               | 0.5        | dB                |

| Switched-Capacitor Filter Sampling Carrier Frequency             |        | -          | 211.066<br>3298 | -<br>-     | kHz<br>Hz         |

|                                         | Notes | Min. | Тур. | Max. | Units   |

|-----------------------------------------|-------|------|------|------|---------|

| Invert Mode Combined Tx and Rx Response |       |      |      |      |         |

| Passband -3dB Cutoff Frequencies        |       |      |      |      |         |

| Low                                     |       | -    | -    | 400  | Hz      |

| High                                    |       | 2800 | -    | -    | Hz      |

| Passband Gain                           |       | -3   | _    | 0.5  | dB      |

| Distortion (@ 1kHz)                     | 3     | -    | 1.75 | 2.75 | %       |

| Passband Gain (@ 1kHz ref.)             | 5     | -2.5 | -1.5 | 0    | dB      |

| Low Frequency Roll-off (<200Hz)         |       | 12   | -    | -    | dB/oct. |

| Invert Mode Single Channel Response     |       |      |      |      |         |

| Unwanted Modulation Products            | 3     |      |      |      |         |

| Rx and Tx Channel                       |       | -    | -40  | -    | dB      |

| Carrier Breakthrough                    | 3     |      |      |      |         |

| Rx and Tx Channel                       | -     | -    | -55  | -    | dB      |

| Baseband Breakthrough                   | 3     |      |      |      |         |

| Rx and Tx Channel                       |       | -    | -40  | -    | dB      |

#### **Operating Characteristics Notes:**

- 1. Batch sampled only.

- 2. By characterisation only.

- 3. Measured with Input Level 0dB.

- 4. Short circuit Rx or Tx input, measure noise at corresponding analogue output, in 30kHz bandwidth.

- 5. Op Amp gain 0dB.

- 6. Clear mode only.

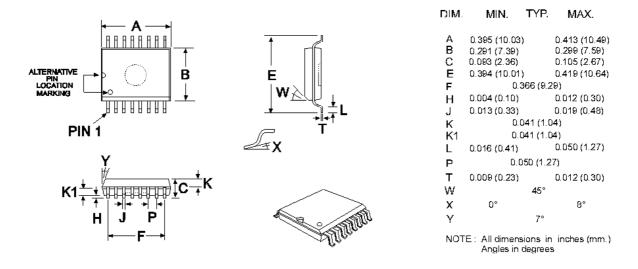

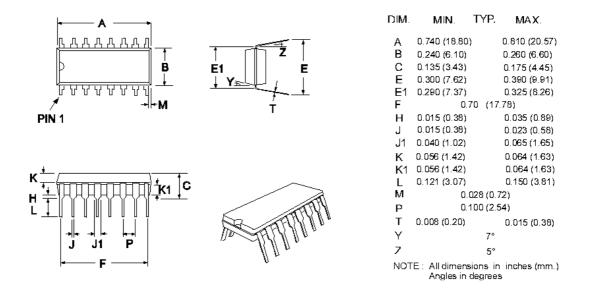

#### 1.7.2 Packaging

Figure 4 16-pin SOIC Mechanical Outline: Order as part no. FX128D4

Figure 5 16-pin Plastic DIL Mechanical Outline: Order as part no. FX128P3

Handling precautions: This product includes input protection, however, precautions should be taken to prevent device damage from electro-static discharge. CML does not assume any responsibility for the use of any circuitry described. No IPR or circuit patent licences are implied. CML reserves the right at any time without notice to change the said circuitry and this product specification. CML has a policy of testing every product shipped using calibrated test equipment to ensure compliance with this product specification. Specific testing of all circuit parameters is not necessarily performed.

# **CONSUMER MICROCIRCUITS LIMITED**

1 WHEATON ROAD WITHAM - ESSEX CM8 3TD - ENGLAND Telephone: +44 1376 513833

Telefax: +44 1376 518247

e-mail: sales@cmlmicro.co.uk

http://www.cmlmicro.co.uk