# **CONSUMER MICROCIRCUITS LTD**

PRODUCT INFORMATION

**QTC Address Decoder**

**Obsolete Product** - For Information Only -

Publication D/103/2 February 1990

### PRELIMINARY INFORMATION

|    | PIN FUNCT                              | NOI             | IS             | PIN CONFIGURATION           |                |

|----|----------------------------------------|-----------------|----------------|-----------------------------|----------------|

| 1  | Data change                            | 15              | D10            | (28 lead                    |                |

| 2  | Power up reset                         | 16              | D11            | Dual-in-Line)               |                |

| 3  | Vss                                    | 17              | D12            | 月1 <sup>1</sup> 28 円 28 円 1 |                |

| 4  | Alert reset                            | 18              | D13            |                             |                |

| 5  | Decode abort                           | 19              | Group digit !0 |                             | FX 103         |

| 6  | Preamble mode                          | 20              | All-call inh.  |                             |                |

| 7  | Alert output                           | 21              | Mute output    |                             |                |

| 8  | 23kHz clock                            | 22              | Mute reset     |                             |                |

| 9  | <u>Qp</u>                              | 23              | VDD            | g                           | QTC<br>ADDRESS |

| 10 | Q1 DECIMAL                             | 24              | N/C            |                             | DECODER        |

| 11 | Q2 ADDRESS                             | 25              | DO             | <u> ф14 15</u> þ            |                |

| 12 | Q3 DIGITS SELECT                       | 26              | D1 QTC<br>DATA |                             |                |

| 13 | Q4                                     | 27              | D2 INPUTS      |                             |                |

| 14 | <b>Q</b> 5                             | 28              | D3             |                             |                |

|    | <ul><li>・ ことのなるのでもは「単元で制度を制度</li></ul> | 796, Tabrill (7 |                |                             |                |

- **FEATURES** 1 TO 5 DIGIT ADDRESS DECODING

- 2nd ADDRESS DECODING

- GROUP & ALL-CALL DECODING

- CODED-BLEEP ALERT OUTPUT

- ON-CHIP ALERT TIMEOUTS

- AUDIO UNMUTE SWITCH OUTPUT

- CALL-CODED MUTE RESET

- 'ABSENT PAGE' MEMORY RECALL

- PREAMBLE MODE OPTION

- LOW POWER CMOS PROCESS

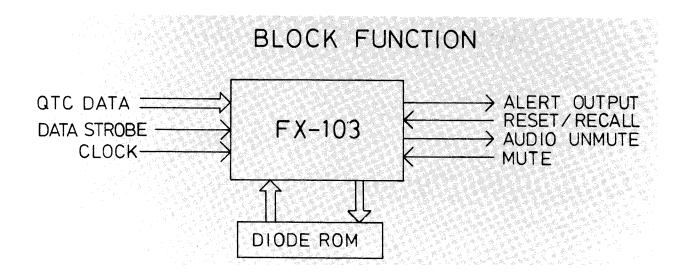

#### DESCRIPTION

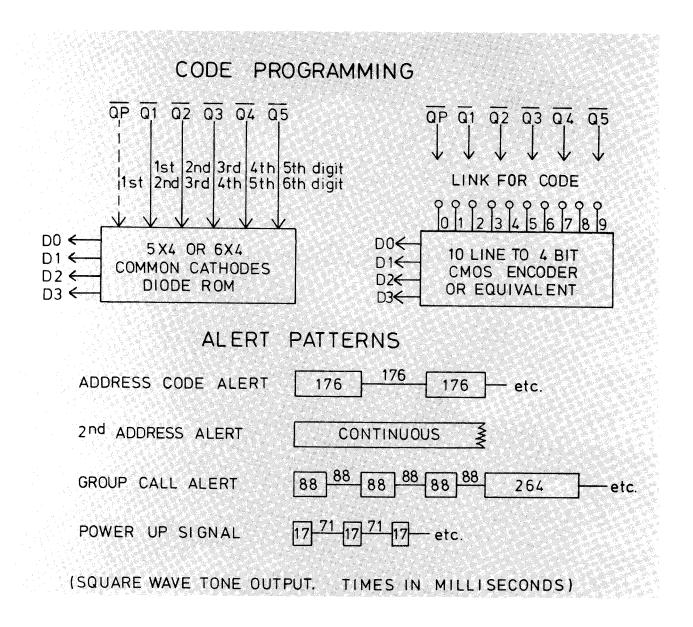

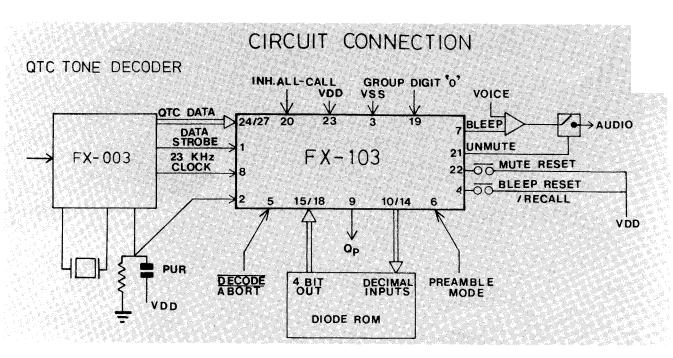

The FX-103 is a versatile and powerful address decoder designed for use in pagers, portable transceivers and mobile radios using tone coded selective signalling. It accepts 4-bit 'QTC coded' output characters from a FX-003 tone decoder and compares them with an address code held in a diode ROM. When the correct code sequence is received the 103 outputs a coded-bleep alert signal. A 2nd distinctive alert pattern is generated if the '2nd Address' code is received, and a 3rd pattern is output for valid group codes. A further pattern is generated on power-up (not applicable during the power cycling routine in Preamble mode).

The FX-103 operates in accordance with the advanced 'HSC' decoding rules, which ensures freedom from cross-code responses and noise triggered false calls.

The alert output signal automatically times-out after 10 seconds, unless reset earlier by the Alert Reset input. Alerts which are not reset by expiration of the timeout period are 'memorised', and may be recalled by operating the Alert Reset input at any later time. The memory outputs the coded pattern of the last 'absent' call received.

An audio unmute output is provided and is switched (unmute) for every valid call. It may be reset manually, through the Mute input, or remotely by an address or group call containing the 'Mute' suffix code. A different suffix code allows the memory contents to be erased if, for example, action is no longer required.

Only the primary address code needs to be programmed in the ROM; group and suffix codes are decoded on-chip. Addresses are programmed 'as written'; consecutive identical digits are automatically translated into 'E' characters (repeat) on-chip. If character E is programmed into the ROM it acts as a termination of the preceding address code digits, and therefore permits shortened codes (1 to 4 digits) to be used. No termination is required in the ROM for 5-digit codes, or 6-digit Preamble mode codes.

As an alternative to a diode ROM, a decimal to binary encoder may be used and the decimal sequence outputs  $\overline{Q1} - \overline{Q5}$ , or  $\overline{Qp} - \overline{Q5}$ , linked to the encoder inputs in the required code sequence.

FX-103 pin-select options include Group Digit '0' (numeric zero becomes the group digit in place of the normal HSC digit 'A'), All-call Inhibit (a group digit received in the Preamble or 1st digit code positions becomes invalid) and Decode Abort (forces invalid at any stage in a decode sequence). The latter facility is useful for imposing externally determined timing limits etc. on the interval between successive code characters, should formal compliance with older signalling standards be required.

A further option is Preamble mode, which is sometimes used to reduce battery drain in pagers. When Preamble is selected the  $\overline{\rm Qp}$  output is enabled and is used to select the preamble digit programmed into ROM. On power-up, the first 'non-F' digit received must be the preamble digit or the device locks-out into the inhibit condition. The inhibit state can only be cleared by powering down. If the correct preamble digit is received following power-up the 103 reverts to normal decode mode, i.e. looks for the address programmed by  $\overline{\rm Q1}$  thro'  $\overline{\rm Q5}$  in accordance with HSC decoding rules.

# ELECTRICAL CHARACTERISTICS (VDD=5V, CLOCK 23.3kHz, -30°C < TA < +85°C)

|            | Characteristic         |                    | Min      | Тур      | Max               | Unit & Notes                           |

|------------|------------------------|--------------------|----------|----------|-------------------|----------------------------------------|

| VDD<br>IDD | Supply voltage (Vss=0  | OV)                | 4.5      | 5<br>100 | 5.5               | μА                                     |

| VOH<br>VOL | Logic output level     | '1'<br>'0'         | 4.5      |          | 0.5               | (V) I source 0.1mA<br>(V) I sink 0.1mA |

| VIH<br>VIL | Logic input level      | '1'<br>'0'         | 3.5      |          | 1.5               | (V)<br>(V)                             |

| PUR        | Time for PUR pin ≥ '   | 1                  |          | "."      | (mS)              |                                        |

|            | Alert timeout:         | decode<br>power-up | 9<br>4.5 |          | 10<br>5           | (Sec.)<br>(Sec.)                       |

|            | Alert output frequence |                    | 2.12     | }        | (kHz) square wave |                                        |

| Ø          | Clock frequency        |                    | 10       | 23.3     | 35                | (kHz) (1)                              |

<sup>1)</sup> Alert frequency, pattern timing and timeout are directly related to clock frequency.

## **DECODE TRUTH TABLE**

Decode mode NORMAL; 5-digit address code '12345' in ROM.

\*Decode mode PREAMBLE; preamble digit '6', address code '12345' in ROM.

The following input character sequences include all valid codes. Note that the 103 employs OPEN CODE rules when decoding Address Suffix characters, i.e. receipt of the correct suffix code characters is valid without further qualification or termination.

For simplicity, only one group code is used as a Group Code example; any valid HSC Group Code may be used. Only one valid Preamble code is shown, any valid NORMAL code is valid with PREAMBLE.

| Input Code            |   | Decode Function                                  |

|-----------------------|---|--------------------------------------------------|

| F12345F               |   | Address alert, audio unmuted                     |

| F12345B               |   | Address alert, audio unmuted                     |

| F12A45F               |   | Group alert, audio unmuted                       |

| F12A45B               |   | Group alert, audio unmuted                       |

| F12345C               |   | 2nd Address alert, audio unmuted                 |

| F12A45C               |   | 2nd Address alert, audio unmuted                 |

| F12345DC              |   | No alert output, mute audio output               |

| F12A45DC              |   | No alert output, mute audio output               |

| F12345DC              |   | No alert output, mute audio output, erase memory |

| F12A45DC              |   | No alert output, mute audio output, erase memory |

| F123                  |   | Invalid address, inhibit decoding until next 'F' |

| *(PUR)F6F12345F       | ) | Address alert, audio unmuted                     |

| *(PUR)6F12345F        | ) | Address alert, audio unmuted                     |

| *(PUR)F61 )           |   | Invalid address, inhibit decoding until          |

| *(PUR)61 ) _          |   | next 'F', recommence '12' etc.                   |

| *(PUR)F6F1 <u>2</u> 3 | ) | Invalid address, inhibit decoding until          |

| *(PUR)6F123           | ) | next 'F', recommence '12' etc.                   |

| *(PUR)F7              |   | Invalid preamble, inhibit until next PUR         |

| *(PUR) (F or 6)       |   | Invalid preamble, inhibit until next PUR         |

CML does not assume any responsibility for the use of any circuitry described. No circuit patent licences are implied and CML reserves the right at any time without notice to change the said circuitry.