# eZ80 FOURTH-GENERATION Z80 PROCESSOR CORE

PROCESSOR DESCRIPTION

PS002200-ZMP0999

©1999 by ZiLOG, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZiLOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZiLOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. Except with the express written approval of ZiLOG, use of information, devices, or technology as critical components of life support systems is not authorized. No licenses are conveyed, implicitly or otherwise, by this document under any intellectual property rights.

## **GENERAL DESCRIPTION**

The eZ80<sup>TM</sup> is ZiLOG's next-generation Z80<sup>TM</sup> processor. The eZ80 provides 16 times the performance of a traditional Z80. The multiple operating modes of the processor allows Z80 and Z180 code to be run without change in the same application with new code, that takes advantage of the eZ80's 16-MB linear addressing space and enhanced instruction set. These features provide customers performance comparable to 16-bit processors with the form factor and power savings of an 8-bit processor. At the same time, the eZ80 remains 100% Z80 code-compatible, reducing customer development time.

The eZ80 also features a Multiply and Accumulate engine, which enables customers to attack signal-processing applications that require polynomial calculations, such as basic filters.

The eZ80 is internet-ready. ZiLOG can provide a complete TCP/IP stack, allowing for rapid internet connectivity.

The eZ80 also features ZiLOG's Debug Interface (ZDI). This two-pin interface allows advanced debugging features without the cost and difficulty and uncertainty of an in-circuit emulator.

The eZ80 is a licensable soft core, allowing rapid integration into designs.

#### **DETAILED DESCRIPTION**

**Z80 High-Performance Microprocessor Core.** The eZ80 is one of the fastest 8-bit CPUs available today, executing code 4 times faster than a standard Z80 operating at the same clock speed. The increased processing efficiency can be used to improve available bandwidth or to decrease power consumption.

Both the increased clock speed and processor efficiency features provides eZ80 customers 16 times the processing performance. This processing power rivals performance customers would normally expect from 16-bit microprocessors.

**16 MB Linear Address.** The eZ80 is also the first 8-bit microprocessor to support 16 MB linear addressing—a feature that addresses large memories that support complex software applications.

Each software module, or each task under a real-time executive or operating system, can operate in Z80-compatible (64 KB) mode, Z80180-compatible mode (1 MB MMU) mode, or full 24-bit (16 MB) address mode.

**Internet-Ready.** A complete TCP/IP stack is also offered so customers can design products that connect to the Internet.

**Multiply and Accumulate.** A Multiply and Accumulate engine operates in parallel with the eZ80 processor to calculate a sum of products that is the core of digital signal processing. The MAC provides 16x16 multiply and 40-bit accumulation.

**ZDI.** The ZiLOG Debug Interface is a 2-pin communication port. When used with the ZiLOG Develop Suite (ZDS) software, ZDI provides on-chip emulation.

PS002200-ZMP0999 eZ80 1

# **ARCHITECTURAL OVERVIEW**

The eZ80 is ZiLOG's fourth-generation Z80 processor core. It is the basis of a new family of integrated microprocessors, and includes the following features:

- Upward-code-compatible from Z80 & Z180

- Several address-generation modes including 24-bit linear addressing

- 24-bit registers and ALU

- One-clock-minimum bus cycles

- Optional autonomous Multiply-Accumulate engine for DSP applications

# **BLOCK DIAGRAM**

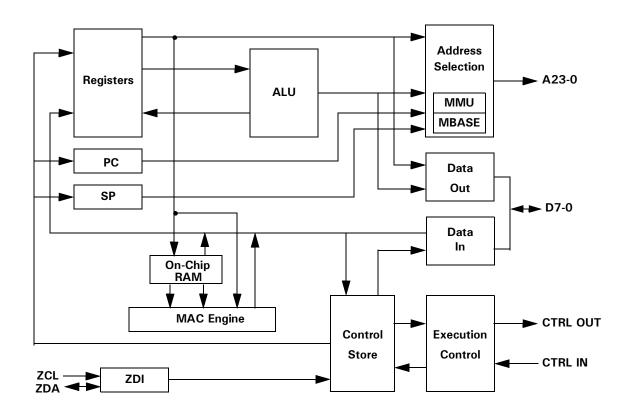

Figure 1 is a block diagram of the eZ80.

FIGURE 1. EZ80 BLOCK DIAGRAM

## **PIN DESCRIPTIONS**

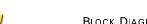

Figure 2 illustrates the logic diagram of the eZ80. Table 1 describes the processor and device pins.

2 eZ80 PS002200-ZMP0999

BLOCK DIAGRAM PIN DESCRIPTIONS

FIGURE 2. EZ80 LOGIC DIAGRAM

PIN DESCRIPTIONS BLOCK DIAGRAM

TABLE 1. PROCESSOR AND DEVICE PIN DESCRIPTIONS

| Symbol | Function                 | Туре                           | Description                                                                                                                                                                                                                                 |

|--------|--------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A23-0  | Address Bus              | Bidirectional, 3-<br>state     | These lines select a location in memory or I/O space to be read or written. The eZ80 does not drive these lines during Reset or external bus acknowledge cycles.                                                                            |

| BUSACK | Bus<br>Acknowledge       | Output, active<br>Low          | The eZ80 responds to a Low on BUSREQ, by 3-stating the address, data, and control signals and driving this line Low.                                                                                                                        |

| BUSREQ | Bus request              | Input, active<br>Low           | External devices can force the eZ80 to release the bus for their use, by driving this line Low.                                                                                                                                             |

| CLK    | Clock                    | Input                          | The master clock of the eZ80.                                                                                                                                                                                                               |

| D7-0   | Data Bus                 | Bidirectional, 3-<br>state     | These lines transfer information to and from I/O and memory devices. The eZ80 drives these lines only during write cycles.                                                                                                                  |

| HALT   | Halt                     | Output, active<br>Low          | A low on this pin indicates that the eZ80 is stopped because of a HALT or SLP instruction.                                                                                                                                                  |

| INSTRD | Instruction<br>Read      | Output, active<br>Low, 3-state | INSTRD Low (with MREQ and MRD Low) indicates that the eZ80 is fetching an instruction from memory. The eZ80 does not drive this line during Reset, nor during bus acknowledge cycles.                                                       |

| INTO   | Interrupt<br>Request 0   | Input, active<br>Low           | External devices can drive this line Low to request an interrupt. The processor responds to this request at the end of the current instruction cycle if it is enabled, and the NMI and BUSREQ signals are inactive.                         |

| ĪNTAK  | Interrupt<br>Acknowledge | Output, active<br>Low, 3-state | INTAK Low indicates that the eZ80 is acknowledging an interrupt request on INTO. The eZ80 does not drive this line during Reset, nor during bus acknowledge cycles.                                                                         |

| IORD   | I/O Read                 | Output, active<br>Low, 3-state | IORD Low indicates that the eZ80 is reading data from a location in I/O space. The addressed I/O device uses this signal to gate data onto the data bus. The eZ80 does not drive this line during Reset, nor during bus acknowledge cycles. |

| ΙΟRΩ   | I/O Request              | Output, active<br>Low, 3-state | IORQ Low indicates that the eZ80 is accessing a location in I/O space. The RD and WR pins indicate the type of access. The eZ80 does not drive this line during Reset, nor during bus acknowledge cycles.                                   |

| IOWR   | I/O Write                | Output, active<br>Low, 3-state | IOWR Low indicates that D7-0 hold data to be stored at the addressed I/O location. The eZ80 does not drive this line during Reset, nor during bus acknowledge cycles.                                                                       |

TABLE 1. PROCESSOR AND DEVICE PIN DESCRIPTIONS (CONTINUED)

| Symbol | Function                 | Туре                           | Description                                                                                                                                                                                                                                                                   |

|--------|--------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MRD    | Memory Read              | Output, active<br>Low, 3-state | MRD Low indicates that the eZ80 is reading data from a location in memory space. The addressed memory uses this signal to gate data onto the data bus. The eZ80 does not drive this line during Reset, nor during bus acknowledge cycles.                                     |

| MREQ   | Memory<br>Request        | Output, active<br>Low, 3-state | MREQ Low indicates that the eZ80 is accessing a location in memory. The RD, WR, and INSTRD pins indicate the type of access. The eZ80 does not drive this line during Reset, nor during bus acknowledge cycles.                                                               |

| MWR    | Memory Write             | Output, active<br>Low, 3-state | MWR low indicates that D7-0 hold data to be stored at the addressed memory location. The eZ80 does not drive this line during Reset, nor during bus acknowledge cycles.                                                                                                       |

| NMI    | Nonmaskable<br>Interrupt | Input, falling-<br>edge active | NMI has a higher priority than INTO and is always recognized at the end of an instruction, regardless of the state of the interrupt enable flipflops. This signal forces processor execution to location 0066H. This input includes a Schmitt trigger to allow RC rise times. |

| RESET  | Master Reset             | Input/Output,<br>active Low    | This signal is used to initialize the eZ80 and other devices in the system. This input must be held Low until the clock is stable. This input includes a Schmitt trigger, allowing RC rise times.                                                                             |

| RETI   | Return from<br>Interrupt | Output, active<br>Low          | A Low on this line indicates that the eZ80 is executing an RETI instruction.                                                                                                                                                                                                  |

| VDD    | Power Supply             |                                | These pins carry power to the device. They must be tied to the same voltage externally.                                                                                                                                                                                       |

| Vss    | Ground                   |                                | These pins are the ground references for the device. They must be tied to the same voltage externally.                                                                                                                                                                        |

| WAIT   | Wait                     | Input, active<br>Low           | External devices can extend bus cycles to more than one clock, by driving this line low.                                                                                                                                                                                      |

# **OPERATIONAL DESCRIPTION**

This section describes, using text, tables, and figures, how the various parts of the eZ80 operate. This description is presented from the processor outward to the peripherals. Refer to the corresponding section of "I/O Registers" on page 20, which describes the eZ80's I/O registers.

PS002200-ZMP0999 eZ80 5

#### PROCESSOR DESCRIPTION

The eZ80 is an 8-bit microprocessor that performs certain 16- or 24-bit operations. In both data sizes, the processor includes an accumulator. Register A is the accumulator for 8-bit operations, and the HL register pair is the accumulator for 16- and 24-bit operations.

# **Processor Program Registers**

In addition to register A, there are six more 8-bit registers named B, C, D, E, H, and L, which can also be operated as register pairs BC, DE, and HL. Flag register F completes the basic register bank.

Two of these basic register banks are included in all Z80 and Z180 processors. High-speed exchange between these banks can be used by a program internally, or one bank can be allocated to the mainline program and the other to interrupt service routines.

Two Index registers IX and IY allow *base and displacement* addressing in memory. IX and IY are not included in the register banks on the eZ80. They are independent of the register banks.

The eZ80 expands the width of the BC, DE, HL, IX, and IY registers from 16 to 24 bits. The Arithmetic/Logic Unit and internal data paths are similarly expanded to 24 bits.

#### **Processor Control Registers**

In addition to the data-oriented registers described above, the eZ80 processor includes several other control registers. Unlike the registers in I/O space that are described in "I/O Registers" on page 20, these control registers have no addresses, but are used implicitly in certain processor operations.

**Program Counter (PC).** This 16- or 24-bit register tracks program execution by the processor, which automatically increments PC while fetching instructions. The processor stores PC on the stack when it executes a CALL or RST instruction, or an interrupt or Trap occurs. It loads PC with a new value when it executes a JUMP, CALL, RST, or RET instruction, and when an interrupt, Trap, or Reset occurs. PC resets to 0000.

**Stack Pointer (SPS or SPL).** SPS is a 16-bit register that is used when the ADL bit is cleared, while SPL is a 24-bit register that is used when ADL is set. The processor decrements the current SP register by 2 or 3, and stores a 16- or 24-bit value in memory at this updated address, when it executes a PUSH, CALL, or RST instruction, and when an interrupt or Trap occurs. The processor fetches a 16- or 24-bit value from memory at the address in SP, and then increments SP by 2 or 3, when it executes a POP, RET, RETI, or RETN instruction. Software can store the SP value in memory, load SP from memory or another register, or load it with a constant/immediate value. Further, software can add or subtract the value in SP to or from another register, and can increment or decrement SP. Finally, software can exchange the 16- or 24-bit value in memory, to which SP currently points, with the contents of a 16- or 24-bit register. SP resets to 0000.

6 eZ80 PS002200-ZMP0999

**Flags (F).** The processor includes two Flag registers each containing six bits, named Zero (Z), Carry (CF), Sign (S), Parity or Overflow (P/V), Half-Carry (HC) and Add/Subtract (N). Certain flags are automatically updated as part of executing certain instructions. Subsequent instructions can then use the flags, either as an operand (ADC, SBC, DAA), or to determine whether to perform a JUMP, CALL, or RET operation. The flags can be saved on the stack with a PUSH instruction, or restored from the stack with a POP instruction. The two sets of flag registers are paired with the two A accumulators; the current pair is toggled by the EX AF,AF' instruction.

#### **Operating Modes**

The multiple operating modes of the processor allows Z80 and Z180 code to be run without change in *virtual Z80* or *virtual Z180* partitions, in the same application with new code that takes advantage of the eZ80's 16-Mbyte linear addressing space and enhanced instruction set.

These operating modes are governed by four factors:

- A state bit called Address and Data Long (ADL)

- Another state bit called *mixed ADL*

- An 8-bit register called MBASE, and

- The state of the eZ80's 80180-compatible Memory Management Unit (MMU)

**Native Z80 Mode.** ADL, mixed ADL, and MBASE reset to 0, and the MMU resets to an inactive state. In this Native Z80 state, the programming model includes 16-bit registers and addresses, and a 64 KB memory space at the start of the eZ80's potential 16-Mbyte memory space.

**Virtual Z80 Mode.** If ADL is cleared, the MMU is not enabled, but MBASE contains a non-zero value, the programming model still includes 16-bit registers and a 64 KB memory space, but this space is relocated by MBASE. In this Virtual Z80 mode, several tasks can each have their own Z80 partition.

**Native Z180 Mode.** If ADL is cleared, MBASE contains zero, and the MMU is active, the programming model is fully Z80180-compatible. The model includes 16-bit registers and a 64 KB *logical* memory addressing space, but the MMU translates these logical addresses to 20-bit *physical* addresses. The 64 KB logical address space can be divided into one to three *areas*, two of which can be relocated anywhere within the first 1 MB of the eZ80's potential 16-Mbyte memory space.

**Virtual Z180 Mode.** If ADL is cleared, the MMU is active, and MBASE contains a non-zero value, the MMU handles mapping within a 1M byte virtual physical address space that is relocated by MBASE. In this Virtual Z180 mode, several tasks can each have their own Z180 partition.

**ADL Mode.** If ADL is set, neither the MMU nor MBASE has any effect on memory addressing. In this mode, the PC, BC, DE, HL, IX and IY registers are expanded from 16 to 24 bits, and a 24-bit Stack Pointer Long (SPL) register replaces the 16-bit Stack Pointer Short (SPS) register that is used in the other modes. When the processor fetches an instruction that includes a 16-bit address or immediate datum in the other modes, it automatically fetches a 24-bit address or datum. Code that operates in ADL mode must be generated by an eZ80-compatible compiler or assembler that generates such instructions.

**Mode Switching.** The eZ80 switches between ADL mode and any of the other modes only as part of a specially-prefixed CALL, JP, RET, or RST instruction, or an interrupt or trap operation. The MBASE register can be changed only in ADL mode. The MMU can be programmed in any mode, but in a non-ADL mode software must take care not to affect its Program Counter when programming the MMU.

**Interrupt and Traps.** Applications that operate only in Native Z80 mode, ADL mode, or Native Z180 mode with Common Bank 0 always enabled, are relatively simple with respect to interrupts and traps. In these modes, memory always starts at the start of the eZ80's potential 16-Mbyte memory space, and the interrupt and trap locations are never mapped.

However, applications that switch between modes, or operate in Virtual Z80, Virtual Z180, or Native Z180 mode with Common Bank 0 disabled, simplify interrupts and trap handling by executing a STMIX instruction to set the mixed ADL bit.

If the mixed ADL bit is 1, interrupts and instruction traps stack the ADL state as well as the PC, and enter ADL mode in the first 64K bytes of the eZ80's potential 16M byte memory space.

#### I/O Space

A separate I/O space includes on-chip and off-chip peripheral devices. On the Z80, I/O space included 8-bit addresses and 256 bytes. All Z180 processors, and the eZ80, feature an expanded I/O space with 16-bit addresses and 64K bytes. The eZ80 includes a few on-chip peripherals in I/O space, which can be augmented by external peripherals.

## **Other Processor Control Registers**

Interrupt High Address (I). The contents of this register are used as the eight high-order address bits, when the processor fetches the address of an interrupt service routine from memory, for an interrupt from the INTI or INT2 pin, or from an on-chip peripheral. The I register points at a table of interrupt service routine addresses, that starts at a 256-byte boundary in the 64K-byte logical address space. The I register resets to 0, and can be read or written by the dedicated instructions LD A,I and LD I,A.

**R Counter (R).** On the Z8018x processors family, this register contains a count of executed fetch cycles. R resets to 0, and can be read or written by the dedicated instructions LD A,R and LD R,A.

#### **Illegal Instruction Traps**

Like most processors, the defined instruction set for the Z8018x family does not fully cover all possible sequences of binary values. The Op Code maps, which begin on page 43, include numerous blank cells. These represent Op Code sequences for which no operation is defined, and are commonly called illegal instructions.

When an eZ80 or other Z8018x processor fetches one of these sequences, it performs a Trap sequence as follows:

- 1. The processor sets the TRAP bit in the Interrupt/Trap Control register.

- If the processor detected the condition while fetching the second byte of the instruction, it clears the UFO bit in the Interrupt/Trap Control register. If the processor detected the condition while fetching the third byte, the processor sets UFO.

- 3. The processor decrements the Stack Pointer (SP) by two and stores the 16-bit logical address from PC, in memory at the new SP address. This address points to the last byte of the illegal Op Code sequence.

- 4. The processor then clears PC and resumes execution at logical address 0000.

**Trap Handling.** The code at logical address 0000 can optionally store the value of SP in memory, and then set SP to an area of memory dedicated to its private stack.

In all cases, the trap-handling routine must store as many registers among AF, BC, DE, HL, IX, and IY as it may use (worst case), by pushing them onto the stack. A general-purpose routine stores all of these registers, those in the alternate set, the value of I and the state of the Interrupt Enable flag.

Next, the Trap-handling code must distinguish among the four events that can bring execution to address 0000:

- A Reset

- A Trap

- A RST 0 instruction

- A program error such as a JUMP to a null pointer.

The code can detect a Trap by reading the Interrupt/Trap Control register (ITC) and checking bit 7 (TRAP). If this bit is 1, a Trap has occurred, and ZiLOG recommends that the Trap-Handling Routine proceed as follows:

- Clear the TRAP bit by writing a 0 to bit 7 of the ITC

- Fetch the PC value stored on the stack

- Examine bit 6 of the ITC (UFO).

• If the UFO bit is 0, decrements the PC value by one, else decrement it by two, so that it points to the start of the illegal instruction.

The next action of the trap-handling routine depends on the application and its stage of development.

**Extending the Instruction Set.** Core software can use illegal instructions as extensions to the eZ80 instruction set. To accomplish this, the trap handler must fetch and examine each illegal instruction. If an illegal instruction is an extension, the trap handler performs the extended operation that the instruction indicates. It then advances the stacked PC value over the instruction, restores the saved register values, and returns to the next instruction.

**Error Message vs. Restart.** Except for such extended instructions, the trap handling software can either:

- Output an error message and wait for someone to examine the situation and restart the application, or

- Attempt to restart the application immediately.

The former course is more common in the debugging/development stages of an application, while the latter may be more appropriate in the production/deployment stage. In the latter case, software may log the event for future readout, using an external storage medium or just in memory.

#### **INTERRUPTS**

ZiLOG Z80 and Z80180 processors have a rich legacy of sophisticated interrupt capabilities. The eZ80 includes aspects of both families' interrupt characteristics.

## Interrupt Resources in the eZ80

**IEF1 and IEF2.** These bits are internal to the processor and can only be affected and manipulated by certain specific events:

- Reset clears IEF1 and IEF2

- EI instructions set IEF1 and IEF2

- DI instructions clear IEF1 and IEF2

- An NMI sequence copies IEF1 to IEF2, then clears IEF1

- A maskable interrupt clears IEF1 and IEF2

- An LD A,I or LD A,R instruction copies IEF2 to the P/V flag

- An RETN instruction copies IEF2 to IEF1

When IEF1 is 1,  $\overline{\text{RESET}}$  and  $\overline{\text{BUSREQ}}$  are both High, and falling edge has occurred on  $\overline{\text{NMI}}$ , the eZ80 checks for maskable interrupt requests from external pins and on-chip peripherals, as it completes each instruction, or each instruction iteration for HALT, the block I/O instructions, block move instructions, and block scan instructions.

**The I Register.** The eZ80 uses the contents of this register as A15–8 of the logical address for fetching interrupt service routine addresses from memory, and in response to interrupt requests from internal peripherals.

#### Nonmaskable Interrupt (NMI)

The eZ80 latches falling edges on the NMI pin. Only a Low on RESET or on BUSREQ takes precedence over NMI. Unless RESET or BUSREQ is Low, the eZ80 checks for a falling edge on NMI as it completes each instruction (each instruction iteration of HALT, the block I/O instructions, block move instructions, and block scan instructions), and performs an NMI sequence if a falling edge has occurred.

An NMI sequence includes four steps. The processor:

- 1. Copies the state of the IEF1 bit to IEF2.

- 2. Clears IEF1 to prevent maskable interrupts.

- 3. Decrements SP by 2, and stores the logical address in the PC in memory at the new address in SP. For most interrupts, this address is the address of the instruction the processor would have executed next, if no interrupt had occurred. If the processor was stopped by HALT or SLP, the value is the address of the next instruction. In the event of an incomplete block transfer, block scan, or block I/O instruction, it is the address of the instruction.

- 4. Loads 0066H into PC, and resumes execution from that logical address.

**NMI** Handling. NMI routines fall into two categories, based on whether the external hardware that drives  $\overline{\text{NMI}}$  is capable of producing another falling edge on the pin, before the NMI service routine has completed its execution and returned to the interrupted process. The case when another falling edge cannot be produced is called *Single Edge Guaranteed*. The case when it is possible to produce another falling edge is called *Repeated Edge Possible*. Debug monitors, which display the state of the interrupted process, fall into the Repeated Edge category.

**Single Edge Guaranteed.** An NMI routine in this category is similar to other interrupt service routines. This routine has the option of storing the contents of SP in memory and loading SP with the address of a memory area that is dedicated for its stack. In any case it must store as many of the registers as it may use during its execution (worst case).

**Repeated Edge Possible.** An NMI routine in this category start with a PUSH AF instruction, then load A from a dedicated location in memory that indicates whether the interrupted process is the NMI routine. If this location indicates that the location is the NMI process, the routine immediately must perform a POP AF and then an RETN instruction, to return to its former execution.

If the in NMI location is cleared, software must set it. Then, if the NMI routine does either of the following:

• A DI instruction in a *Save The Registers* routine that it shares with other means of entry, or

• Displays the I register or the interrupt-enable state of the interrupted process, and allows a user/programmer to change these (in essence, a debug monitor)

the NMI must perform LD A, I and PUSH AF instructions. These instructions store the I register at the address in SP plus 1, and the interrupt enabled state (IEF2) in the

P/V flag and in bit 2 of the memory location pointed to by SP.

If the NMI routine uses a common *Save The Registers* subroutine that it shares with other entry points, the save subroutine can perform a DI instruction to prevent interruption by maskable interrupts.

The NMI routine has the option to store the SP value in a dedicated location in memory, and load SP with the address of a dedicated NMI stack area.

In any case, the NMI routine must PUSH as many other registers as it will use (worst case). A debug monitor typically pushes all registers in both banks, so that it can display them.

**Exiting The NMI Routine.** On completion of its processing, an NMI routine must restore the saved registers. If the routine uses its own stack area, the routine then restores the SP value of the interrupted process. If the routine set an in NMI memory location on the way in, the routine clears this location.

NMI routines that did *not* save the I register and IEF2 state at the start, can conclude with POP AF and RETN instructions. RETN copies the state of IEF2 back into IEF1, restoring the interrupt enable state of the interrupted process.

NMI routines that saved I and IEF2 at the start, must conclude with a POP AF for the saved I register and IEF2 bit, then, an LD I,A, followed by a JP V to a POP AF, EI, RET sequence. The JP instruction is followed by LD I,A, POP AF, and RET instructions.

INT<sub>0</sub>

**INTO Modes.** The eZ80 can handle interrupts requested by a device on the  $\overline{\text{INTO}}$  pin, in any of three ways called modes 0, 1, or 2.

The special instructions IM 0, IM 1, and IM 2 select among these three modes. Reset selects mode 0.

**INTO** Processor Response. The eZ80 performs an  $\overline{\texttt{INTO}}$  interrupt sequence at the end of an instruction<sup>1</sup>, if all of the following are true:

- <del>INTO</del> is Low

- Bit 0 of the Interrupt/Trap Control register is 1 to enable INTO

- IEF1 is 1, enabling interrupts in general

- RESET and BUSREQ are both High

- A negative edge on MMI has not been detected

12 eZ80 PS002200-ZMP0999

<sup>1.</sup> Each instruction iteration for HALT, the block I/O, block move, and block scan instructions

When all of these conditions occur simultaneously, the eZ80 responds.

While all <u>INTO</u> acknowledge cycles follow a general pattern, they differ as to what (if anything) the processor does with the data on D7-0, and what it does after the acknowledge cycle. These actions depend on the most recently executed IM instruction (if any), as described in the next three sections.

**INTO Mode 0.** If no IM instruction has been executed since Reset, or if the most recently executed IM instruction was IM 0, the eZ80 performs an  $\overline{\texttt{INTO}}$  sequence as follows:

- 1. It clears IEF1 and IEF2, preventing further interrupts

- 2. It drives **INSTRD** Low

- 3. It waits several clock cycles

- 4. It drives TORQ Low. Simultaneous lows on TNSTRD and TORQ indicate an TNTO interrupt acknowledge cycle. In response to this condition, the highest-priority peripheral that is requesting an interrupt places an 8-bit value on the D7-0 data bus.

- 5. It samples  $\overline{WAIT}$ , and waits until it is High.

- 6. It samples D7-0 and interprets the value as an instruction Op Code. In this mode, the vector registers of all ZiLOG daisy-chainable peripherals must be programmed to provide one of the RST Op Codes C7, CF, D7, DF, E7, EF, F7, or FFH.

#### **Notes:**

- 1. Read RST as Restart.

- 2. The eZ80 does not automatically stack the contents of the program counter during an INTO Mode 0 interrupt sequence. This means that the only other Op Code that a peripheral can return (assuming the interrupted process is to be restarted) is a CALL instruction DCH. Intel 808x-family interrupt controllers can return a three-byte CALL instruction, but ZiLOG peripherals cannot.

- 7. It terminates the cycle by driving TNSTRD High, then TORQ High.

- 8. If the Op Code is CALL, the processor fetches two more bytes to complete the instruction.

- 9. The processor decrements SP by 2 and stores the contents of PC in memory at the new address in SP. Typically, this value is the address of the instruction the processor would have executed next, if no interrupt had occurred. If the processor was stopped by HALT or SLP, this value is the address of the next instruction. For an incomplete block transfer, block scan, or block I/O instruction, this value is the address of the instruction.

- 10. If the Op Code was RST, the processor resumes execution at logical address 0000, 0008, 0010, 0018, 0020, 0028, 0030, or 0038H. If the Op Code was CALL, it resumes execution at the logical address fetched in step 8.

In mode 0, each peripheral connected to  $\overline{\text{INT0}}$  must feature a register, the contents of which it returns on D7-0 when it detects  $\overline{\text{INSTRD}}$  and  $\overline{\text{IORQ}}$  Low, and it is requesting an interrupt, and the IEI pin is High. Software programs each such register with one of the RST Op Codes C7, CF, D7, DF, E7, EF, F7 or FFH.

If a peripheral can replace the low-order bits of this value with a code reflecting the peripheral's status, this feature must be disabled for mode 0 operation.

If the number of devices that can interrupt on  $\overline{\text{INT0}}$  is restricted, each device can have its own RST instruction, improving interrupt response time by eliminating the requirement for the interrupt service routine to poll multiple devices.

If multiple devices must share a RST instruction, that interrupt service routine must poll these devices in the same priority order that they are arranged on the IEI-IEO daisy chain. Because a ZiLOG peripheral sets its IUS bit when:

- It detects <u>INSTRD</u> and <u>IORQ</u> Low

- It is requesting an interrupt, and

- Its IEI pin is High.

To insure correct operation of the daisy chain, the polling process must lead to:

- Servicing the highest priority requesting device that performed the poll

- Clearing its IUS bit either explicitly, or for a Z80 peripheral, by concluding the ISR with a RETI instruction.

**INTO Mode 1.** If the most recently executed IM instruction was IM 1, the eZ80 performs an  $\overline{\mathtt{INTO}}$  sequence as follows:

- 1. It clears IEF1 and IEF2, preventing further interrupts

- 2. It drives TNSTRD Low

- 3. It waits several clock cycles

- 4. It drives TORQ Low. Simultaneous Lows on TNSTRD and TORQ indicate an TNTO interrupt acknowledge cycle

- 5. It samples  $\overline{WAIT}$ , and waits until it is High.

- 6. It terminates the cycle by driving TNSTRD High, then TORQ High.

- 7. It ignores the data on D7-0 and substitutes the value FFH, which is RST 38.

- 8. It decrements SP by 2, and stores the contents of PC in memory at the new logical address in SP. Typically, this address is the address of the instruction the processor would have executed next, if no interrupt had occurred. If the processor was stopped by HALT or SLP, this value is the address of the next instruction. For an incomplete block transfer, block scan, or block I/O instruction, this value is the address of the instruction.

- 9. It loads 0038H into PC, and resumes instruction execution from that logical address.

In mode 1, the interrupt service routine must poll all of the devices connected to TNTO, to determine which device generated the interrupt. If any ZiLOG peripherals can request an interrupt, this polling must be performed in the same priority order that the devices are arranged on the IEI-IEO daisy chain. This order is required because a ZiLOG peripheral sets its IUS bit when:

- It detects <u>INSTRD</u> and <u>IORQ</u> Low

- It is requesting an interrupt, and

- Its IEI pin is High.

To ensure correct operation of the daisy chain the polling process must lead to:

- Servicing the device that requested the interrupt

- Clearing the device's IUS bit either explicitly, or for a Z80 peripheral, by concluding the ISR with a RETI instruction.

The best way to ensure this requirement is by actually polling the IUS bits, for devices that allow their IUS bits to be read.

**INTO Mode 2.** If the most recently executed IM instruction was IM 2, the eZ80 performs an  $\overline{\mathtt{INTO}}$  sequence as follows:

- 1. It clears IEF1 and IEF2, preventing further interrupts

- 2. It drives INSTRD Low

- 3. It waits several clock cycles

- 4. It drives TORQ Low. Simultaneous lows on TNSTRD and TORQ indicate an TNTO interrupt acknowledge cycle. In response to this condition, the highest-priority peripheral that is requesting an interrupt places an 8-bit value on the D7-0 data bus.

- 5. It samples  $\overline{WAIT}$ , and waits until it is High.

- 6. It captures the data from D7-0. This byte must have D0 Low/0 for proper operation.

- 7. It terminates the cycle by driving TNSTRD High, then TORQ High.

- 8. It decrements SP by 2, and stores the contents of PC in memory at the new logical address in SP. Typically, this value is the address of the instruction the processor would have executed next, if no interrupt had occurred. If the processor was stopped by HALT or SLP, this value is the address of the next instruction. For an incomplete block transfer, block scan, or block I/O instruction, this value is the address of the instruction.

- 9. It places the contents of the I register on A15-8, the value captured in step 7 on A7-0, and fetches the Less Significant (LS) byte of an interrupt service routine address from memory at that address.

- 10. It drives A0 to go High/1, and fetches the More Significant (MS) byte of the interrupt service routine address from memory at that address.

- 11. It esumes execution at the logical address fetched in steps 9-10.

In mode 2, each peripheral connected to INTO must have an Interrupt Vector Register, the contents of which it returns when:

- The peripheral detects <u>INSTRD</u> and <u>IORQ</u> Low

- The peripheral is requesting an interrupt, and

- Its IEI pin is High.

User software can program each Interrupt Vector register with any even binary value

If a peripheral can replace the low-order bits of this value with a code reflecting its status, this feature can be enabled in mode 2 (in which case the peripheral *occupies more than one slot* in the interrupt vector table). These *Vector includes status* features improve interrupt response time, reducing the amount of status-polling that the interrupt service routine must do, to identify the exact cause of the interrupt.

**Interrupt Handling.** Any Interrupt Service Routine (ISR) may save the contents of SP in memory, and loads SP with the address of a memory area that is dedicated to its stack. Most interrupt service routines do not include these steps.

An  $\overline{\text{INTO}}$  ISR must save the contents of the registers it uses (worst case), using PUSH and/or EX AF, AF' and EXX instructions.

If the application includes a mechanism for allowing nested interrupts, the ISR can begin as specified by that mechanism, leading to an IE instruction that allows the ISR to be interrupted by other interrupts. Most applications do not include these steps.

Next, the ISR must read status registers from each device that can request an interrupt on INTO, to identify the cause of the interrupt. The ISR must handle each interrupting device according to this status, and the device and application requirements.

Many ISRs read data from interrupting device(s), or write data to interrupting device(s). In addition, the ISRs can write registers in interrupting device, to modify the device(s) mode, status, or operation.

When interrupt processing is complete, the ISR may end either of two ways. If nested interrupts were allowed, the ISR ends as specified by the nesting mechanism. If nested interrupts were not allowed, the ISR must restore the saved registers and conclude with EI and RET instructions.

**Note:** the Z80 and Z80180 instruction sets include an RETI instruction, that is used for servicing Z80 peripherals. Because the eZ80 does not include Z80 peripherals, nor does it allow them to be connected externally, there is no reason to ever conclude a eZ80 ISR with an RETI. RET is both shorter and faster than RETI, and has the same function.

#### **MEMORY**

The eZ80 provides several address-generation modes:

**Native Z80 mode.** The total memory address space is the first 64K bytes of the overall eZ80 memory space. Neither the Z80180-compatible Memory Management Unit (MMU) nor the Memory Base (MBASE) register has any effect on addressing.

**Virtual Z80 mode.** The memory address space can be any 64 KB in the overall 16M byte eZ80 memory space, under control of the MBASE register. The MMU has no effect on memory addressing.

**Native Z180 mode.** The memory address space is the first 1M bytes of the overall eZ80 memory space, under control of the Z180-compatible MMU. MBASE has no effect on memory addressing.

**Virtual Z180 mode.** This mode allows the memory address space to be any 1 MB of the overall 16 MB eZ80 memory space, under control of the MBASE register. The MMU operates within the selected 1 MB space.

Address and Data Long (ADL) mode. This mode allows programs compiled or assembled for the eZ80 to operate in a 16M byte linear address space. In this mode, the 16-bit registers PC, BC, DE, HL, IX, and IY expand to 24 bits, as does the width of the ALU. The processor automatically fetches an additional byte of address or immediate data in those instructions that contain a 16-bit address or datum in other modes.

Prefix-override bytes allow any instruction to operate as in ADL mode in one of the first four modes, or to use 16 bits MMU or MBASE addressing in ADL mode.

#### **Addressing Modes**

Instructions may specify a memory address in several ways. eZ80 addressing modes include:

**Relative Addressing.** JR and DJNZ instructions include a signed 8-bit displacement that specifies a range of addresses -126 to +129 from the Op Code, to which program control can be transferred.

**Direct Addressing.** Instructions include a 16-bit or 24-bit logical address, depending on the ADL mode bit.

**Register Indirect Addressing.** The address is taken from one of the register pairs BC, DE or HL.

**Indexed Addressing.** In this mode, instructions include an 8-bit signed displacement from the address in an index register, IX or IY.

Other contexts in which memory is accessed include instruction fetching, interrupts, DMA operations, and cycles generated by external masters while BUSACK is Low.

#### **Memory Management Unit (MMU)**

The eZ80 includes an 80180-compatible Memory Management Unit to enable programs written for an 8018x family processor to be run without change. For new code, the 24-bit linear address mode is far more straightforward and easier to use.

The 16-bit address used by software are called logical addresses. When the MMU is enabled it translates these 16-bit logical addresses into 20-bit physical addresses, as part of all memory accesses performed by the processor. The MMU has no effect on accesses performed by the DMA channels, which include 20-bit address registers. The MMU also has no effect on addresses in I/O space, which always have A23–16 all 0.

The MMU resets to a state in which it has no effect on addresses in processor cycles, passing A15–0 through without change and keeping A23–16 all 0. If an application needs 64 KB of memory or less, the MMU need not be used.

Even when the MMU has been programmed to perform active address translation, it passes A11–0 from the logical to the physical address. In other words, it manages memory in 4 KB blocks.

The section "MMU Registers" on page 20, details the registers associated with the MMU.

**MMU Operation.** The MMU compares bits 15–12 of each logical address to two 4-bit fields in its Common/Base Address Register (CBAR). These comparisons are unsigned.

If bits 15–12 of a logical address are less than the value in bits 3–0 of the CBAR, the MMU maps the address to Common Area 0. For these addresses, the MMU passes bits 15–12 to the A15–12 pins unchanged, and sets A23–16 to 0.

If bits 15–12 of a logical address are greater than or equal to the value in bits 3–0 of the CBAR, but are less than the value in bits 7–4 of the CBAR, the MMU maps the address to the Bank Area. For these addresses, the MMU adds the value in its 8-bit Bank Base Register (BBR) to bits 15–12 of the logical address, and outputs the 8-bit sum on A19–12, and sets A23-20 to 0.

If bits 15–12 of a logical address are greater than or equal to the value in bits 7–4 of the CBAR, the MMU maps the address to Common Area 1. For these addresses, the MMU adds the value in its 8-bit Common Base Register (CBR) to bits 15–12 of the logical address, outputs the 8-bit sum on A19–12, and sets A23-20 to 0.

**NOTE:** The value in bits 7–4 of the CBAR must never be less than the value in bits 3–0 of the CBAR.

**MMU Configurations.** In the general case, the MMU divides the 64 KB logical memory space into three parts. Common Area 0 is located at the start of the 1 MB physical address space. The Bank Area and Common Area 1 are relocatable to other parts of the physical address space under control of the Bank Base Register and Common Base Register, respectively.

18 eZ80 PS002200-ZMP0999

Certain combinations of values in the CBAR result in the logical address space being divided into fewer active areas:

- If the CBAR contains 0, all logical addresses fall into Common Area 1, and are relocated to a contiguous 65KB area starting at the address in the CBR times 4096.

- If CBAR3–0 are 0 but CBAR7–4 are non-zero, the Bank Area and Common Area 1 are active. Logical addresses less than (CBAR7–4)\*4096 are relocated by the Bank Base Register while other addresses are relocated by the Common Base Register.

- If CBAR7–4 and CBAR3–0 are equal and non-zero, Common Area 0 and Common Area 1 are active. Logical addresses less than (CBAR3–0)\*4096 are not relocated and map to the start of physical memory. Other addresses are relocated by the Common Base Register.

**The MMU After Reset.** Because the CBAR resets to 11110000, logical addresses 0000–EFFFH are in the Bank Area and F000–FFFFH are in Common Area 1 after Reset. But since the BBR and CBR both reset to zero, the MMU passes all logical addresses through without change, with A23–16 all 0.

#### INPUT/OUTPUT

The eZ80 includes an I/O space that is distinct from memory space. I/O space is accessed by means of IN and OUT instructions rather than LD, PUSH, POP, and other instructions that access memory space. The MMU passes addresses in I/O space through without change; these addresses always have A23–16 all 0.

#### I/O Instructions

The original Z80 featured a 256-byte I/O space. The following instructions are specific to the Z80's 256-byte I/O space, and must only be used on the eZ80 to address external I/O devices that do not decode A15–8:

```

OUT (port), A

IND

INDR

INI

INIR

OTDR

OTIR

OUTD

OUTI

```

The following instructions ensure that A15–8 are all 0 and can be used to access the eZ80's on-chip I/O registers, as well as external devices that decode A15–8 as all 0s:

```

INO r, (port)

OUTO (port), r

OTDM

OTDMR

OTIM

OTIMR

```

I/O REGISTERS CLOCK CIRCUITS

The following instructions drive A15–0 from the BC register pair and can be used to access the full 64 KB I/O space:

The following instruction can access the entire 64 KB I/O space, by pre-loading bits 15–8 of the address into A. (This step is unnecessary for external devices that do not decode A15–8.)

#### **CLOCK CIRCUITS**

The eZ80 requires a logic-level clock on its CLK pin. This signal must be free of overshoot or ringing and must make continuous, monotonic, and rapid transitions in both directions.

# **RESET CONDITIONS**

The effects of Reset on each of the registers in I/O space is described in Tables 2–4 in "I/O Registers". Among processor registers, the following registers and state bits are cleared to 0: ADL, Mixed ADL, MBASE, PC, SP, I, IEF1, IEF2, R, and F. The following are not changed by Reset: A, B, C, D, E, H, L, IX, and IY.

## I/O REGISTERS

Preceding sections describe the processor registers and the eZ80's programming model. This section describes the registers in I/O space that control the operation of the overall device and its on-chip peripherals. Register addresses that do not appear in this table are not used.

## **REGISTERS SUMMARY**

| Register Name             | Addr (hex) | Register Name      | Addr (hex) |

|---------------------------|------------|--------------------|------------|

| Common Base Register      | 38         | Bank Base Register | 39         |

| Common/Bank Area Register | 3A         |                    |            |

## MMU REGISTERS

See the <u>Memory Management Unit</u> section, starting on page 18, for additional register information.

TABLE 2. COMMON BASE REGISTER (0038H) CBR

| Bit                                          | 7 | 6                     | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------------------------------------|---|-----------------------|---|---|---|---|---|---|

| Bit/Field                                    |   | Base of Common Area 1 |   |   |   |   |   |   |

| R/W                                          |   | R/W                   |   |   |   |   |   |   |

| Reset                                        | 0 | 0 0 0 0 0 0 0         |   |   |   |   |   |   |

| Note: $R = Read W = Write X = Indeterminate$ |   |                       |   |   |   |   |   |   |

| Bit      |                       |     |       |                                                                                                                                                                                                                  |

|----------|-----------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Position | Bit/Field             | R/W | Value | Description                                                                                                                                                                                                      |

| 7-0      | Common 1<br>Area Base | R/W |       | If the comparison of bits 15-12 of a logical address indicates that the address is in Common Area 1, this value (shifted left 12 bits, times 4096) is added to the logical address to form the physical address. |

TABLE 3. BANK BASE REGISTER (0039H) BBR

| Bit                                        | 7 | 6                 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------------------------------------------|---|-------------------|---|---|---|---|---|---|

| Bit/Field                                  |   | Base of Bank Area |   |   |   |   |   |   |

| R/W                                        |   | R/W               |   |   |   |   |   |   |

| Reset                                      | 0 | 0 0 0 0 0 0 0     |   |   |   |   |   |   |

| Note: R = Read W = Write X = Indeterminate |   |                   |   |   |   |   |   |   |

| Bit<br>Position | Bit/Field         | R/W | Value | Description                                                                                                                                                                                                      |

|-----------------|-------------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0             | Bank Area<br>Base | R/W |       | If the comparison of bits 15–12 of a logical address indicates that the address is in the Bank Area, this value (shifted left 12 bits, times 4096) is added to the logical address to form the physical address. |

TABLE 4. COMMON/BANK AREA REGISTER (003AH) CBAR

| Bit                                        | 7               | 6      | 5        | 4     | 3                      | 2 | 1 | 0 |

|--------------------------------------------|-----------------|--------|----------|-------|------------------------|---|---|---|

| Bit/Field                                  | Bank            | /Commo | n 1 Bour | ndary | Common O/Bank Boundary |   |   |   |

| R/W                                        | R/W             |        |          |       | R/W                    |   |   |   |

| Reset                                      | 1 1 1 1 0 0 0 0 |        |          |       |                        |   | 0 |   |

| Note: R = Read W = Write X = Indeterminate |                 |        |          |       |                        |   |   |   |

| Bit<br>Position | Bit/Field                     | R/W | Value | Description                                                                                                  |

|-----------------|-------------------------------|-----|-------|--------------------------------------------------------------------------------------------------------------|

| 7-4             | Bank/<br>Common 1<br>Boundary | R/W |       | If bits 15–12 of a logical address are greater than or equal to this value, the address is in Common Area 1. |

| 3-0             | Common 0/<br>Bank<br>Boundary | R/W |       | If bits 15–12 of a logical address are less than this value, the address is in Common Area 0.                |

**Note:** If bits 3-0 of this reg  $\leq$  bits 15-12 of a logical address < bits 7-4 of this reg, the address is in the Bank Area. Do not program this register so that bits 3-0 > bits 7-4. All comparisons are unsigned.

## **INSTRUCTION SET**

The eZ80 is descended from the ZiLOG Z80. Its 8-bit data bus and 24-bit address space fit well into a wide variety of mid-range embedded processing applications. This processor provides significantly more computing power than a microcontroller, at a fraction of the system cost of a larger microprocessor.

Instructions and features that are new to the eZ80 are denoted by a dagger (†). Instructions that exist in the Z80 but are undocumented, do not exist in the Z8018x family, and are implemented and acknowledged in the eZ80, are denoted by a double dagger (‡).

## **CLASSES OF INSTRUCTIONS**

TABLE 5. LOAD INSTRUCTIONS

| Mnemonic                                              | Operands        | Instruction              |  |  |  |  |

|-------------------------------------------------------|-----------------|--------------------------|--|--|--|--|

| LD                                                    | dst,src         | Load                     |  |  |  |  |

| LEA                                                   | $qq,IX/Y \pm d$ | Load Effective Address † |  |  |  |  |

| PEA                                                   | IX/Y ± d        | Push Effective Address†  |  |  |  |  |

| POP                                                   | dst             | Pop                      |  |  |  |  |

| PUSH src Push                                         |                 |                          |  |  |  |  |

| † Instructions and features that are new to the eZ80. |                 |                          |  |  |  |  |

22 eZ80 PS002200-ZMP0999

TABLE 6. ARITHMETIC INSTRUCTIONS

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| ADC      | dst,src  | Add with Carry                        |

| ADD      | dst,src  | Add                                   |

| СР       | A,src    | Compare                               |

| CPD(R)   |          | Block Scan, decrementing (and Repeat) |

| CPI(R)   |          | Block Scan, incrementing (and Repeat) |

| DAA      |          | Decimal Adjust Accumulator            |

| DEC      | dst      | Decrement                             |

| INC      | dst      | Increment                             |

| MLT      | rr       | Multiply                              |

| NEG      |          | Negate Accumulator                    |

| SBC      | dst,src  | Subtract with Carry                   |

| SUB      | A,src    | Subtract                              |

TABLE 7. LOGICAL INSTRUCTIONS

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| AND      | A,src    | Logical AND            |

| CPL      |          | Complement accumulator |

| OR       | A,src    | Logical OR             |

| TST      | A,src    | Test accumulator       |

| XOR      | A,src    | Logical Exclusive OR   |

TABLE 8. EXCHANGE INSTRUCTIONS

| Mnemonic | Operands | Instruction                        |

|----------|----------|------------------------------------|

| EX       | AF,AF′   | Exchange Accumulator and Flags     |

| EX       | DE,HL    | Exchange DE and HL                 |

| EX       | (SP),rr  | Exchange register and top of stack |

| EXX      |          | Exchange register banks            |

TABLE 9. PROGRAM CONTROL INSTRUCTIONS

| Mnemonic | Operands | Instruction                       |

|----------|----------|-----------------------------------|

| CALL     | cc,dst   | Conditional Call                  |

| CALL     | dst      | Call                              |

| DJNZ     | dst      | Decrement and Jump if Non-Zero    |

| JP       | cc,dst   | Conditional Jump                  |

| JP       | dst      | Jump                              |

| JR       | cc',dst  | Conditional Jump Relative         |

| JR       | dst      | Jump Relative                     |

| RET      | CC       | Conditional Return                |

| RET      |          | Return                            |

| RETI     |          | Return from Interrupt             |

| RETN     |          | Return from Nonmaskable interrupt |

| RST      | dst      | Restart                           |

TABLE 10. BIT MANIPULATION INSTRUCTIONS

| Mnemonic | Operands | Instruction |

|----------|----------|-------------|

| BIT      | n,src    | Bit test    |

| RES      | n,dst    | Reset bit   |

| SET      | n,dst    | Set bit     |

TABLE 11. BLOCK TRANSFER INSTRUCTIONS

| Mnemonic | Operands | perands Instruction                   |  |

|----------|----------|---------------------------------------|--|

| LDD(R)   |          | Block Move, decrementing (and Repeat) |  |

| LDI(R)   |          | Block Move, incrementing (and Repeat) |  |

TABLE 12. ROTATE AND SHIFT INSTRUCTIONS

| Mnemonic | Operands | Instruction                       |

|----------|----------|-----------------------------------|

| RL       | dst      | Rotate Left                       |

| RLA      |          | Rotate Left Accumulator           |

| RLC      | dst      | Rotate Left Circular              |

| RLCA     |          | Rotate Left Circular Accumulator  |

| RLD      |          | Rotate Left Decimal               |

| RR       | dst      | Rotate Right                      |

| RRA      |          | Rotate Right Accumulator          |

| RRC      | dst      | Rotate Right Circular             |

| RRCA     |          | Rotate Right Circular Accumulator |

| RRD      |          | Rotate Right Decimal              |

| SLA      | dst      | Shift Left                        |

| SRA      | dst      | Shift Right Arithmetic            |

| SRL      | dst      | Shift Right Logical               |

TABLE 13. INPUT/OUTPUT INSTRUCTIONS

| Mnemonic         | Operands    | Instruction                                       |

|------------------|-------------|---------------------------------------------------|

| IN               | A, (n)      | Input to A from port n                            |

| IN               | r, (C)      | Input to register from port in BC                 |

| INO              | r, (n)      | Input to r from port n in page 0                  |

| IND(R)           |             | Block Input, decrement HL (and Repeat)            |

| IND2(R)          |             | Block Input, decrement both (and Repeat)†         |

| INDM(R)          |             | Block Input, page 0, decrement both (and Repeat)† |

| INI(R)           |             | Block Input, increment HL (and Repeat)            |

| INI2(R)          |             | Block Input, decrement both (and Repeat)†         |

| INIM(R)          |             | Block Input, page 0, increment both (and Repeat)† |

| OTDM(R)          |             | Block Output, page 0, decrement both (and Repeat) |

| OTIM(R)          |             | Block Output, page 0, increment both (and Repeat) |

| OUT              | (n), A      | Output from A to port n                           |

| OUT              | (C), r      | Output from register to port in BC                |

| OUT0             | (n), r      | Output from register to port n in page 0          |

| OUTD (OTDR)      |             | Block Output, decrement HL (and Repeat)           |

| OUTD2 Block      |             | Block Output, decrement both (and Repeat)†        |

| (OTD2R)          |             |                                                   |

| OUTI (OTIR)      |             | Block Output, increment HL (and Repeat)           |

| OUTI2 (OTI2R)    |             | Block Output. decrement both (and Repeat)†        |

| TSTIO            | n           | Test port (0,C) under mask                        |

| † Instructions a | nd features | that are new to the eZ80.                         |

TABLE 14. PROCESSOR CONTROL INSTRUCTIONS

| Mnemonic                                              | Operands | Instruction           |

|-------------------------------------------------------|----------|-----------------------|

| CCF                                                   |          | Complement Carry Flag |

| DI                                                    |          | Disable Interrupts    |

| EI                                                    |          | Enable Interrupts     |

| HALT                                                  |          | Halt                  |

| IM                                                    | 0/1/2    | Interrupt Mode        |

| NOP                                                   |          | No Operation          |

| RSMIX                                                 |          | Reset Mix Flag†       |

| SCF                                                   |          | Set Carry Flag        |

| SLP                                                   |          | Sleep                 |

| STMIX                                                 |          | Set Mix Flag†         |

| † Instructions and features that are new to the eZ80. |          |                       |

# **PROCESSOR FLAGS**

Table 15 shows the Flag register. Bits in this register are set and cleared by certain instructions as described in the eZ80 User Manual. Some of the Flags are tested by conditional JR, JP, CALL, and RET instructions, and some are used by subsequent instructions such as ADC, SBC, and DAA. The Flags can also be pushed and popped with accumulator A.

TABLE 15. FLAG REGISTER

| Bit                     | 7 | 6 | 5 | 4  | 3 | 2   | 1 | 0  |

|-------------------------|---|---|---|----|---|-----|---|----|

| Name                    | S | Z | х | HC | х | P/V | N | CF |

| Reset                   | 0 | 0 | х | 0  | х | 0   | 0 | 0  |

| Note: X = Indeterminate |   |   |   |    |   |     |   |    |

| Bit/<br>Field | Bit<br>Position | Description             |

|---------------|-----------------|-------------------------|

| S             | 7               | Sign Flag               |

| Z             | 6               | Zero Flag               |

|               | 5               | reserved                |

| HC            | 4               | Half-carry Flag         |

|               | 3               | reserved                |

| P/V           | 2               | Parity or Overflow Flag |

| N             | 1               | Add/Subtract Flag       |

| CF            | 0               | Carry Flag              |

CONDITION CODES INSTRUCTION SET

## **CONDITION CODES**

Table 16 shows the codes used in the *Flags Affected* columns of the Instruction Summary Table, Table 19, to indicate how each flag is affected by each type of instruction.

TABLE 16. FLAG SETTINGS DEFINITIONS

| Symbol | Definition                                              |

|--------|---------------------------------------------------------|

| 0      | Cleared to 0                                            |

| 1      | Set to 1                                                |

| *      | Set or cleared according to the result of the operation |

| _      | Unaffected                                              |

| X      | Undefined                                               |

| V      | Set if Overflow or Underflow                            |

| P      | Set if Parity or result is Even                         |

| NZ     | Set if the count in B or BC is non-zero                 |

Table 17 shows the condition codes that can be used in conditional JP, CALL, and RET instructions in assembly language. A subset of these codes can also be used in JR instructions, which are shorter and faster than JPs.

TABLE 17. CONDITION CODES

| Mnemonic | Definition       | Flag Settings | Valid in JR? |

|----------|------------------|---------------|--------------|

| С        | Carry            | CF = 1        | Υ            |

| NC       | No Carry         | CF = 0        | Y            |

| Z        | Zero             | Z = 1         | Y            |

| NZ       | Non-Zero         | Z = 0         | Y            |

| М        | Minus            | S = 1         | N            |

| Р        | Positive or zero | S = 0         | N            |

| PE       | Parity Even      | P/V = 1       | N            |

| PO       | Parity Odd       | P/V = 0       | N            |

| V        | Overflow         | P/V = 1       | N            |

| NV       | No Overflow      | P/V = 0       | N            |

# **ASSEMBLY LANGUAGE SYNTAX**

For two-operand instructions, Z80 assembly language syntax puts the destination operand before the source operand.

**EXAMPLE:** LD A, (1234) is a Load instruction, while LD (1234), A is a Store instruction.

Instruction Set Notation

Past Z80 assemblers allowed the destination operand to be omitted (implicit) if the Op Code mnemonic only allowed one destination operand, for example, AND L instead of AND A, L. Use of these short forms is discouraged because it is a cause of possible error (the programmer mistakes the implicit destination). But for legacy code, all known Z80 assemblers still accept the short form.

**Note:** The assembly language uses C ambiguously, to designate one of the 8-bit registers as well as a condition code to test the Carry flag. This processor description uses CF to designate the Carry flag, and HC to designate the Half-Carry flag (as opposed to the 8-bit register H)

## **NOTATION**

Table 18 describes other notation used in the Instruction Summary table.

TABLE 18. SYMBOLS

| Symbol                        | Definition                                                                                                                                                     |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (aa)                          | (mn), $(IX \pm d)$ , $(IY \pm d)$ , $(BC)$ , $(DE)$ , or $(HL)$ .                                                                                              |

| (BC), (DE),<br>(HL)           | The 8-bit contents of memory, at the address pointed to by a register pair. (HL) can also indicate a 16-bit value in memory.†                                  |

| $(IX \pm d),$<br>$(IY \pm d)$ | The 8- or 16†-bit content of memory at the address formed<br>by adding the contents of the index register and the signed<br>displacement d in the instruction. |

| (mn)                          | The 8-bit content of memory at the direct address mn                                                                                                           |

| (SP)                          | The 16-bit contents of memory at the address pointed to by SP, and the next higher address.                                                                    |

| ±d                            | Since d is signed, it would be more correct to just write $\pm$ instead. But we write $\pm$ to emphasize that d is signed.                                     |

| AF                            | A concatenated with F, with A as the more significant byte                                                                                                     |

| b                             | A bit number 0-7                                                                                                                                               |

| СС                            | A condition code C, NC, Z, NZ, S, M, PE, PV, V, or NV                                                                                                          |

| cc'                           | A condition code C, NC, Z, or NZ                                                                                                                               |

| d                             | An 8-bit signed displacement -128 to +127                                                                                                                      |

| ee                            | A 16-bit register BC, DE, HL, SP, IX, or IY                                                                                                                    |

| IEF1,2                        | The processor's two Interrupt Enable Flags.                                                                                                                    |

| ih                            | IXH or IYH‡                                                                                                                                                    |

| il                            | IYH or IYL‡                                                                                                                                                    |

| ir                            | IXH, IXL, IYH, or IYL‡                                                                                                                                         |

| m                             | An 8-bit variable A, B, C, D, E, H, L, (HL), (IX $\pm$ d), or (IY $\pm$ d)                                                                                     |

| mn                            | A 16-bit immediate data value or direct address                                                                                                                |

| n                             | A 8-bit immediate value or port number, 0-255 or 0-FFH                                                                                                         |

| op1-op2                       | A range of Op Code values, that includes some of the values between the low and high values. See the Note.                                                     |

| PC                            | Program Counter                                                                                                                                                |

| рр                            | A 16-bit register BC, DE, HL, SP, IX, IY, or AF                                                                                                                |

|                               | s and features that are new to the eZ80.<br>s that exist in the Z80 but are undocumented.                                                                      |

TABLE 18. SYMBOLS

| Symbol                            | Definition                                                                                                                                         |  |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| q                                 | A, B, C, D, E, H, L, IXH $\ddagger$ , IXL $\ddagger$ , IYH $\ddagger$ , IYL $\ddagger$ , (HL), (IX $\pm$ d), or (IY $\pm$ d)                       |  |  |  |  |  |  |

| qq                                | A 16-bit register BC, DE, HL, IX, or IY†                                                                                                           |  |  |  |  |  |  |

| r, r'                             | An 8-bit register A, B, C, D, E, H, or L.                                                                                                          |  |  |  |  |  |  |

| rae                               | An 8-bit register A, B, C, D, or E                                                                                                                 |  |  |  |  |  |  |

| rr                                | A 16-bit register HL, IX, or IY.                                                                                                                   |  |  |  |  |  |  |

| s                                 | A, B, C, D, E, H, L, IXH $\ddagger$ , IXH $\ddagger$ , IYH $\ddagger$ , IYL $\ddagger$ , n, (HL), (IX $\pm$ d), or (IY $\pm$ d)                    |  |  |  |  |  |  |

| SP                                | Stack Pointer                                                                                                                                      |  |  |  |  |  |  |

| SS                                | A 16-bit register BC, DE, HL, or SP                                                                                                                |  |  |  |  |  |  |

| ss <sub>H</sub> , ss <sub>L</sub> | The more- and less-significant eight bits of a register pair                                                                                       |  |  |  |  |  |  |

| tt                                | A 16-bit register like ss, except that the value that designates HL in the ss encoding, here means same as the destination register HL, IX, or IY. |  |  |  |  |  |  |

| † Instructions                    | † Instructions and features that are new to the eZ80.                                                                                              |  |  |  |  |  |  |

| ‡ Instructions                    | that exist in the Z80 but are undocumented.                                                                                                        |  |  |  |  |  |  |

**Note:** The symbol – between Op Codes (op1–op2), in the Op Codes column of the Instruction Summary table, indicates all the binary values between the indicated lower and upper limits inclusive, that can be formed by incrementing the set of bits that differ between the lower and upper value.

EXAMPLE: 00–C0 represents 00, 40, 80, and C0, while 40–BF represents all the values in that range.

## **INSTRUCTION SUMMARY**

The following table describes each type or class of instruction, using the notation described in the preceding sections. In cases where the same location acts as both Destination (Dest) and Source code, is centered between the Dest and Source columns (for example, the DEC instruction). The table is sorted by the assembly language mnemonics.

TABLE 19. INSTRUCTION SUMMARY

|                                  | Addre | ss Mode        | Op Code(s)<br>(Hex) | Flags Affected |   |    |     |   |    |  |  |

|----------------------------------|-------|----------------|---------------------|----------------|---|----|-----|---|----|--|--|

| Instruction and Operation        | Dest  | Source         |                     | S              | Z | нс | P/V | N | CF |  |  |