## EMP-B50P12

## Programmable Isolated IPM

## PI-IPM<sup>TM</sup> Features:

### ■ Power Module:

- NPT IGBTs 50A, 1200V

- 10us Short Circuit capability

- Square RBSOA

- Low Vce<sub>(on)</sub> (2.15Vtyp @ 50A, 25°C)

- Positive Vce<sub>(on)</sub> temperature coefficient

- Gen III HexFred Technology

- Low diode V<sub>F</sub> (1.78Vtyp @ 50A, 25°C)

- Soft reverse recovery

- $2m\Omega$  sensing resistors on all phase outputs

- T/C < 50ppm/°C</li>

### Embedded driving board

- Programmable 40 Mips DSP

- Current sensing feedback from all phases

- Full protection from ground and line to line faults

- UVLO, OVLO on DCbus voltage

- Embedded flyback smps for floating stages (single 15Vdc @ 300mA input required)

- Asynchronous isolated 2Mbps serial port for DSP communication and programming

- IEEE standard 1149.1 (JTAG port interface) for program downloading and debugging

- Separated turn on / turn off outputs for IGBTs di/dt control

- Isolated serial port input with strobe signal for quadrature encoders

## Description

The EMP-B50P12 is a fully integrated Intelligent Power Module for high performances Servo Motor Driver applications.

The device core is a state of the art DSP, the TMS320LF2406A\* at 40 Mips, interfaced with a full set of peripheral designed to handle all analog feedback and control signals needed to correctly manage the power section of the device.

The PI-IPM<sup>TM</sup> has been designed and tailored to implement internally all functions needed to close the current loop of a high performances servo motor driver, a basic software is already installed in the DSP and the JTAG connector allows the user to easily develop and download its own proprietary algorithm.

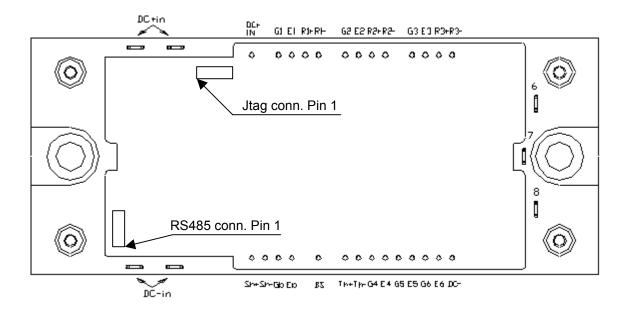

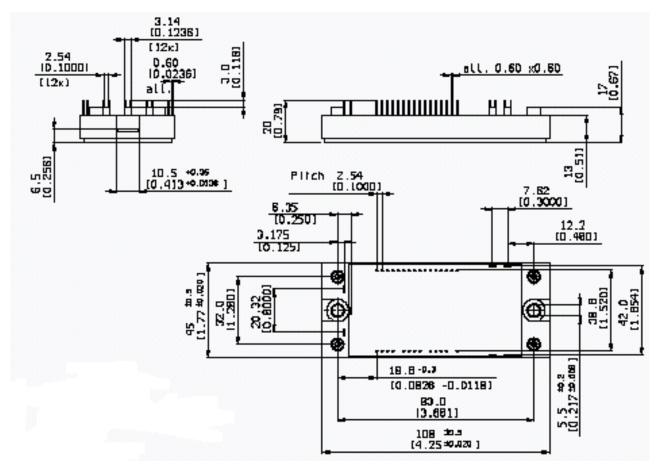

The device comes in the EMP<sup>TM</sup> package, fully compatible in length, width and height with the popular EconoPack 2 outline.

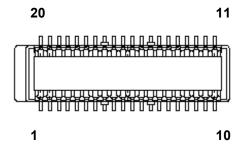

### Package:

$(EMP^{TM} - Inverter)$ (EconoPack 2 outline compatible)

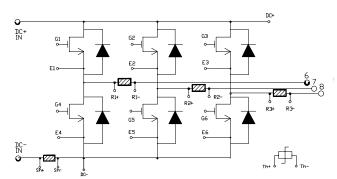

### **Power Module schematic:**

Three phase inverter with current sensing resistors on all output phases

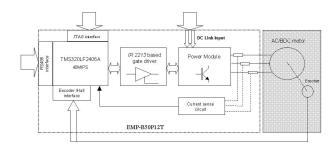

### **Control Board Block Schematic:**

\* First samples come with the TMS320LF2406 at 30Mips, please refer to TI datasheet for further information about performances.

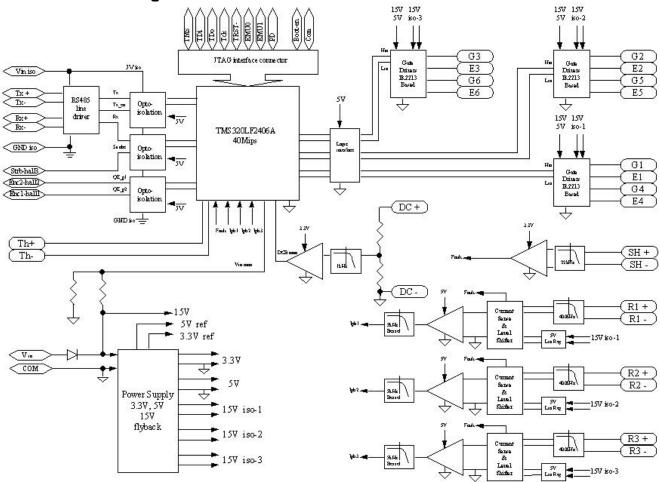

## **Detailed Block Diagram**

Signal pins on RS485 serial port

| Symbol       | Lead Description                                                                       | Pin nu | ımber  |

|--------------|----------------------------------------------------------------------------------------|--------|--------|

| Vin iso      | External 5V supply voltage for opto-couplers and line driver supply                    | 6      |        |

| GND iso      | Extenal 5V supply ground reference for opto-couplers and line driver supply            | 7      |        |

| Tx+          | RS485 Trasmitter Non inverting Driver Output                                           | 1      |        |

| Tx-          | RS485 Trasmitter Inverting Driver Output                                               | 2      |        |

| Rx+          | RS485 Receiver Non inverting Driver Input                                              |        | RS485  |

| Rx-          | RS485 Receiver Inverting Driver Input                                                  |        | serial |

| Enc1 – Hall1 | Incremental Encoder Input 1 / Position hall effect sensor input 1 (GND iso referenced) |        | port   |

| Enc2 – Hall2 | Incremental Encoder Input 2 / Position hall effect sensor input 2 (GND iso referenced) |        |        |

| Strb – Hall3 | Incremental Encoder Strobe Input / Position hall effect sensor input 3 (GND iso ref)   |        |        |

| Vin          | External 15V supply voltage. Internally referred to DC bus minus pin (DC -)            | 17-18  |        |

| СОМ          | External 15V supply ground reference. This pin is directly connected to DC -           | 19-20  |        |

Signal pins on IEEE1149.1 JTAG connector

| Symbol  | Lead Description                                                                                                                           |        | Pir  | number     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------------|

| TMS     | JTAG test mode select                                                                                                                      | Input  | 12   |            |

| TDI     | JTAG test data input                                                                                                                       | Input  | 14   |            |

| TDO     | JTAG test data output                                                                                                                      | Output | 13   |            |

|         | JTAG test clock. TCK is a 10MHz clock source from the emulation pod. This                                                                  |        | 15   |            |

| TCK     | signal can be used to drive the system test clock.                                                                                         | Input  |      |            |

| TRST-   | JTAG test reset                                                                                                                            | Input  | 11   |            |

| EMU0    | Emulation pin 0                                                                                                                            | I/O    | 9-10 |            |

| EMU1    | Emulation pin 1                                                                                                                            | I/O    | 7-8  | IEEE1149.1 |

|         | Presence detect.                                                                                                                           |        | 1    | JTAG       |

|         | Indicates that the emulation cable is connected and that the PI-IPM logic is                                                               |        |      |            |

| PD      | powered up. PD is tied to the DSP 3.3V supply through a 1k resistor.                                                                       | Output |      |            |

|         | JTAG test clock return. Test clock input to the emulator.                                                                                  |        | 16   |            |

| TCK_RET | Internally short circuited to TCK.                                                                                                         | Output |      |            |

| Boot-En | Boot ROM enable. This pin is sampled during DSP reset, pulling it low enables DSP boot ROM (Only in Flash versions). 47k internal pull up. | Input  | 17   |            |

| COM     | External 15V supply ground reference. This pin is directly connected to DC -                                                               | N/A    | 20   |            |

Following pins are intended for signal communication between driving board and power module only, though here described for completeness, they are on purpose not available to the user.

| DC +     | DC Bus plus input signal                                                                  |                                |  |  |  |

|----------|-------------------------------------------------------------------------------------------|--------------------------------|--|--|--|

| DC -     | DC Bus minus input signal (internally connected to COM)                                   |                                |  |  |  |

| Th+      | Thermal sensor positive input                                                             |                                |  |  |  |

| Th -     | Thermal sensor negative input (internally connected to COM)                               |                                |  |  |  |

| Sh +     | DC Bus minus series shunt positive input (Kelvin point)                                   |                                |  |  |  |

| Sh -     | DC Bus minus series shunt negative input (internally connected to COM, Kelvin point)      | Lateral connectors on embedded |  |  |  |

| G1/2/3   | Gate connections for high side IGRTs                                                      |                                |  |  |  |

| E1/2/3   | Emitter connections for high side IGBTs (Kelvin points)  driving board                    |                                |  |  |  |

| R1/2/3 + | Output current sensing resistor positive input (IGBTs emitters 1/2/3 side, Kelvin points) |                                |  |  |  |

| R1/2/3 - | Output current sensing resistor negative input (Motor side, Kelvin points)                |                                |  |  |  |

| G4/5/6   | Gate connections for low side IGBTs                                                       |                                |  |  |  |

| E4/5/6   | Emitter connections for low side IGBTs (Kelvin points)                                    |                                |  |  |  |

## Absolute Maximum Ratings (T<sub>C</sub>=25°C)

Absolute Maximum Ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to  $V_{DC}$ , all currents are defined positive into any lead. Thermal Resistance and Power Dissipation ratings are measured at still air conditions.

|                       | Symbol                                                                 | Parameter Definition                                        | Min.  | Max.  | Units |

|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------|-------|-------|-------|

|                       | V <sub>DC</sub>                                                        | DC Bus Voltage                                              | 0     | 1000  | V     |

|                       | V <sub>CES</sub>                                                       | Collector Emitter Voltage                                   | 0     | 1200  | V     |

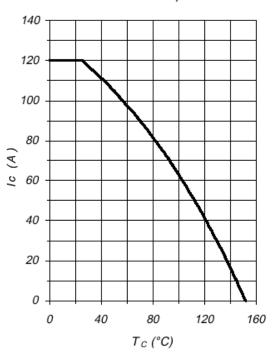

|                       | Ic @ 100C IGBTs continuous collector current (T <sub>C</sub> = 100 °C) |                                                             |       | 50    |       |

|                       | Ic @ 25C                                                               | IGBTs continuous collector current                          |       | 100   |       |

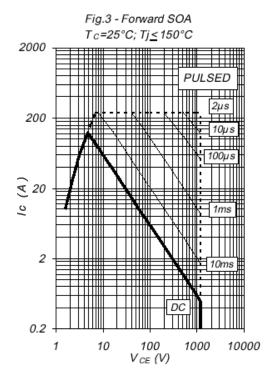

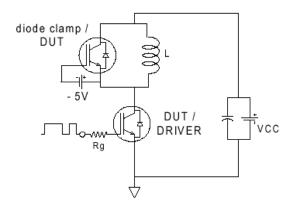

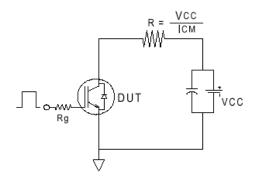

| Inverter              | Ісм                                                                    | Pulsed Collector Current (Fig.3, Fig. CT.5)                 |       | 200   | Α     |

| iliverter             | lF                                                                     | Diode Continuous Forward Current (T <sub>C</sub> = 100 °C)  |       | 50    |       |

|                       | I <sub>FM</sub>                                                        | Diode Maximum Forward Current                               |       | 200   |       |

|                       | V <sub>GE</sub>                                                        | Gate to Emitter Voltage                                     | -20   | +20   | V     |

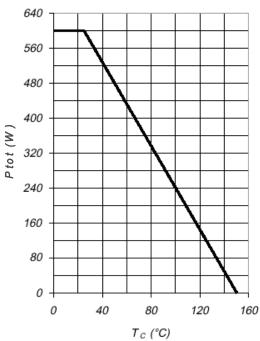

| P <sub>D @ 25°C</sub> |                                                                        | Power Dissipation (One transistor)                          |       | 600   | W     |

|                       | P <sub>D @ 100°C</sub>                                                 | Power Dissipation (One transistor, T <sub>C</sub> = 100 °C) |       | 250   | VV    |

|                       | V <sub>in</sub>                                                        | Non isolated supply voltage (DC- referenced)                | -20   | 20    |       |

| Driving<br>Board      | V <sub>in-iso</sub>                                                    | Isolated supply voltage (GND iso referenced)                | 0     | 5.5   | V     |

|                       | Rx                                                                     | RS485 Receiver input voltage (GND iso referenced)           | - 7   | 12    |       |

| _                     | MT Mounting Torque                                                     |                                                             |       | 3.5   | Nm    |

| Power<br>Module       | TJ                                                                     | Operating Junction Temperature                              | -40   | +150  | °C    |

|                       | T <sub>STG</sub>                                                       | Storage Temperature Range                                   | -40   | +150  |       |

|                       | Vc-iso                                                                 | Isolation Voltage to Base Copper Plate                      | -2500 | +2500 | V     |

### **Electrical Characteristics: Inverter**

For proper operation the device should be used within the recommended conditions.

### $T_J = 25$ °C (unless otherwise specified)

| Symbol                        | Parameter Definition                    | Min. | Тур. | Max. | Units | Test Conditions                                                        | Fig.  |

|-------------------------------|-----------------------------------------|------|------|------|-------|------------------------------------------------------------------------|-------|

| V <sub>(BR)CES</sub>          | Collector To Emitter Breakdown Voltage  | 1200 |      |      | V     | V <sub>GE</sub> = 0V, I <sub>C</sub> = 250μA                           | _     |

| $\Delta V_{(BR)CES}$ /        | Temperature Coeff. of Breakdown Voltage |      | +1.2 |      | V/°C  | V <sub>GE</sub> = 0V, I <sub>C</sub> = 1mA (25 - 125 °C)               |       |

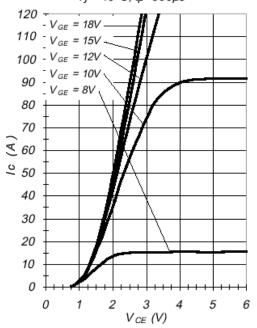

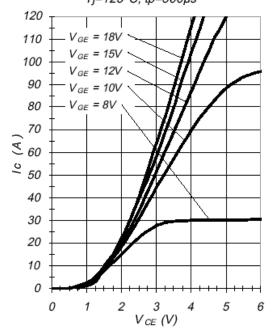

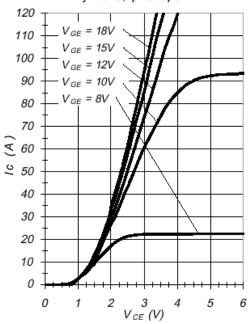

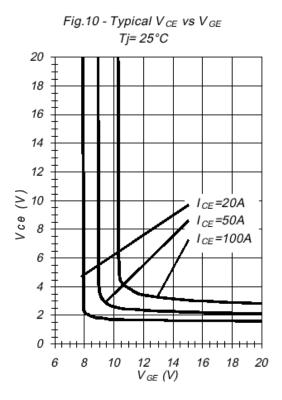

|                               |                                         |      | 2.15 | 2.34 |       | Ic = 50A, V <sub>GE</sub> = 15V                                        | 5, 6  |

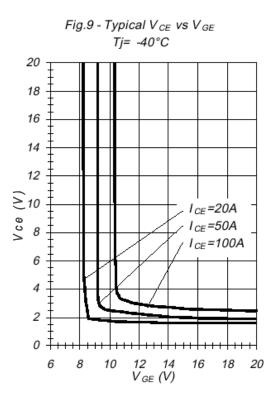

| V <sub>CE(on)</sub>           | Collector To Emitter Saturation Voltage |      | 3.24 | 3.78 | V     | I <sub>C</sub> = 100A, V <sub>GE</sub> = 15V                           | 7,9   |

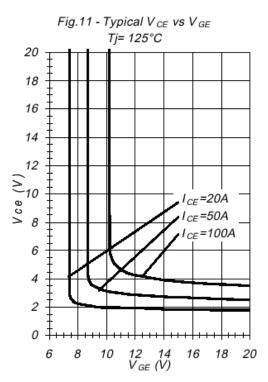

|                               |                                         |      | 2.6V | 3.0  |       | Ic = 50A, V <sub>GE</sub> = 15V, T <sub>J</sub> = 125 °C               | 10,11 |

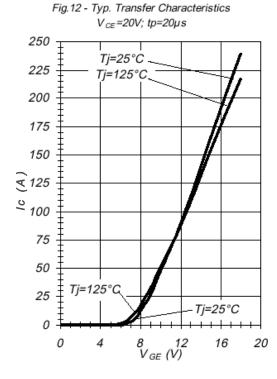

| V <sub>GE(th)</sub>           | Gate Threshold Voltage                  | 4.4  | 4.7  | 5.5  | V     | $V_{CE} = V_{GE}, I_C = 250 \mu A$                                     | 9,10  |

| $\Delta V_{GE(th)/\Delta Tj}$ | Temp. Coeff. of Threshold Voltage       |      | -1.2 |      | mV/°C | V <sub>CE</sub> = V <sub>GE</sub> , I <sub>C</sub> = 1mA (25 - 125 °C) | 11,12 |

| g <sub>fe</sub>               | Forward Trasconductance                 | 29   | 33   | 38   | S     | V <sub>CE</sub> = 50V, I <sub>C</sub> = 50A, PW = 80μs                 |       |

|                               |                                         |      |      | 500  |       | V <sub>GE</sub> = 0V, V <sub>CE</sub> = 1200V                          |       |

| I <sub>CES</sub>              | Zero Gate Voltage Collector Current     |      | 650  | 1350 | μΑ    | V <sub>GE</sub> = 0V, V <sub>CE</sub> = 1200V, T <sub>J</sub> = 125 °C |       |

|                               |                                         |      |      | 4000 |       | V <sub>GE</sub> = 0V, V <sub>CE</sub> = 1200V, T <sub>J</sub> = 150 °C |       |

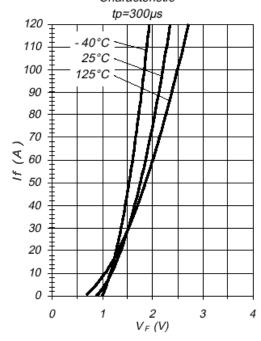

| M                             | Diada Fassiand Valtana Duan             |      | 1.78 | 2.1  | V     | I <sub>C</sub> = 50A                                                   | 8     |

| V <sub>FM</sub>               | Diode Forward Voltage Drop              |      | 1.90 | 2.22 | V     | I <sub>C</sub> = 50A, T <sub>J</sub> = 125 °C                          | 8     |

| I <sub>RM</sub>               | Diode Reverse Leakage Current           |      |      | 20   | μΑ    | V <sub>R</sub> = 1200V, T <sub>J</sub> = 25 °C                         |       |

| I <sub>GES</sub>              | Gate To Emitter Leakage Current         |      |      | ±200 | nA    | V <sub>GE</sub> = 20V                                                  |       |

## Electrical Characteristics: Inverter (continued)

| R1/2/3 | Sensing Resistors                  | 1.9  | 2 | 2.1  | mΩ    |  |

|--------|------------------------------------|------|---|------|-------|--|

| Rsh    | DC bus minus series shunt resistor | 4.75 | 5 | 5.25 | 11152 |  |

## Switching Characteristics: Inverter

For proper operation the device should be used within the recommended conditions.  $T_J = 25^{\circ}C$  (unless otherwise specified)

| Symbol               | Parameter Definition                          | Min | Тур        | Max  | Units | Test Conditions                                                                                          | Fig.           |  |

|----------------------|-----------------------------------------------|-----|------------|------|-------|----------------------------------------------------------------------------------------------------------|----------------|--|

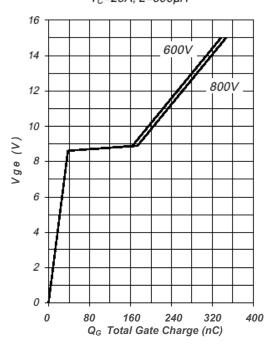

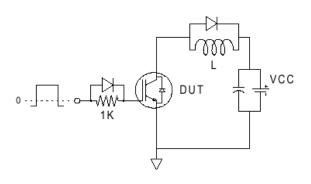

| Qg                   | Total Gate Charge (turn on)                   |     | 338        | 508  |       | I <sub>C</sub> = 50A                                                                                     | 22             |  |

| Qge                  | Gate – Emitter Charge (turn on)               |     | 38         | 58   | nC    | V <sub>DC</sub> = 600V                                                                                   | 23             |  |

| Q <sub>gc</sub>      | Gate - Collector Charge (turn on)             |     | 164        | 246  |       | V <sub>GE</sub> = 15V                                                                                    | CT1            |  |

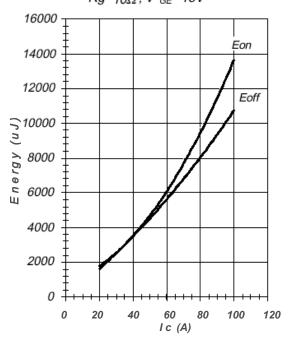

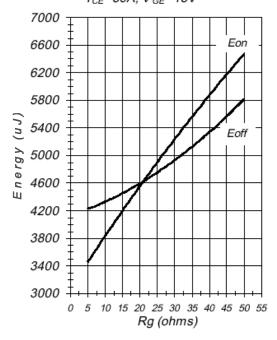

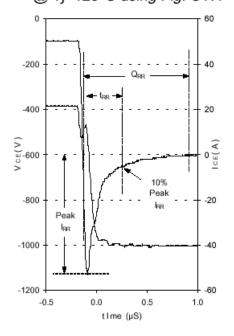

| Eon                  | Turn on Switching Loss                        |     | 2345       | 2750 |       | I <sub>C</sub> = 50A, V <sub>DC</sub> = 600V, T <sub>J</sub> = 25 °C                                     | CT1            |  |

| E <sub>off</sub>     | Turn off Switching Loss                       |     | 3284       | 3960 | μJ    | $V_{GE}$ = 15V, $R_{G}$ =10 $\Omega$ , L = 200 $\mu$ H                                                   | WF1            |  |

| E <sub>tot</sub>     | Total Switching Loss                          |     | 5630       | 6710 |       | Tail and Diode Rev. Recovery included                                                                    | WF2            |  |

| E <sub>on</sub>      | Turn on Switching Loss                        |     | 3652       | 4083 |       | I <sub>C</sub> = 50A, V <sub>DC</sub> = 600V, T <sub>J</sub> = 125 °C                                    | 13,            |  |

| E <sub>off</sub>     | Turn off Switching Loss                       |     | 4660       | 5676 | μJ    | $V_{GE}$ = 15V, $R_{G}$ =10 $\Omega$ , L = 200 $\mu$ H                                                   | 15<br>CT1      |  |

| E <sub>tot</sub>     | Total Switching Loss                          |     | 8312       | 9759 |       | Tail and Diode Rev. Recovery included                                                                    | WF1<br>WF2     |  |

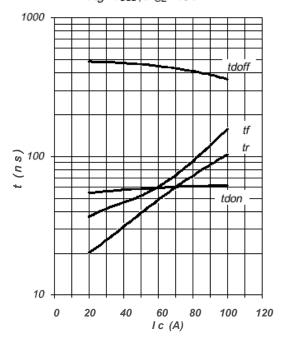

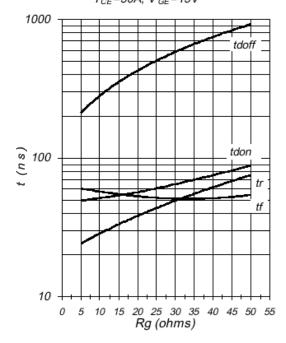

| td (on)              | Turn on delay time                            |     | 50         | 65   |       | 1 504 V 000V T 405 00                                                                                    | 14,16          |  |

| tr                   | Rise time                                     |     | 50         | 70   | ns    | $I_C = 50A$ , $V_{DC} = 600V$ , $T_J = 125$ °C                                                           | CT1            |  |

| td (off)             | Turn off delay time                           |     | 300        | 400  |       | V = 45V D =400 L = 200 H                                                                                 | WF1            |  |

| tf                   | Fall time                                     |     | 30         | 45   |       | $V_{GE}$ = 15V, $R_{G}$ =10Ω, $L$ = 200 $\mu$ H                                                          | WF2            |  |

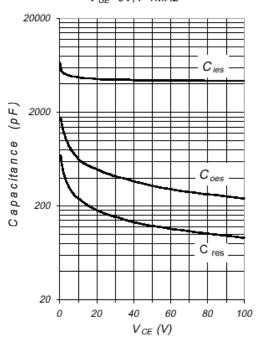

| Cies                 | Input Capacitance                             |     | 4400       |      |       | V <sub>DC</sub> = 30V                                                                                    |                |  |

| Coes                 | Output Capacitance                            |     | 420        |      | pF    | V <sub>GE</sub> = 0V                                                                                     | 22             |  |

| C <sub>res</sub>     | Reverse Transfer Capacitance                  |     | 170        |      |       | f = 1MHz                                                                                                 |                |  |

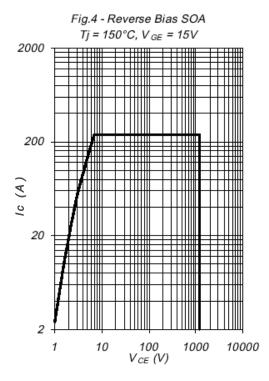

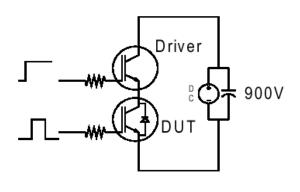

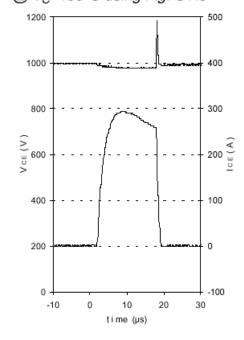

| RBSOA                | Reverse Bias Safe Operating Area              | F   | FULL SQUAF | RE   |       | $T_J$ = 150 °C, $I_C$ =250A, $V_{GE}$ = 15V to 0V<br>$V_{CC}$ = 1000V, $V_p$ = 1200V, $R_G$ = 5 $\Omega$ | 4<br>CT2       |  |

| SCSOA                | Short Circuit Safe Operating Area             | 10  |            |      | μs    | $T_J$ = 150 °C, $V_{GE}$ = 15V to 0V $V_{CC}$ = 900V, $V_{P}$ = 1200V, $R_G$ = 5 $\Omega$                | CT3<br>WF4     |  |

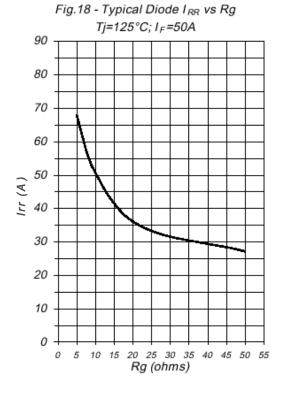

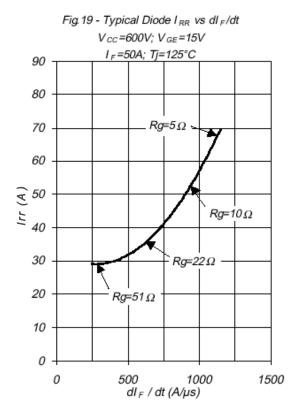

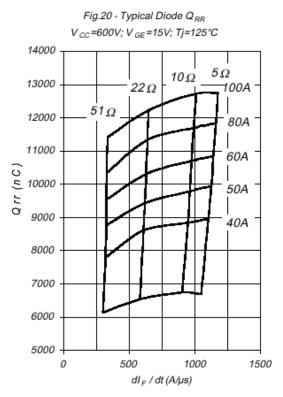

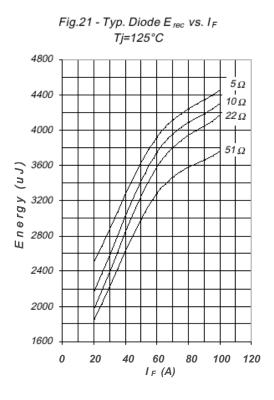

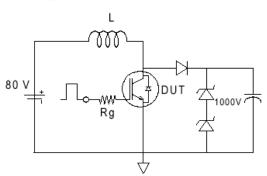

| Erec                 | Diode reverse recovery energy                 |     | 3200       | 4300 | μJ    | T <sub>J</sub> = 125 °C                                                                                  | 17,18<br>19,20 |  |

| trr                  | Diode reverse recovery time                   |     | 150        |      | ns    | $I_C = 50A$ , $V_{DC} = 600V$ ,                                                                          | 21             |  |

| Irr                  | Peak reverse recovery current                 |     | 56         | 72   | Α     | $V_{GE}$ = 15V, $R_{G}$ =10 $\Omega$ , L = 200 $\mu$ H                                                   | CT4<br>WF3     |  |

| Rth <sub>J-C_T</sub> | Each IGBT to copper plate thermal resistance  |     |            | 0.35 | °C/W  |                                                                                                          |                |  |

| $Rth_{J-C\_D}$       | Each Diode to copper plate thermal resistance |     |            | 0.60 | °C/W  |                                                                                                          |                |  |

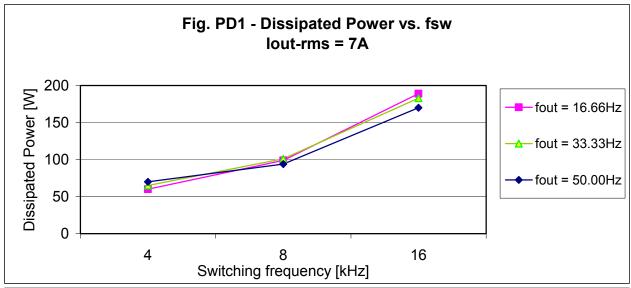

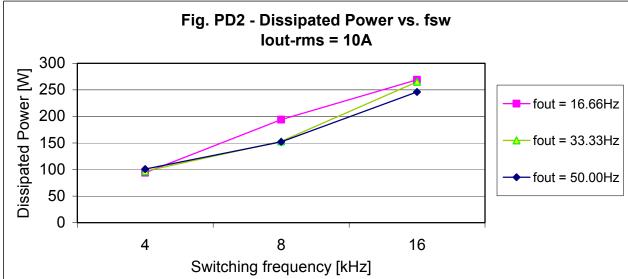

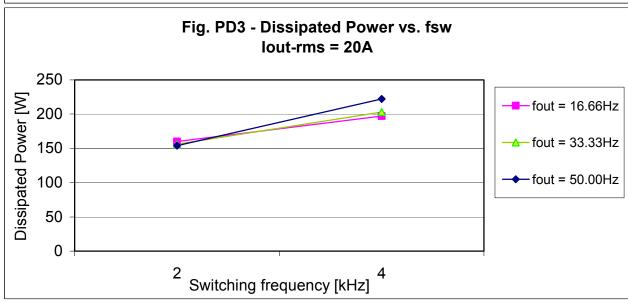

|                      |                                               |     | 65         |      |       | $I_C = 7A$ , $V_{DC} = 515V$ , fsw = 4kHz                                                                | PD1            |  |

| Pdiss                | Total Dissipated Power                        |     | 180        |      | W     | I <sub>C</sub> = 7A, V <sub>DC</sub> = 515V, fsw = 16kHz                                                 | <u> </u>       |  |

|                      |                                               |     | 155        |      |       | $I_C = 20A$ , $V_{DC} = 515V$ , fsw = 2kHz                                                               | PD3            |  |

|                      |                                               |     | 210        |      | 1     | $I_C = 20A$ , $V_{DC} = 515V$ , fsw = 4kHz                                                               |                |  |

## Electrical Characteristics: Embedded Driving Board (EDB) communication ports

For proper operation the device should be used within the recommended conditions.

Vin = 15V, Vin-iso = 5V,  $T_C = T_{MIN}$  to  $T_{MAX}$  (unless otherwise specified)

| Symbol                             | Parameter Definition                          | Min.     | Тур.                                                                                                     | Max.  | Units | Test Conditions                                                                                   | Conn.         |

|------------------------------------|-----------------------------------------------|----------|----------------------------------------------------------------------------------------------------------|-------|-------|---------------------------------------------------------------------------------------------------|---------------|

| Vin                                | EDB Input supply Voltage                      | 12       | 15                                                                                                       | 18    | ٧     |                                                                                                   |               |

| Isupp                              | EDB Input Supply Current                      | 180      |                                                                                                          | 250   | mA    | V <sub>DC</sub> = 600V, f <sub>PWM</sub> = 16kHz                                                  |               |

| Vin iso                            | EDB isolated supply voltage                   | 4.5      | 5                                                                                                        | 5.5   | V     |                                                                                                   | RS485         |

| lq. iso                            | EDB isolated quiescent supply current         |          | 9                                                                                                        | 15    | mA    | Rx+ =Vin iso, Rx- =GND iso<br>Hall1/2/3 = open,<br>Tx enabled by DSP                              | port          |

| Isupp. iso                         | EDB isolated supply current                   | 30       | 40                                                                                                       | 50    | mA    | Hall1/2/3 low, Tx enabled.<br>Rx+ =GND iso, Rx- =Vin iso                                          |               |

| V <sub>DO-TX</sub>                 | Differential Driver Output Voltage            | 2        |                                                                                                          |       | ٧     | Rload = 120 Ω                                                                                     |               |

| V <sub>CO-ТХ</sub>                 | Driver Common mode output voltage             |          |                                                                                                          | 3     | ٧     | Rioad = 120 \$2                                                                                   |               |

| V <sub>DI-RX</sub>                 | Receiver Input Differential Threshold Voltage | - 0.2    |                                                                                                          | 0.2   | ٧     | 40/                                                                                               | RS485<br>port |

| R <sub>IN-RX</sub>                 | Receiver Input Resistance                     |          | 120                                                                                                      |       | Ω     | - 7V ≤ V <sub>CM</sub> ≤ +12V                                                                     |               |

| f <sub>MAX</sub>                   | RS485 maximum data rate                       | 2        |                                                                                                          |       | Mbps  |                                                                                                   |               |

| Venc-high /<br>Vhall-high          | Logic High Input Voltage                      | 3.6      |                                                                                                          |       | V     | Enc1 / Hall1                                                                                      | B0405         |

| Venc-low /<br>Vhall-low            | Logic Low Input Voltage                       |          |                                                                                                          | 2     | V     | Enc2 / Hall2<br>Strb / Hall3                                                                      | RS485<br>port |

| lenc-low /<br>Ihall-low            | Logic Low Input Current                       | - 5.2    |                                                                                                          |       | mA    | input pins                                                                                        |               |

| TMS TDI TDO TCK TRST- EMU0 EMU1 PD | JTAG interface pins                           | d<br>Tex | Please see<br>TMS320LF2406A<br>datasheet from<br>Texas Instruments<br>and V <sub>PD</sub> specifications |       |       | Directly connected from<br>DSP to connector pins.<br>EMU0 and EMU1 with 4.7k<br>internal pull up. | JTAG          |

| V <sub>PD</sub>                    | Presence detect voltage                       | 3.2      | 3.3                                                                                                      | 3.4   | V     | I <sub>PD</sub> =-100μA                                                                           | JTAG          |

| V <sub>Boot En</sub>               | Boot ROM enable input voltage                 |          |                                                                                                          | 0.5   | V     | Active low                                                                                        | JTAG          |

| I <sub>Boot-En</sub>               | Boot ROM enable input current                 |          |                                                                                                          | - 100 | μΑ    | Active low                                                                                        | JIAG          |

|                                    |                                               |          |                                                                                                          |       |       |                                                                                                   |               |

|                                    |                                               |          |                                                                                                          |       |       |                                                                                                   |               |

|                                    |                                               |          |                                                                                                          |       |       |                                                                                                   |               |

|                                    |                                               |          |                                                                                                          |       |       |                                                                                                   |               |

|                                    |                                               |          |                                                                                                          |       |       |                                                                                                   |               |

## AC Electrical Characteristics: Embedded Driving Board (EDB) DSP pins mapping

For proper operation the device should be used within the recommended conditions.

Vin = 15V, Vin-iso = 5V,  $T_C = T_{MIN}$  to  $T_{MAX}$  (unless otherwise specified)

| Symbol                | Parameter Definition                            | Min.                                                                                                                                                                               | Тур.  | Max.  | Units | Test<br>Conditions | DSP<br>pin         |

|-----------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------------------|--------------------|

| $V_{\text{DCgain}}$   | DC bus voltage feedback partition coefficient   | 3.40                                                                                                                                                                               | 3.47  | 3.54  | mV/V  |                    | 72                 |

| $V_{DCpole}$          | DC bus voltage feedback filter pole             | 680                                                                                                                                                                                | 720   | 760   | Hz    |                    | 12                 |

| VTHgain               | Thermal sensor feedback value at 25 °C 1        | 2.150                                                                                                                                                                              | 2.268 | 2.382 | V     |                    | - 70               |

| Vin-gain              | Input voltage feedback partition coefficient    | 125                                                                                                                                                                                | 128   | 131   | mV/V  |                    |                    |

| Vin-pole              | Input voltage feedback filter pole              | 1600                                                                                                                                                                               | 1700  | 1800  | Hz    |                    | 69                 |

| lph- <sub>GAIN</sub>  | Current feedback gain                           | 16.3                                                                                                                                                                               | 16.5  | 16.7  | mV/A  |                    |                    |

| Iph-pole              | Current feedback filter pole <sup>3</sup>       | 4.3                                                                                                                                                                                | 5.0   | 5.7   | kHz   |                    | ph1: 79            |

| lph- <sub>LAT</sub>   | Current feedback signal delay                   |                                                                                                                                                                                    |       | 12    | μs    | - all phases       | ph2: 77<br>ph3: 74 |

| Iph- <sub>Zero</sub>  | Zero current input voltage level <sup>2</sup>   | 1.63                                                                                                                                                                               | 1.65  | 1.67  | V     |                    | pns. 74            |

| I <sub>SC</sub>       | Short Circuit Threshold Current                 | 110                                                                                                                                                                                | 128   | 146   | А     | all phases         | _                  |

| I <sub>SC-DEL</sub>   | Short Circuit detection delay time              |                                                                                                                                                                                    | 3     | 6     | μs    | all phases         | 6                  |

| DCoc                  | DC bus minus over-current level                 | 55                                                                                                                                                                                 | 60    | 65    | А     | DC bus minus       |                    |

| DC <sub>OC-pole</sub> | DC bus minus over-current filter pole           |                                                                                                                                                                                    | 400   |       | kHz   | DC bus minus       | 6                  |

| WD                    | External watchdog timeout (see also RS~ signal) | 0.9                                                                                                                                                                                | 1.6   | 2.5   | Sec   |                    | 85                 |

| PDPINTB               | Power Down Protection Interrupt B               |                                                                                                                                                                                    | 3.3   |       | V     | 4.7k pull up       | 95                 |

| COM                   | DSP Ground                                      | 2, 3, 5, 7, 11, 12, 13, 14, 15, 19, 21, 22, 23, 24, 26, 27, 29, 32, 34, 38, 41, 43, 45, 46, 48, 49, 50, 53, 56, 58, 60, 63, 65, 66, 67, 68, 71, 73, 75, 76, 78, 80, 81, 84, 90, 97 |       |       |       |                    |                    |

| 3.3V                  | DSP 3.3V supply                                 | 4, 10, 20, 30, 35, 47, 54, 59, 64, 91, 98                                                                                                                                          |       |       |       |                    |                    |

|                       |                                                 |                                                                                                                                                                                    |       |       |       |                    |                    |

|                       |                                                 |                                                                                                                                                                                    |       |       |       |                    |                    |

|                       |                                                 |                                                                                                                                                                                    |       |       |       |                    |                    |

|                       |                                                 |                                                                                                                                                                                    |       |       |       |                    |                    |

<sup>&</sup>lt;sup>3</sup> First samples have been assembled with a 20kHz filter pole

## Other DSP pins mapping

| Signal Definition                           | DSP pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase 1 high side IGBT gate drive signal    | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DSP Event Manager A output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Phase 1 low side IGBT gate drive signal     | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DSP Event Manager A output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Phase 2 high side IGBT gate drive signal    | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DSP Event Manager A output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Phase 2 low side IGBT gate drive signal     | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DSP Event Manager A output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Phase 3 high side IGBT gate drive signal    | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DSP Event Manager A output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Phase 3 low side IGBT gate drive signal     | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | DSP Event Manager A output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Incremental Encoder input 1                 | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Optically isolated input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Incremental Encoder input 2                 | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Optically isolated input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Incremental Encoder Strobe signal           | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Optically isolated input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3.3V reference voltage                      | 82, 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3.3V reference voltage for ADC converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Flash programming voltage pin               | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Supplied by the embedded flyback regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Boot ROM enable signal                      | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | See also EDB electrical characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SCI transmit data                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Drives Tx+ and Tx- through an opto-isolator and a line driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SCI receive data                            | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Driven by Rx+ and Rx- through an opto-isolator and a line driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SCI transmit enable                         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Transmit enable for SCI line driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| System general fault input (latched)        | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Activated by short circuits on output phases and DC bus minus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| System general fault output reset signal    | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LFAULT Reset signal, to be activated via software after a fault or system boot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| System general fault input (not latched)    | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Activated by short circuits on output phases and DC bus minus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DSP reset input signal (see also WD signal) | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Forces a DSP reset if WD signal holds too long (see also EDB electrical char.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PLL oscillator input pin                    | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | A 10Mhz oscillator at 100ppm frequency stability feeds this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PLL filter input 1                          | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PLL filter for 40Mhz DSP clock frequency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |