# MPPS™ Miniature Package Power Solutions COMBINATION DUAL DIE MLP EVALUATION BOARD THERMAL **SPECIFICATION SHEET**

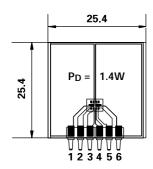

### **EVALUATION BOARD DIAGRAM**

| DEVICE          | PIN CONNECTIONS |    |    |    |    |    |

|-----------------|-----------------|----|----|----|----|----|

|                 | 1               | 2  | 3  | 4  | 5  | 6  |

| Dual Transistor | C1              | В1 | E1 | В2 | E2 | C2 |

| Dual MOSFET     | D1              | S1 | G1 | S2 | G2 | D2 |

Note: Designers needing to evaluate electrical performance using the thermal evaluation boards must be aware that the device(s) pass the the datasheet limits but the resistance paths of the PCB contribute significant series resistance.

This should be taken into account when measuring higher current VCE(sat) , VBE(sat) and VBE(on) parameters.

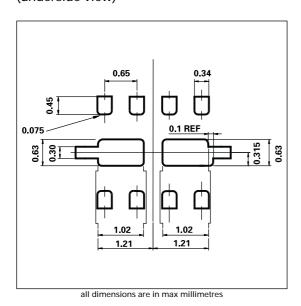

### **RECOMMENDED FOOTPRINT 3mm x 2mm MLP** (underside view)

3mm x 2mm (Dual die) MLP

**SHORTFORM TABLES** (see page 3)

ZETEX

# ZXTD\*\*M832EV ZXM\*\*\*M832EV

## ${\rm P_D}$ & THERMAL DATA

| PARAMETER                                                     | SYMBOL                                       | LIMIT        | UNIT       |  |

|---------------------------------------------------------------|----------------------------------------------|--------------|------------|--|

| Power Dissipation at TA=25°C                                  |                                              |              |            |  |

| Power Dissipation at TA=25°C (a)(f)<br>Linear Derating Factor | PD                                           | 1.5<br>12    | W<br>mW/°C |  |

| Power Dissipation at TA=25°C (b)(f)<br>Linear Derating Factor | P <sub>D</sub>                               | 2.45<br>19.6 | W<br>mW/°C |  |

| Power Dissipation at TA=25°C (c)(f)<br>Linear Derating Factor | PD                                           | 1<br>8       | W<br>mW/°C |  |

| Power Dissipation at TA=25°C (d)(f)<br>Linear Derating Factor | PD                                           | 1.13<br>9    | W<br>mW/°C |  |

| Power Dissipation at TA=25°C (d)(g)<br>Linear Derating Factor | P <sub>D</sub>                               | 1.7<br>13.6  | W<br>mW/°C |  |

| Power Dissipation at TA=25°C (e)(g)<br>Linear Derating Factor | P <sub>D</sub>                               | 3<br>24      | W<br>mW/°C |  |

| Operating and Storage Temperature Range                       | T <sub>j</sub> :T <sub>stg</sub> -55 to +150 |              | °C         |  |

| THERMAL RESISTANCE                                            |                                              |              |            |  |

| Junction to Ambient (a)(f)                                    | $R_{\theta JA}$                              | 83.3         | °C/W       |  |

| Junction to Ambient (b)(f)                                    | $R_{\theta JA}$                              | 51           | °C/W       |  |

| Junction to Ambient (c)(f)                                    | $R_{\theta JA}$                              | 125          | °C/W       |  |

| Junction to Ambient (d)(f)                                    | $R_{\theta JA}$                              | 111          | °C/W       |  |

| Junction to Ambient (d)(g)                                    | $R_{\theta JA}$                              | 73.5         | °C/W       |  |

| Junction to Ambient (e)(g)                                    | $R_{\theta JA}$                              | 41.7         | °C/W       |  |

#### Notes

(a) For a dual device surface mounted on 8 sq cm single sided 2oz copper on FR4 PCB, in still air conditions with all exposed pads attached. The copper area is split down the centre line into two separate areas with one half connected to each half of the dual device.

(b) Measured at t<5 secs for a dual device surface mounted on 8 sq cm single sided 2oz copper on FR4 PCB, in still air conditions with all exposed pads attached. The copper area is split down the centre line into two separate areas with one half connected to each half of the dual device.

(c) For a dual device surface mounted on 8 sq cm single sided 2oz copper on FR4 PCB, in still air conditions with minimal lead connections only.

(d) For a dual device surface mounted on 10 sq cm single sided 1oz copper on FR4 PCB, in still air conditions with all exposed pads attached attached. The copper area is split down the centre line into two separate areas with one half connected to each half of the dual device.

- (e) For a dual device surface mounted on 85 sq cm single sided 2oz copper on FR4 PCB, in still air conditions with all exposed pads attached. The copper area is split down the centre line into two separate areas with one half connected to each half of the dual device.

- (f) For a dual device with one active die.

- (g) For dual device with 2 active die running at equal power.

- (i) The minimum copper dimensions required for mounting are no smaller than the exposed metal pads on the base of the device as shown in the package dimensions data. The thermal resistance for a dual device mounted on 1.5mm thick FR4 board using minimum copper 1 oz weight, 1mm wide tracks and one half of the device active is Rth = 250°C/W giving a power rating of Ptot = 500mW.

# ZXTD\*\*M832EV ZXM\*\*\*M832EV

Notes

# ZXTD\*\*M832EV ZXM\*\*\*M832EV

## **SHORTFORM TABLE** (Transistor)

| Dual Transistor | Part                  |       | V <sub>CEO</sub> | I <sub>C</sub>  | Combination Dual           | Part | Polarity | V <sub>CEO</sub> | Ic   |

|-----------------|-----------------------|-------|------------------|-----------------|----------------------------|------|----------|------------------|------|

| Device Type     | Code                  |       | V                | Α               | Device Type                | Code |          | v                | Α    |

|                 |                       |       | #ZXTDA1M832EV    | DA1             | NPN                        | 15   | 4.5      |                  |      |

| #ZXTDAM832EV    | ZXTDBM832EV DBB NPN & |       | 4.5              | #ZXIDATIVIO3ZEV | JAI                        | PNP  | -12      | -4               |      |

| #ZXTDBM832EV    |                       | NPN   | 20<br>50         | 4.5<br>4        | #ZXTDB2M832EV              | DB2  | NPN      | 20               | 4.5  |

|                 |                       |       |                  |                 |                            |      | PNP      | -20              | -3.5 |

| #ZXTD2M832EV    |                       |       |                  |                 | # <b>7</b> VTD02M022EV     | DC3  | NPN      | 50               | 4    |

|                 | D11                   | PNP & | -12              | -4              | #ZXTDC3M832EV              | DC3  | PNP      | -40              | -3   |

|                 | D22<br>D33            | PNP   | -20<br>-40       | -3.5<br>-3      | #ZXTDE4M832EV              | DE4  | NPN      | 80               | 3.5  |

|                 |                       |       |                  |                 | # L A I DE 4 IVI 8 3 2 E V | DE4  | PNP      | -70              | -2.5 |

### **SHORTFORM TABLE (MOSFET)**

| Dual Transistor | Part<br>Code | Polarity  | BV <sub>DSS</sub> | טי   | Combination Dual | Part Pola | Polarity  | BV <sub>DSS</sub> | I <sub>D</sub> |

|-----------------|--------------|-----------|-------------------|------|------------------|-----------|-----------|-------------------|----------------|

| Device Type     | Couc         |           | V                 | Α    | Device Type      | Couc      |           | V                 | Α              |

| #ZXMN2AM832EV   | DNA          | N-Channel | 20                | 2.9  |                  |           | N-Channel | 30                | 2.9            |

| #ZXMN3AM832EV   | DNB          | N-Channel | 30                | 2.9  | #ZXMC3AM832EV    | C01       |           |                   |                |

| #ZXMP62M832EV   | DPA          | P-Channel | -20               | -1.3 |                  |           | P-Channel | -30               | -2.1           |

<sup>#</sup> Prefix is an internal ordering requirement only.

### © Zetex plc 2002

Europe Americas Asia Pacific Zetex plc Fields New Road Zetex (Asia) Ltd 3701-04 Metroplaza, Tower 1 Hing Fong Road Kwai Fong Zetex Inc 700 Veterans Memorial Hwy Zetex GmbH Streitfeldstraße 19 Fields New Road Chadderton Oldham, OL9 8NP United Kingdom Telephone (44) 161 622 4422 Fax: (44) 161 622 4420 D-81673 München Hauppauge, NY11788 Germany Telefon: (49) 89 45 49 49 0 Fax: (49) 89 45 49 49 49 Hong Kong Telephone: (852) 26100 611 Fax: (852) 24250 494 Telephone: (631) 360 2222 Fax: (631) 360 8222 europe.sales@zetex.com usa.sales@zetex.com asia.sales@zetex.com

These offices are supported by agents and distributors in major countries world-wide.

This publication is issued to provide outline information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned. The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.

For the latest product information, log on to  $\boldsymbol{www.zetex.com}$

ISSUE 1 - SEPTEMBER 2002

SCMPPSTMEV