# Z8<sup>Plus</sup> User's Manual

© 1999 by ZiLOG, Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of ZiLOG, Inc. The information in this document is subject to change without notice. Devices sold by ZiLOG, Inc. are covered by warranty and patent indemnification provisions appearing in ZiLOG, Inc. Terms and Conditions of Sale only.

ZiLOG, Inc. makes no warranty, express, statutory, implied or by description, regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. ZiLOG, Inc. makes no warranty of merchantability or fitness for any purpose.

The software described herein is provided on an as-is basis and without warranty. ZiLOG accepts no liability for incidental or consequential damages arising from use of the software.

ZiLOG, Inc. shall not be responsible for any errors that may appear in this document. ZiLOG, Inc. makes no commitment to update or keep current the information contained in this document.

ZiLOG's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to such intended use is executed between the customer and ZiLOG prior to use. Life support devices or systems are those which are intended for surgical implantation into the body, or which sustains life whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

ZiLOG, Inc. 910 East Hamilton Ave., Suite 110 Campbell, CA 95008

Telephone: (408) 558-8500 FAX: (408) 558-8300

Internet: http://www.zilog.com

The following conventions have been adopted to provide clarity and ease of use:

#### Courier Font For Executables

Commands, variables, icon names, entry field names, selection buttons, code examples, and other executable items are distinguished by the use of the Courier font. Where the use of the font is not possible, like in the Index, the name of the entity is capitalized. For example, a procedure may contain an instruction which appears as: Click on File. However, an Index entry would appear as FILE.

### • Grouping of Actions Within A Procedure Step

Actions in a procedure step are all performed on the same window or dialog box. Actions performed on different windows or dialog boxes appear in separate steps.

### • Sequencing Words Within A Procedure Step

When an item in a procedure contains a series of actions, the second action is preceded by the word *then*, and the third and subsequent actions are preceded by the word *and*. For example: Click on View, then Memory, and Z8 Code Memory.

• Unavailable menu items are presented in gray.

## **ADDITIONAL SOURCES OF INFORMATION**

In addition to this manual, you should have access to and be familiar with the following documentation:

- Z8 Microcontrollers User's Manual, UM95Z800103

- Data Sheet for each product with which you work.

# Z8<sup>PLUS</sup> USER'S MANUAL

Totally Logical

# TABLE OF CONTENTS

| Chapter Title and Subsections     | Page |

|-----------------------------------|------|

| Chapter 1. Address Space          |      |

| Introduction                      | 1-1  |

| Register File Space               | 1-1  |

| General-Purpose Registers         | 1-5  |

| Working Register Groups           | 1-6  |

| Precautions                       | 1-8  |

| Control and Peripheral Registers  | 1-10 |

| Control Registers                 | 1-10 |

| Peripheral Registers              | 1-10 |

| Program Memory                    | 1-11 |

| Stack                             | 1-13 |

| Chapter 2. Addressing Modes       |      |

| Addressing Modes                  | 2-1  |

| Register Addressing (R)           | 2-2  |

| Indirect Register Addressing (IR) | 2-3  |

| Indexed Addressing (X)            | 2-5  |

| Direct Addressing (DA)            | 2-7  |

| Relative Addressing (RA)          | 2-8  |

| Immediate Data Addressing (IM)    | 2-9  |

UM001000-Z8X0199

| Chapter Title and Subsections       | Page |

|-------------------------------------|------|

| Chapter 3. Instruction Set          |      |

| Functional Summary                  | 3-1  |

| Processor Flags                     | 3-5  |

| Condition Codes                     | 3-7  |

| Notation And Binary Encoding        | 3-10 |

| Assembly Language Syntax            | 3-12 |

| Z8Plus Instruction Summary          | 3-12 |

| Opcode Map                          | 3-18 |

| Instruction Description and Formats | 3-19 |

| ADC-Add with Carry                  | 3-20 |

| ADC-Add with Carry                  | 3-22 |

| ADD-Add                             | 3-23 |

| AND-Logical AND                     | 3-25 |

| CALL-Call Procedure                 | 3-27 |

| CCF-Complement Carry Flag           | 3-29 |

| CLR-Clear                           | 3-30 |

| COM-Complement                      | 3-31 |

| CP-Compare                          | 3-32 |

| DA-Decimal Adjust                   | 3-34 |

| DEC-Decrement                       | 3-37 |

| DECW-Decrement Word                 | 3-38 |

| DI-Disable Interrupts               | 3-39 |

| DJNZ-Decrement And Jump If Non-zero | 3-40 |

| EI-Enable Interrupts                | 3-42 |

| HALT-Halt                           | 3-43 |

| INC-Increment                       | 3-44 |

| INCW-Increment Word                 | 3-46 |

| IRET-Interrupt Return               | 3-47 |

| JP-Jump                             | 3-48 |

| Chapter Title and Subsection      | Page |

|-----------------------------------|------|

| JR–Jump Relative                  | 3-50 |

| LD-Load                           | 3-51 |

| LDC-Load Constant                 | 3-55 |

| LDCI-Load Constant Auto Increment | 3-57 |

| NOP-No Operation                  | 3-59 |

| OR-Logical OR                     | 3-60 |

| POP-Pop                           | 3-62 |

| PUSH-Push                         | 3-63 |

| RCF-Reset Carry Flag              | 3-64 |

| RET-Return                        | 3-65 |

| RL-Rotate Left                    | 3-66 |

| RLC-Rotate Left Through Carry     | 3-68 |

| RLC-Rotate Left Through Carry     | 3-69 |

| RR-Rotate Right                   | 3-70 |

| RRC-Rotate Right Through Carry    | 3-72 |

| RRC-Rotate Right Through Carry    | 3-73 |

| SBC-Subtract with Carry           | 3-74 |

| SCF-Set Carry Flag                | 3-76 |

| SRA-Shift Right Arithmetic        | 3-77 |

| SRP-Set Register Pointer          | 3-79 |

| STOP-Stop                         | 3-81 |

| SUB-Subtract                      | 3-82 |

| SWAP-Swap Nibbles                 | 3-84 |

| TCM-Test Complement Under Mask    | 3-85 |

| TM-Test Under Mask                | 3-87 |

| WDT-Watch-Dog Timer               | 3-89 |

| XOR-Logical Exclusive OR          | 3-90 |

| Z8 <sup>PLUS</sup> | User's | Manual |

|--------------------|--------|--------|

| Table              | of Con | tents  |

| Chapter Title and Subsections                      |      |

|----------------------------------------------------|------|

| Chapter 4. Interrupts                              |      |

| Introduction                                       | 4-1  |

| Interrupt Sources                                  | 4-3  |

| External Interrupt Sources                         | 4-3  |

| Internal Interrupt Sources                         | 4-4  |

| Interrupt Request (IREQ) Register Logic And Timing | 4-4  |

| Interrupt Mask Register (IMASK) Initialization     | 4-5  |

| Interrupt Request (IREQ) Register Initialization   | 4-7  |

| IREQ Software Interrupt Generation                 | 4-9  |

| Vectored Processing                                | 4-9  |

| Nesting of Vectored Interrupts                     | 4-11 |

| Polled Processing                                  | 4-12 |

| Reset Conditions                                   | 4-12 |

# Appendix A. Accessing the ZBBS/Internet

**Bulletin Board Information**

How to Access the ZBBS

ZiLOG On The Internet

# **Problem/Suggestion Report Form**

## Index

# Z8<sup>PLUS</sup> USER'S MANUAL

Totally Logical

# LIST OF FIGURES

| Chapter Title and Subsections                                                                                                                                                                                                                                                                                                                                                 | Page                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Chapter 1. Address Space  Figure 1-1. Complete Register File RAM Space  Figure 1-2. 16-Bit Register Addressing  Figure 1-3. Accessing Individual Bits (Example)  Figure 1-4. Working Register Addressing (Example)  Figure 1-5. Register Pointer  Figure 1-6. Program Memory Map  Figure 1-7. Stack Pointer  Figure 1-8. Stack Operations                                     | 1-5 1-7 1-8 1-12 1-13   |

| Chapter 2. Addressing Modes  Figure 2-1. 8-Bit Register Addressing  Figure 2-2. 4-Bit Register Addressing  Figure 2-3. Indirect Addressing of Register File Memory  Figure 2-4. Indirect Register Addressing to Program Memory  Figure 2-5. Indexed Register Addressing  Figure 2-6. Direct Addressing  Figure 2-7. Retrieve Addressing  Figure 2-8. Immedate Data Addressing | 2-3 2-4 2-5 2-6 2-7 2-8 |

| Chapter 3. Instruction Set Figure 3-1. Flag Register Figure 3-2. Op Code Map                                                                                                                                                                                                                                                                                                  |                         |

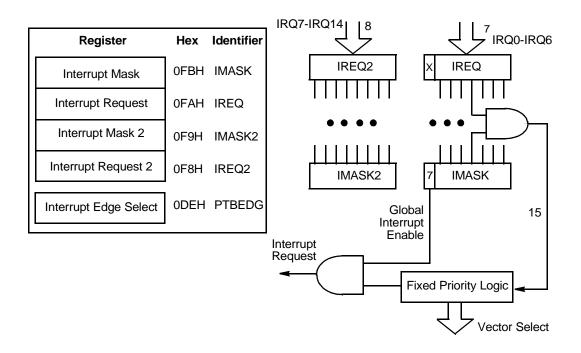

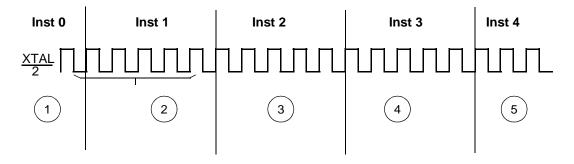

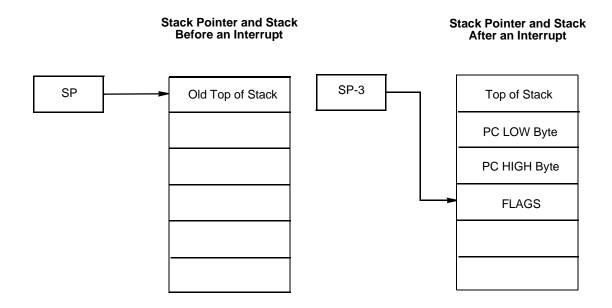

| Chapter 4. Interruupts  Figure 4-1. Interrupt Control Register Addresses and Identifiers  Figure 4-2. Interrupt Block Diagram  Figure 4-3. Interrupt Service Sequence  Figure 4-4. Interrupt Mask Register  Figure 4-5. Interrupt Mask 2 Register                                                                                                                             | 4-2<br>4-4<br>4-5       |

UM001000-Z8X0199 xi

| Z8 <sup>PL</sup> | <sup>US</sup> User's Manual |

|------------------|-----------------------------|

| List             | of Figures                  |

| 77.1 | $\sim$ |

|------|--------|

|      |        |

| Figure 4-6. Interrupt Request Register           | 4-7 |

|--------------------------------------------------|-----|

| Figure 4-7. Interrupt Request Register 2         | 4-8 |

| Figure 4-8. Stacks Before and After Interrupt 4- | -10 |

| Figure 4-9. Interrupt Vector Table Location      | -11 |

xii UM001000-Z8X0199

# Z8<sup>PLUS</sup> USER'S MANUAL

Totally Logical

# LIST OF TABLES

| Chapter Title and Subsections                                               | Page |

|-----------------------------------------------------------------------------|------|

| Chapter 1. Address Space                                                    |      |

| Table 1-1 Z8 <sup>PLUS</sup> Core Control Registers                         | 1-3  |

| Table 1-1 Page 0 Register File Organization                                 |      |

| Chapter 3. Instruction Set                                                  |      |

| Table 3-1 Load Instructions                                                 | 3-2  |

| Table 3-2 Arithmetic Instructions                                           |      |

| Table 3-3 Logical Instructions                                              |      |

| Table 3-4 Program Control Instructions                                      |      |

| Table 3-5 Bit Manipulation Instructions                                     |      |

| Table 3-6 Block Transfer Instructions                                       |      |

| Table 3-7 Rotate and Shift Instructions                                     | 3-4  |

| Table 3-8 CPU Control Instructions                                          | 3-4  |

| Table 3-9 Flag Definitions                                                  | 3-7  |

| Table 3-10 Flag Settings Definitions                                        |      |

| Table 3-11 Condition Codes                                                  |      |

| Table 3-12 Notational Shorthand                                             | 3-10 |

| Table 3-13 Additional Symbols                                               | 3-11 |

| Table 3-14 Instruction Summary                                              | 3-13 |

| Table 3-15 Lower Nibble Values                                              | 3-17 |

| Table 3-16 DA Operation Reference                                           | 3-34 |

| Table 3-17 Register Pointers, Working Register Groups, and Actual Registers | 3-79 |

| Chapter 4. Interrupts                                                       |      |

| Table 4-1 Z8E001 Interrupt Types, Sources, and Vectors                      | 4-3  |

UM001000-Z8X0199 xiii

### INTRODUCTION

Two address spaces are available for the Z8<sup>PLUS</sup> MCU:

- Register file RAM contains addresses for all the control registers and all the general purpose registers.

- · Program memory contains addresses for all memory locations where executable code and/or data are stored.

### REGISTER FILE SPACE

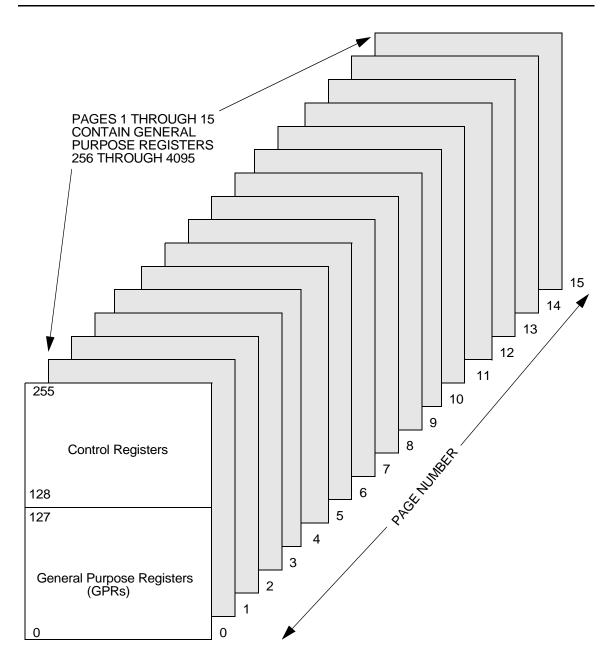

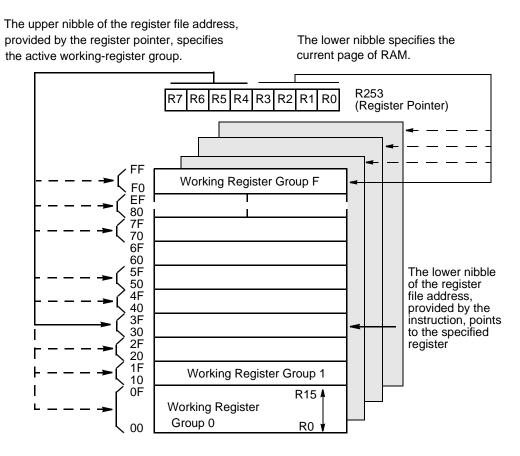

The on-chip register file RAM is organized into 16 pages, where each page has 256 addressable memory locations. The first page (page 0) contains both control registers and general purpose registers. All the remaining pages (pages 1 through 15) contain only general purpose registers. Figure 1-1 illustrates the complete register file RAM space. As shown, control registers are located in the upper half of page 0. Any specific implementation of the Z8<sup>PLUS</sup> core may use only a subset of the complete register file RAM space.

Table 1-1 describes the Core Control Registers and Table 1-2 shows the Page 0 Register File organization.

All registers on the  $Z8^{PLUS}$ -family products are fully read/writable. Hardware may write lock certain registers or bits under some conditions. The TCTLHI register is one such example.

UM001000-Z8X0199 1–1

Figure 1-1. Complete Register File RAM Space

Table 1-1. Z8<sup>PLUS</sup> Core Control Registers

| Hex Address | Register Name | Register Description | Comments             |

|-------------|---------------|----------------------|----------------------|

| 0FFH        | STKPTR (SPL)  | Stack Pointer Low    | LSB of Stack Pointer |

| 0FEH        | SPH           | Stack Pointer High   | MSB of Stack Pointer |

| 0FDH        | REGPTR(RP)    | Register Pointer     |                      |

| 0FCH        | FLAGS         | Flags                |                      |

| 0FBH        | IMASK         | Interrupt Mask 1     | Ints. 0 - 6          |

| 0FAH        | IREQ          | Interrupt Request 1  | Ints. 0 - 6          |

| 0F9H        | IMASK2        | Interrupt Mask 2     | Ints. 7 - 14         |

| 0F8H        | IREQ2         | Interrupt Request 2  | Ints. 7 - 14         |

| 0F7H        |               |                      | Reserved             |

| 0F6H        |               |                      | Reserved             |

| 0F5H        |               |                      | Reserved             |

| 0H4H        |               |                      | Reserved             |

| 0F3H        |               |                      | Reserved             |

| 0F2H        |               |                      | Reserved             |

| 0F1H        |               |                      | Reserved             |

| 0F0H        |               |                      | Reserved             |

The Stack Pointer High register (0FEH), the interrupt mask register 2 (0F9H), and the interrupt request register 2 (0F8H) are optional and are reserved if not implemented.

Table 1-2. Page 0 Register File Organization

| Hex Address Range | Register Description                             |  |

|-------------------|--------------------------------------------------|--|

| F0 - FF           | Core Control Registers                           |  |

| E0 - EF           | Virtual Copy of the Current Working Register Set |  |

| D0 - DF           | Port Logic Control Registers                     |  |

| C0 -CF            | Timer Peripherals Control Registers              |  |

| B0 - BF           | Reserved for Future Extensions                   |  |

| A0 - AF           | Reserved for Future Extensions                   |  |

| 90 - 9F           | Reserved for Future Extensions                   |  |

| 80 - 8F           | Reserved for Future Extensions                   |  |

| 70 - 7F           | General Purpose Registers                        |  |

| 60 - 6F           | General Purpose Registers                        |  |

| 50 - 5F           | General Purpose Registers                        |  |

| 40 - 4F           | General Purpose Registers                        |  |

| 30 - 3F           | General Purpose Registers                        |  |

| 20 - 2F           | General Purpose Registers                        |  |

| 10 -1F            | General Purpose Registers                        |  |

| 00 - 0F           | General Purpose Registers                        |  |

Registers can be accessed as either 8-bit or 16-bit registers using Direct, Indirect, or Indexed Addressing. All general-purpose registers can be referenced or modified by any instruction that accesses an 8-bit register, without the need for special instructions. Registers accessed as 16 bits are treated as even-odd register pairs. In this case, the data's Most Significant Byte (MSB) is stored in the even numbered register, while the Least Significant Byte (LSB) goes into the next higher odd numbered register (Figure 1-2).

Figure 1-2. 16-Bit Register Addressing

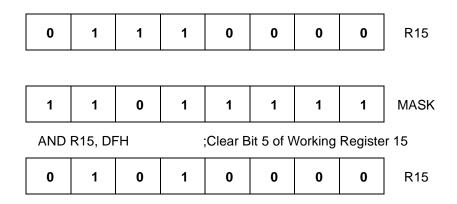

By using a logical instruction and a mask, individual bits within registers can be accessed for bit set, bit clear, bit complement, or bit test operations. For example, the instruction AND R15, MASK performs a bit clear operation. Figure 1-3 shows this example.

Figure 1-3. Accessing Individual Bits (Example)

When instructions are executed, registers are only read, not written, when defined as sources; and read and/or written when defined as destinations. All General-Purpose Registers function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

## **General-Purpose Registers**

General-Purpose Registers (GPR) are undefined after the device is powered up. The registers keep their last value after any reset, as long as the reset occurs in the  $V_{CC}$  voltage-specified operating range. It does not keep its last state from a  $V_{LV}$  reset if  $V_{CC}$  drops below 1 . 8V.

## **Working Register Groups**

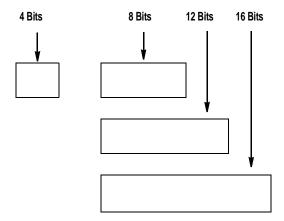

Instructions can access 8-bit registers and register pairs (16-bit words) using either 4-, 8-, or 12-bit address fields. Eight-bit address fields refer to the actual address of the register within the current page. For example, Register 58H is accessed by calling upon its 8-bit address, 01011000 (58H). The lower nibble of the Register Pointer specifies the current RAM page.

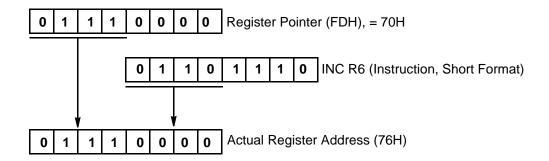

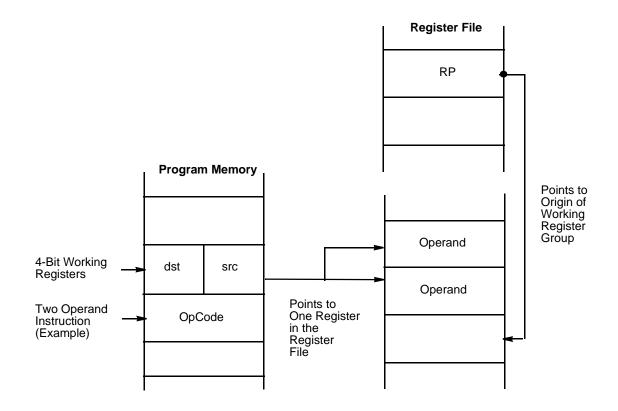

With 4-bit addressing, the register file is logically divided into 16 Working Register Groups of 16 registers each, as shown in Table 1-3. These 16 registers are known as Working Registers. A Register Pointer (one of the control registers, FDH) contains the base address of the active Working Register Group. The High nibble of the Register Pointer determines the current Working Register Group.

When accessing one of the Working Registers, the 4-bit address of the Working Register is combined with the upper four bits (High nibble) of the Register Pointer, thus forming the 8-bit actual address. Figure 1-4 illustrates this operation. Since working registers are typically specified by short format instructions, there are fewer bytes of code needed. In addition, when processing interrupts or changing tasks, the Register Pointer (see Figure 1-5) speeds context switching. A special Set Register Pointer (SRP) instruction sets the contents of the Register Pointer.

Data transfer across RAM page boundaries can be accomplished via 12-bit addressing. Using certain instruction modes, data can be moved from the current page and working group into any register on the chip by specifying the absolute 12-bit address, including page. Not all family members support 12-bit addressing. See the applicable product specification for specific information.

Table 1-3. Working Register Groups

| Register Pointer (FDH)<br>High Nibble (Binary) | Working Register Group<br>(HEX) | Actual Registers (HEX) |

|------------------------------------------------|---------------------------------|------------------------|

| 1111                                           | F                               | F0 - FF                |

| 1110                                           | Е                               | E0 - EF                |

| 1101                                           | D                               | D0 - DF                |

| 1100                                           | С                               | C0 - CF                |

| 1011                                           | В                               | B0 - BF                |

| 1010                                           | A                               | A0 - AF                |

| 1001                                           | 9                               | 90 - 9F                |

| 1000                                           | 8                               | 80 - 8F                |

| 0111                                           | 7                               | 70 - 7F                |

**Table 1-3. Working Register Groups (Continued)**

| Register Pointer (FDH)<br>High Nibble (Binary) | Working Register Group<br>(HEX) | Actual Registers (HEX) |

|------------------------------------------------|---------------------------------|------------------------|

| 0110                                           | 6                               | 60 - 6F                |

| 0101                                           | 5                               | 50 - 5F                |

| 0100                                           | 4                               | 40 - 4F                |

| 0011                                           | 3                               | 30 - 3F                |

| 0010                                           | 2                               | 20 - 2F                |

| 0001                                           | 1                               | 10 - 1F                |

| 0000                                           | 0                               | 00 - 0F                |

Figure 1-4. Working Register Addressing (Example)

Figure 1-5. Register Pointer

#### **Precautions**

Registers in the Standard Register File must be correctly used or certain conditions produce inconsistent results.

- The watch-dog timer can only be disabled via software if the first instruction out of RESET performs this function. During the execution of the first instruction after the Z8<sup>PLUS</sup> leaves RESET, the upper five bits of the TCTLHI register can be written. After the first instruction, hardware does not allow the upper five bits of this register to be written.

- Some control registers, including the port inputs and timer count registers, may be updated by hardware.

Writing these registers from software always overrides the hardware update from the same cycle, but with unpredictable results. For example, writing into the count value register of a running timer can cause

unexpected results if the hardware was in the process of decrementing the timer for the terminal count and generating an interrupt.

• The register space from 0E0H-0EFH is special. The MCU uses these addresses to flag accesses via 4-bit addressing mode to the current working register group. There are no physical registers at that location. Care must be taken that the Register Pointer never points at Group E on the first page (be loaded with E0H). This is an undefined case. Also, indirect addressing does *not* redirect a second time and find the working registers. This is also an undefined case. As an example, in the code below, R0 does *not* find the data in register 08. It returns garbage. R2 correctly contains a copy of register 08.

| SRP | #%00     |

|-----|----------|

| LD  | R1, #%E8 |

| LD  | R0, @R1  |

| LD  | R2,%E8   |

#### CONTROL AND PERIPHERAL REGISTERS

## **Control Registers**

The standard control registers govern the operation of the CPU. Any instruction which references the register file can access these control registers. Available control registers are:

- Stack Pointer Low (SPL or STKPTR)

- Stack Pointer High (SPH)

- Register Pointer (RP or REGPTR)

- Flags (FLAGS)

- Interrupt Mask 1 (IMASK)

- Interrupt Request 1 (IREQ)

- Interrupt Mask 2 (IMASK2)

- Interrupt Request 2 (IREQ2)

A 16-bit Program Counter (PC) to determine the sequence of current program instructions. The PC is not an addressable register.

## **Peripheral Registers**

Peripheral registers are used to transfer data, configure the operating mode, and control the operation of the on-chip peripherals. Any instruction that references the register file can access the peripheral registers. Possible peripheral registers can include:

- Timer Count Value Register for Timer n

- Auto-Initialization Value Register(s) for Timer n

- Timer Control Registers (High and Low Byte)

- Watch-Dog Timer Registers (High and Low Byte)

In addition, the port registers are considered to be peripheral registers. Ports generally have at least the following four dedicated registers which are readable and writable by software:

- Port Input Value Register

- Port Output Value Register

- Port Control Register

- Port Special Function Register

#### PROGRAM MEMORY

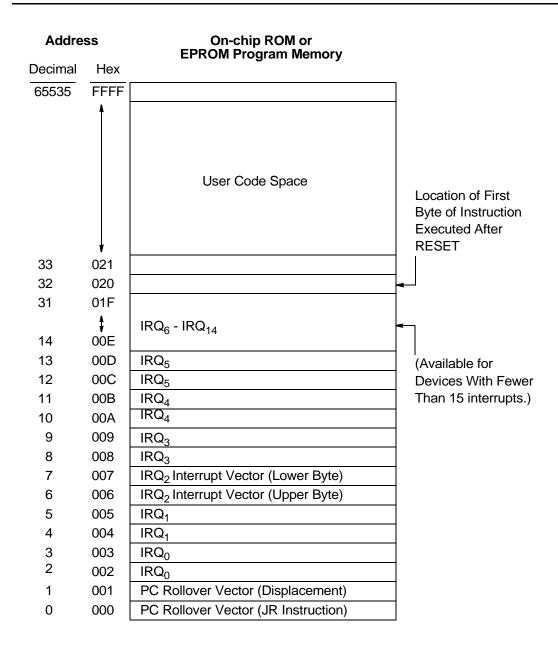

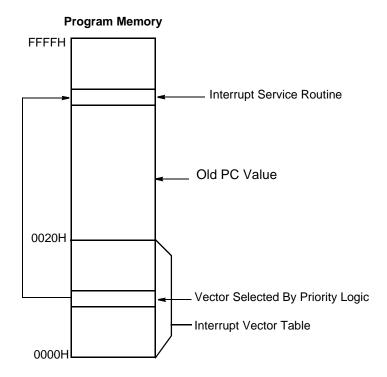

The program memory map is shown in Figure 1-6. The first two bytes of program memory are reserved for the PC rollover vector. When the PC wraps around to 0000H, bytes 0000H and 0001H are executed as instructions, enabling a user defined behavior for this occurrence. For example, a JR instruction in 0000H and a corresponding displacement in 0001H could be defined for the PC rollover vector. The next 30 bytes of Program Memory are reserved for the interrupt vectors. These locations contain 16-bit vectors that correspond to the available interrupts. Address 0020H through the end of the populated memory (0FFFFh, 64 KB maximum) consists of on-chip mask-programmable ROM or EPROM or Flash. The first byte of program memory executed following a RESET is located at 0020H. See the product data sheet for the exact program, data, register memory size, and address range available.

The internal program memory may be one-time programmable (OTP) or mask programmable dependent on the specific device. A ROM protect feature prevents dumping of the ROM contents. The ROM Protect option is mask-programmable and is selected by the customer when the ROM code is submitted. For programmable memory devices, the ROM Protect option is an OTP programming option.

1–11 UM001000-Z8X0199

Figure 1-6. Program Memory Map

1–12 UM001000-Z8X0199

ZiLOG

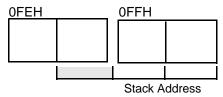

#### STACK

The stack always resides in the general purpose registers of the on-chip register file RAM. The stack pointer register (SP) contains an address into the standard register file that is the address of the operand that is currently on the top of the stack. The register 0FFH is the 8-bit stack pointer (SP), that is used for all stack operations (see Figure 1-7).

Some devices prepend the lower nibble of register 0FEH to form a 12-bit stack pointer. Otherwise, register 0FEH is reserved.

Figure 1-7. Stack Pointer

The stack address is decremented prior to a PUSH operation and incremented after a POP operation. The stack address always points to the data stored on the top of the stack. The stack is a return stack for CALL instructions and interrupts, as well as a data stack.

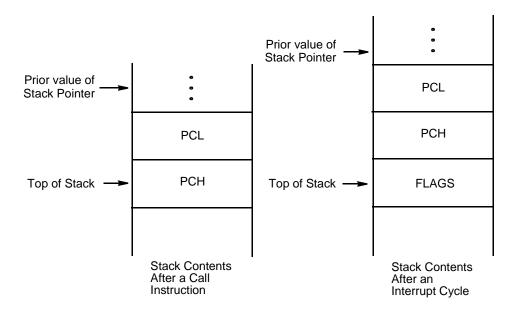

During a CALL instruction, the contents of the Program Counter are saved on the stack. The PC is restored during a RET instruction. Interrupts cause the contents of the PC and FLAGS registers to be saved on the stack. The IRET instruction restores them (see Figure 1-8).

An overflow or underflow can occur when the stack address is incremented or decremented during normal stack operations. The programmer must prevent this occurrence or unpredictable operation may result. The stack must not encroach into the control registers.

1-13

Figure 1-8. Stack Operations

#### ADDRESSING MODES

The Z8<sup>PLUS</sup> microcontroller provides six addressing modes:

- Register (R)

- Indirect Register (IR)

- Indexed (X)

- Direct Address (DA)

- Relative Address (RA)

- Immediate Data (IM)

With the exception of immediate data and condition codes, all operands are expressed as register file or Program Memory addresses. Registers are accessed using 12-bit addresses in the range of 000H-FFFH. The Program Memory is accessed using 16-bit addresses (or register pairs) in the range of 0000H-FFFFH.

Generally, registers are accessed, within the current page, by specifying an 8-bit address. The upper 4 bits of the absolute address is specified by pre-pending the lower 4 bits of the Register Pointer (0FDH) (the Page Pointer) to the 8-bit address to form a 12-bit address.

Working Registers are accessed using 4-bit addresses in the range of 0-15 (OH-FH). The address of the register being accessed is formed by the combination of the lower 4 bits of the RP (Page Pointer), the upper four bits in the Register Pointer (Group Pointer) and the 4-bit working register address supplied by the instruction.

Registers can be used in pairs to designate 16-bit values or memory addresses. A Register Pair must be specified as an even-numbered address in the range of 0–14 for Working Registers, or 0–4094 for general purpose registers.

UM001000-Z8X0199

In the following definitions of Z8<sup>PLUS</sup> Addressing Modes, the use of register can also imply register pair, working register, or working register pair, depending on the context.

**NOTE:** See the product data sheet for exact program and register memory types and address ranges available.

## **REGISTER ADDRESSING (R)**

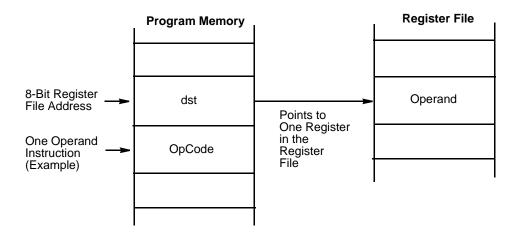

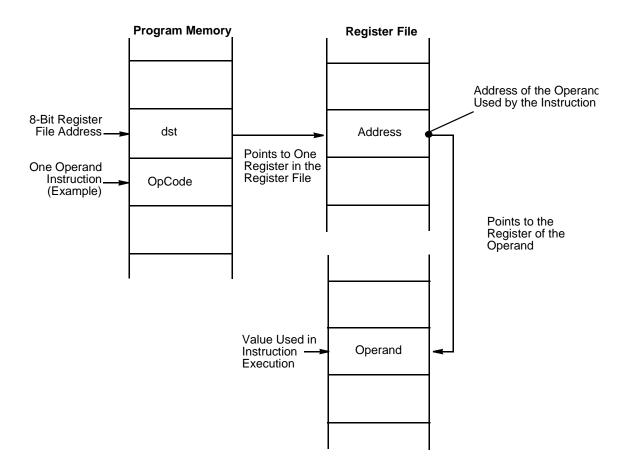

In 8-bit Register Addressing mode, the operand value is equivalent to the contents of the specified register or register pair.

In the Register Addressing (see Figure 2-1), the destination and/or source address specified corresponds to the actual register in the current page of the register file.

Figure 2-1. 8-Bit Register Addressing

Figure 2-2. 4-Bit Register Addressing

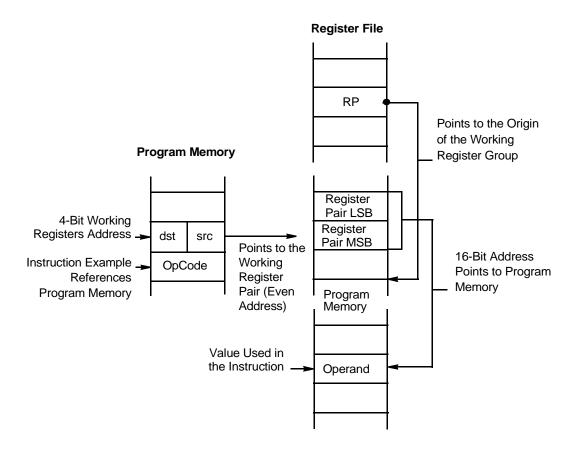

In 4-bit Register Addressing (see Figure 2-2), the destination and/or source addresses point to the Working Register within the current Working Register Group. This 4-bit address is combined with the Register Pointer to form the actual 12-bit address of the affected register.

## INDIRECT REGISTER ADDRESSING (IR)

In the Indirect Register Addressing Mode, the contents of the specified register are equivalent to the address of the operand (see Figure 2-3 and Figure 2-4).

Depending upon the instruction selected, the specified register contents points to a Register or Program Memory location.

When accessing program memory, register pairs or Working Register pairs are used to hold the 16-bit addresses.

Figure 2-3. Indirect Addressing of Register File Memory

Figure 2-4. Indirect Register Addressing to Program Memory

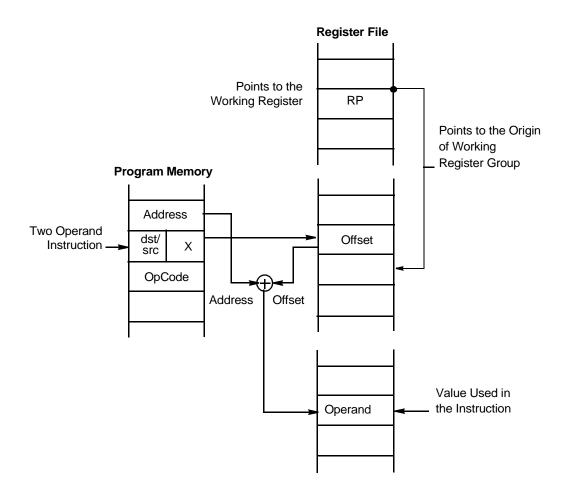

## **INDEXED ADDRESSING (X)**

The Indexed Addressing Mode is used only by the Load (LD) instruction. An indexed address consists of a register address offset by the contents of a designated Working Register (the Index). This offset is added to the register address to obtain the address of the operand. Figure 2-5 illustrates this addressing convention.

UM001000-Z8X0199 2-5

Figure 2-5. Indexed Register Addressing

# **DIRECT ADDRESSING (DA)**

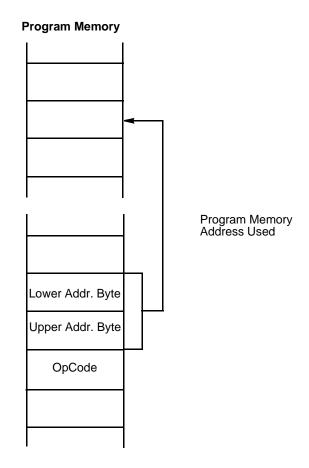

The Direct Addressing mode, as shown in Figure 2-6, specifies the address of the next instruction to be executed. Only the Conditional Jump (JP) and Call (CALL) instructions use this addressing mode.

Figure 2-6. Direct Addressing

## **RELATIVE ADDRESSING (RA)**

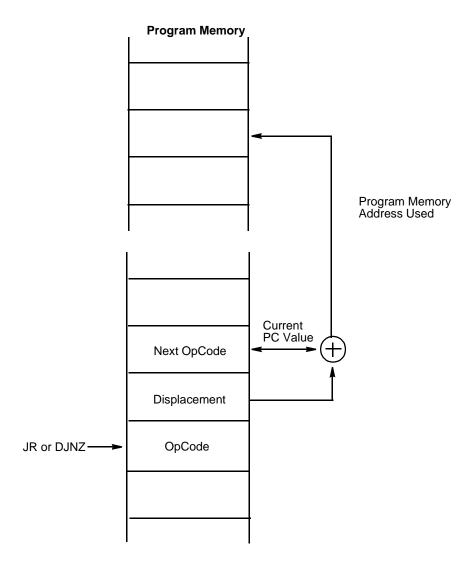

In the Relative Addressing mode, illustrated in Figure 2-7, the instruction specifies a two's-complement signed displacement in the range of -128 to +127. This is added to the contents of the Program Counter to obtain the address of the next instruction to be executed. The PC (prior to the add) consists of the address of the instruction following the Jump Relative (JR) or Decrement and Jump if Non-Zero (DJNZ) instruction. JR and DJNZ are the only instructions which use this addressing mode.

Figure 2-7. Retrieve Addressing

## **IMMEDIATE DATA ADDRESSING (IM)**

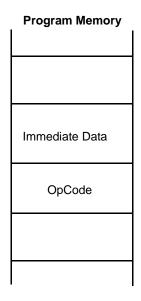

Immediate data is considered to be an addressing mode for the purposes of this discussion. It is the only addressing mode that does not indicate a register or memory address as the source operand. The operand value used by the instruction is the value supplied in the operand field itself. Because an immediate operand is part of the instruction, it is always located in the Program Memory address space (see Figure 2-8).

Figure 2-8. Immedate Data Addressing

## **FUNCTIONAL SUMMARY**

Z8<sup>PLUS</sup> instructions can be divided into the following eight functional groups:

- Load

- Arithmetic

- Logical

- Program Control

- Bit Manipulation

- Block Transfer

- Rotate and Shift

- CPU Control

Table 3-1 through Table 3-8 show the instructions belonging to each group and the number of operands required for each. The source operand is src, the destination operand is dst, and a condition code is cc.

When instructions are executed, registers defined as sources are read only. All General-Purpose Registers function as:

- accumulators

- address pointers

- index registers

- stack areas

- scratch pad memory

**Table 3-1. Load Instructions**

| Mnemonic | Operands | Instruction   |

|----------|----------|---------------|

| CLR      | dst      | Clear         |

| LD       | dst, src | Load          |

| LDC      | dst, src | Load Constant |

| POP      | dst      | Pop           |

| PUSH     | src      | Push          |

**Table 3-2. Arithmetic Instructions**

| Mnemonic | Operands | Instruction         |

|----------|----------|---------------------|

| ADC      | dst, src | Add with Carry      |

| ADD      | dst, src | Add                 |

| СР       | dst, src | Compare             |

| DA       | dst      | Decimal Adjust      |

| DEC      | dst      | Decrement           |

| DECW     | dst      | Decrement Word      |

| INC      | dst      | Increment           |

| INCW     | dst      | Increment Word      |

| SBC      | dst, src | Subtract with Carry |

| SUB      | dst, src | Subtract            |

**Table 3-3. Logical Instructions**

| Mnemonic | Operands | Instruction          |

|----------|----------|----------------------|

| AND      | dst, src | Logical AND          |

| COM      | dst      | Complement           |

| OR       | dst, src | Logical OR           |

| XOR      | dst, src | Logical Exclusive OR |

3-2 UM001000-Z8X0199

**Table 3-4. Program Control Instructions**

| Mnemonic | Operands | Instruction                 |

|----------|----------|-----------------------------|

| CALL     | dst      | Call Procedure              |

| DJNZ     | dst, src | Decrement and Jump Non-Zero |

| IRET     |          | Interrupt Return            |

| JP       | cc, dst  | Jump                        |

| JR       | cc, dst  | Jump Relative               |

| RET      |          | Return                      |

**Table 3-5. Bit Manipulation Instructions**

| Mnemonic | Operands | Instruction                   |

|----------|----------|-------------------------------|

| TCM      | dst, src | Test Complement<br>Under Mask |

| TM       | dst, src | Test Under Mask               |

| AND      | dst, src | Bit Clear                     |

| OR       | dst, src | Bit Set                       |

| XOR      | dst, src | Bit Complement                |

**Table 3-6. Block Transfer Instructions**

| Mnemonic Operands Instruc |          | Instruction                     |

|---------------------------|----------|---------------------------------|

| LDCI                      | dst, src | Load Constant<br>Auto Increment |

UM001000-Z8X0199 3-3

**Table 3-7. Rotate and Shift Instructions**

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left Through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right Through Carry |

| SRA      | dst      | Shift Right Arithmetic     |

| SWAP     | dst      | Swap Nibbles               |

**Table 3-8. CPU Control Instructions**

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| CCF      |          | Complement Carry Flag |

| DI       |          | Disable Interrupts    |

| EI       |          | Enable Interrupts     |

| HALT     |          | Halt                  |

| NOP      |          | No Operation          |

| RCF      |          | Reset Carry Flag      |

| SCF      |          | Set Carry Flag        |

| SRP      | src      | Set Register Pointer  |

| STOP     |          | Stop                  |

| WDT      |          | Refresh WDT           |

## PROCESSOR FLAGS

The Flag Register (FCH) informs the user of the processor's bcurrent status. The flags and their bit positions in the Flag Register are shown in Figure 3-1.

The Flag Register contains eight bits of status information which are set or cleared by CPU operations. Four of the bits (C, V, Z and S) can be tested for use with conditional Jump instructions. Two flags (H and D) are used for BCD arithmetic. The two remaining bits in the Flag Register are the watch-dog timer reset flag and the stop mode recovery flag. Both of these flag bits may be tested and must be explicitly cleared by software.

As with bits in the other control registers, the Flag Register bits can be set or reset by instructions; however, only those instructions that do not affect the flags as an outcome of the execution should be assigned a value.

Figure 3-1. Flag Register Flag Register (FCH: Read/Write) R252 Flags

| Bit                                                | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|----------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|

| R/W                                                | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| Reset                                              | U   | U   | U   | U   | U   | U   | *   | *   |

| R = Read W = Write X = Indeterminate U = Unchanged |     |     |     |     |     |     |     |     |

| Bit/Field         | Bit<br>Position | R/W | Value | Description                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|-----------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Carry<br>Flag (C) | 7               | R/W |       | The Carry Flag is set to 1 whenever the result of an arithmetic operation generates a carry out of or a borrow into the high order bit 7. Otherwise, the Carry Flag is cleared to 0. Following Rotate and Shift instructions, the Carry Flag contains the last value shifted out of the specified register.  An instruction can set (I), reset(O), or complement the Carry Flag. |

|                   |                 |     |       | The carry flag is not effected by RESET.                                                                                                                                                                                                                                                                                                                                         |

| Zero<br>Flag (Z)  | 6               | R/W |       | For arithmetic and logical operations, the Zero Flag is set to 1 if the result is 0. Otherwise, the Zero Flag is cleared to 0.                                                                                                                                                                                                                                                   |

|                   |                 |     |       | If the result of testing bits in a register is 00H, the Zero Flag is set to 1. Otherwise the Zero Flag is cleared to 0.                                                                                                                                                                                                                                                          |

|                   |                 |     |       | If the result of a Rotate or Shift operation is 00H, the Zero Flag is set to 1.                                                                                                                                                                                                                                                                                                  |

|                   |                 |     |       | The Zero Flag is not effected by a RESET command.                                                                                                                                                                                                                                                                                                                                |

3-5

| г                             |   |     |                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|---|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sign Flag<br>(S)              | 5 | R/W | The Sign Flag stores the value of the most significant bit of a result following an arithmetic, logical, rotate, or shift operation.                                                                                                                                                                                                                                                                                  |

|                               |   |     | When performing arithmetic operations on signed numbers, binary two's-complement notation is used to represent and process information. A positive number is identified by a 0 in the most significant bit position (bit 7); therefore, the Sign Flag is also 0.                                                                                                                                                      |

|                               |   |     | A negative number is identified by a 1 in the most significant bit position (bit 7); therefore, the Sign Flag is also 1.                                                                                                                                                                                                                                                                                              |

|                               |   |     | The Sign Flag is not effected by RESET.                                                                                                                                                                                                                                                                                                                                                                               |

| Overflow (V)                  | 4 | R/W | For signed arithmetic, rotate, and shift operations, the Overflow Flag is set to 1 when the result is greater than the maximum possible number (>127) or less than the minimum possible number (<-128) that can be represented in two's-complement form. The Overflow Flag is cleared to 0 if no overflow occurs.                                                                                                     |

|                               |   |     | Following logical operations the Overflow Flag is cleared to 0.                                                                                                                                                                                                                                                                                                                                                       |

|                               |   |     | The Overflow Flag is not effected by RESET.                                                                                                                                                                                                                                                                                                                                                                           |

| Decimal<br>Adjust<br>Flag (D) | 3 | R/W | The Decimal Adjust Flag is used for BCD arithmetic. Since the algorithm for correcting BCD operations is different for addition and subtraction, this flag specifies what type of instruction was last executed so that the subsequent Decimal Adjust (DA) operation can function properly. Normally, the Decimal Adjust Flag cannot be used as a test condition.                                                     |

|                               |   |     | After a subtraction, the Decimal Adjust Flag is set to 1. Following an addition it is cleared to 0.                                                                                                                                                                                                                                                                                                                   |

|                               |   |     | The Decimal Adjust Flag is not effected by RESET.                                                                                                                                                                                                                                                                                                                                                                     |

| Half-<br>Carry<br>Flag (H)    | 2 | R/W | The Half Carry Flag is set to 1 whenever an addition generates a carry out of bit 3 (Overflow) or a subtraction generates a "borrow into" bit 3. The Half Carry Flag is used by the Decimal Adjust (DA) instruction to convert the binary result of a previous addition or subtraction into the correct decimal (BCD) result. As in the case of the Decimal Adjust Flag, the user does not normally access this flag. |

|                               |   |     | The Half Carry flag is not effected by RESET.                                                                                                                                                                                                                                                                                                                                                                         |

| Watch-<br>Dog<br>Timer<br>(WDT)  | 1                | R/W                                                                                                                                                                                            | The Watch-Dog Timer reset flag is set by a watchdog timer timeout. This permits software to determine if a timeout of the watchdog timer has occurred.  The WDT flag is cleared by the RESET pin. The WDT and SMR flags are the only flags effected by RESET. This behavior permits software to determine if a RESET occurred, if a WDT timeout occurred, or if a return from STOP mode occurred.  Software must explicitly clear this flag after detecting the timeout condition. |

|----------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                  |                  |                                                                                                                                                                                                | Failure to clear this flag may result in undefined behavior.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Stop<br>Mode<br>Recovery<br>Flag | Mode<br>Recovery | The Stop Mode Recovery (SMR) flag is set upon the execution of a STOP instruction. This permits software to determine if a return from stop mode has occurred upon returning to active status. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| (SMR)                            |                  |                                                                                                                                                                                                | The SMR flag is cleared by the RESET pin. The WDT and SMR flags are the only flags effected by RESET. This behavior permits software to determine if a RESET occurred, if a WDT timeout occurred, or if a return from STOP mode occurred.                                                                                                                                                                                                                                          |

|                                  |                  |                                                                                                                                                                                                | Software must explicitly clear this flag after detecting the SMR condition.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                  |                  |                                                                                                                                                                                                | Failure to clear this flag may result in undefined behavior.                                                                                                                                                                                                                                                                                                                                                                                                                       |

## **CONDITION CODES**

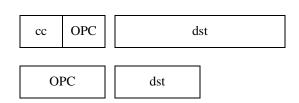

The C, Z, S, and V Flags control the operation of the conditional JUMP instructions. Sixteen frequently useful functions of the flag settings are encoded in a 4-bit field called the condition code (cc), which forms bits 4-7 of the conditional instructions.

Flag Definitions, Flag Settings and Condition Codes are summarized in Table 3-9, Table 3-10, and Table 3-11.

Table 3-9. Flag Definitions

| Flag | Description   |

|------|---------------|

| С    | Carry Flag    |

| Z    | Zero Flag     |

| S    | Sign Flag     |

| V    | Overflow Flag |

**Table 3-10. Flag Settings Definitions**

| Symbol | Definition                            |

|--------|---------------------------------------|

| 0      | Cleared to 0                          |

| 1      | Set to 1                              |

| *      | Set or cleared according to operation |

| _      | Unaffected                            |

| X      | Undefined                             |

**Table 3-11. Condition Codes**

| Binary | HEX | Mnemonic | Definition   | Flag Settings |

|--------|-----|----------|--------------|---------------|

| 0000   | 0   | F        | Always False | _             |

| 1000   | 8   | (blank)  | Always True  | _             |

| 0111   | 7   | С        | Carry        | C = 1         |

| 1111   | F   | NC       | No Carry     | C = 0         |

| 0110   | 6   | Z        | Zero         | Z = 1         |

| 1110   | Е   | NZ       | Non-Zero     | Z = 0         |

| 1101   | D   | PL       | Plus         | S = 0         |

| 0101   | 5   | Ml       | Minus        | S = 1         |

| 0100   | 4   | OV       | Overflow     | V = 1         |

| 1100   | С   | NOV      | No Overflow  | V = 0         |

**Table 3-11. Condition Codes (Continued)**

| Binary | HEX | Mnemonic | Definition                     | Flag Settings           |

|--------|-----|----------|--------------------------------|-------------------------|

| 0110   | 6   | EQ       | Equal                          | Z = 1                   |

| 1110   | Е   | NE       | Not Equal                      | Z = 0                   |

| 1001   | 9   | GE       | Greater Than or Equal          | (S XOR V) = 0           |

| 0001   | 1   | LT       | Less Than                      | (S XOR V) = 1           |

| 1010   | A   | GT       | Greater Than                   | (Z OR (S XOR V)) = 0    |

| 0010   | 2   | LE       | Less Than or Equal             | (Z OR (S XOR V)) = 1    |

| 1111   | F   | UGE      | Unsigned Greater Than or Equal | C = 0                   |

| 0111   | 7   | ULT      | Unsigned Less Than             | C = 1                   |

| 1011   | В   | UGT      | Unsigned Greater Than          | (C = 0  AND  Z = 0) = 1 |

| 0011   | 3   | ULE      | Unsigned Less Than or Equal    | (C OR Z) = 1            |

UM001000-Z8X0199 3-9

## **NOTATION AND BINARY ENCODING**

The operands and status flags use a notational shorthand. Operands, condition codes, address modes, and their notations are described in Table 3-12.

**Table 3-12. Notational Shorthand**

| Notation | Address Mode                                          | Operand      | Range*                                                                                                                     |

|----------|-------------------------------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------|

| сс       | Condition Code                                        |              | See Table 3-11, condition codes                                                                                            |

| r        | Working Register                                      | Rn           | n = 0 - 15                                                                                                                 |

| R        | Register<br>or<br>Working Register                    | Reg<br>Rn    | Reg. represents a number in the range of 00H to FFH $n = 0 - 15$                                                           |

| RR       | Indirect Register Pair or Working Register Pair       | Reg<br>RRp   | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                           |

| Ir       | Indirect Working Register                             | @Rn          | n = 0 -15                                                                                                                  |

| IR       | Indirect Register<br>or<br>Indirect Working Register  | @Reg<br>@Rn  | Reg. represents a number in the range of 00H to FFH $n = 0-15$                                                             |

| Irr      | Indirect Working Register<br>Pair                     | @RRp         | p = 0, 2, 4, 6, 8, 10, 12, or 14                                                                                           |

| IRR      | Indirect Register Pair<br>or<br>Working Register Pair | @Reg<br>@RRp | Reg. represents an even number in the range 00H to FFH p=0, 2, 4, 6, 8, 10, 12, or 14                                      |

| X        | Indexed                                               | Reg (Rn)     | Reg. represents a number in the range of 00H to FFH $n = 0 - 15$                                                           |

| DA       | Direct Address                                        | Addrs        | Addrs. represents a number in the range of 0000H to FFFFH                                                                  |

| RA       | Relative Address                                      | Addrs        | Addrs. represents a number in the range of +127 to -128 which is an offset relative to the address of the next instruction |

| IM       | Immediate                                             | #Data        | Data is a number between 00H to FFH                                                                                        |

<sup>\*</sup>See the device product specification to determine the exact register file range available. The register file size varies by the device type.

Table 3-13, which follows, describes additional symbols used.

**Table 3-13. Additional Symbols**

| Symbol | Definition                    |

|--------|-------------------------------|

| dst    | Destination Operand           |

| src    | Source Operand                |

| @      | Indirect Address Prefix       |

| SP     | Stack Pointer                 |

| PC     | Program Counter               |

| FLAGS  | Flag Register (FCH)           |

| RP     | Register Pointer (FDH)        |

| IMR    | Interrupt Mask Register (FBH) |

| #      | Immediate Operand Prefix      |

| %      | Hexadecimal Number Prefix     |

| Н      | Hexadecimal Number Suffix     |

| В      | Binary Number Suffix          |

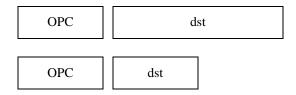

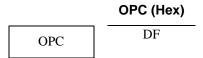

| OPC    | op code                       |

Assignment of a value is indicated by the symbol  $\leftarrow$ , for example:

$$dst \leftarrow dst + src$$

indicates the source data is added to the destination data and the result is stored in the destination location.

The notation addr(n) is used to refer to bit 'n' of a given location. The following example refers to bit 7 of the destination operand.

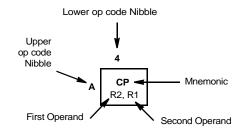

Some instructions operate with several addressing modes. This situation is indicated by an op code number written like x[ ]. The brackets are filled by a nibble indicating the addressing mode in use. For example, ADD 0[] indicates that the ADD instruction works identically for more than one addressing mode.

# **Assembly Language Syntax**

For proper instruction execution, assembly language syntax requires that the destination and source be specified as dst, src (in that order). The following instruction descriptions show the format of the object code produced by the assembler. This binary format should be followed by users who prefer manual program coding or who intend to implement their own assembler. Other third party assemblers can differ. Please consult the software user's manual for detailed information.

**Example**: The contents of registers 43H and 08H are added, and the result is stored in 43H. The assembly syntax and resulting object code are:

| ASM: | ADD | 43H, | 08H | (ADD dst, src) |

|------|-----|------|-----|----------------|

| OBJ: | 04  | 08   | 43  | (OPC src, dst) |

In general, whenever an instruction format requires an 8-bit register address, that address can specify any register location in the range 0 - 255. When using working registers (R0-R15), a 4-bit address is used. If a working register is used and an 8-bit address is required by the assembler, an E is pre-pended to the 4-bit working register address. If, in the above example, the source register is a working register, the assembly syntax and resulting object code are:

| ASM: | ADD | 43H, | R8 | (ADD dst, src) |

|------|-----|------|----|----------------|

| OBJ: | 04  | E8   | 43 | (OPC src, dst) |

#### **NOTES:**

- 1. Note that the 4-bit address R8 was expanded to 8-bits by pre-pending EH. This expansion occurs any time a 4-bit address isspecified for an instruction that takes 8-bit operands.

- 2. See the device product specification to determine the exact register file range available. The register file size varies by device type

# **Z8PLUS INSTRUCTION SUMMARY**

The instructions marked with this symbol (†) have an identical set of addressing modes, which are encoded for brevity. The upper nibble is described in Table 3-14, and the lower nibble is represented by []. The second nibble's value is described in Table 3-15, and is found beside the applicable addressing mode pair. For example, the op code of an ADC instruction using the addressing modes r (destination) and r (source) is 13H.

**Table 3-14. Instruction Summary**

|                                                                                         |          | ress<br>ode | op code    | Flags Affecte |   |   | ed . |   |   |

|-----------------------------------------------------------------------------------------|----------|-------------|------------|---------------|---|---|------|---|---|

| Instruction and Operation                                                               | dst      | src         | Byte (Hex) | С             | Z | S | ٧    | D | Н |

| <b>ADC</b> dst, src dst $\leftarrow$ dst + src +C                                       | †        |             | 1[]        | *             | * | * | *    | 0 | * |

| <b>ADD</b> dst, src dst $\leftarrow$ dst + src                                          | †        |             | 0[ ]       | *             | * | * | *    | 0 | * |

| AND dst, src<br>dst ← dst AND src                                                       | †        |             | 5[ ]       | -             | * | * | 0    | - | _ |

| CALL src<br>$SP \leftarrow SP - 2$<br>$PC \leftarrow src$                               |          | DA          | D6         | -             | _ | _ | _    | _ | ı |

| CALL src<br>$SP \leftarrow SP - 2$<br>$PC \leftarrow @src$                              |          | IRR         | D4         | -             | - | - | -    | _ | ı |

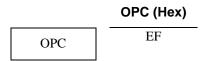

| CCF<br>C ←NOT C                                                                         |          |             | EF         | *             | _ | - | -    | _ | - |

| CLR dst $dst \leftarrow 0$                                                              | R<br>IR  |             | B0<br>B1   | -             | - | _ | -    | _ | - |

| $\begin{array}{l} \textbf{COM dst} \\ \text{dst} \leftarrow \text{NOT dst} \end{array}$ | R<br>IR  |             | 60<br>61   | -             | * | * | 0    | - | - |

| CP dst, src<br>dst – src                                                                | †        |             | A[ ]       | *             | * | * | *    | _ | - |

| $\mathbf{DA}$ dst dst $\leftarrow$ DA dst                                               | R<br>IR  |             | 40<br>41   | *             | * | * | -    | - | _ |

| <b>DEC</b> dst dst $\leftarrow$ dst $-1$                                                | R<br>IR  |             | 00<br>01   | -             | * | * | *    | - | _ |

| <b>DECW</b> dst dst $\leftarrow$ dst $-1$                                               | RR<br>IR |             | 80<br>81   | -             | * | * | *    | _ | - |

**Table 3-14. Instruction Summary (Continued)**

| In administration and I Own water                                                                                                                | Addres       | s Mode | op code                       |   |   |   | d |   |   |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|-------------------------------|---|---|---|---|---|---|--|

| Instruction and Operation                                                                                                                        | dst          | src    | Byte (Hex)                    | С | Z | S | V | D | Н |  |

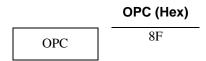

| $\mathbf{DI}$ $IMR(7) \leftarrow 0$                                                                                                              |              |        | 8F                            | _ | _ | - | _ | _ |   |  |

| <b>DJNZ</b> , dst, src r RA<br>dst $\leftarrow$ dst - 1<br>if dst $\neq$ 0<br>then PC $\leftarrow$ PC + src<br>Range: -128 $\leq$ src $\leq$ 127 | RA           |        | $rA \\ (r = 0 - F)$           | _ | _ | _ | _ | _ | _ |  |

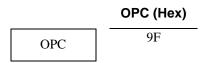

| EI IMR(7) $\leftarrow$ 1                                                                                                                         |              |        | 9F                            | _ | _ | - | _ | _ | _ |  |

| HALT                                                                                                                                             |              |        | 7F                            | _ | _ | _ | _ | _ | _ |  |

| <b>INC</b> dst dst $\leftarrow$ dst + 1                                                                                                          | r<br>R<br>IR |        | rE<br>(r = 0 - F)<br>20<br>21 | _ | * | * | * | - | _ |  |

| <b>INCW</b> dst dst $\leftarrow$ dst + 1                                                                                                         | RR<br>IR     |        | A0<br>A1                      | _ | * | * | * |   | _ |  |

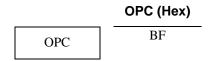

| IRET<br>FLAGS $\leftarrow$ @SP;<br>SP $\leftarrow$ SP + 1<br>PC $\leftarrow$ @SP;<br>SP $\leftarrow$ SP + 2;<br>IMR(7) $\leftarrow$ 1            |              |        | BF                            | * | * | * | * | * | * |  |

| JP cc, src<br>if cc is true,<br>then PC ← src                                                                                                    |              | DA     | $ccD \\ (cc = 0 - F)$         | - | - | _ | - | - | _ |  |

| JP src<br>PC ← @src                                                                                                                              |              | IRR    | 30                            | - | - | _ | - | _ | - |  |

| JR cc, src<br>if cc is true,<br>then PC $\leftarrow$ PC + src<br>Range: $-128 \le \text{src} \le 127$                                            |              | RA     | $ccB \\ c = 0 - F$            | _ | _ | _ | _ | _ | _ |  |

**Table 3-14. Instruction Summary (Continued)**

| In admirable in an il Americal | Addres | s Mode | op code     |   |   |   |   |   |   |  |

|--------------------------------|--------|--------|-------------|---|---|---|---|---|---|--|

| Instruction and Operation      | dst    | src    | Byte (Hex)  | С | Z | S | V | D | Н |  |

| LD dst, src                    | r      | Im     | r C         | _ | _ | _ | _ | _ | - |  |

| $dst \leftarrow src$           | r      | R      | r 8         |   |   |   |   |   |   |  |

|                                | R      | r      | r 9         |   |   |   |   |   |   |  |

|                                |        |        | (r = 0 - F) |   |   |   |   |   |   |  |

|                                | r      | X      | C7          |   |   |   |   |   |   |  |

|                                | X      | r      | D7          |   |   |   |   |   |   |  |

|                                | r      | Ir     | E3          |   |   |   |   |   |   |  |

|                                | Ir     | r      | F3          |   |   |   |   |   |   |  |

|                                | R      | R      | E4          |   |   |   |   |   |   |  |

|                                | R      | IR     | E5          |   |   |   |   |   |   |  |

|                                | R      | IM     | E6          |   |   |   |   |   |   |  |

|                                | IR     | IM     | E7          |   |   |   |   |   |   |  |

|                                | IR     | R      | F5          |   |   |   |   |   |   |  |

| LDC dst, src                   | r      | Irr    | C2          | _ | _ | _ | _ | _ | _ |  |

| $dst \leftarrow src$           | lrr    | r      | D2          |   |   |   |   |   |   |  |

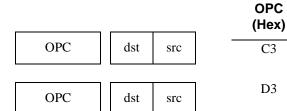

| LDCI dst, src                  | Ir     | Irr    | C3          | _ | _ | _ | _ | _ | _ |  |

| $@dst \leftarrow @src$         | lrr    | r      | D3          |   |   |   |   |   |   |  |

| $dst \leftarrow dst + 1$       |        |        |             |   |   |   |   |   |   |  |

| $src \leftarrow src + 1$       |        |        |             |   |   |   |   |   |   |  |

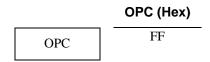

| NOP                            |        |        | FF          | _ | _ | _ | _ | _ | _ |  |

| OR dst, src                    | †      |        | 4[]         | _ | * | * | 0 | _ | _ |  |

| $dst \leftarrow dst OR src$    |        |        |             |   |   |   |   |   |   |  |

| POP dst                        | R      |        | 50          | _ | _ | _ | _ | _ | _ |  |

| dst ← @SP                      | IR     |        | 51          |   |   |   |   |   |   |  |

| $SP \leftarrow SP + 1$         |        |        |             |   |   |   |   |   |   |  |

| PUSH src                       | R      |        | 70          | _ |   | _ |   |   | _ |  |

| $SP \leftarrow SP - 1$         | IR     |        | 71          |   |   |   |   |   |   |  |

| $@SP \leftarrow src$           |        |        | , 1         |   |   |   |   |   |   |  |

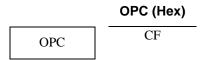

| RCF                            |        |        | CE          | 0 |   |   |   |   |   |  |

|                                |        |        | CF          | 0 | _ | _ | _ | _ | _ |  |

| C ← 0                          |        |        |             |   |   |   |   |   |   |  |

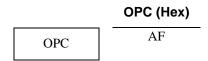

| RET                            |        |        | AF          | _ | _ | _ | _ | _ | _ |  |

| $PC \leftarrow @SP;$           |        |        |             |   |   |   |   |   |   |  |

| $SP \leftarrow SP + 2$         |        |        |             |   |   |   |   |   |   |  |

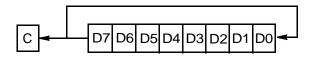

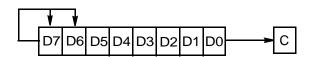

| RL dst                         | R      |        | 90          | * | * | * | * | _ | _ |  |

| C 7 04                         | IR     |        | 91          |   |   |   |   |   |   |  |

| <u>[C ◆+[7 0]◆-</u>            |        |        |             |   |   |   |   |   |   |  |

**Table 3-14. Instruction Summary (Continued)**

|                                                  | Addres  | s Mode | op code    | Flags Affected |   |   |   |   |   |  |

|--------------------------------------------------|---------|--------|------------|----------------|---|---|---|---|---|--|

| Instruction and Operation                        | dst     | src    | Byte (Hex) | С              | Z | S | V | D | Н |  |

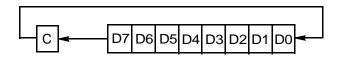

| RLC dst                                          | R<br>IR |        | 10<br>11   | *              | * | * | * | _ | _ |  |

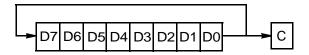

| RR dst  →C→7 0                                   | R<br>IR |        | E0<br>E1   | *              | * | * | * | _ | _ |  |

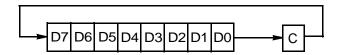

| <b>RRC</b> dst                                   | R<br>IR |        | C0<br>C1   | *              | * | * | * | _ | _ |  |

| <b>SBC</b> dst, src<br>dst ← dst – src –<br>C    | Ť       |        | 3[]        | *              | * | * | * | 1 | * |  |

| <b>SCF</b> C ← 1                                 |         |        | DF         | 1              | - | - | _ | _ | _ |  |

| <b>SRA</b> dst                                   | R<br>IR |        | D0<br>D1   | *              | * | * | 0 | - | _ |  |

| SRP src<br>RP ← src                              | Im      |        | 31         | -              | - | - | - |   | _ |  |

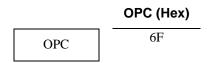

| STOP                                             |         |        | 6F         | _              | _ | _ | _ | _ | _ |  |

| <b>SUB</b> dst, src dst $\leftarrow$ dst $-$ src | †       |        | 2[ ]       | *              | * | * | * | 1 | * |  |

| SWAP dst    7                                    | R<br>IR |        | F0<br>F1   | -              | * | * | - | - | _ |  |

| TCM dst, src<br>(NOT dst) AND src                | †       |        | 6[]        | _              | * | * | 0 | _ | _ |  |

| TM dst, src<br>dst AND src                       | †       |        | 7[]        | -              | * | * | 0 | _ | - |  |

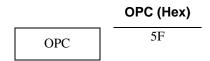

| WDT                                              |         |        | 5F         | -              | - | _ | _ | _ | _ |  |

| <b>XOR</b> dst, src dst $\leftarrow$ dst XOR src | †       |        | 7[]        | -              | * | * | 0 | _ | - |  |

**Table 3-15. Lower Nibble Values**

| Addres<br>dst | s Mode<br>src | Lower<br>op code Nibble |

|---------------|---------------|-------------------------|

| r             | r             | [2]                     |

| r             | Ir            | [3]                     |

| R             | R             | [4]                     |

| R             | IR            | [5]                     |

| R             | IM            | [6]                     |

| IR            | IM            | [7]                     |

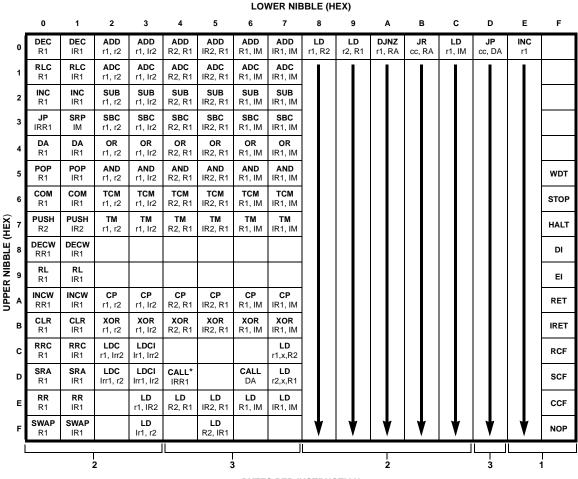

Figure 3-2, which follows, illustrates the Op Code map.

UM001000-Z8X0199 3-17

### OP CODE MAP

#### BYTES PER INSTRUCTION

#### Notes: