### XRD66092

CMOS 750 KSPS, 12-Bit Analog-to-Digital Converter with Serial Logic Interface Port

FEATURES April 1996-1

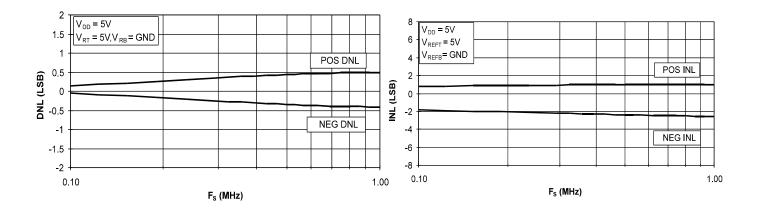

• 12-Bit Monotonic ADC with DNL = ±1 LSB, INL = ±2.5 LSB

• SNR > 66 dB

• Sampling Frequency ≤ 750 kHz

Internal Track and Hold

Single 5 V Supply

Rail-to-Rail Input Range

V<sub>REF</sub> Range: 1.5 V to V<sub>DD</sub>

CMOS Low Power: 175 mW (typ)

• Binary and Two's Complement Digital Output Mode

Serial Port

• ESD: 2000 V Minimum

- Underflow and Overflow Outputs

- Precision Aperture Output

- 6 Reference Resistor Taps

- Latch-Up Free

#### **APPLICATIONS**

- Control Systems

- Instrumentation

- DAS

- Sonar

- Digital Radio

#### **GENERAL DESCRIPTION**

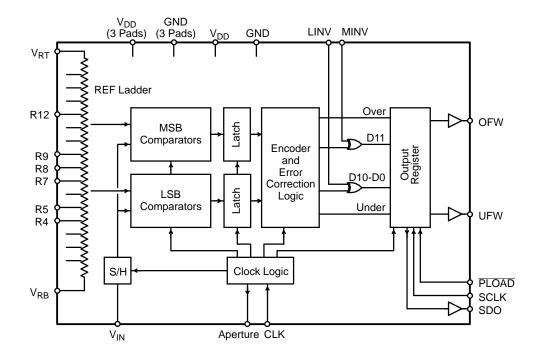

The XRD66092 is a 12-bit 750 kHz subranging Analog-to-Digital Converter with an internal track and hold.

The XRD66092 operates with a single supply ranging from +3 V to +5 V while consuming less than 175 mW of power (typical).

Separate pins for  $V_{RT}$  and  $V_{RB}$  allow flexibility for analog input  $(V_{IN})$  and the reference voltage range  $(\Delta V_{REF})$ .

Data is presented at the serial output port every clock cycle with a 2.5 cycle pipeline delay. LINV and MINV enable binary and 2's complement data formatting. 6 ladder tap pins provide for transfer function adjustment.

#### SIMPLIFIED BLOCK DIAGRAM

#### ORDERING INFORMATION

| Package<br>Type | Temperature<br>Range | Part No.    | DNL<br>(LSB) | INL<br>(LSB) |

|-----------------|----------------------|-------------|--------------|--------------|

| PDIP            | −40 to +85°C         | XRD66092AIP | ±1           | 2 1/2        |

| SOIC            | −40 to +85°C         | XRD66092AID | ±1           | 2 1/2        |

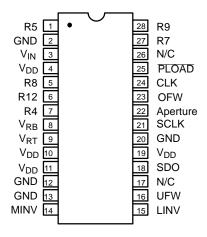

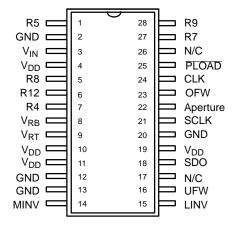

#### **PIN CONFIGURATIONS**

See Packaging Section for Package Dimensions

28 Pin PDIP (0.600")

28 Pin SOIC (Jedec, 0.300)

#### **PIN OUT DEFINITIONS**

| PIN NO. | NAME     | DESCRIPTION                                       |  |  |

|---------|----------|---------------------------------------------------|--|--|

| 1       | R5       | Ref. Resistor Ladder Tap (5/16 V <sub>REF</sub> ) |  |  |

| 2       | GND      | Analog Ground (Substrate)                         |  |  |

| 3       | $V_{IN}$ | Analog Input                                      |  |  |

| 4       | $V_{DD}$ | Analog Positive Supply                            |  |  |

| 5       | R8       | Ref. Resistor Ladder Tap (1/2 V <sub>REF</sub> )  |  |  |

| 6       | R12      | Ref. Resistor Ladder Tap (3/4 V <sub>REF</sub> )  |  |  |

| 7       | R4       | Ref. Resistor Ladder Tap (1/4 V <sub>REF</sub> )  |  |  |

| 8       | $V_{RB}$ | Negative Reference                                |  |  |

| 9       | $V_{RT}$ | Positive Reference                                |  |  |

| 10      | $V_{DD}$ | Analog Positive Supply                            |  |  |

| 11      | $V_{DD}$ | Analog Positive Supply                            |  |  |

| 12      | GND      | Analog Ground (Substrate)                         |  |  |

| 13      | GND      | Analog Ground (Substrate)                         |  |  |

| 14      | MINV     | Invert MSB (Active High)                          |  |  |

|         |          |                                                   |  |  |

| PIN NO. | NAME     | DESCRIPTION                                       |  |  |  |

|---------|----------|---------------------------------------------------|--|--|--|

| 15      | LINV     | Invert LSB (Active High)                          |  |  |  |

| 16      | UFW      | Underflow Bit                                     |  |  |  |

| 17      | N/C      | No Connection                                     |  |  |  |

| 18      | SDO      | Serial Data Out                                   |  |  |  |

| 19      | $V_{DD}$ | Digital Positive Supply                           |  |  |  |

| 20      | GND      | Digital Ground (Substrate)                        |  |  |  |

| 21      | SCLK     | Serial Clock                                      |  |  |  |

| 22      | Aperture | Aperture Delay Sync                               |  |  |  |

| 23      | OFW      | Overflow Bit                                      |  |  |  |

| 24      | CLK      | Clock                                             |  |  |  |

| 25      | PLOAD    | Serial Shift Register Data Load                   |  |  |  |

| 26      | N/C      | No Connection                                     |  |  |  |

| 27      | R7       | Ref. Resistor Ladder Tap (7/16 V <sub>REF</sub> ) |  |  |  |

| 28      | R9       | Ref. Resistor Ladder Tap (9/16 V <sub>REF</sub> ) |  |  |  |

#### **ELECTRICAL CHARACTERISTICS TABLE**

Unless Otherwise Specified: V<sub>DD</sub> = 5 V, FS = 750 kHz (50% Duty Cycle), V<sub>REF(+)</sub> = 5.0 V, V<sub>REF(-)</sub> = GND, TA = 25°C, V<sub>IN</sub> Connected through 39 $\Omega$

| 25°C                                                                                                                                                            |                                                                   |                     |                                                  |                            |                                |                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|---------------------|--------------------------------------------------|----------------------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                                                                                                                                       | Symbol                                                            | Min                 | Тур                                              | Max                        | Units                          | Test Conditions/Comments                                                                                                            |

| KEY FEATURES                                                                                                                                                    |                                                                   |                     |                                                  |                            |                                |                                                                                                                                     |

| Resolution<br>Sampling Rate                                                                                                                                     | FS                                                                | 12                  |                                                  | 750                        | Bits<br>kHz                    |                                                                                                                                     |

| ACCURACY1                                                                                                                                                       |                                                                   |                     |                                                  |                            |                                |                                                                                                                                     |

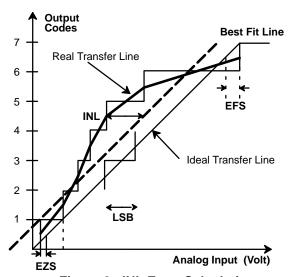

| Differential Non-Linearity Integral Non-Linearity (See NO TAG) Zero Scale Error Full Scale Error                                                                | DNL<br>INL<br>EZS<br>EFS                                          |                     | ±1/2<br>±2<br>+10<br>-10                         | <u>±</u> 1<br><u>+</u> 2.5 | LSB<br>LSB<br>LSB<br>LSB       | Best Fit Line<br>(Max INL – Min INL)/2                                                                                              |

| REFERENCE VOLTAGES                                                                                                                                              | LIS                                                               |                     | -10                                              |                            | LOB                            |                                                                                                                                     |

| Positive Ref. Voltage Negative Ref. Voltage Differential Ref. Voltage <sup>3</sup>                                                                              | V <sub>RT</sub><br>V <sub>RB</sub><br>V <sub>REF</sub>            | 1.5<br>GND<br>1.5   |                                                  | V <sub>DD</sub>            | V<br>V<br>V                    | 4.5 to 5 V is recommended for specified performance, $V_{REF(+)} - V_{REF(-)}$                                                      |

| Ladder Resistance                                                                                                                                               | $R_{L}$                                                           |                     | 550                                              |                            | Ω                              | REF(T) REF(T)                                                                                                                       |

| ANALOG INPUT                                                                                                                                                    |                                                                   |                     |                                                  |                            |                                |                                                                                                                                     |

| Input Bandwidth (–3 dB) <sup>4</sup> Input Voltage Range Input Capacitance Sample <sup>5</sup> Input Capacitance Convert <sup>5</sup> Aperture Delay from Clock | BW<br>V <sub>IN</sub><br>C <sub>IN</sub>                          | V <sub>REF(-)</sub> | 10<br>50<br>8<br>20                              | V <sub>REF(+)</sub>        | MHz<br>V p-p<br>pF<br>pF<br>ns |                                                                                                                                     |

| DIGITAL INPUTS                                                                                                                                                  |                                                                   |                     |                                                  |                            |                                |                                                                                                                                     |

| Logical "1" Voltage<br>Logical "0" Voltage<br>Leakage Currents <sup>6</sup><br>CLK, MINV, LINV, SCLK,                                                           | V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IN</sub>             |                     | 2.4 0.8                                          |                            | V<br>V                         | V <sub>IN</sub> =GND to V <sub>DD</sub>                                                                                             |

| PLOAD Input Capacitance Clock Timing                                                                                                                            |                                                                   |                     | 10<br>5                                          |                            | μA<br>pF                       |                                                                                                                                     |

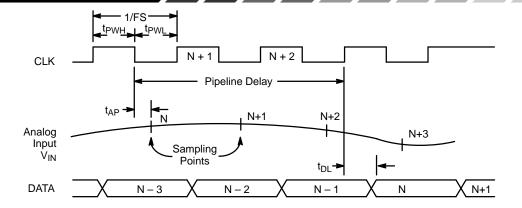

| Clock Period Rise & Fall Time <sup>7</sup> "High" Time "Low" Time Duty Cycle Serial Register Timing                                                             | t <sub>R</sub> , t <sub>F</sub> t <sub>PWH</sub> t <sub>PWL</sub> | 1.33<br>665<br>665  | 15<br>50                                         |                            | μs<br>ns<br>ns<br>ns<br>%      | 1/FS                                                                                                                                |

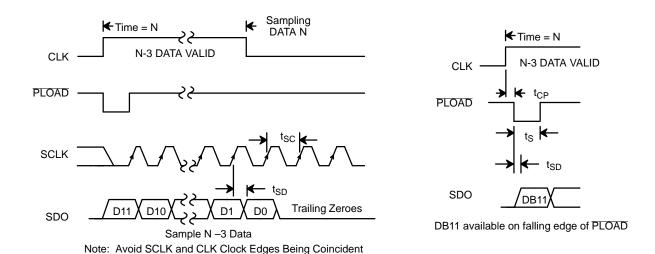

| Shift Clock Period Shift Clock to Data Delay Minimum Pulse Width PLOAD Clock↑ to PLOAD↓ For Valid D11                                                           | tsc<br>tsp<br>ts<br>t <sub>CP</sub>                               | 110                 | 20<br>50<br>0                                    |                            | ns<br>ns<br>ns<br>ns           |                                                                                                                                     |

| DIGITAL OUTPUTS                                                                                                                                                 |                                                                   |                     |                                                  |                            |                                | C <sub>OUT</sub> =15 pF                                                                                                             |

| Logical "1" Voltage<br>Logical "1" Source Current<br>Logical "0" Voltage<br>Logical "0" Sink Current<br>Tristate Leakage<br>Data Valid Delay                    | VOH<br>IOH<br>VOL<br>IOL<br>IOZ<br>tDL                            |                     | V <sub>DD</sub> -0.5<br>4<br>0.5<br>4<br>1<br>30 |                            | V<br>mA<br>V<br>mA<br>μA<br>ns | $I_{LOAD} = 4 \text{ mA}$ $V_{OH} = V_{DD}-0.5$ $I_{LOAD} = 4 \text{ mA}$ $V_{OL} = 0.5 \text{ V}$ $V_{OUT}=GND \text{ to } V_{DD}$ |

#### **ELECTRICAL CHARACTERISTICS TABLE (CONT'D)**

|                                                                    |                                    |     | 25°C    |     |         |                                 |

|--------------------------------------------------------------------|------------------------------------|-----|---------|-----|---------|---------------------------------|

| Parameter                                                          | Symbol                             | Min | Тур     | Max | Units   | Test Conditions/Comments        |

| POWER SUPPLIES <sup>8</sup>                                        |                                    |     |         |     |         |                                 |

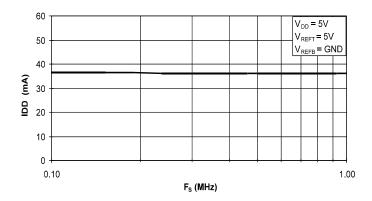

| Operating Voltage (V <sub>DD</sub> )<br>Current (V <sub>DD</sub> ) | V <sub>DD</sub><br>I <sub>DD</sub> |     | 5<br>35 | 45  | V<br>mA |                                 |

| AC PARAMETERS Signal Noise Ratio                                   | SNR                                | 66  |         |     | dB      | V <sub>IN</sub> = 5 Vp-p, 1 kHz |

#### **NOTES**

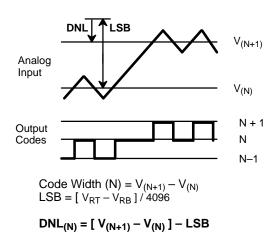

- Tester measures code transitions by dithering the voltage of the analog input (V<sub>IN</sub>). The difference between the measured and the ideal code width (V<sub>REF</sub>/4096) is the DNL error. The INL error is the maximum distance (in LSBs) from the best fit line to any transition voltage. Accuracy is a function of the sampling rate (FS).

- 2 Guaranteed. Not tested.

- Specified values guarantee functionality. Refer to other parameters for accuracy.

- 4 –3 dB bandwidth is a measure of performance of the A/D input stage (S/H amplifier). Refer to other parameters for accuracy within the specified bandwidth.

- <sup>5</sup> A 39Ω resistor should be put in series with V<sub>IN</sub> to dampen transients associated with inductive output impedance of typical op amps.

- <sup>6</sup> All inputs have diodes to V<sub>DD</sub> and GND. Input(s) MINV and LINV have internal pull down(s). Input DC currents will not exceed specified limits for any input voltage between GND and V<sub>DD</sub>.

- Condition to meet aperture delay specifications (t<sub>AP</sub>, t<sub>AJ</sub>). Actual rise/fall time can be less stringent with no loss of accuracy.

- 8 GND pins are internally connected through the silicon substrate.

Specifications are subject to change without notice

#### ABSOLUTE MAXIMUM RATINGS (TA = +25°C unless otherwise noted)<sup>1, 2, 3</sup>

| V <sub>DD</sub> to GND 7 V                      | Storage Temperature –65 to +150°C                  |

|-------------------------------------------------|----------------------------------------------------|

| $V_{RT}$ & $V_{RB}$ $V_{DD}$ +0.5 to GND –0.5 V | Lead Temperature (Soldering 10 seconds) +300°C     |

| All Inputs                                      | Package Power Dissipation Rating @ 75°C PDIP. SOIC |

| Digital Outputs $V_{DD}$ +0.5 to GND –0.5 V     | Derates above 75°C14mW/°C                          |

|                                                 |                                                    |

#### NOTES:

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation at or above this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

Any input pin which can see a value outside the absolute maximum ratings should be protected by Schottky diode clamps (HP5082-2835) from input pin to the supplies. *All inputs have protection diodes* which will protect the device from short transients outside the supplies of less than 100mA for less than 100µs.

3 GND refers to AGND and DGND.

Figure 1. XRD66092 Timing Diagram

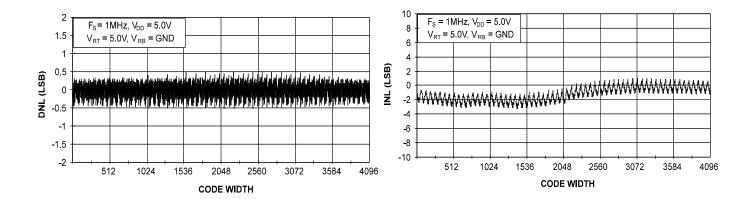

Figure 2. DNL Measurement

#### **UFW: Underflow (Output)**

This signal indicates when the Analog Input ( $V_{IN}$ ) goes below the  $V_{RB}$  range, and is normally at a low logic level. When  $V_{IN} < V_{RB}$ , UFW will go high and the data bits will show negative full scale (i.e. all 0's if MINV & LINV are low).

#### **OFW: Underflow (Output)**

This signal indicates when the Analog Input ( $V_{IN}$ ) goes above the  $V_{RB}$  range, and is normally at a low logic level. When  $V_{IN} > V_{RB}$ , OFW will go high and the data bits will show positive full scale (i.e. all 0's if MINV & LINV are low).

#### **SDO: Serial Data output**

After the internal shift register is updated using the PLOAD signal, the SDO pin outputs the A/D result starting with the MSB

Figure 3. INL Error Calculation

(which appears just after the  $\overline{\text{PLOAD}}$  strobe). Each bit is output on the rising edge of SCLK.

#### **SCLK: Serial Data Port Clock**

The SCLK controls the output of the serial port through SDO. SDO is updated on every rising edge of SCLK. The  $\overline{\text{PLOAD}}$  signal will override the SCLK signal.

#### **PLOAD**:

Serial data port shift register load: When  $\overline{\text{PLOAD}}$  is low (i.e. level triggered not edge triggered) the current parallel data will be loaded into the shift register.  $\overline{\text{PLOAD}}$  overrides SCLK. When  $\overline{\text{PLOAD}}$  is high, the data can be shifted out through the SDO pin with SCLK.

Figure 4. Serial Port Timing Chart

#### **APERTURE: Aperture Delay Sync (output)**

This signal is high when the internal sample/hold function is sampling  $V_{\text{IN}}$ , and goes low when it is in the hold mode (when the ADC is comparing the stored input value to the reference lad-

der). The value of  $V_{\text{IN}}$  at the high to low transition of APERTURE is the value that will be digitized. A system can monitor this signal and adjust the CLK phase to accurately synchronize the sampling point to an external event.

| MINV<br>LINV                                                                | 0 0                                                                        | 0<br>1                                         | 1<br>0                                         | 1 1                                        |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|--------------------------------------------|

| V <sub>RT</sub> ' ' ' ' ' V <sub>IN</sub> mid scale ' ' ' ' V <sub>RB</sub> | 111 11<br>111 10<br><br>100 01<br>100 00<br>011 11<br><br>000 01<br>000 01 | 100 00<br>100 01<br>111 10<br>111 11<br>000 00 | 011 11<br>011 10<br>000 01<br>000 00<br>111 11 | 000 00<br>000 01<br>10<br>011 11<br>100 00 |

|                                                                             | binary                                                                     | inverted<br>2's complement                     | 2's complement                                 | inverted<br>binary                         |

**Table 1. Output Data Format Truth Table**

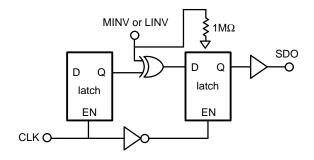

#### MINV & LINV: Digital Output Format (inputs)

These signals control the format of the digital output data bits DB0 – DB11. Normally both pins are held low so the data is in straight binary format (all 0's when  $V_{IN}=V_{RB}$ ; all 1's when  $V_{IN}=V_{RT}$ ). If MINV is pulled high then the MSB (DB11) will be inverted. If LINV is pulled high then the LSBs (DB0 – DB10) will

be inverted. The OFW and UFW bits are not affected by these signals.

MINV & LINV are meant to be static digital signals. If they are to change during operation they should only change when the CLK is low. Changing MINV and/or LINV when CLK is high is acceptable, but the effects on the digital outputs will not be seen until the output latch of the output register is enabled. MINV and

LINV have internal pull down devices. Please see the simplified logic circuit *Figure 5*.

Figure 5. MINV, LINV Simplified Logic Circuit

#### **VIN Analog Input**

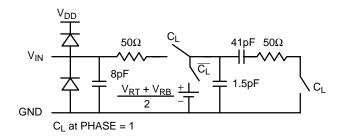

The XRD66L92 has a switched capacitor track and hold input stage.  $V_{IN}$  is sampled at the high to low clock transition. The *Figure 6.* shows the equivalent input circuit.

Figure 6. Equivalent Input Circuit

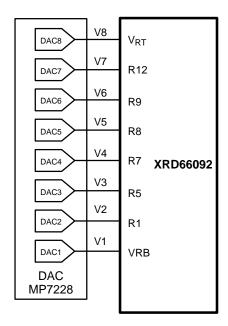

#### **Reference Ladder Taps**

These taps connect to every sixteenth point along the reference ladder; R4 is 4/16th up from  $V_{RB}$ , R7 is 7/16ths up from  $V_{RB}$ . These taps can be used to alter the transfer curve of the ADC. The internal interconnect resistance from the pin to the ladder is less than  $3\Omega$  for the even numbered taps, (i.e. R4,R6, etc.) and is approximately  $10\Omega$  for the odd numbered taps.

Altering the transfer curve may be desirable to enhance or reduce the probability of codes for certain ranges of  $V_{\text{IN}}$ . This is often referred to as probability density function shaping, or histogram shaping. 0.8 V maximum per tap is recommended for ap-

plications above  $85^{\circ}$ C. Up to 1.6 V is allowed for applications under  $85^{\circ}$ C.

#### **APPLICATION NOTES**

$V_{IN}$  signals should not exceed  $V_{DD}$  +0.5V or go below GND -0.5V. All pins have internal protection diodes that will protect them from short transients (<100 $\mu$ s) outside the supply range.

All GND pins are connected internally through the P– substrate. DC voltage differences between any GND pins will cause undesirable internal substrate currents.

The power supply ( $V_{DD}$ ) and reference voltage ( $V_{RT}$  &  $V_{RB}$ ) pins should be decoupled with  $0.1\mu F$  and  $10\mu F$  capacitors to GND, placed as close to the chip as possible.

The digital outputs should not drive long wires or buses. The capacitive coupling and reflections will contribute noise to the conversion.

The reference tap pins can be used to create piecewise-linear transfer functions. By forcing voltages on these pins, a 7 segment transfer function can be made. See *Figure 7*.

Only the Ladder detail shown.

Figure 7. A/D with Programmed Ladder Control for Creating a Piecewise Linear Transfer Function

#### PERFORMANCE CHARACTERISTICS

Graph 1. DNL vs. F<sub>S</sub>

Graph 2. INL vs. FS

Graph 3. I<sub>DD</sub> vs. F<sub>S</sub>

**Graph 4. DNL Error Plot**

**Graph 5. INL Error Plot**

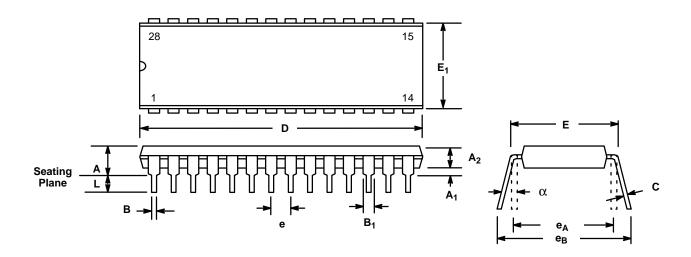

# 28 LEAD PLASTIC DUAL-IN-LINE (600 MIL PDIP)

|                | INC   | HES       | MILLIN | METERS |

|----------------|-------|-----------|--------|--------|

| SYMBOL         | MIN   | MAX       | MIN    | MAX    |

| Α              | 0.160 | 0.250     | 4.06   | 6.35   |

| A <sub>1</sub> | 0.015 | 0.070     | 0.38   | 1.78   |

| A <sub>2</sub> | 0.125 | 0.195     | 3.18   | 4.95   |

| В              | 0.014 | 0.024     | 0.36   | 0.56   |

| B <sub>1</sub> | 0.030 | 0.070     | 0.76   | 1.78   |

| С              | 0.008 | 0.014     | 0.20   | 0.38   |

| D              | 1.380 | 1.565     | 35.05  | 39.75  |

| Е              | 0.600 | 0.625     | 15.24  | 15.88  |

| E <sub>1</sub> | 0.485 | 0.580     | 12.32  | 14.73  |

| е              | 0.10  | 0.100 BSC |        | 4 BSC  |

| e <sub>A</sub> | 0.60  | 0.600 BSC |        | 24 BSC |

| e <sub>B</sub> | 0.600 | 0.700     | 15.24  | 17.78  |

| L              | 0.115 | 0.200     | 2.92   | 5.08   |

| α              | 0°    | 15°       | 0°     | 15°    |

Note: The control dimension is the inch column

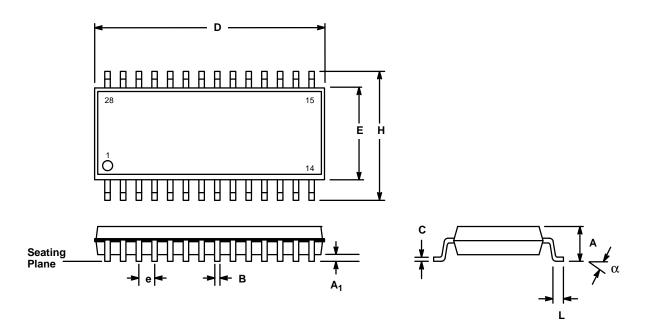

# 28 LEAD SMALL OUTLINE (300 MIL JEDEC SOIC)

|        | INC   | HES       | MILLIN | METERS |

|--------|-------|-----------|--------|--------|

| SYMBOL | MIN   | MAX       | MIN    | MAX    |

| Α      | 0.093 | 0.104     | 2.35   | 2.65   |

| A1     | 0.004 | 0.012     | 0.10   | 0.30   |

| В      | 0.013 | 0.020     | 0.33   | 0.51   |

| С      | 0.009 | 0.013     | 0.23   | 0.32   |

| D      | 0.697 | 0.713     | 17.70  | 18.10  |

| Е      | 0.291 | 0.299     | 7.40   | 7.60   |

| е      | 0.0   | 0.050 BSC |        | 7 BSC  |

| Н      | 0.394 | 0.419     | 10.00  | 10.65  |

| L      | 0.016 | 0.050     | 0.40   | 1.27   |

| α      | 0°    | 8°        | 0°     | 8°     |

Note: The control dimension is the millimeter column

### Notes

#### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1996 EXAR Corporation

Datasheet April 1996

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.