W83977TF

## 4. INFRARED (IR) PORT

The Infrared (IR) function provides point-to-point (or multi-point to multi-point) wireless communication which can operate under various transmission protocols including IrDA 1.0 SIR, SHARP ASK-IR. IR port shares the same port with UART B port in W83977TF. Please refer to section 11.5 for configuration information.

## 5. PARALLEL PORT

### 5.1 Printer Interface Logic

The parallel port of the W83977TF makes possible the attachment of various devices that accept eight bits of parallel data at standard TTL level. The W83977TF supports an IBM XT/AT compatible parallel port (SPP), bi-directional parallel port (BPP), Enhanced Parallel Port (EPP), Extended Capabilities Parallel Port (ECP), Extension FDD mode (EXTFDD), Extension 2FDD mode (EXT2FDD) on the parallel port. Refer to the configuration registers for more information on disabling, power-down, and on selecting the mode of operation.

Table 5-1 shows the pin definitions for different modes of the parallel port.

| HOST<br>CONNECTOR | PIN NUMBER<br>OF W83977TF | PIN ATTRIBUTE | SPP     | EPP     | ECP                                               |

|-------------------|---------------------------|---------------|---------|---------|---------------------------------------------------|

| 1                 | 36                        | 0             | nSTB    | nWrite  | nSTB, HostClk <sup>2</sup>                        |

| 2-9               | 31-26, 24-23              | I/O           | PD<0:7> | PD<0:7> | PD<0:7>                                           |

| 10                | 22                        | I             | nACK    | Intr    | nACK, PeriphClk <sup>2</sup>                      |

| 11                | 21                        | I             | BUSY    | nWait   | BUSY, PeriphAck <sup>2</sup>                      |

| 12                | 19                        | I             | PE      | PE      | PEerror, nAckReverse <sup>2</sup>                 |

| 13                | 18                        | I             | SLCT    | Select  | SLCT, Xflag <sup>2</sup>                          |

| 14                | 35                        | 0             | nAFD    | nDStrb  | nAFD, HostAck <sup>2</sup>                        |

| 15                | 34                        | I             | nERR    | nError  | nFault <sup>1</sup> , nPeriphRequest <sup>2</sup> |

| 16                | 33                        | 0             | nINIT   | nInit   | nINIT <sup>1</sup> , nReverseRqst <sup>2</sup>    |

| 17                | 32                        | 0             | nSLIN   | nAStrb  | nSLIN <sup>1</sup> , ECPMode <sup>2</sup>         |

**TABLE 5-1-1** PARALLEL PORT CONNECTOR AND PIN DEFINITIONS

Notes:

n<name > : Active Low

1. Compatible Mode

2. High Speed Mode

3. For more information, refer to the IEEE 1284 standard.

## PRELIMINARY

| HOST<br>CONNECTOR | PIN NUMBER OF<br>W83977TF | PIN<br>ATTRIBUTE | SPP   | PIN<br>ATTRIBUTE | EXT2FDD | PIN<br>ATTRIBUT<br>E | EXTFDD  |

|-------------------|---------------------------|------------------|-------|------------------|---------|----------------------|---------|

| 1                 | 36                        | 0                | nSTB  |                  |         |                      |         |

| 2                 | 31                        | I/O              | PD0   | I                | INDEX2  | I                    | INDEX2  |

| 3                 | 30                        | I/O              | PD1   | I                | TRAK02  | I                    | TRAK02  |

| 4                 | 29                        | I/O              | PD2   | I                | WP2     | I                    | WP2     |

| 5                 | 28                        | I/O              | PD3   | I                | RDATA2  | I                    | RDATA2  |

| 6                 | 27                        | I/O              | PD4   | I                | DSKCHG2 | I                    | DSKCHG2 |

| 7                 | 26                        | I/O              | PD5   |                  |         |                      |         |

| 8                 | 24                        | I/O              | PD6   | OD               | MOA2    |                      |         |

| 9                 | 23                        | I/O              | PD7   | OD               | DSA2    |                      |         |

| 10                | 22                        | I                | nACK  | OD               | DSB2    | OD                   | DSB2    |

| 11                | 21                        | I                | BUSY  | OD               | MOB2    | OD                   | MOB2    |

| 12                | 19                        | I                | PE    | OD               | WD2     | OD                   | WD2     |

| 13                | 18                        | I                | SLCT  | OD               | WE2     | OD                   | WE2     |

| 14                | 35                        | 0                | nAFD  | OD               | RWC2    | OD                   | RWC2    |

| 15                | 34                        | I                | nERR  | OD               | HEAD2   | OD                   | HEAD2   |

| 16                | 33                        | 0                | nINIT | OD               | DIR2    | OD                   | DIR2    |

| 17                | 32                        | 0                | nSLIN | OD               | STEP2   | OD                   | STEP2   |

### TABLE 5-1-2 PARALLEL PORT CONNECTOR AND PIN DEFINITIONS

## 5.2 Enhanced Parallel Port (EPP)

#### TABLE 5-2 PRINTER MODE AND EPP REGISTER ADDRESS

| A2 | A1 | A0 | REGISTER                       | NOTE |

|----|----|----|--------------------------------|------|

| 0  | 0  | 0  | Data port (R/W)                | 1    |

| 0  | 0  | 1  | Printer status buffer (Read)   | 1    |

| 0  | 1  | 0  | Printer control latch (Write)  | 1    |

| 0  | 1  | 0  | Printer control swapper (Read) | 1    |

| 0  | 1  | 1  | EPP address port (R/W)         | 2    |

| 1  | 0  | 0  | EPP data port 0 (R/W)          | 2    |

| 1  | 0  | 1  | EPP data port 1 (R/W)          | 2    |

| 1  | 1  | 0  | EPP data port 2 (R/W)          | 2    |

| 1  | 1  | 1  | EPP data port 2 (R/W)          | 2    |

Notes:

1. These registers are available in all modes.

2. These registers are available only in EPP mode.

#### 5.2.1 Data Swapper

The system microprocessor can read the contents of the printer's data latch by reading the data swapper.

#### 5.2.2 Printer Status Buffer

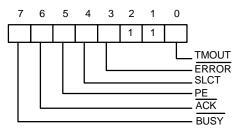

The system microprocessor can read the printer status by reading the address of the printer status buffer. The bit definitions are as follows:

- Bit 7: This signal is active during data entry, when the printer is off-line during printing, when the print head is changing position, or during an error state. When this signal is active, the printer is busy and cannot accept data.

- Bit 6: This bit represents the current state of the printer's ACK signal. A 0 means the printer has received a character and is ready to accept another. Normally, this signal will be active for approximately 5 microseconds before BUSY stops.

- Bit 5: Logical 1 means the printer has detected the end of paper.

- Bit 4: Logical 1 means the printer is selected.

- Bit 3: Logical 0 means the printer has encountered an error condition.

- Bit 1, 2: These two bits are not implemented and are logic one during a read of the status register.

- Bit 0: This bit is valid in EPP mode only. It indicates that a 10 µS time-out has occurred on the EPP bus. A logic 0 means that no time-out error has occurred; a logic 1 means that a time-out error has been detected. Writing a logic 1 to this bit will clear the time-out status bit; writing a logic 0 has no effect.

W83977TF

#### 5.2.3 Printer Control Latch and Printer Control Swapper

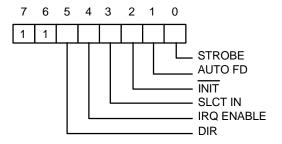

The system microprocessor can read the contents of the printer control latch by reading the printer control swapper. Bit definitions are as follows:

- Bit 7, 6: These two bits are a logic one during a read. They can be written.

- Bit 5: Direction control bit

When this bit is a logic 1, the parallel port is in input mode (read); when it is a logic 0, the parallel port is in output mode (write). This bit can be read and written. In SPP mode, this bit is invalid and fixed at zero.

- Bit 4: A 1 in this position allows an interrupt to occur when ACK changes from low to high.

- Bit 3: A 1 in this bit position selects the printer.

- Bit 2: A 0 starts the printer (50 microsecond pulse, minimum).

- Bit 1: A 1 causes the printer to line-feed after a line is printed.

- Bit 0: A 0.5 microsecond minimum high active pulse clocks data into the printer. Valid data must be present for a minimum of 0.5 microseconds before and after the strobe pulse.

#### 5.2.4 EPP Address Port

The address port is available only in EPP mode. Bit definitions are as follows:

W83977TF

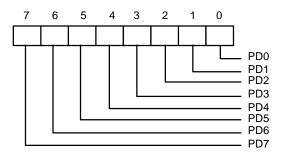

The contents of DB0-DB7 are buffered (non-inverting) and output to ports PD0-PD7 during a write operation. The leading edge of  $\overline{IOW}$  causes an EPP address write cycle to be performed, and the trailing edge of  $\overline{IOW}$  latches the data for the duration of the EPP write cycle.

PD0-PD7 ports are read during a read operation. The leading edge of  $\overline{IOR}$  causes an EPP address read cycle to be performed and the data to be output to the host CPU.

### 5.2.5 EPP Data Port 0-3

These four registers are available only in EPP mode. Bit definitions of each data port are as follows:

When accesses are made to any EPP data port, the contents of DB0-DB7 are buffered (non-inverting) and output to the ports PD0-PD7 during a write operation. The leading edge of  $\overline{IOW}$  causes an EPP data write cycle to be performed, and the trailing edge of  $\overline{IOW}$  latches the data for the duration of the EPP write cycle.

During a read operation, ports PD0-PD7 are read, and the leading edge of  $\overline{\text{IOR}}$  causes an EPP read cycle to be performed and the data to be output to the host CPU.

| REGISTER               | 7    | 6   | 5   | 4     | 3     | 2    | 1      | 0      |

|------------------------|------|-----|-----|-------|-------|------|--------|--------|

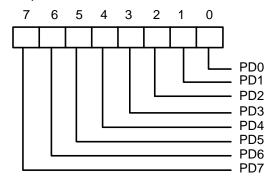

| Data Port (R/W)        | PD7  | PD6 | PD5 | PD4   | PD3   | PD2  | PD1    | PD0    |

| Status Buffer (Read)   | BUSY | ACK | PE  | SLCT  | ERROR | 1    | 1      | TMOUT  |

| Control Swapper (Read) | 1    | 1   | 1   | IRQEN | SLIN  | INIT | AUTOFD | STROBE |

| Control Latch (Write)  | 1    | 1   | DIR | IRQ   | SLIN  | INIT | AUTOFD | STROBE |

| EPP Address Port R/W)  | PD7  | PD6 | PD5 | PD4   | PD3   | PD2  | PD1    | PD0    |

| EPP Data Port 0 (R/W)  | PD7  | PD6 | PD5 | PD4   | PD3   | PD2  | PD1    | PD0    |

| EPP Data Port 1 (R/W)  | PD7  | PD6 | PD5 | PD4   | PD3   | PD2  | PD1    | PD0    |

| EPP Data Port 2 (R/W)  | PD7  | PD6 | PD5 | PD4   | PD3   | PD2  | PD1    | PD0    |

| EPP Data Port 3 (R/W)  | PD7  | PD6 | PD5 | PD4   | PD3   | PD2  | PD1    | PD0    |

#### 5.2.6 Bit Map of Parallel Port and EPP Registers

#### PRELIMINARY

| EPP NAME | TYPE | EPP DESCRIPTION                                                                                                             |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------|

| nWrite   | 0    | Denotes an address or data read or write operation.                                                                         |

| PD<0:7>  | I/O  | Bi-directional EPP address and data bus.                                                                                    |

| Intr     | I    | Used by peripheral device to interrupt the host.                                                                            |

| nWait    | I    | Inactive to acknowledge that data transfer is completed. Active to indicate that the device is ready for the next transfer. |

| PE       | I    | Paper end; same as SPP mode.                                                                                                |

| Select   | I    | Printer selected status; same as SPP mode.                                                                                  |

| nDStrb   | 0    | This signal is active low. It denotes a data read or write operation.                                                       |

| nError   | I    | Error; same as SPP mode.                                                                                                    |

| nlnits   | 0    | This signal is active low. When it is active, the EPP device is reset to its initial operating mode.                        |

| nAStrb   | 0    | This signal is active low. It denotes an address read or write operation.                                                   |

#### 5.2.7 EPP Pin Descriptions

#### 5.2.8 EPP Operation

When the EPP mode is selected in the configuration register, the standard and bi-directional modes are also available. The PDx bus is in the standard or bi-directional mode when no EPP read, write, or address cycle is currently being executed. In this condition all output signals are set by the SPP Control Port and the direction is controlled by DIR of the Control Port.

A watchdog timer is required to prevent system lockup. The timer indicates that more than 10  $\mu$ S have elapsed from the start of the EPP cycle to the time WAIT is deasserted. The current EPP cycle is aborted when a time-out occurs. The time-out condition is indicated in Status bit 0.

#### 5.2.8.1 EPP Operation

The EPP operates on a two-phase cycle. First, the host selects the register within the device for subsequent operations. Second, the host performs a series of read and/or write byte operations to the selected register. Four operations are supported on the EPP: Address Write, Data Write, Address Read, and Data Read. All operations on the EPP device are performed asynchronously.

#### 5.2.8.2 EPP Version 1.9 Operation

The EPP read/write operation can be completed under the following conditions:

a. If the nWait is active low, when the read cycle (nWrite inactive high, nDStrb/nAStrb active low) or write cycle (nWrite active low, nDStrb/nAStrb active low) starts, the read/write cycle proceeds normally and will be completed when nWait goes inactive high.

b. If nWait is inactive high, the read/write cycle will not start. It must wait until nWait changes to active low, at which time it will start as described above.

#### 5.2.8.3 EPP Version 1.7 Operation

The EPP read/write cycle can start without checking whether nWait is active or inactive. Once the read/write cycle starts, however, it will not terminate until nWait changes from active low to inactive high.

## 5.3 Extended Capabilities Parallel (ECP) Port

This port is software and hardware compatible with existing parallel ports, so it may be used as a standard printer mode if ECP is not required. It provides an automatic high burst-bandwidth channel that supports DMA for ECP in both the forward (host to peripheral) and reverse (peripheral to host) directions.

Small FIFOs are used in both forward and reverse directions to improve the maximum bandwidth requirement. The size of the FIFO is 16 bytes. The ECP port supports an automatic handshake for the standard parallel port to improve compatibility mode transfer speed.

The ECP port supports run-length-encoded (RLE) decompression (required) in hardware. Compression is accomplished by counting identical bytes and transmitting an RLE byte that indicates how many times the next byte is to be repeated. Hardware support for compression is optional.

For more information about the ECP Protocol, refer to the Extended Capabilities Port Protocol and ISA Interface Standard.

| NAME     | ADDRESS   | I/O | ECP MODES | FUNCTION                  |

|----------|-----------|-----|-----------|---------------------------|

| data     | Base+000h | R/W | 000-001   | Data Register             |

| ecpAFifo | Base+000h | R/W | 011       | ECP FIFO (Address)        |

| dsr      | Base+001h | R   | All       | Status Register           |

| dcr      | Base+002h | R/W | All       | Control Register          |

| cFifo    | Base+400h | R/W | 010       | Parallel Port Data FIFO   |

| ecpDFifo | Base+400h | R/W | 011       | ECP FIFO (DATA)           |

| tFifo    | Base+400h | R/W | 110       | Test FIFO                 |

| cnfgA    | Base+400h | R   | 111       | Configuration Register A  |

| cnfgB    | Base+401h | R/W | 111       | Configuration Register B  |

| ecr      | Base+402h | R/W | All       | Extended Control Register |

#### 5.3.1 ECP Register and Mode Definitions

Note: The base addresses are specified by CR60 and 61, which are determined by configuration register or hardware setting.

| MODE | DESCRIPTION                                                             |

|------|-------------------------------------------------------------------------|

| 000  | SPP mode                                                                |

| 001  | PS/2 Parallel Port mode                                                 |

| 010  | Parallel Port Data FIFO mode                                            |

| 011  | ECP Parallel Port mode                                                  |

| 100  | EPP mode (If this option is enabled in the CRF0 to select ECP/EPP mode) |

| 101  | Reserved                                                                |

| 110  | Test mode                                                               |

| 111  | Configuration mode                                                      |

Note: The mode selection bits are bit 7-5 of the Extended Control Register.

W83977TF

### 5.3.2 Data and ecpAFifo Port

Modes 000 (SPP) and 001 (PS/2) (Data Port)

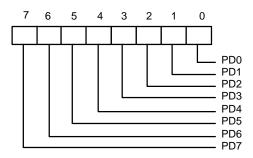

During a write operation, the Data Register latches the contents of the data bus on the rising edge of the input. The contents of this register are output to the PD0-PD7 ports. During a read operation, ports PD0-PD7 are read and output to the host. The bit definitions are as follows:

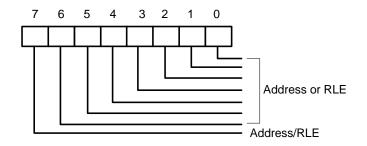

Mode 011 (ECP FIFO-Address/RLE)

A data byte written to this address is placed in the FIFO and tagged as an ECP Address/RLE. The hardware at the ECP port transmits this byte to the peripheral automatically. The operation of this register is defined only for the forward direction. The bit definitions are as follows:

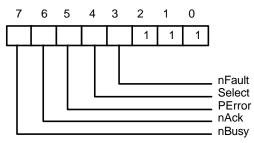

#### 5.3.3 Device Status Register (DSR)

These bits are at low level during a read of the Printer Status Register. The bits of this status register are defined as follows:

Bit 7: This bit reflects the complement of the Busy input.

- Bit 6: This bit reflects the nAck input.

- Bit 5: This bit reflects the PError input.

- Bit 4: This bit reflects the Select input.

- Bit 3: This bit reflects the nFault input.

Bit 2-0: These three bits are not implemented and are always logic one during a read.

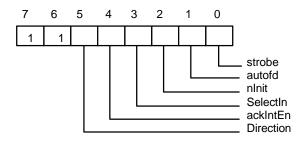

## 5.3.4 Device Control Register (DCR)

The bit definitions are as follows:

Bit 6, 7: These two bits are logic one during a read and cannot be written.

- Bit 5: This bit has no effect and the direction is always out if mode = 000 or mode = 010. Direction is valid in all other modes.

- 0 the parallel port is in output mode.

- 1 the parallel port is in input mode.

- Bit 4: Interrupt request enable. When this bit is set to a high level, it may be used to enable interrupt requests from the parallel port to the CPU due to a low to high transition on the ACK input.

- Bit 3: This bit is inverted and output to the SLIN output.

- 0 The printer is not selected.

- 1 The printer is selected.

- Bit 2: This bit is output to the  $\overline{INIT}$  output.

- Bit 1: This bit is inverted and output to the  $\overline{AFD}$  output.

- Bit 0: This bit is inverted and output to the  $\overline{\text{STB}}$  output.

#### 5.3.5 cFifo (Parallel Port Data FIFO) Mode = 010

This mode is defined only for the forward direction. The standard parallel port protocol is used by a hardware handshake to the peripheral to transmit bytes written or DMAed from the system to this FIFO. Transfers to the FIFO are byte aligned.

#### 5.3.6 ecpDFifo (ECP Data FIFO) Mode = 011

When the direction bit is 0, bytes written or DMAed from the system to this FIFO are transmitted by a hardware handshake to the peripheral using the ECP parallel port protocol. Transfers to the FIFO are byte aligned.

When the direction bit is 1, data bytes from the peripheral are read under automatic hardware handshake from ECP into this FIFO. Reads or DMAs from the FIFO will return bytes of ECP data to the system.

#### 5.3.7 tFifo (Test FIFO Mode) Mode = 110

Data bytes may be read, written, or DMAed to or from the system to this FIFO in any direction. Data in the tFIFO will not be transmitted to the parallel port lines. However, data in the tFIFO may be displayed on the parallel port data lines.

#### 5.3.8 cnfgA (Configuration Register A) Mode = 111

This register is a read-only register. When it is read, 10H is returned. This indicates to the system that this is an 8-bit implementation.

#### 5.3.9 cnfgB (Configuration Register B) Mode = 111

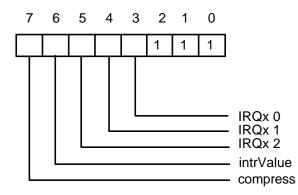

The bit definitions are as follows:

Bit 7: This bit is read-only. It is at low level during a read. This means that this chip does not support hardware RLE compression.

Bit 6: Returns the value on the ISA IRQ line to determine possible conflicts.

Bit 5-3: Reflect the IRQ resource assigned for ECP port.

| cnfgB[5:3] | IRQ resource                                                   |

|------------|----------------------------------------------------------------|

| 000        | reflect other IRQ resources selected by PnP register (default) |

| 001        | IRQ7                                                           |

| 010        | IRQ9                                                           |

| 011        | IRQ10                                                          |

| 100        | IRQ11                                                          |

| 101        | IRQ14                                                          |

| 110        | IRQ15                                                          |

| 111        | IRQ5                                                           |

|            |                                                                |

Bit 2-0: These five bits are at high level during a read and can be written.

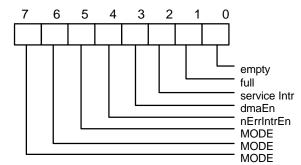

## 5.3.10 ecr (Extended Control Register) Mode = all

This register controls the extended ECP parallel port functions. The bit definitions are follows:

Bit 7-5: These bits are read/write and select the mode.

- 000 Standard Parallel Port mode. The FIFO is reset in this mode.

- 001 PS/2 Parallel Port mode. This is the same as 000 except that direction may be used to tri-state the data lines and reading the data register returns the value on the data lines and not the value in the data register.

- 010 Parallel Port FIFO mode. This is the same as 000 except that bytes are written or DMAed to the FIFO. FIFO data are automatically transmitted using the standard parallel port protocol. This mode is useful only when direction is 0.

- 011 ECP Parallel Port Mode. When the direction is 0 (forward direction), bytes placed into the ecpDFifo and bytes written to the ecpAFifo are placed in a single FIFO and auto transmitted to the peripheral using ECP Protocol. When the direction is 1 (reverse direction), bytes are moved from the ECP parallel port and packed into bytes in the ecpDFifo.

- 100 Selects EPP Mode. In this mode, EPP is activated if the EPP mode is selected.

- 101 Reserved.

- 110 Test Mode. The FIFO may be written and read in this mode, but the data will not be transmitted on the parallel port.

- 111 Configuration Mode. The confgA and confgB registers are accessible at 0 x 400 and 0x401 in this mode.

## PRELIMINARY

#### Bit 4: Read/Write (Valid only in ECP Mode)

- 1 Disables the interrupt generated on the asserting edge of nFault.

- 0 Enables an interrupt pulse on the high to low edge of nFault. If nFault is asserted (interrupt) an interrupt will be generated and this bit is written from a 1 to 0.

#### Bit 3: Read/Write

- 1 Enables DMA.

- 0 Disables DMA unconditionally.

#### Bit 2: Read/Write

- 1 Disables DMA and all of the service interrupts.

- 0 Enables one of the following cases of interrupts. When one of the service interrupts has occurred, the serviceIntr bit is set to a 1 by hardware. This bit must be reset to 0 to re-enable the interrupts. Writing a 1 to this bit will not cause an interrupt.

(a) dmaEn = 1: During DMA this bit is set to a 1 when terminal count is reached.

(b) dmaEn = 0 direction = 0: This bit is set to 1 whenever there are writeIntr Threshold or more bytes free in the FIFO.

(c) dmaEn = 0 direction = 1: This bit is set to 1 whenever there are readIntr Threshold or more valid bytes to be read from the FIFO.

#### Bit 1: Read only

- 0 The FIFO has at least 1 free byte.

- 1 The FIFO cannot accept another byte or the FIFO is completely full.

#### Bit 0: Read only

1

- 0 The FIFO contains at least 1 byte of data.

- The FIFO is completely empty.

|          | D7                      | D6            | D5        | D4         | D3       | D2          | D1     | D0     | NOTES |

|----------|-------------------------|---------------|-----------|------------|----------|-------------|--------|--------|-------|

| data     | PD7                     | PD6           | PD5       | PD4        | PD3      | PD2         | PD1    | PD0    |       |

| ecpAFifo | Addr/RLE                | Address or R  | RLE field |            |          |             |        |        | 2     |

| dsr      | nBusy                   | nAck          | PError    | Select     | nFault   | 1           | 1      | 1      | 1     |

| dcr      | 1                       | 1             | Directio  | ackIntEn   | SelectIn | nlnit       | autofd | strobe | 1     |

| cFifo    | Parallel Port Data FIFO |               |           |            |          |             |        | 2      |       |

| ecpDFifo | ECP Data FI             | ECP Data FIFO |           |            |          |             |        |        | 2     |

| tFifo    | Test FIFO               |               |           |            |          |             |        |        | 2     |

| cnfgA    | 0                       | 0             | 0         | 1          | 0        | 0           | 0      | 0      |       |

| cnfgB    | compress                | intrValue     | 1         | 1          | 1        | 1           | 1      | 1      |       |

| ecr      |                         | MODE          |           | nErrIntrEn | dmaEn    | serviceIntr | full   | empty  |       |

#### 5.3.11 Bit Map of ECP Port Registers

Notes:

1. These registers are available in all modes.

2. All FIFOs use one common 16-byte FIFO.

## 5.3.12 ECP Pin Descriptions

| NAME                    | TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                       |

|-------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| nStrobe (HostClk)       | 0    | The nStrobe registers data or address into the slave on the asserting edge during write operations. This signal handshakes with Busy.                                                                                                                                                                                             |

| PD<7:0>                 | I/O  | These signals contains address or data or RLE data.                                                                                                                                                                                                                                                                               |

| nAck (PeriphClk)        | I    | This signal indicates valid data driven by the peripheral when asserted. This signal handshakes with nAutoFd in reverse.                                                                                                                                                                                                          |

| Busy (PeriphAck)        | Ι    | This signal deasserts to indicate that the peripheral can accept<br>data. It indicates whether the data lines contain ECP command<br>information or data in the reverse direction. When in reverse<br>direction, normal data are transferred when Busy (PeriphAck)<br>is high and an 8-bit command is transferred when it is low. |

| PError (nAckReverse)    | I    | This signal is used to acknowledge a change in the direction of<br>the transfer (asserted = forward). The peripheral drives this<br>signal low to acknowledge nReverseRequest. The host relies<br>upon nAckReverse to determine when it is permitted to drive<br>the data bus.                                                    |

| Select (Xflag)          | I    | Indicates printer on line.                                                                                                                                                                                                                                                                                                        |

| nAutoFd (HostAck)       | 0    | Requests a byte of data from the peripheral when it is asserted.<br>This signal indicates whether the data lines contain ECP<br>address or data in the forward direction. When in forward<br>direction, normal data are transferred when nAutoFd (HostAck)<br>is high and an 8-bit command is transferred when it is low.         |

| nFault (nPeriphRequest) | Ι    | Generates an error interrupt when it is asserted. This signal is<br>valid only in the forward direction. The peripheral is permitted<br>(but not required) to drive this pin low to request a reverse<br>transfer during ECP Mode.                                                                                                |

| nInit (nReverseRequest) | 0    | This signal sets the transfer direction (asserted = reverse, deasserted = forward). This pin is driven low to place the channel in the reverse direction.                                                                                                                                                                         |

| nSelectIn (ECPMode)     | 0    | This signal is always deasserted in ECP mode.                                                                                                                                                                                                                                                                                     |

## PRELIMINARY

#### 5.3.13 ECP Operation

The host must negotiate on the parallel port to determine if the peripheral supports the ECP protocol before ECP operation. After negotiation, it is necessary to initialize some of the port bits. The following are required:

- (a) Set direction = 0, enabling the drivers.

- (b) Set strobe = 0, causing the nStrobe signal to default to the deasserted state.

- (c) Set autoFd = 0, causing the nAutoFd signal to default to the deasserted state.

- (d) Set mode = 011 (ECP Mode)

ECP address/RLE bytes or data bytes may be sent automatically by writing the ecpAFifo or ecpDFifo, respectively.

#### 5.3.13.1 Mode Switching

Software will execute P1284 negotiation and all operations prior to a data transfer phase under programmed I/O control (mode 000 or 001). Hardware provides an automatic control line handshake, moving data between the FIFO and the ECP port only in the data transfer phase (mode 011 or 010).

If the port is in mode 000 or 001 it may switch to any other mode. If the port is not in mode 000 or 001 it can only be switched into mode 000 or 001. The direction can be changed only in mode 001.

When in extended forward mode, the software should wait for the FIFO to be empty before switching back to mode 000 or 001. In ECP reverse mode the software waits for all the data to be read from the FIFO before changing back to mode 000 or 001.

#### 5.3.13.2 Command/Data

ECP mode allows the transfer of normal 8-bit data or 8-bit commands. In the forward direction, normal data are transferred when HostAck is high and an 8-bit command is transferred when HostAck is low. The most significant bits of the command indicate whether it is a run-length count (for compression) or a channel address.

In the reverse direction, normal data are transferred when PeriphAck is high and an 8-bit command is transferred when PeriphAck is low. The most significant bit of the command is always zero.

#### 5.3.13.3 Data Compression

The W83977TF supports run length encoded (RLE) decompression in hardware and can transfer compressed data to a peripheral. Note that the odd (RLE) compression in hardware is not supported. In order to transfer data in ECP mode, the compression count is written to the ecpAFifo and the data byte is written to the ecpDFifo.

#### 5.3.14 FIFO Operation

The FIFO threshold is set in configuration register 5. All data transfers to or from the parallel port can proceed in DMA or Programmed I/O (non-DMA) mode, as indicated by the selected mode. The FIFO is used by selecting the Parallel Port FIFO mode or ECP Parallel Port Mode. After a reset, the FIFO is disabled.

#### 5.3.15 DMA Transfers

DMA transfers are always to or from the ecpDFifo, tFifo, or CFifo. The DMA uses the standard PC DMA services. The ECP requests DMA transfers from the host by activating the PDRQ pin. The DMA will empty or fill the FIFO using the appropriate direction and mode. When the terminal count in the DMA controller is reached, an interrupt is generated and serviceIntr is asserted, which will disable the DMA.

#### 5.3.16 Programmed I/O (NON-DMA) Mode

The ECP or parallel port FIFOs can also be operated using interrupt driven programmed I/O. Programmed I/O transfers are to the ecpDFifo at 400H and ecpAFifo at 000H or from the ecpDFifo located at 400H, or to/from the tFifo at 400H. The host must set the direction, state, dmaEn = 0 and serviceIntr = 0 in the programmed I/O transfers.

The ECP requests programmed I/O transfers from the host by activating the IRQ pin. The programmed I/O will empty or fill the FIFO using the appropriate direction and mode.

## 5.4 Extension FDD Mode (EXTFDD)

In this mode, the W83977TF changes the printer interface pins to FDC input/output pins, allowing the user to install a second floppy disk drive (FDD B) through the DB-25 printer connector. The pin assignments for the FDC input/output pins are shown in Table 5-1.

After the printer interface is set to EXTFDD mode, the following occur:

- (1) Pins  $\overline{\text{MOB}}$  and  $\overline{\text{DSB}}$  will be forced to inactive state.

- (2) Pins DSKCHG, RDATA, WP, TRAKO, INDEX will be logically ORed with pins PD4-PD0 to serve as input signals to the FDC.

- (3) Pins PD4-PD0 each will have an internal resistor of about 1K ohm to serve as pull-up resistor for FDD open drain/collector output.

- (4) If the parallel port is set to EXTFDD mode after the system has booted DOS or another operating system, a warm reset is needed to enable the system to recognize the extension floppy drive.

## 5.5 Extension 2FDD Mode (EXT2FDD)

In this mode, the W83977TF changes the printer interface pins to FDC input/output pins, allowing the user to install two external floppy disk drives through the DB-25 printer connector to replace internal floppy disk drives A and B. The pin assignments for the FDC input/output pins are shown in Table5-1.

After the printer interface is set to EXTFDD mode, the following occur:

- (1) Pins MOA, DSA, MOB, and DSB will be forced to inactive state.

- (2) Pins DSKCHG, RDATA, WP, TRAKO, and INDEX will be logically ORed with pins PD4-PD0 to serve as input signals to the FDC.

- (3) Pins PD4-PD0 each will have an internal resistor of about 1K ohm to serve as pull-up resistor for FDD open drain/collector output.

- (4) If the parallel port is set to EXT2FDD mode after the system has booted DOS or another operating system, a warm reset is needed to enable the system to recognize the extension floppy drive.

W83977TF

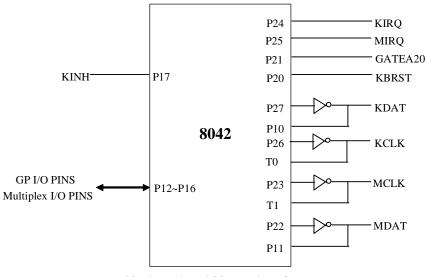

## 6. KEYBOARD CONTROLLER

The KBC (8042 with licensed KB BIOS) circuit of W83977TF is designed to provide the functions needed to interface a CPU with a keyboard and/or a PS/2 mouse, and can be used with IBM®- compatible personal computers or PS/2-based systems. The controller receives serial data from the keyboard or PS/2 mouse, checks the parity of the data, and presents the data to the system as a byte of data in its output buffer. Then, the controller will assert an interrupt to the system when data are placed in its output buffer. The keyboard and PS/2 mouse are required to acknowledge all data transmissions. No transmission should be sent to the keyboard or PS/2 mouse until an acknowledge is received for the previous data byte.

Keyboard and Mouse Interface

## 6.1 Output Buffer

The output buffer is an 8-bit read-only register at I/O address 60H (Default, PnP programmable I/O address LD5-CR60 and LD5-CR61). The keyboard controller uses the output buffer to send the scan code received from the keyboard and data bytes required by commands to the system. The output buffer can only be read when the output buffer full bit in the register is "1".

## 6.2 Input Buffer

The input buffer is an 8-bit write-only register at I/O address 60H or 64H (Default, PnP programmable I/O address LD5-CR60, LD5-CR61, LD5-CR62, and LD5-CR63). Writing to address 60H sets a flag to indicate a data write; writing to address 64H sets a flag to indicate a command write. Data written to I/O address 60H is sent to keyboard (unless the keyboard controller is expecting a data byte) through the controller's input buffer only if the input buffer full bit in the status register is 0.

## 6.3 Status Register

The status register is an 8-bit read-only register at I/O address 64H (Default, PnP programmable I/O address LD5-CR62 and LD5-CR63), that holds information about the status of the keyboard controller and interface. It may be read at any time.

| BIT | BIT FUNCTION                      | DESCRIPTION                                                                                                                                                    |

|-----|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Output Buffer Full                | 0: Output buffer empty<br>1: Output buffer full                                                                                                                |

| 1   | Input Buffer Full                 | 0: Input buffer empty<br>1: Input buffer full                                                                                                                  |

| 2   | System Flag                       | This bit may be set to 0 or 1 by writing to the system flag<br>bit in the command byte of the keyboard controller. It<br>defaults to 0 after a power-on reset. |

| 3   | Command/Data                      | 0: Data byte<br>1: Command byte                                                                                                                                |

| 4   | Inhibit Switch                    | 0: Keyboard is inhibited<br>1: Keyboard is not inhibited                                                                                                       |

| 5   | Auxiliary Device Output<br>Buffer | 0: Auxiliary device output buffer empty<br>1: Auxiliary device output buffer full                                                                              |

| 6   | General Purpose Time-<br>out      | 0: No time-out error<br>1: Time-out error                                                                                                                      |

| 7   | Parity Error                      | 0: Odd parity<br>1: Even parity (error)                                                                                                                        |

## 6.4 Commands

| COMMAND                                 |                                    | FUNCTION                          |  |  |  |  |

|-----------------------------------------|------------------------------------|-----------------------------------|--|--|--|--|

| 20h                                     | Read Co                            | mmand Byte of Keyboard Controller |  |  |  |  |

| 60h                                     | Write Co                           | mmand Byte of Keyboard Controller |  |  |  |  |

|                                         | BIT                                | BIT DEFINITION                    |  |  |  |  |

|                                         | 7                                  | Reserved                          |  |  |  |  |

|                                         | 6                                  | IBM Keyboard Translate Mode       |  |  |  |  |

|                                         | 5                                  | Disable Auxiliary Device          |  |  |  |  |

|                                         | 4                                  | Disable Keyboard                  |  |  |  |  |

|                                         | 3                                  | Reserve                           |  |  |  |  |

|                                         | 2                                  | System Flag                       |  |  |  |  |

|                                         | 1                                  | Enable Auxiliary Interrupt        |  |  |  |  |

|                                         | 0 Enable Keyboard Interrupt        |                                   |  |  |  |  |

| A4h                                     | Test Password                      |                                   |  |  |  |  |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Returns 0Fah if Password is loaded |                                   |  |  |  |  |

|                                         | Returns                            | 0F1h if Password is not loaded    |  |  |  |  |

6.4 Commands, continued

| COMMAND | FUNCTION                                                                                  |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| A5h     | Load Password                                                                             |  |  |  |  |  |  |

|         | Load Password until a "0" is received from the system                                     |  |  |  |  |  |  |

| A6h     | Enable Password                                                                           |  |  |  |  |  |  |

|         | Enable the checking of keystrokes for a match with the password                           |  |  |  |  |  |  |

| A7h     | Disable Auxiliary Device Interface                                                        |  |  |  |  |  |  |

| A8h     | Enable Auxiliary Device Interface                                                         |  |  |  |  |  |  |

| A9h     | Interface Test                                                                            |  |  |  |  |  |  |

|         | BIT BIT DEFINITION                                                                        |  |  |  |  |  |  |

|         | 00 No Error Detected                                                                      |  |  |  |  |  |  |

|         | 01 Auxiliary Device "Clock" line is stuck low                                             |  |  |  |  |  |  |

|         | 02 Auxiliary Device "Clock" line is stuck high                                            |  |  |  |  |  |  |

|         | 03 Auxiliary Device "Data" line is stuck low                                              |  |  |  |  |  |  |

|         | 04 Auxiliary Device "Data" line is stuck low                                              |  |  |  |  |  |  |

| AAh     | Self-test                                                                                 |  |  |  |  |  |  |

|         | Returns 055h if self test succeeds                                                        |  |  |  |  |  |  |

| ABh     | Interface Test                                                                            |  |  |  |  |  |  |

|         | BIT BIT DEFINITION                                                                        |  |  |  |  |  |  |

|         | 00 No Error Detected                                                                      |  |  |  |  |  |  |

|         | 01 Keyboard "Clock" line is stuck low                                                     |  |  |  |  |  |  |

|         |                                                                                           |  |  |  |  |  |  |

|         | 02     Keyboard "Clock" line is stuck high       03     Keyboard "Data" line is stuck low |  |  |  |  |  |  |

|         |                                                                                           |  |  |  |  |  |  |

|         | 04 Keyboard "Data" line is stuck high                                                     |  |  |  |  |  |  |

| ADh     | Disable Keyboard Interface                                                                |  |  |  |  |  |  |

| AEh     | Enable Keyboard Interface                                                                 |  |  |  |  |  |  |

| C0h     | Read Input Port(P1) and send data to the system                                           |  |  |  |  |  |  |

| C1h     | Continuously puts the lower four bits of Port1 into STATUS register                       |  |  |  |  |  |  |

| C2h     | Continuously puts the upper four bits of Port1 into STATUS register                       |  |  |  |  |  |  |

| D0h     | Send Port2 value to the system                                                            |  |  |  |  |  |  |

| D1h     | Only set/reset GateA20 line based on the system data bit 1                                |  |  |  |  |  |  |

| D2h     | Send data back to the system as if it came from Keyboard                                  |  |  |  |  |  |  |

| D3h     | Send data back to the system as if it came from Auxiliary Device                          |  |  |  |  |  |  |

| D4h     | Output next received byte of data from system to Auxiliary Device                         |  |  |  |  |  |  |

| E0h     | Reports the status of the test inputs                                                     |  |  |  |  |  |  |

| FXh     | Pulse only RC(the reset line) low for $6\mu$ S if Command byte is even                    |  |  |  |  |  |  |

PRELIMINARY

### 6.5 Hardware GATEA20/Keyboard Reset Control Logic

The KBC implements a hardware control logic to speed-up GATEA20 and KBRESET. This control logic is controlled by LD5-CRF0 as follows:

#### 6.5.1 KB Control Register (Logic Device 5, CR-F0)

| BIT  | 7      | 6      | 5        | 4        | 3        | 2     | 1     | 0      |

|------|--------|--------|----------|----------|----------|-------|-------|--------|

| NAME | KCLKS1 | KCLKS0 | Reserved | Reserved | Reserved | P92EN | HGA20 | HKBRST |

## KCLKS1, KCLKS0

This 2 bits are for the KBC clock rate selection.

- = 0 0 KBC clock input is 6 Mhz

- = 0 1 KBC clock input is 8 Mhz

- = 1 0 KBC clock input is 12 Mhz

- = 1 1 KBC clock input is 16 Mhz

#### P92EN (Port 92 Enable)

A "1" on this bit enables Port 92 to control GATEA20 and KBRESET.

A "0" on this bit disables Port 92 functions.

#### HGA20 (Hardware GATE A20)

A "1" on this bit selects hardware GATEA20 control logic to control GATE A20 signal.

A "0" on this bit disables hardware GATEA20 control logic function.

#### HKBRST (Hardware Keyboard Reset)

A "1" on this bit selects hardware KB RESET control logic to control KBRESET signal.

A "0" on this bit disables hardware KB RESET control logic function.

When the KBC receives data that follows a "D1" command, the hardware control logic sets or clears GATE A20 according to the received data bit 1. Similarly, the hardware control logic sets or clears KBRESET depending on the received data bit 0. When the KBC receives a "FE" command, the KBRESET is pulse low for  $6\mu$ S(Min.) with  $14\mu$ S(Min.) delay.

GATEA20 and KBRESET are controlled by either the software control or the hardware control logic and they are mutually exclusive. Then, GATEA20 and KBRESET are merged along with Port92 when P92EN bit is set.

| 6.5.2 | Port 92 | Control | Register | (Default | Value = 0x24) |

|-------|---------|---------|----------|----------|---------------|

|-------|---------|---------|----------|----------|---------------|

| BIT  | 7        | 6        | 5        | 4        | 3        | 2        | 1     | 0       |

|------|----------|----------|----------|----------|----------|----------|-------|---------|

| NAME | Res. (0) | Res. (0) | Res. (1) | Res. (0) | Res. (0) | Res. (1) | SGA20 | PLKBRST |

SGA20 (Special GATE A20 Control)

A "1" on this bit drives GATE A20 signal to high.

A "0" on this bit drives GATE A20 signal to low.

#### PLKBRST (Pull-Low KBRESET)

A "1" on this bit causes KBRESET to drive low for  $6\mu$ S (Min.) with  $14\mu$ S (Min.) delay. Before issuing another keyboard reset command, the bit must be cleared.

PRELIMINARY

## 6.6 OnNow / Security Keyboard and Mouse Wake-Up

### ---- Programmable Keyboard / Mouse Wake-Up Functions

Winbond's unique programmable keyboard/ mouse wake-up functions provide the system diversified methods for either OnNow wake-up application, or security control application. The keyboard or mouse can wake up the system by producing a panel switch low pulse on PANSWOUT pin, and connect it to chipset (for example Intel<sup>TM</sup> chipset TX, LX PIIX4) panel switch input. The wake-up conditions can be programmed as pre-determined or any keys/buttons. To implement this function, a 32.768KHz crystal must be installed between XTAL1 and XTAL2, or a 32.768KHz clock to be connected to XTAL1 and leave XTAL2 open. The VsB pin must be connected to +5V VsB of ATX power supply, and an external battery should be installed on VBAT pin to store the data (the passwords and wake-up status which had been set already) when power fails.

#### 6.6.1 Keyboard Wake-Up Function

The keyboard wake-up function is enable by setting LD-0A CR-E0 bit 6. The pre-determined keys data are stored in registers, and they can be access by an indirection method. At first, write their index address to LD-0A CR-E1, then access them by reading/writing LD-0A CR-E2. A zero data is written to the register means the comparison of this register will be ignored. The pre-programmed keys may be 1 to 5 keys with various combinations. If LD-0A CR-E0 bit 0 is set, the system will be waken up after any key struck.

#### 6.6.2 Keyboard Password Wake-Up Function

To implement this function, the bit 7 of LD-0A CR-E0 must be set, and panel switch input is connected to PANSWIN pin. Thus PANSWIN is blocked to PANSWOUT, by setting LD-0A CR-E0 properly and make only keyboard can wake up the system with preset keys (password).

#### 6.6.3 Mouse Wake-Up Function

The mouse wake-up function is activated by setting bit 5 of LD-0A CR-E0. If bit 1 of LD-0A CR-E0 is set, any movement or button clicking will make up the system. Otherwise, the mouse can wake up the system only by clicking its button twice successively with the mouse unmoved. The bit 4 of LD-0A CR-E0 determines which button (left or right) to perform wake-up function.