# 3. UART PORT

## 3.1 Universal Asynchronous Receiver/Transmitter (UART A, UART B)

The UARTs are used to convert parallel data into serial format on the transmit side and convert serial data to parallel format on the receiver side. The serial format, in order of transmission and reception, is a start bit, followed by five to eight data bits, a parity bit (if programmed) and one, one and half (five-bit format only) or two stop bits. The UARTs are capable of handling divisors of 1 to 65535 and producing a 16x clock for driving the internal transmitter logic. Provisions are also included to use this 16x clock to drive the receiver logic. The UARTs also support the MIDI data rate. Furthermore, the UARTs also include complete modem control capability and a processor interrupt system that may be software trailed to the computing time required to handle the communication link. The UARTs have a FIFO mode to reduce the number of interrupts presented to the CPU. In each UART, there are 16-byte FIFOs for both receive and transmit mode.

## 3.2 Register Address

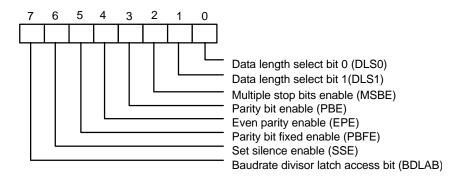

#### 3.2.1 UART Control Register (UCR) (Read/Write)

The UART Control Register controls and defines the protocol for asynchronous data communications, including data length, stop bit, parity, and baud rate selection.

- Bit 7: BDLAB. When this bit is set to a logical 1, designers can access the divisor (in 16-bit binary format) from the divisor latches of the baudrate generator during a read or write operation. When this bit is reset, the Receiver Buffer Register, the Transmitter Buffer Register, or the Interrupt Control Register can be accessed.

- Bit 6: SSE. A logical 1 forces the Serial Output (SOUT) to a silent state (a logical 0). Only IRTX is affected by this bit; the transmitter is not affected.

- Bit 5: PBFE. When PBE and PBFE of UCR are both set to a logical 1,

- (1) if EPE is logical 1, the parity bit is fixed as logical 0 to transmit and check.

- (2) if EPE is logical 0, the parity bit is fixed as logical 1 to transmit and check.

W83977TF

# TABLE 3-1 UART Register Bit Map

| Bit Number       |                                                  |     |                                                     |                                                 |                                           |                                       |                                     |                                        |                                             |                                                       |

|------------------|--------------------------------------------------|-----|-----------------------------------------------------|-------------------------------------------------|-------------------------------------------|---------------------------------------|-------------------------------------|----------------------------------------|---------------------------------------------|-------------------------------------------------------|

| Register         |                                                  | 0   | 1                                                   | 2                                               | 3                                         | 4                                     | 5                                   | 6                                      | 7                                           |                                                       |

| + 0<br>BDLAB = 0 | Receiver<br>Buffer<br>Register<br>(Read Only)    | RBR | RX Data<br>Bit 0                                    | RX Data<br>Bit 1                                | RX Data<br>Bit 2                          | RX Data<br>Bit 3                      | RX Data<br>Bit 4                    | RX Data<br>Bit 5                       | RX Data<br>Bit 6                            | RX Data<br>Bit 7                                      |

| + 0<br>BDLAB = 0 | Transmitter<br>Buffer Register<br>(Write Only)   | TBR | TX Data<br>Bit 0                                    | TX Data<br>Bit 1                                | TX Data<br>Bit 2                          | TX Data<br>Bit 3                      | TX Data<br>Bit 4                    | TX Data<br>Bit 5                       | TX Data<br>Bit 6                            | TX Data<br>Bit 7                                      |

| + 1<br>BDLAB = 0 | Interrupt Control<br>Register                    | ICR | RBR Data<br>Ready<br>Interrupt<br>Enable<br>(ERDRI) | TBR<br>Empty<br>Interrupt<br>Enable<br>(ETBREI) | USR<br>Interrupt<br>Enable<br>(EUSRI)     | HSR<br>Interrupt<br>Enable<br>(EHSRI) | 0                                   | 0                                      | 0                                           | 0                                                     |

| + 2              | Interrupt Status<br>Register<br>(Read Only)      | ISR | "0" if<br>Interrupt<br>Pending                      | Interrupt<br>Status<br>Bit (0)                  | Interrupt<br>Status<br>Bit (1)            | Interrupt<br>Status<br>Bit (2)**      | 0                                   | 0                                      | FIFOs<br>Enabled                            | FIFOs<br>Enabled<br>**                                |

| + 2              | UART FIFO<br>Control<br>Register<br>(Write Only) | UFR | FIFO<br>Enable                                      | RCVR<br>FIFO<br>Reset                           | XMIT<br>FIFO<br>Reset                     | DMA<br>Mode<br>Select                 | Reserved                            | Reversed                               | RX<br>Interrupt<br>Active<br>Level<br>(LSB) | RX<br>Interrupt<br>Active Level<br>(MSB)              |

| + 3              | UART Control<br>Register                         | UCR | Data<br>Length<br>Select<br>Bit 0<br>(DLS0)         | Data<br>Length<br>Select<br>Bit 1<br>(DLS1)     | Multiple<br>Stop Bits<br>Enable<br>(MSBE) | Parity<br>Bit<br>Enable<br>(PBE)      | Even<br>Parity<br>Enable<br>(EPE)   | Parity<br>Bit Fixed<br>Enable<br>PBFE) | Set<br>Silence<br>Enable<br>(SSE)           | Baudrate<br>Divisor<br>Latch<br>Access Bit<br>(BDLAB) |

| + 4              | Handshake<br>Control<br>Register                 | HCR | Data<br>Terminal<br>Ready<br>(DTR)                  | Request<br>to<br>Send<br>(RTS)                  | Loopback<br>RI<br>Input                   | IRQ<br>Enable                         | Internal<br>Loopback<br>Enable      | 0                                      | 0                                           | 0                                                     |

| + 5              | UART Status<br>Register                          | USR | RBR Data<br>Ready<br>(RDR)                          | Overrun<br>Error<br>(OER)                       | Parity Bit<br>Error<br>(PBER)             | No Stop<br>Bit<br>Error<br>(NSER)     | Silent<br>Byte<br>Detected<br>(SBD) | TBR<br>Empty<br>(TBRE)                 | TSR<br>Empty<br>(TSRE)                      | RX FIFO<br>Error<br>Indication<br>(RFEI) **           |

| + 6              | Handshake<br>Status Register                     | HSR | CTS<br>Toggling<br>(TCTS)                           | DSR<br>Toggling<br>(TDSR)                       | RI Falling<br>Edge<br>(FERI)              | DCD<br>Toggling<br>(TDCD)             | Clear<br>to Send<br>(CTS)           | Data Set<br>Ready<br>(DSR)             | Ring<br>Indicator<br>(RI)                   | Data Carrier<br>Detect<br>(DCD)                       |

| + 7              | User Defined<br>Register                         | UDR | Bit 0                                               | Bit 1                                           | Bit 2                                     | Bit 3                                 | Bit 4                               | Bit 5                                  | Bit 6                                       | Bit 7                                                 |

| + 0<br>BDLAB = 1 | Baudrate Divisor<br>Latch Low                    | BLL | Bit 0                                               | Bit 1                                           | Bit 2                                     | Bit 3                                 | Bit 4                               | Bit 5                                  | Bit 6                                       | Bit 7                                                 |

| + 1<br>BDLAB = 1 | Baudrate<br>Divisor Latch<br>High                | BHL | Bit 8                                               | Bit 9                                           | Bit 10                                    | Bit 11                                | Bit 12                              | Bit 13                                 | Bit 14                                      | Bit 15                                                |

\*: Bit 0 is the least significant bit. The least significant bit is the first bit serially transmitted or received.

\*\*: These bits are always 0 in 16450 Mode.

- Bit 4: EPE. This bit describes the number of logic 1's in the data word bits and parity bit only when bit 3 is programmed. When this bit is set, an even number of logic 1's are sent or checked. When the bit is reset, an odd number of logic 1's are sent or checked.

- Bit 3: PBE. When this bit is set, the position between the last data bit and the stop bit of the SOUT will be stuffed with the parity bit at the transmitter. For the receiver, the parity bit in the same position as the transmitter will be detected.

- Bit 2: MSBE. This bit defines the number of stop bits in each serial character that is transmitted or received.

- (1) If MSBE is set to a logical 0, one stop bit is sent and checked.

- (2) If MSBE is set to a logical 1, and data length is 5 bits, one and a half stop bits are sent and checked.

- (3) If MSBE is set to a logical 1, and data length is 6, 7, or 8 bits, two stop bits are sent and checked.

- Bits 0 and 1: DLS0, DLS1. These two bits define the number of data bits that are sent or checked in each serial character.

TABLE 3-2 WORD LENGTH DEFINITION

| DLS1 | DLS0 | DATA LENGTH |  |  |

|------|------|-------------|--|--|

| 0    | 0    | 5 bits      |  |  |

| 0    | 1    | 6 bits      |  |  |

| 1    | 0    | 7 bits      |  |  |

| 1    | 1    | 8 bits      |  |  |

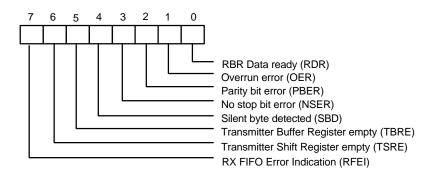

#### 3.2.2 UART Status Register (USR) (Read/Write)

This 8-bit register provides information about the status of the data transfer during communication.

Bit 7: RFEI. In 16450 mode, this bit is always set to a logic 0. In 16550 mode, this bit is set to a logic 1 when there is at least one parity bit error, no stop bit error or silent byte detected in the FIFO. In 16550 mode, this bit is cleared by reading from the USR if there are no remaining errors left in the FIFO.

- Bit 6: TSRE. In 16450 mode, when TBR and TSR are both empty, this bit will be set to a logical 1. In 16550 mode, if the transmit FIFO and TSR are both empty, it will be set to a logical 1. Other thanthese two cases, this bit will be reset to a logical 0.

- Bit 5: TBRE. In 16450 mode, when a data character is transferred from TBR to TSR, this bit will be set to a logical 1. If ETREI of ICR is a logical 1, an interrupt will be generated to notify the CPU to write the next data. In 16550 mode, this bit will be set to a logical 1 when the transmit FIFO is empty. It will be reset to a logical 0 when the CPU writes data into TBR or FIFO.

- Bit 4: SBD. This bit is set to a logical 1 to indicate that received data are kept in silent state for a full word time, including start bit, data bits, parity bit, and stop bits. In 16550 mode, it indicates the same condition for the data on top of the FIFO. When the CPU reads USR, it will clear this bit to a logical 0.

- Bit 3: NSER. This bit is set to a logical 1 to indicate that the received data have no stop bit. In 16550 mode, it indicates the same condition for the data on top of the FIFO. When the CPU reads USR, it will clear this bit to a logical 0.

- Bit 2: PBER. This bit is set to a logical 1 to indicate that the parity bit of received data is wrong. In 16550 mode, it indicates the same condition for the data on top of the FIFO. When the CPU reads USR, it will clear this bit to a logical 0.

- Bit 1: OER. This bit is set to a logical 1 to indicate received data have been overwritten by the next received data before they were read by the CPU. In 16550 mode, it indicates the same condition instead of FIFO full. When the CPU reads USR, it will clear this bit to a logical 0.

- Bit 0: RDR. This bit is set to a logical 1 to indicate received data are ready to be read by the CPU in the RBR or FIFO. After no data are left in the RBR or FIFO, the bit will be reset to a logical 0.

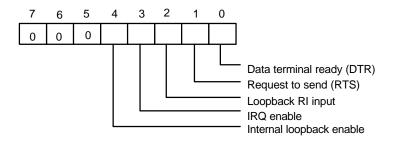

#### 3.2.3 Handshake Control Register (HCR) (Read/Write)

This register controls the pins of the UART used for handshaking peripherals such as modem, and controls the diagnostic mode of the UART.

- Bit 4: When this bit is set to a logical 1, the UART enters diagnostic mode by an internal loopback, as follows:

- (1) SOUT is forced to logical 1, and SIN is isolated from the communication link instead of the TSR.

- (2) Modem output pins are set to their inactive state.

- (3) Modem input pins are isolated from the communication link and connect internally as DTR (bit 0 of HCR)  $\rightarrow \overline{\text{DSR}}$ , RTS (bit 1 of HCR)  $\rightarrow \overline{\text{CTS}}$ , Loopback RI input (bit 2 of HCR)  $\rightarrow \overline{\text{RI}}$  and IRQ enable (bit 3 of HCR)  $\rightarrow \overline{\text{DCD}}$ . Aside from the above connections, the LIART operates normally. This method allows the

Aside from the above connections, the UART operates normally. This method allows the CPU to test the UART in a convenient way.

- Bit 3: The UART interrupt output is enabled by setting this bit to a logic 1. In the diagnostic mode this bit is internally connected to the modem control input  $\overline{\text{DCD}}$ .

- Bit 2: This bit is used only in the diagnostic mode. In the diagnostic mode this bit is internally connected to the modem control input  $\overline{RI}$ .

- Bit 1: This bit controls the  $\overline{\text{RTS}}$  output. The value of this bit is inverted and output to  $\overline{\text{RTS}}$ .

- Bit 0: This bit controls the DTR output. The value of this bit is inverted and output to DTR.

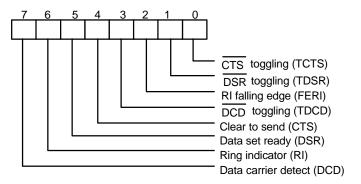

#### 3.2.4 Handshake Status Register (HSR) (Read/Write)

This register reflects the current state of four input pins for handshake peripherals such as a modem and records changes on these pins.

- Bit 7: This bit is the opposite of the  $\overline{\text{DCD}}$  input. This bit is equivalent to bit 3 of HCR in loopback mode.

- Bit 6: This bit is the opposite of the RI input. This bit is equivalent to bit 2 of HCR in loopback mode.

- Bit 5: This bit is the opposite of the  $\overline{\text{DSR}}$  input. This bit is equivalent to bit 0 of HCR in loopback mode.

- Bit 4: This bit is the opposite of the  $\overline{\text{CTS}}$  input. This bit is equivalent to bit 1 of HCR in loopback mode.

- Bit 3: TDCD. This bit indicates that the  $\overline{\text{DCD}}$  pin has changed state after HSR was read by the CPU.

- Bit 2: FERI. This bit indicates that the RI pin has changed from low to high state after HSR was read by the CPU.

- Bit 1: TDSR. This bit indicates that the  $\overline{\text{DSR}}$  pin has changed state after HSR was read by the CPU.

- Bit 0: TCTS. This bit indicates that the  $\overline{\text{CTS}}$  pin has changed state after HSR was read.

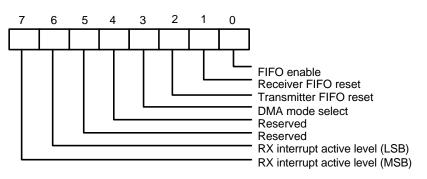

## 3.2.5 UART FIFO Control Register (UFR) (Write only)

This register is used to control the FIFO functions of the UART.

Bit 6, 7: These two bits are used to set the active level for the receiver FIFO interrupt. For example, if the interrupt active level is set as 4 bytes, once there are more than 4 data characters in the receiver FIFO, the interrupt will be activated to notify the CPU to read the data from the FIFO.

| BIT 7 | BIT 6 | RX FIFO INTERRUPT ACTIVE LEVEL (BYTES) |

|-------|-------|----------------------------------------|

| 0     | 0     | 01                                     |

| 0     | 1     | 04                                     |

| 1     | 0     | 08                                     |

| 1     | 1     | 14                                     |

TABLE 3-3 FIFO TRIGGER LEVEL

Bit 4, 5: Reserved

- Bit 3: When this bit is programmed to logic 1, the DMA mode will change from mode 0 to mode 1 if UFR bit 0 = 1.

- Bit 2: Setting this bit to a logical 1 resets the TX FIFO counter logic to initial state. This bit will clear to a logical 0 by itself after being set to a logical 1.

- Bit 1: Setting this bit to a logical 1 resets the RX FIFO counter logic to initial state. This bit will clear to a logical 0 by itself after being set to a logical 1.

- Bit 0: This bit enables the 16550 (FIFO) mode of the UART. This bit should be set to a logical 1 before other bits of UFR are programmed.

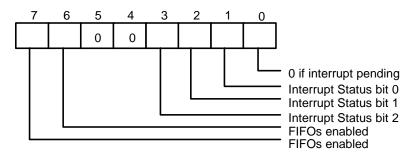

## 3.2.6 Interrupt Status Register (ISR) (Read only)

This register reflects the UART interrupt status, which is encoded by different interrupt sources into 3 bits.

- Bit 7, 6: These two bits are set to a logical 1 when UFR bit 0 = 1.

- Bit 5, 4: These two bits are always logic 0.

- Bit 3: In 16450 mode, this bit is 0. In 16550 mode, both bit 3 and 2 are set to a logical 1 when a timeout interrupt is pending.

- Bit 2, 1: These two bits identify the priority level of the pending interrupt, as shown in the table below.

- Bit 0: This bit is a logical 1 if there is no interrupt pending. If one of the interrupt sources has occurred, this bit will be set to a logical 0.

| ISR      |          |          |          | INTERRUPT SET AND FUNCTION |                        |                                                                                             |                                                                                      |  |

|----------|----------|----------|----------|----------------------------|------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--|

| Bit<br>3 | Bit<br>2 | Bit<br>1 | Bit<br>0 | Interrupt<br>priority      | Interrupt Type         | Interrupt Source                                                                            | Clear Interrupt                                                                      |  |

| 0        | 0        | 0        | 1        | -                          | -                      | No Interrupt pending                                                                        | -                                                                                    |  |

| 0        | 1        | 1        | 0        | First                      | UART Receive<br>Status | 1. OER = 1 2. PBER =1<br>3. NSER = 1 4. SBD = 1                                             | Read USR                                                                             |  |

| 0        | 1        | 0        | 0        | Second                     | RBR Data Ready         | <ol> <li>RBR data ready</li> <li>FIFO interrupt active level<br/>reached</li> </ol>         | 1. Read RBR<br>2. Read RBR until FIFO<br>data under active level                     |  |

| 1        | 1        | 0        | 0        | Second                     | FIFO Data Timeout      | Data present in RX FIFO for 4<br>characters period of time since last<br>access of RX FIFO. | Read RBR                                                                             |  |

| 0        | 0        | 1        | 0        | Third                      | TBR Empty              | TBR empty                                                                                   | <ol> <li>Write data into TBR</li> <li>Read ISR (if priority is<br/>third)</li> </ol> |  |

| 0        | 0        | 0        | 0        | Fourth                     | Handshake status       | 1. TCTS = 1 2. TDSR = 1<br>3. FERI = 1 4. TDCD = 1                                          | Read HSR                                                                             |  |

TABLE 3-4 INTERRUPT CONTROL FUNCTION

\*\* Bit 3 of ISR is enabled when bit 0 of UFR is logical 1.

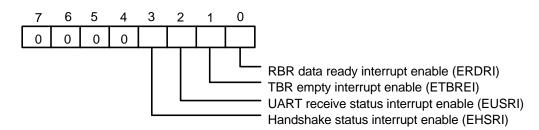

#### 3.2.7 Interrupt Control Register (ICR) (Read/Write)

This 8-bit register allows the five types of controller interrupts to activate the interrupt output signal separately. The interrupt system can be totally disabled by resetting bits 0 through 3 of the Interrupt Control Register (ICR). A selected interrupt can be enabled by setting the appropriate bits of this register to a logical 1.

Bit 7-4: These four bits are always logic 0.

Bit 3: EHSRI. Setting this bit to a logical 1 enables the handshake status register interrupt.

Bit 2: EUSRI. Setting this bit to a logical 1 enables the UART status register interrupt.

Bit 1: ETBREI. Setting this bit to a logical 1 enables the TBR empty interrupt.

Bit 0: ERDRI. Setting this bit to a logical 1 enables the RBR data ready interrupt.

#### 3.2.8 Programmable Baud Generator (BLL/BHL) (Read/Write)

Two 8-bit registers, BLL and BHL, compose a programmable baud generator that uses 24 MHz to generate a 1.8461 MHz frequency and divides it by a divisor from 1 to 2 -1. The output frequency of the baud generator is the baud rate multiplied by 16, and this is the base frequency for the transmitter and receiver. The table in the next page illustrates the use of the baud generator with a frequency of 1.8461 MHz. In high-speed UART mode (refer to CR0C bit7 and CR0C bit6), the programmable baud generator directly uses 24 MHz and the same divisor as the normal speed divisor. In high-speed mode, the data transmission rate can be as high as 1.5M bps.

# 3.2.9 User-defined Register (UDR) (Read/Write)

This is a temporary register that can be accessed and defined by the user.

#### TABLE 3-5 BAUD RATE TABLE

| BAUD RATE FROM DIFFERENT PRE-DIVIDER |                             |                        |                                                  |                                             |  |  |  |

|--------------------------------------|-----------------------------|------------------------|--------------------------------------------------|---------------------------------------------|--|--|--|

| Pre-Div: 13<br>1.8461M Hz            | Pre-Div:1.625<br>14.769M Hz | Pre-Div: 1.0<br>24M Hz | Decimal divisor used<br>to generate 16X<br>clock | Error Percentage between desired and actual |  |  |  |

| 50                                   | 400                         | 650                    | 2304                                             | **                                          |  |  |  |

| 75                                   | 600                         | 975                    | 1536                                             | **                                          |  |  |  |

| 110                                  | 880                         | 1430                   | 1047                                             | 0.18%                                       |  |  |  |

| 134.5                                | 1076                        | 1478.5                 | 857                                              | 0.099%                                      |  |  |  |

| 150                                  | 1200                        | 1950                   | 768                                              | **                                          |  |  |  |

| 300                                  | 2400                        | 3900                   | 384                                              | **                                          |  |  |  |

| 600                                  | 4800                        | 7800                   | 192                                              | **                                          |  |  |  |

| 1200                                 | 9600                        | 15600                  | 96                                               | **                                          |  |  |  |

| 1800                                 | 14400                       | 23400                  | 64                                               | **                                          |  |  |  |

| 2000                                 | 16000                       | 26000                  | 58                                               | 0.53%                                       |  |  |  |

| 2400                                 | 19200                       | 31200                  | 48                                               | **                                          |  |  |  |

| 3600                                 | 28800                       | 46800                  | 32                                               | **                                          |  |  |  |

| 4800                                 | 38400                       | 62400                  | 24                                               | **                                          |  |  |  |

| 7200                                 | 57600                       | 93600                  | 16                                               | **                                          |  |  |  |

| 9600                                 | 76800                       | 124800                 | 12                                               | **                                          |  |  |  |

| 19200                                | 153600                      | 249600                 | 6                                                | **                                          |  |  |  |

| 38400                                | 307200                      | 499200                 | 3                                                | **                                          |  |  |  |

| 57600                                | 460800                      | 748800                 | 2                                                | **                                          |  |  |  |

| 115200                               | 921600                      | 1497600                | 1                                                | **                                          |  |  |  |

\*\* The percentage error for all baud rates, except where indicated otherwise, is 0.16%.

Note. Pre-Divisor is determined by CRF0 of UART A and B.