### **MOSEL VITELIC**

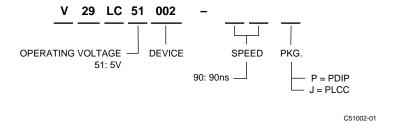

# V29LC51002 2 MEGABIT (262,144 x 8 BIT) 5 VOLT CMOS FLASH MEMORY

**PRELIMINARY**

#### Features

- 256Kx8-bit Organization

- Address Access Time: 90 ns

- Single 5V ± 10% Power Supply

- Sector Erase Mode Operation

- 512 bytes per Sector, 512 Sectors

- Sector-Erase Cycle Time: 10ms (Max)

- Byte-Write Cycle Time: 30µs (Max)

- Minimum 1,000 Erase-Program Cycles

- Low power dissipation

- Active Read Current: 20mA (Typ)

- Active Program Current: 30mA (Typ)

- Standby Current: 100μA (Max)

- Low V<sub>CC</sub> Program Inhibit Below 3.5V

- CMOS and TTL Interface

- Packages:

- 32-pin Plastic DIP

- 32-pin PLCC

### Description

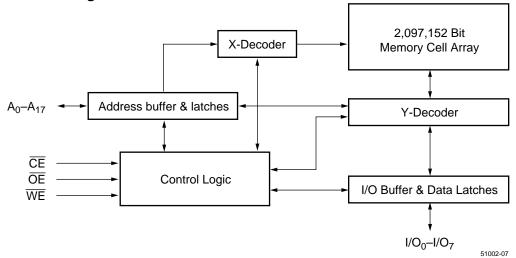

The V29LC51002 is a high speed 262,144 x 8 bit CMOS flash memory. Writing or erasing the device is done with a single 5 Volt power supply. The device has separate chip enable  $\overline{\text{CE}}$ , write enable  $\overline{\text{WE}}$ , and output enable  $\overline{\text{OE}}$  controls to eliminate bus contention.

The V29LC51002 features a sector erase operation which allows each sector to be erased and reprogrammed without affecting data stored in other sectors. The device also supports full chip erase.

### Device Usage Chart

| Operating            | Package | Outline | Access Time (ns) | Tompovotuvo         |

|----------------------|---------|---------|------------------|---------------------|

| Temperature<br>Range | Р       | J       | 90               | Temperature<br>Mark |

| 0°C to 70°C          | •       | •       | •                | Blank               |

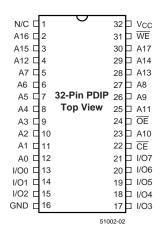

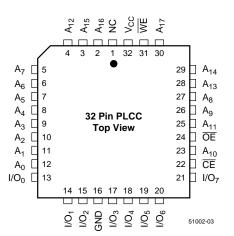

# Pin Configurations

## Pin Names

| A <sub>0</sub> -A <sub>17</sub>    | Address Inputs        |

|------------------------------------|-----------------------|

| I/O <sub>0</sub> –I/O <sub>7</sub> | Data Input/Output     |

| CE                                 | Chip Enable           |

| ŌĒ                                 | Output Enable         |

| WE                                 | Write Enable          |

| V <sub>CC</sub>                    | 5V ± 10% Power Supply |

| GND                                | Ground                |

| NC                                 | No Connect            |

# Functional Block Diagram

# Capacitance (1,2)

| Symbol           | Parameter                           | Test Setup          | Тур. | Max. | Units |

|------------------|-------------------------------------|---------------------|------|------|-------|

| C <sub>IN</sub>  | Input Capacitance                   | V <sub>IN</sub> = 0 | 6    | 8    | pF    |

| C <sub>OUT</sub> | C <sub>OUT</sub> Output Capacitance |                     | 8    | 12   | pF    |

| C <sub>IN2</sub> | Control Pin Capacitance             | V <sub>IN</sub> = 0 | 8    | 10   | pF    |

### NOTE:

- 1. Capacitance is sampled and not 100% tested.

- 2.  $T_A = 25^{\circ}C$ ,  $V_{CC} = 5V \pm 10\%$ , f = 1 MHz.

# Latch Up Characteristics<sup>(1)</sup>

| Parameter                                                                    | Min. | Max.                | Unit |

|------------------------------------------------------------------------------|------|---------------------|------|

| Input Voltage with Respect to GND on A <sub>9</sub> , $\overline{\text{OE}}$ | -1   | +13                 | V    |

| Input Voltage with Respect to GND on I/O, address or control pins            | -1   | V <sub>CC</sub> + 1 | V    |

| V <sub>CC</sub> Current                                                      | -100 | +100                | mA   |

#### NOTE

1. Includes all pins except  $V_{CC}$ . Test conditions:  $V_{CC}$  = 5V, one pin at a time.

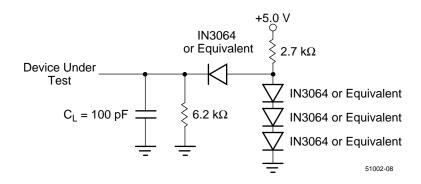

### AC Test Load

# Absolute Maximum Ratings<sup>(1)</sup>

| Symbol           | Parameter                                                   | Commercial   | Unit |

|------------------|-------------------------------------------------------------|--------------|------|

| V <sub>IN</sub>  | Input Voltage (input or I/O pins)                           | -2 to +7     | V    |

| V <sub>IN</sub>  | Input Voltage (A <sub>9</sub> pin, $\overline{\text{OE}}$ ) | -2 to +13    | V    |

| V <sub>CC</sub>  | Power Supply Voltage                                        | -0.5 to +5.5 | V    |

| T <sub>STG</sub> | Storage Temerpature (Plastic)                               | -65 to +125  | °C   |

| T <sub>OPR</sub> | Operating Temperature                                       | 0 to +70     | °C   |

| I <sub>OUT</sub> | Short Circuit Current <sup>(2)</sup>                        | 200 (Max.)   | mA   |

#### NOTE:

# DC Electrical Characteristics

(over the commercial operating range)

| Parameter<br>Name | Parameter                            | Test Conditions                                                                                                                                                                                                                                                                                                       | Min. | Max. | Unit |

|-------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>IL</sub>   | Input LOW Voltage                    | V <sub>CC</sub> = V <sub>CC</sub> Min.                                                                                                                                                                                                                                                                                | _    | 0.8  | V    |

| V <sub>IH</sub>   | Input HIGH Voltage                   | V <sub>CC</sub> = V <sub>CC</sub> Max.                                                                                                                                                                                                                                                                                | 2    | _    | V    |

| I <sub>IL</sub>   | Input Leakage Current                | $V_{IN} = GND \text{ to } V_{CC}, V_{CC} = V_{CC} \text{ Max.}$                                                                                                                                                                                                                                                       | _    | ±1   | μΑ   |

| I <sub>OL</sub>   | Output Leakage Current               | $V_{OUT} = GND$ to $V_{CC}$ , $V_{CC} = V_{CC}$ Max.                                                                                                                                                                                                                                                                  | _    | ±10  | μΑ   |

| V <sub>OL</sub>   | Output LOW Voltage                   | V <sub>CC</sub> = V <sub>CC</sub> Min., I <sub>OL</sub> = 2.1mA                                                                                                                                                                                                                                                       | _    | 0.4  | V    |

| V <sub>OH</sub>   | Output HIGH Voltage                  | V <sub>CC</sub> = V <sub>CC</sub> Min, I <sub>OH</sub> = -400μA                                                                                                                                                                                                                                                       | 2.4  | _    | V    |

| I <sub>CC1</sub>  | Read Current                         | $\overline{\text{CE}} = \overline{\text{OE}} = \text{V}_{\text{IL}}, \overline{\text{WE}} = \text{V}_{\text{IH}}, \text{ all I/Os open},$ Address input = $\text{V}_{\text{IL}}/\text{V}_{\text{IH}}, \text{ at f} = \text{1/t}_{\text{RC}} \text{ Min.},$ $\text{V}_{\text{CC}} = \text{V}_{\text{CC}} \text{ Max.}$ | _    | 40   | mA   |

| I <sub>CC2</sub>  | Write Current                        | $\overline{CE} = \overline{WE} = VIL, \overline{OE} = V_{IH}, V_{CC} = V_{CC} Max.$                                                                                                                                                                                                                                   | _    | 50   | mA   |

| I <sub>SB</sub>   | TTL Standby Current                  | $\overline{CE} = \overline{OE} = \overline{WE} = V_{IH}, V_{CC} = V_{CC} Max.$                                                                                                                                                                                                                                        | _    | 2    | mA   |

| I <sub>SB1</sub>  | CMOS Standby Current                 | $\overline{CE} = \overline{OE} = \overline{WE} = V_{CC} - 0.3V, V_{CC} = V_{CC} Max.$                                                                                                                                                                                                                                 | _    | 100  | μА   |

| V <sub>H</sub>    | Device ID Voltage for A <sub>9</sub> | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}$                                                                                                                                                                                                                                                      | 11.5 | 12.5 | V    |

| I <sub>H</sub>    | Device ID Current for A <sub>9</sub> | $\overline{CE} = \overline{OE} = V_{IL}, \overline{WE} = V_{IH}, A9 = V_{H} Max.$                                                                                                                                                                                                                                     | _    | 50   | μΑ   |

<sup>1.</sup> Stress greater than those listed unders "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>2.</sup> No more than one output maybe shorted at a time and not exceeding one second long.

# **AC Electrical Characteristics**

(over all temperature ranges)

# **Read Cycle**

| Parameter        |                                   | -9   | 00   |      |

|------------------|-----------------------------------|------|------|------|

| Name             | Parameter                         | Min. | Max. | Unit |

| t <sub>RC</sub>  | Read Cycle Time                   | 90   | _    | ns   |

| t <sub>AA</sub>  | Address Access Time               | _    | 90   | ns   |

| t <sub>ACS</sub> | Chip Enable Access Time           | _    | 90   | ns   |

| t <sub>OE</sub>  | Output Enable Access Time         | _    | 45   | ns   |

| t <sub>CLZ</sub> | CE Low to Output Active           | 0    | _    | ns   |

| t <sub>OLZ</sub> | OE Low to Output Active           | 0    | _    | ns   |

| t <sub>DF</sub>  | OE or CE High to Output in High Z | 0    | 40   | ns   |

| t <sub>OH</sub>  | Output Hold from Address Change   | 0    | _    | ns   |

# Program (Erase/Program) Cycle

| Doromotor          |                     |      | -90  |      |      |  |

|--------------------|---------------------|------|------|------|------|--|

| Parameter<br>Name  | Parameter           | Min. | Тур. | Max. | Unit |  |

| t <sub>WC</sub>    | Write Cycle Time    | 90   | _    | _    | ns   |  |

| t <sub>AS</sub>    | Address Setup Time  | 0    | _    | _    | ns   |  |

| t <sub>AH</sub>    | Address Hold Time   | 45   | _    | _    | ns   |  |

| t <sub>CS</sub>    | CE Setup Time       | 0    | _    | _    | ns   |  |

| t <sub>CH</sub>    | CE Hold Time        | 0    | _    | _    | ns   |  |

| t <sub>OES</sub>   | OE Setup Time       | 0    | _    | _    | ns   |  |

| t <sub>OEH</sub>   | OE High Hold Time   | 0    | _    | _    | ns   |  |

| t <sub>WP</sub>    | WE Pulse Width      | 45   | _    | _    | ns   |  |

| t <sub>WPH</sub>   | WE Pulse Width High | 30   | _    | _    | ns   |  |

| t <sub>DS</sub>    | Data Setup Time     | 30   | _    | _    | ns   |  |

| t <sub>DH</sub>    | Data Hold Time      | 0    | _    | _    | ns   |  |

| t <sub>WHWH1</sub> | Programming Cycle   | _    | _    | 30   | μs   |  |

| t <sub>WHWH2</sub> | Sector Erase Cycle  | _    | _    | 10   | ms   |  |

| t <sub>WHWH3</sub> | Chip Erase Cycle    | _    | 3    | _    | sec  |  |

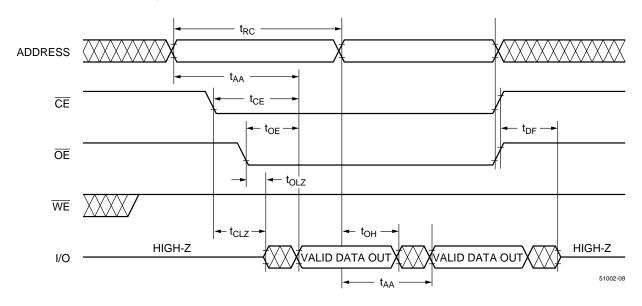

# Waveforms of Read Cycle

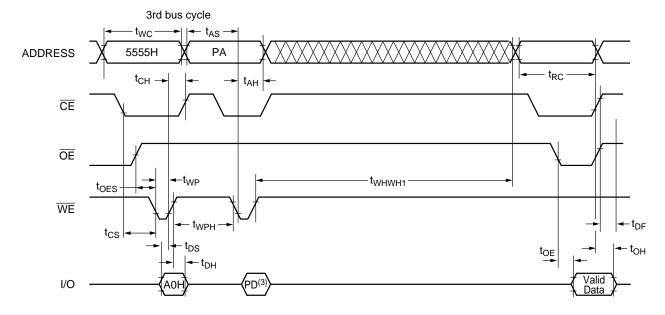

# Waveforms of WE Controlled-Program Cycle

C51002-10

#### NOTES:

- 1. PA: The address of the memory location to be programmed.

- 2. PD: The data at the byte address to be programmed.

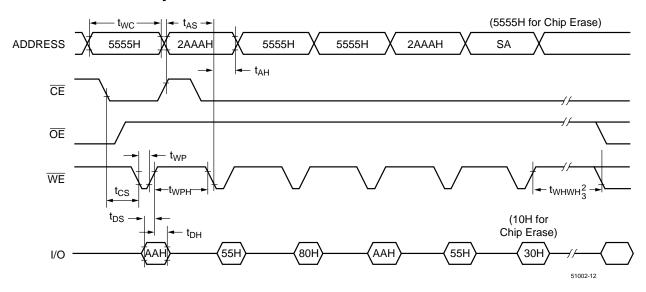

# Waveforms of Erase Cycle<sup>(1)</sup>

#### NOTES:

- 1. PA: The address of the memory location to be programmed.

- 2. PD: The data at the byte address to be programmed.

- 3. SA: The sector address for Sector Erase.

#### **FUNCTIONAL DESCRIPTION**

### Read Cycle

A read cycle is performed by holding both  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  signals LOW. Data Out becomes valid only when these conditions are met. During a read cycle  $\overline{\text{WE}}$  must be HIGH prior to  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  going LOW.  $\overline{\text{WE}}$  must remain HIGH during the read operation for the read to complete (see Table 1).

## Output Disable

Returning  $\overline{\text{OE}}$  or  $\overline{\text{CE}}$  HIGH, whichever occurs first will terminate the read operation and place the I/O pins in the HIGH-Z state.

## Standby

The device will enter standby mode when the  $\overline{\text{CE}}$  signal is HIGH. The I/O pins are placed in the HIGH-Z, independent of the  $\overline{\text{OE}}$  input state.

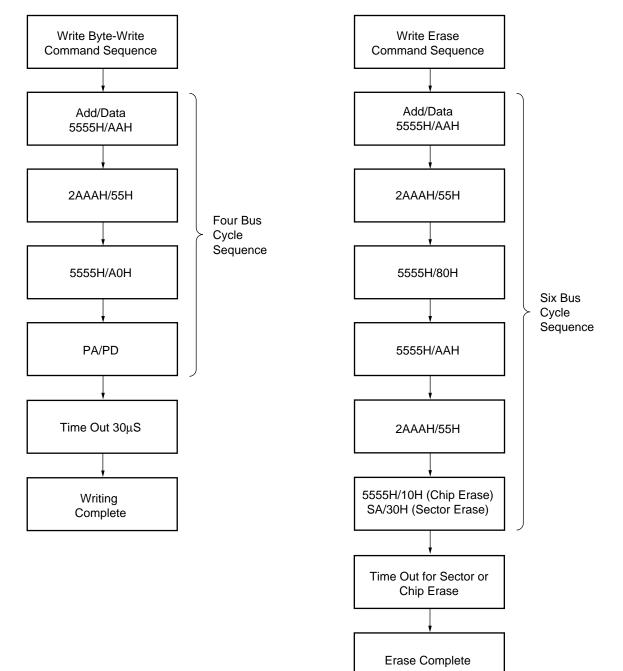

# Byte Write Cycle

The V29LC51002 is programmed on a byte-bybyte basis. The byte write operation is initiated by using a specific four-bus-cycle sequence: two unlock program cycles, a program setup command and program data program cycles (see Table 2).

During the byte write cycle, addresses are latched on the falling edge of either  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever is last. Data is latched on the rising edge of  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$ , whichever is first. The byte write cycle can be  $\overline{\text{CE}}$  controlled or  $\overline{\text{WE}}$  controlled.

#### V29LC51002

|     | =      |

|-----|--------|

| 512 |        |

| 512 |        |

| •   |        |

| •   |        |

| 512 |        |

| 512 | 00000H |

|     |        |

C51002-15

## Sector Erase Cycle

The V29LC51002 features a sector erase operation which allows each sector to be erased and reprogrammed without affecting data stored in other sectors. Sector erase operation is initiated by using a specific six-bus-cycle sequence: Two unlock program cycles, a setup command, two additional unlock program cycles, and the sector erase command (see Table 2). A sector must be first erased before it can be re-written. While in the internal erase mode, the device ignores any program attempt into the device. Sector erase is completed in 10ms max. The V29LC51002 is shipped fully erased (all bits = 1).

Table 1. Operation Modes Decoding

| Decoding Mode  | CE              | ŌĒ              | WE              | A <sub>0</sub> | A <sub>1</sub> | A <sub>9</sub> | I/O    |

|----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|--------|

| Read           | V <sub>IL</sub> | V <sub>IL</sub> | V <sub>IH</sub> | A <sub>0</sub> | A <sub>1</sub> | A <sub>9</sub> | READ   |

| Byte Write     | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | A <sub>0</sub> | A <sub>1</sub> | A <sub>9</sub> | PD     |

| Standby        | V <sub>IH</sub> | Х               | Х               | Х              | Х              | Х              | HIGH-Z |

| Output Disable | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IH</sub> | Х              | Х              | Х              | HIGH-Z |

#### NOTES:

- 1. X = Don't Care,  $V_{IH} = HIGH$ ,  $V_{IL} = LOW$ ,  $V_{H} = 12.5V Max$ .

- 2. PD: The data at the byte address to be programmed.

## Table 2. Command Codes

| Command             | First Bus<br>Program | Cycle | Second B<br>Program |      | Third Bus |      | Fourth Bu |        | Fifth Bus<br>Program | Cycle | Six Bus<br>Program | Cycle |

|---------------------|----------------------|-------|---------------------|------|-----------|------|-----------|--------|----------------------|-------|--------------------|-------|

| Command<br>Sequence | Address              | Data  | Address             | Data | Address   | Data | Address   | Data   | Address              | Data  | Address            | Data  |

| Read                | XXXXH                | F0H   |                     |      |           |      |           |        |                      |       |                    |       |

| Read                | 5555H                | AAH   | 2AAAH               | 55H  | 5555H     | F0H  | RA(1)     | RD(2)  |                      |       |                    |       |

| Autoselect          | 5555H                | ААН   | 2AAAH               | 55H  | 5555H     | 90H  | 00H       | 40H(6) |                      |       |                    |       |

|                     |                      |       |                     |      |           |      | 01H       | 82H(7) |                      |       |                    |       |

| Byte<br>Program     | 5555H                | AAH   | 2AAAH               | 55H  | 5555H     | A0H  | PA        | PD(4)  |                      |       |                    |       |

| Chip Erase          | 5555H                | ААН   | 2AAAH               | 55H  | 5555H     | 80H  | 5555H     | AAH    | 2AAAH                | 55H   | 5555H              | 10H   |

| Sector Erase        | 5555H                | ААН   | 2AAAH               | 55H  | 5555H     | 80H  | 5555H     | AAH    | 2AAAH                | 55H   | SA(5)              | 30H   |

#### NOTES:

- 1. RA: Read Address

- 2. RD: Read Data

- 3. PA: The address of the memory location to be programmed.

- 4. PD: The data at the byte address to be programmed.

- 5. SA(5): Sector Address

- 6. 40H: Manufacturing ID

- 7. 82H: Device ID

# Chip Erase Cycle

The V29LC51002 features a chip-erase operation. The chip erase operation is initiated by using a specific six-bus-cycle sequence: two unlock program cycles, a setup command, two additional unlock program cycles, and the chip erase command (see Table 2).

The automatic erase begins on the rising edge of the last  $\overline{WE}$  or  $\overline{CE}$  pulse in the command sequence and is completed in 3 sec max.

# Byte Program Algorithm

# Chip/Sector Erase Algorithm

C51002-16

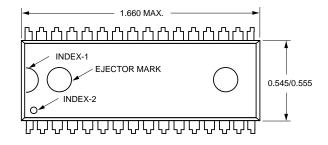

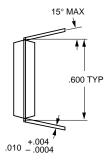

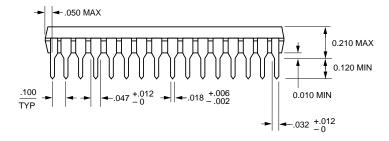

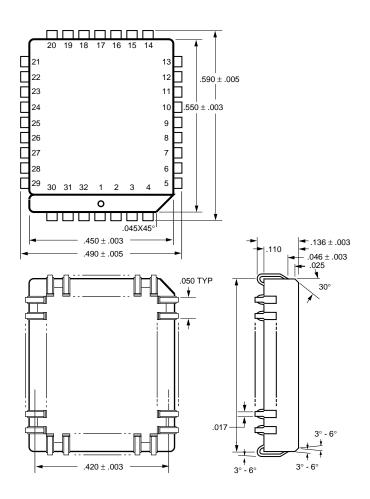

# Package Diagrams

# 32-pin Plastic DIP

# 32-pin PLCC

### **MOSEL VITELIC**

### **WORLDWIDE OFFICES**

### V29LC51002

#### U.S.A.

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0952

#### **HONG KONG**

19 DAI FU STREET TAIPO INDUSTRIAL ESTATE TAIPO, NT, HONG KONG PHONE: 852-2666-3307 FAX: 852-2770-8011

#### **TAIWAN**

7F, NO. 102 MIN-CHUAN E. ROAD, SEC. 3 TAIPEI

PHONE: 886-2-2545-1213 FAX: 886-2-2545-1209

NO 19 LI HSIN RD. SCIENCE BASED IND. PARK HSIN CHU, TAIWAN, R.O.C. PHONE: 886-3-578-3344 FAX: 886-3-579-2838

#### **JAPAN**

**SINGAPORE**

10 ANSON ROAD #23-13

INTERNATIONAL PLAZA

FAX: 65-3237013

SINGAPORE 079903

PHONE: 65-3231801

WBG MARINE WEST 25F 6, NAKASE 2-CHOME MIHAMA-KU, CHIBA-SHI CHIBA 261-71

PHONE: 81-43-299-6000 FAX: 81-43-299-6555

#### **IRELAND & UK**

BLOCK A UNIT 2 BROOMFIELD BUSINESS PARK MALAHIDE CO. DUBLIN, IRELAND PHONE: +353 1 8038020 FAX: +353 1 8038049

### GERMANY (CONTINENTAL EUROPE & ISRAEL)

71083 HERRENBERG BENZSTR. 32 GERMANY

PHONE: +49 7032 2796-0 FAX: +49 7032 2796 22

### U.S. SALES OFFICES

#### **NORTHWESTERN**

3910 NORTH FIRST STREET SAN JOSE, CA 95134 PHONE: 408-433-6000 FAX: 408-433-0952

#### **NORTHEASTERN**

SUITE 436 20 TRAFALGAR SQUARE NASHUA, NH 03063 PHONE: 603-889-4393 FAX: 603-889-9347

#### **NORTHEASTERN**

SUITE 436 20 TRAFALGAR SQUARE NASHUA, NH 03063 PHONE: 603-889-4393 FAX: 603-889-9347

#### **SOUTHWESTERN**

SUITE 200 5150 E. PACIFIC COAST HWY. LONG BEACH, CA 90804 PHONE: 562-498-3314 FAX: 562-597-2174

# CENTRAL & SOUTHEASTERN

604 FIELDWOOD CIRCLE RICHARDSON, TX 75081 PHONE: 972-690-1402 FAX: 972-690-0341

© Copyright 1999, MOSEL VITELIC Inc.

7/99 Printed in U.S.A.

The information in this document is subject to change without notice.

MOSEL VITELIC makes no commitment to update or keep current the information contained in this document. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of MOSEL-VITELIC.

MOSEL VITELIC subjects its products to normal quality control sampling techniques which are intended to provide an assurance of high quality products suitable for usual commercial applications. MOSEL VITELIC does not do testing appropriate to provide 100% product quality assurance and does not assume any liability for consequential or incidental arising from any use of its products. If such products are to be used in applications in which personal injury might occur from failure, purchaser must do its own quality assurance testing appropriate to such applications.