# SIEMENS

# V23809-E1-E30 8B/10BV23809-E1-E40 1300 nm ESCON<sup>®</sup> Parallel Transceiver

**Preliminary Data Sheet**

# **FEATURES**

- Complies with ESCON and SBCON standards

- Fully compatible with parallel trans-٠ ceiver V23806-A6-X1

- Transceiver includes clock recovery • module, P-S /S-P and ESCON/SBCON receptacle

- **Optional 8B/10B coder/decoder function** ٠ (E40 only)

- SMT component for easy mounting on • surface mount PC boards

- Transceiver mates keved ESCON/ **SBCON** connector

- Data rates for ESCON/SBCON applica-• tions from 100 to 200 MBaud

- Data rates for individual applications . from 100 to 300 MBaud

- Transmission distance of 3 km and • more

- Single power supply of 3.0 V to 5.5 V (E40 only)

- Extremely low power consumption <2 W at 3.3 V (E40 only)

- · All inputs and outputs TTL compatible

- Excellent EMI performance

- System optimized for 62.5 and 50 μm graded index fiber

- 0.7" spacing between optical interface • of transmitter and receiver

- · Low profile for high slot density

# **APPLICATIONS**

- ESCON architecture

- · High speed computer links

- Local area networks

- · High definition/digital television

- · Switching systems

- Control systems

- FC transceiver version with SC duplex • shell planned

# Maximum Ratings (Absolute maximum stress)

Exceeding any one of these values may destroy the device immediately. However, the electro-optical characteristics described in the following tables are only valid for use under the recommended operating conditions.

| Power Dissipation (PD)                                          |                      |

|-----------------------------------------------------------------|----------------------|

| Supply voltage (V <sub>CC</sub> -V <sub>EE</sub> )              |                      |

| Maximum Inqut Voltage (V <sub>IN</sub> )                        | $V_{EE}$ to $V_{CC}$ |

| Operating Case Temperature (Tcase)                              | –25 to 85°C          |

| Humidity/Temperature Test Condition (R <sub>H</sub> )           | 85/85 %/°C           |

| Lifetest Condition (Tamb/life)                                  | 115/1000°C/h         |

| Soldering Conditions Temp/Time (T <sub>sold</sub> )             | 260/10°C/s           |

| ESD Resistance (all pins to V <sub>EE</sub> , Human Body) (ESD) | 1.5 k∖               |

| Output Current (I <sub>o</sub> )                                | 50 mA                |

|                                                                 |                      |

ESCON<sup>®</sup> is a registered trademark of IBM.

# DESCRIPTION

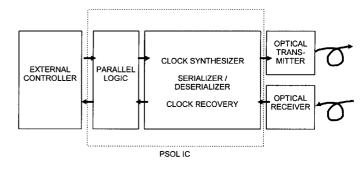

The Siemens ESCON/SBCON optical devices, along with the ESCON/SBCON optical duplex connector, are best suited for high speed fiber optic duplex transmission systems operating at a wavelength of 1300 nm. The system is fully compatible with the IBM ESCON standard and the upcoming SBCON of ANSI. It includes a transmitter and a receiver as well as the clock recovery function and the serial/parallel interfaces. In addition, an 8 B/10 B coder-decoder function can be used optionally.

The ESCON Parallel Transceiver is designed for data rates of up to 300 MBaud. A non-dissipative plastic receptacle matches the ESCON duplex connector.

The inputs/outputs are TTL compatible and the unit operates on a single power supply from 3.0 to 5.5 V.

The optical interface of transmitter and receiver have standard 0.7" spacing. Receptacle and connector have been keyed in order to prevent reverse insertion of the connector into the receptacle. After proper insertion the connector is securely held by a snap-in lock mechanism.

The transmitter converts parallel electrical TTL input signals into an optical serial signal at data rates of between 100 and 300 MBaud. The receiver performs clock recovery on the incoming data stream and converts data to a parallel output.

# New Built-in Functions (E40 only)

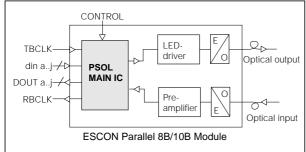

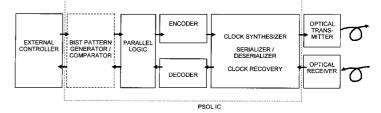

The ESCON Parallel Transceiver 8B/10B contains an encoder/decoder unit, a serial/parallel converter part, a synthesizer/clock recovery PLL section, and a TTL input and a PECL output interface, as well as the serial electro-optical converting function.

The data from the parallel TTL input interface are converted to a serial bitstream feeding an LED driver. The differential receiver signal is converted to parallel data words at the TTL output.

This transceiver meets the requirements for the IBM  $\ensuremath{\mathsf{ESCON}}^{\ensuremath{\$}}$  standard.

# Figure 1. PSOL module overview

The transceiver can be operated in two modes:

a) FSOL mode: conversion of 10 bit electrical data words to a serial bitstream and conversion of a serial bitstream to 10 bit-wide electrical data words.

In this mode the transceiver can be used as a plug-in replacement for the Parallel Transceiver V23806-A6-X1.

b) PSOL mode: conversion of 8 bit electrical data words to a serial optical bitstream using an 8B/10B encoder for optical data transmission and conversion of a serial bitstream to 10 bit-wide electrical data words using a 10B/8B decoder.

Switching between the two modes is done by applying Vcc or GND to the FSOL/PSOL pins respectively.

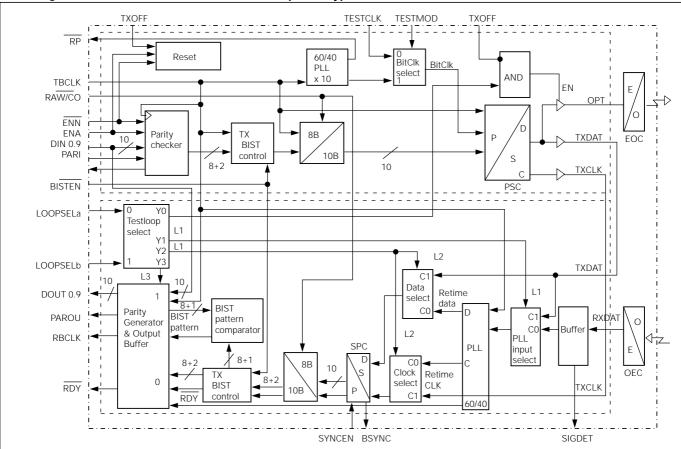

#### Figure 2. Functionality: PSOL main IC in FSOL mode

### **Recommended Operating Conditions**

| Parameter                        | Sym.                             | Min             | Max             | Units |

|----------------------------------|----------------------------------|-----------------|-----------------|-------|

| Operating Ambient<br>Temperature | Т <sub>С</sub>                   | 0               | 70              | °C    |

| Power Supply Voltage             | V <sub>CC</sub> -V <sub>EE</sub> | 3               | 5.5             | V     |

| Supply Current 3.3 V             | I <sub>CC</sub>                  |                 | 300             | mA    |

| Supply Current 5 V               |                                  |                 | 400             |       |

| Data Input High Voltage          | V <sub>IH</sub>                  | 2               | V <sub>CC</sub> | V     |

| Data Input Low Voltage           | V <sub>IL</sub>                  | V <sub>ee</sub> | 0.8             |       |

| Input Data Rise/Fall, 10–90%     | t, t<br>R'F                      | 0.4             | 1.3             | ns    |

| Output Current High              | I <sub>0</sub>                   |                 | -0.4            | mA    |

| Output Current Low               | I <sub>CC2</sub>                 |                 | 4               | 1     |

#### **Transmitter Electro-Optical Characteristics** (Values in parentheses are for 300 MBd)

| Transmitter                                                            | Sym.            | Min.         | Тур.  | Max.         | Units |

|------------------------------------------------------------------------|-----------------|--------------|-------|--------------|-------|

| Data Rate                                                              | DR              | 100          |       | 200<br>(320) | MBaud |

| Supply Current 3.3 V <sup>(1)</sup>                                    | I <sub>CC</sub> |              |       | 200          | mA    |

| Supply Current 5 V <sup>(1)</sup>                                      |                 |              |       | 300          |       |

| Launched Power (Ave.) BOL<br>into 62.5µm Fiber <sup>(2, 3, 4)</sup>    | Po              | -21<br>(-22) | -16.5 | -14          | dBm   |

| Launched Power (Ave.) EOL<br>into 62.5µm Fiber <sup>(2, 3, 4, 7)</sup> |                 | -22<br>(-23) |       |              |       |

| Transmitter                                      | Sym.                            | Min. | Тур. | Max.       | Units |

|--------------------------------------------------|---------------------------------|------|------|------------|-------|

| Center Wavelength <sup>(5, 6)</sup>              | Ι <sub>C</sub>                  | 1285 |      | 1355       | nm    |

| Spectral Width (FWHM) <sup>(6)</sup>             | σλ                              |      |      | 160        |       |

| Temperature Coefficient,<br>Optical Optput Power | ТСр                             |      |      | 0.03       | dB/°C |

| Output Rise/Fall Time,<br>20–80% <sup>(6)</sup>  | t <sub>R</sub> , t <sub>F</sub> |      | 1    | 1.7<br>(2) | ns    |

| Deterministic Jitter <sup>(8)</sup>              | Jd                              |      | 0.6  | 0.8        |       |

| Random Jitter <sup>(9)</sup>                     | J <sub>r</sub>                  |      |      | 0.06       |       |

| Extinction Ratio<br>(dynamic) <sup>(10)</sup>    | ER                              |      | -16  | -13        | dB    |

#### Notes

- 1. Transmitter operating at 200 MBaud and 50% duty cycle.

- Measured at the end of 1 meter fiber, cladding modes removed at a data rate of between 50 and 200 MBaud, 50% duty cycle.

- 3. Po [dBm]=10 log (Po/1 mW)

- 4. Po (BOL) >–20dBm and Po (EOL) >–21.5 dBm at  $T_{case}$ =60°C.

- 5. Measured at T<sub>case</sub>=60°C

- 6. Full width, half magnitude of peak wavelength: special relationship between  $\lambda c$ ,  $d\lambda$ , tr/tf according to FC-PH Rev 4.3 Paragraph 6.3.2. and Fig.26. Spectral width must be considered.

- 7. Over  $10^5$  hours lifetime at  $T_{amb}=35^{\circ}C$

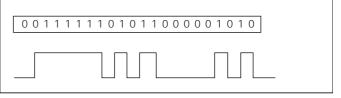

- Deterministic Jitter, measured at 200 MBaud with Jitter Test Pattern shown in Figure 5. In the Test Pattern are five positive and five negative transitions. Measure the time of the 50% crossing of all 10 transitions. The time of each crossing is then compared to the mean expected time of the crossing. The DJ is the range of the timing variations.

- 9. RMS value measured with 1010 pattern at 200 Mbaud. Peak-topeak value is determined as RMS multiplied by 14 for BER 1E-12.

- Extinction ratio is the logarithmic measure of the optical power in the OFF state (POFF) to twice the average power (P0): ER=10 log [(2xP0)/POFF]; optical power measured in mW or ER=ΩP0+3dBΩ–POFF; optical power measured in dBm

#### Receiver Electro-Optical Characteristics (Values in parentheses are for 300 MBd)

| Receiver                                                   | Sym.                                   | Min.               | Тур.  | Max.         | Units |

|------------------------------------------------------------|----------------------------------------|--------------------|-------|--------------|-------|

| Data Rate                                                  | Dr                                     | 100                |       | 200<br>(300) | MBaud |

| Supply Current <sup>(1)</sup>                              | I <sub>CC</sub>                        |                    | 1     | 100          | mA    |

| Sensitivity (Average<br>Power)BOL <sup>(2, 3, 4)</sup>     | P <sub>IN</sub>                        | -32.5<br>(-29)     | -35.5 |              | dBm   |

| Sensitivity (Average<br>Power) EOL <sup>(2, 3, 4, 5)</sup> |                                        | -32<br>(-<br>28.5) | -35   |              |       |

| Saturation (Average<br>Power)                              | P <sub>SAT</sub>                       | -14                |       |              |       |

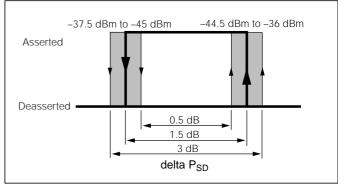

| Signal Detect<br>Assert Level <sup>(6)</sup>               | P <sub>SDA</sub>                       | -44.5              |       | -36,0        |       |

| Signal Detect<br>Deassert Level <sup>(6)</sup>             | P <sub>SDD</sub>                       | -45                |       | -37.5        |       |

| Signal Detect<br>Hysteresis                                | P <sub>SDA</sub> -<br>P <sub>SDD</sub> | 0.5                | 1.5   | 3            | dB    |

| Signal Detect<br>Reaction Time                             | SDreac                                 | 3                  |       | 500          | μs    |

| Receiver                                                     | Sym.                                   | Min. | Тур. | Max. | Units          |

|--------------------------------------------------------------|----------------------------------------|------|------|------|----------------|

| Signal Detect<br>Hysteresis                                  | P <sub>SDA</sub> -<br>P <sub>SDD</sub> | 0.5  | 1.5  | 3    | dB             |

| Signal Detect<br>Reaction Time                               | SDrea<br>c                             | 3    |      | 500  | μs             |

| Max. Deterministic<br>Jitter Optical Input <sup>(7, 9)</sup> | J <sup>d</sup>                         |      |      | 0.19 | % of<br>Unit   |

| Max. Random Jitter<br>RMS Optical Input <sup>(8, 9)</sup>    | Jr                                     |      |      | 0.09 | Inter-<br>vals |

# Notes

- 1. For  $V_{CC}$ - $V_{EE}$  (min, max). 50% duty cycle.

- 2. Measured at the end of 1 meter fiber, cladding modes removed at a data rate of between 50 and 200 MBaud, 50% duty cycle.

- 3. Po [dBm]=10 log (Po [mW])

- 4. Measured at BER=1E-12, 200 MBaud transmission rate and 50% duty cycle  $2^7$ -1 PRBS pattern; center wavelength between 1200nm and 1500 nm, fiber type 62.5/125  $\mu$ m/0.29 NA or 50/125  $\mu$ m/0.2 NA; input optical rise and fall times are 1.2 ns and 1.5 ns (20% 80%) respectively.

- 5. Over  $10^5$  hours lifetime at  $T_{amb}=35^{\circ}C$

- Indicates the presence or absence of optical power at the receiver input. Signal detect at logic "high" when asserted. All powers are average power levels. Pattern 2<sup>7</sup>-1 at 200 MBaud.

- 7. Deterministic Jitter measured at 200 MBaud with Jitter Test Pattern shown in Figure 5. In the test pattern are five positive and five negative transitions. Measure the time of the 50% crossing of all 10 transitions. The time of each crossing is then compared to the mean expected time of the crossing. The DJ is the range of the timing variations.

- To convert from specified RMS value to peak-to-peak value (at BER 1E-12) multiply value by 14.

- 9. Jitter at optical input. Jitter magnitudes above specified level may increase the bit error rate.

### Transceiver Pin Description 10 Bit Interface: FSOL Mode In this mode the transceiver is compatible with the former ver-

sion, V23806-A6-X1

| Pin#                              | Pin Name    | Level/Logic     | Description                         |

|-----------------------------------|-------------|-----------------|-------------------------------------|

| 1, 6, 9, 26,<br>43, 45,<br>48, 51 | Vee         | Power<br>Supply | Ground attached to the case         |

| 2                                 | Vcc PRE     |                 | Preamplifier positive power supply  |

| 3                                 | SIGDET      | TTL out         | Signal detected                     |

| 4                                 | LOCKREF     | TTL in          | Control input for RX PLL            |

| 5                                 | SYNCEN      |                 | Control of byte alignment operation |

| 7,8                               | VccFAST     | Power<br>Supply | Bipolar IC positive power supply    |

| 10 to 19                          | Dout a to j | TTL out         | Data output parallel 10 channels    |

| 20                                | RBCLK       | TTL out         | Read byte clock                     |

| 21                                | PAROUT      |                 | Parity bit out                      |

| 22                                | BSYNC       |                 | Byte synchronization operation      |

| 23                                | PARERR      | TTL out         | Parity bit error                    |

| Pin#     | Pin Name   | Level/Logic     | Description                                          |

|----------|------------|-----------------|------------------------------------------------------|

| 24,25    | VccSLOW    | Power<br>Supply | Logic positive power supply                          |

| 27       | Loopsel a  | TTL in          | Test loop select                                     |

| 28       | Loopsel b  |                 |                                                      |

| 29       | RESREC     |                 | Receiver reset                                       |

| 30       | RESFF      |                 | Reset all flip-flops                                 |

| 31       | TBCLK      |                 | Transmit byte clock                                  |

| 32       | PARIN      |                 | Parity bit in                                        |

| 33 to 42 | Din j to a |                 | Data input parallel 10<br>channels                   |

| 44       | TESTCLK    |                 | Test clock. In test mode this clock is the bit clock |

| 46       | TESTMOD    |                 | If this signal is low<br>TESTCLK is used             |

| 47       | TXOFF      |                 | Transceiver off when logical high                    |

| 49,50    | Vcc DRI    | Power<br>Supply | LED driver positive power supply                     |

# Transceiver Pin Description 8 Bit interface: PSOL Mode (E40 only)

| Pin#                           | Pin Name        | Level/<br>Logic | Description                                |

|--------------------------------|-----------------|-----------------|--------------------------------------------|

| 1, 6, 26,<br>43, 45,<br>48, 51 | Vee             | Power<br>Supply | Ground attached to the case                |

| 2                              | Vcc PRE         |                 | Preamplifier positive power supply         |

| 3                              | SIGDET          | TTL out         | Signal detected                            |

| 4                              | R               |                 | Read pulse for external FIFOs              |

| 5                              | SYNCEN          | TTL in          | Control of byte alignment operation        |

| 7,8                            | VccFAST         | Power<br>Supply | Positive power supply of the bipolar IC    |

| 9                              | PSOL1/<br>PSOL2 | TTL in          | Mode select for PSOL Mode 1<br>or Mode 2   |

| 10                             | RK              | TTL out         | Receiver special character flag            |

| 11 to 18                       | Dout A to H     |                 | Decoded data output parallel<br>8 channels |

| 19                             | RCV             |                 | Receiver code violation                    |

| 20                             | RBCLK           |                 | Read byte clock                            |

| 21                             | PAROUT          |                 | Parity bit out                             |

| 22                             | W               |                 | Write pulse for external FIFOs             |

| 23                             | PARERR          |                 | Parity bit error                           |

| 24, 25                         | VccSLOW         | Power<br>Supply | Logic positive power supply                |

| Pin#     | Pin Name   | Level/<br>Logic | Description                               |

|----------|------------|-----------------|-------------------------------------------|

| 27       | Loopsel a  | TTL in          | Test loop select                          |

| 28       | Loopsel b  |                 |                                           |

| 29       | EPI        | -               | Enable parallel input                     |

| 30       | ENPI       | -               | Enable next parallel input                |

| 31       | TBCLK      |                 | Transmit byte clock                       |

| 32       | PARIN      |                 | Parity bit in                             |

| 33       | ТСУ        |                 | Transmitter code violation                |

| 34 to 41 | Din H to A |                 | Uncoded data input parallel<br>8 channels |

| 42       | ТК         |                 | Transmitter special character flag        |

| 44       | RAW/COD    |                 | Select Raw Mode/Coder Mode                |

| 46       | BIST       |                 | Enable built-in self test                 |

| 47       | TXOFF      |                 | Transceiver off when logical high         |

| 49, 50   | Vcc DRI    | Power<br>Supply | LED driver positive power supply          |

# Figure 4. Signal detect threshold and hysteresis

# Figure 5. Jitter test pattern

# Block diagram of the ESCON transceiver in PSOL mode (E40 only)

# **APPLICATION NOTE**

# **Power Supply Filtering**

In most of the applications using ESCON 200 MBd Optical Transceivers, additional high speed circuits such as switching power supply, clock oscillator, or high speed multiplexer are present on the application board. These often create power supply noise at a high spectral bandwidth, caused by very fast transitions in today's chip technology.

The Siemens ESCON Transceiver Family provides superior EMI performance regarding emission and immission of radiation and provides immunity against conductive noise. Some basic recommendations are given in this document to ensure proper functionality in the field.

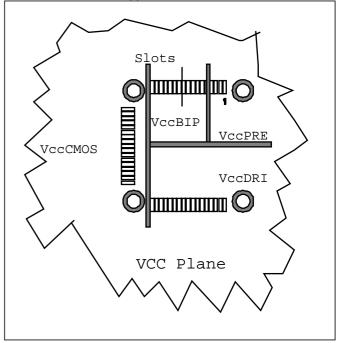

For proper operation the use of a multilayer board with ground and Vcc plane is strongly recommended. The Vcc plane should be slotted as shown in Figure 6 to avoid crosstalk between different circuitry inside the module. The metallized package is internally connected to the V<sub>EE</sub>-pins of the module. Nevertheless the package must be connected externally to ground for best shielding characteristics. Ground contact should be made with the ground rings shown in Figure 6. Because of high switching currents at V<sub>CC</sub>DRI, the use of an external 6.8 to 22  $\mu$ F capacitor is recommended at V<sub>CC</sub>DRI.

The observance of normal design rules for high speed digital systems is sufficient to ensure safe operation.

Figure 6. Slotting of V<sub>CC</sub> plane

Note: Slots are non-copper areas inside the  $V_{\mbox{CC}}$  plane to avoid cross-current flow

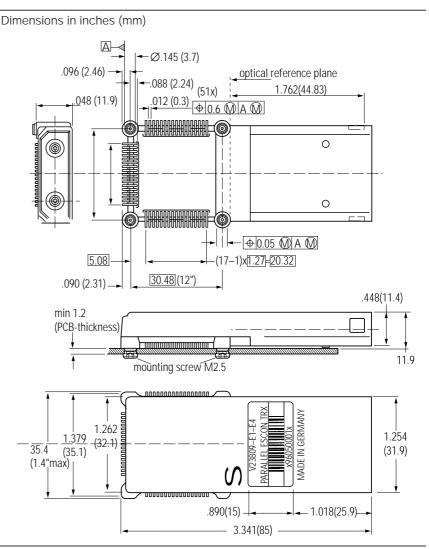

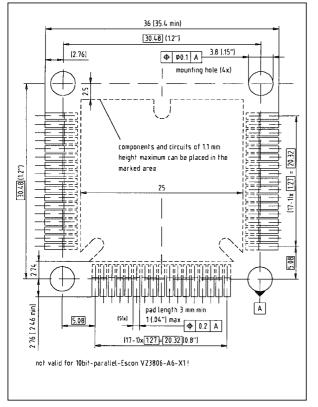

# Figure 7. Recommended footprint

The avoidance of any component or non-isolated structure, like tracks or vias, under the transceiver is strongly recommended.

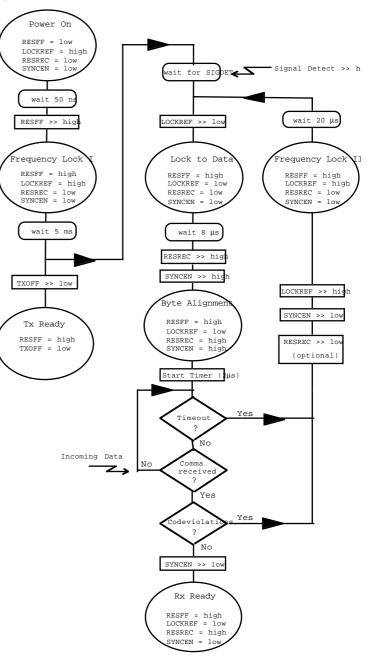

#### Figure 8. Power-on sequence in FSOL mode