## I<sup>2</sup>C-bus E<sup>2</sup>PROM

# TC89112P, TC89113P

TC89112P and TC89113P are electrically erasable, programmable read only memory (E<sup>2</sup>PROM). An I<sup>2</sup>C-bus type interface is built in to enable connection of I<sup>2</sup>C-bus systems. Other systems can also be easily connected, and control is possible with 2 pins.

| PART No. | CAPACITY | ORGANIZATION | PACKAGE |

|----------|----------|--------------|---------|

| TC89112P | 2048-bit | 256 x 8-bit  | DIP8    |

| TC89113P | 4096-bit | 512 × 8-bit  | Dire    |

### **FEATURES**

## ♦ I<sup>2</sup>C-bus systems interface

- 2 Bytes Page Write Mode

- **♦** Automatic Word Address Incrementing

- ◆Self timed Write Cycle (Built-in Timer)

- ◆Single 5V Supply

- **♦**Low Power Dissipations

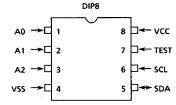

## **PIN ASSIGINMENT (TOP VIEW)**

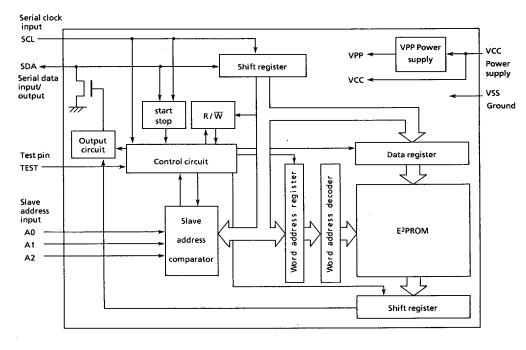

## **BLOCK DIAGRAM**

170991

5-13

9097249 0028471 471 =

## PIN FUNCTION

| PIN NAME       | Input/Output | FUNCTIONS                                                                                                                                                            |

|----------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A2<br>A1<br>A0 | Input        | Slave address input This pin is used to set the lower 3 bits of slave addresses. Each bit is set to either "H" or "L" level. With TC89113, A0 is fixed at "L" level. |

| SCL            | Input        | Serial clock input  The data transfer clock input pin.                                                                                                               |

| SDA            | input/Output | Serial data input/output The data input/output pin. This is sink open drain output, so connect external pull-up resistance.                                          |

| TEST           | Input        | Test pin Fixed at "L" level.                                                                                                                                         |

| vcc            | Power supply | +5V                                                                                                                                                                  |

| VSS            | rower supply | ov (GND)                                                                                                                                                             |

170991

## **OPERATIONAL DESCRIPTION**

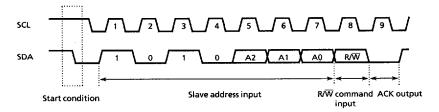

### 1. DATA TRANSFER

Data is transferred serially using the pins SCL and SDA . SCL is the clock input pin. SDA is the data input/output pin.

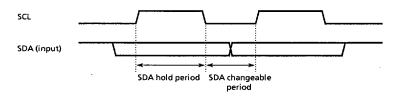

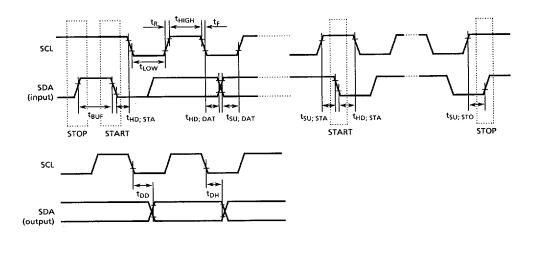

## 1.1 BASIC TIMING

## (1) Data Input

Data is input at the rising edge of the SCL line.

It is necessary to maintain SDA at a constant level while SCL is at "H" level.

The SDA level must be changed while SCL is at "L" level.

If the SDA level is changed while SCL is at "H" level, the start condition or stop condition will be issued.

Figure 1-1. Data input timing

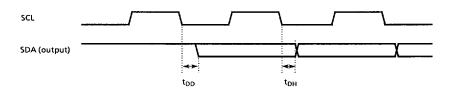

## (2) Data Output

Data output is synchronized with the SCL falling.

Figure 1-2. Data output timing

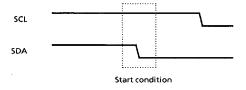

## 1.2 START CONDITION

Data transfers are started by issuing the start condition.

The start condition is issued by switching SDA from "H" level to "L" level while SCL is at "H" level.

Figure 1-3. Issuing the start condition

170991

9097249 0028473 244

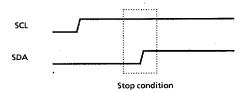

### 1.3 STOP CONDITION

Data transfers are stopped by issuing the stop condition.

The stop condition is issued by switching SDA from "L" level to "H" level while SCL is at "H" level.

Figure 1-4. Issuing the stop condition

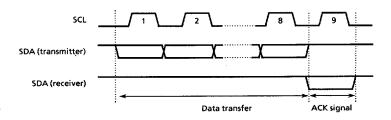

### 1.4 DATA TRANSFER FORMAT

Data is transferred in 9-bit units. The first 8 bits are used to transfer data and the final bit is used for the device receiving the data to generate an ACK (Acknowledge) signal.

Figure 1-5. Data transfer format

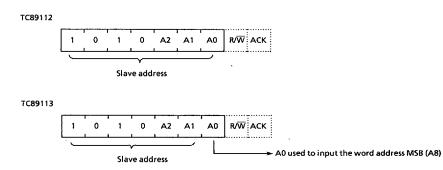

#### **DEVICE SELECTION** 2.

## 2.1 SLAVE ADDRESS INPUT

Devices are selected by inputting their slave addresses. The slave address is input after issuing the start condition. The device is selected if the input slave address matches the unique slave address of the device. If busy (writing), however, a device will not be selected even in the case of a match.

When the device is selected, "0" is output as ACK in bit 9. When the device is not selected, "1" is output.

Figure 2-1. Slave address and R/W command

170991

9097249 0028474 180 🖿

### 2.2 SLAVE ADDRESS CONFIGURATION

Slave addresses have a 7-bit configuration. The upper 4 bits are the fixed address "1010" and the lower 3 bits can be set to any optional address using external pins AO, A1 and A2.

With the TC89113, A0 is used to input the word address MSB (A8) that specifies the memory cell position.

Note: With the TC89113, the external pin A0 has no meaning and is normally connected to Vss.

Figure 2-2. Slave address configuration

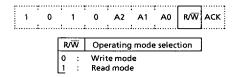

### 3. OPERATING MODE SELECTION

Operating modes are selected by inputting the R/ $\overline{W}$  command. The R/ $\overline{W}$  command is input after inputting the slave address. The Write mode is selected when the R/ $\overline{W}$  command is "0" and the Read mode is selected when it is "1".

Figure 3-1. R/W Command

## 4. OPERATING EXECUTION

The operations include the Write mode and the Read mode.

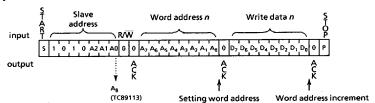

### 4.1 WRITE MODE

The Write mode includes Byte Write and Page Write.

### 4.1.1 BYTE WRITE

The Byte Write mode is used to write data to 1 byte of any optional word address.

### (1) Method of Operation

Inputting "0" with the  $R/\overline{W}$  command selects the Write mode.

Input an 8-bit word address after ACK is output. In the case of the TC89113, the word address MSB (A8) is input at the slave address A0 position. When the 8 bits of the slave address have been input, "0" is output as the next ACK.

Input 8 bits of write data after ACK is output. When the 8 bits of write data have been input, "0" is output as the next ACK.

170991

9097249 0028475 017 📟

Issue the stop condition after ACK is output. Writing starts at the point where the stop condition is issued and writing is performed automatically internally.

(2) Automatic Word Address Incrementing

After the write data have been input, the word address is automatically incremented at ACK output timing. Data is then written to that input word address.

(3) Access When Busy (Writing)

A device cannot be selected when busy (writing). Even if the slave addresses match, the device is not selected and "1" will be output as ACK after the R/W command is input.

### 4.1.2 PAGE WRITE

The Page Write mode is used to write data simultaneously to the 2 bytes of any optional word address and the next word address.

(1) Method of Operation

At the beginning, use the same method used for the Byte Write mode. After input of 8 bits of write data and output of ACK, input another 8 bits of write data. After that, as with the Byte Write mode, issue the stop condition and write the data. The two bytes are written simultaneously.

Input "0" to the LSB (A0) of the word address.

The write data input first are written to the input word address and the write data input after that are written to the next word address.

(2) Automatic Word Address Incrementing

After the write data have been input, the word address is automatically incremented at ACK output timing. In the Page Write mode, the word address is incremented twice. Data are written to the input word address and the next word address.

(3) Access When Busy (Writing)

As in the Byte Write mode, a device cannot be selected when busy (writing).

## 4.2 RAED MODE

The read modes include Current Read, Random Read and Sequential Read.

### 4.2.1 CURRENT READ

The Current Read mode is used to read the data from the currently set word address.

(1) Method of Operation

Select the Read mode by inputting "1" with the R/W command. After ACK is output, the 8 bits of data obtained by reading the currently set word address are output at the SCL fall.

"1" is input as the next ACK. After ACK is input, issue the stop condition to end the operation.

(2) Automatic Word Address Incrementing

After the output of the read data, the word address is automatically incremented at ACK input timing.

### 4.2.2 RANDOM READ

The Random Read mode is used to read data from any optional word address.

(1) Method of Operation

First, execute the dummy write mode to set a word address. Continue until ACK is output after input of the word address.

Next, issue the start condition. After that, read the data with the same method used for the Current Read mode. The 8 bits of data obtained by reading the input word address are output.

170991

(2) Automatic Word Address Incrementing

After the output of the read data, the word address is automatically incremented at ACK input timing.

## 4.2.3 SEQUENTIAL READ

The Sequential Read mode is used to read data sequentially.

(1) Method of Operation

First, use the same method used in the Current Read and Random Read modes. Then, when "0" is input as ACK after output of the read data, 8 bits of read data are output at the SCL fall. Data will continue to be read sequentially as long as "0" is input as ACK.

Input "1" as ACK to end reading.

After ACK has been input, issue the stop condition to end the operation.

When started with the Current Read mode, reading is performed sequentially from the currently set word address. And when started with Random Read mode, reading is performed sequentially from the input word address.

(2) Automatic Word Address Incrementing After the output of the read data, the word address is automatically incremented at ACK input timing.

## 5. POWER-ON CAUTION

Approximately 1ms of standby time is required from power-on to the start of operation.

## 6. OPERATIONAL SEQUENCE

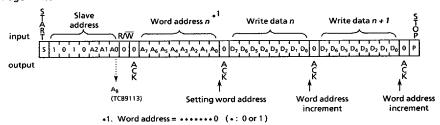

### (1) Byte Write

## (2) Page Write

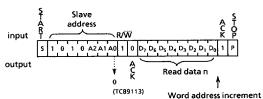

## (3) Current Read

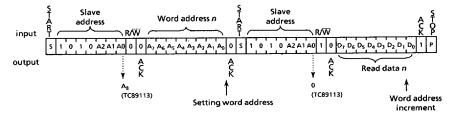

## (4) Random Read

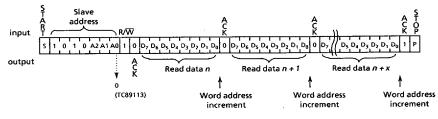

## (5) Sequential Read

170991

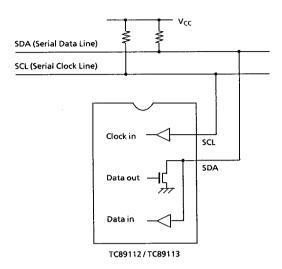

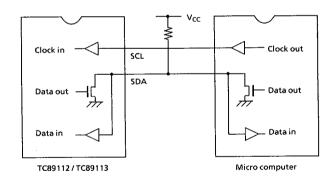

## 7. CONNECTIONS

(1) Typical Connection Between I<sup>2</sup>C-bus Interfaces

## (2) Normal Connection

When SDA is connected to a sink open drain output port.

## **ELECTRICAL CHARACTERISTICS**

**ABSOLUTE MAXIMUM RATINGS**

(GND = 0V)

| PARAMETER                    | SYMBOL           | RATINGS                        | UNITS |  |

|------------------------------|------------------|--------------------------------|-------|--|

| Supply Voltage               | V <sub>CC</sub>  | – 0.3 to 7                     | V     |  |

| Input Voltage                | V <sub>IN</sub>  | – 0.3 to V <sub>CC</sub> + 0.3 | V     |  |

| Output Voltage               | V <sub>OUT</sub> | – 0.3 to V <sub>CC</sub> + 0.3 | V     |  |

| Power Dissipation            | PD               | 600                            | mW    |  |

| Soldering Temperature (time) | Tsld             | 260 (10sec)                    | °c    |  |

| Storage Temperature          | Tstg             | – 55 to 125                    | °C    |  |

| Operating Temperature        | Topr             | 0 to 70                        | °C    |  |

RECOMMENDED OPERATING CONDITION

(GND = 0V, Topr = 0 to 70°C)

| PARAMETER          | SYMBOL          | PINS | CONDITIONS | Min.                  | Max.                  | UNITS |

|--------------------|-----------------|------|------------|-----------------------|-----------------------|-------|

| Supply Voltage     | v <sub>cc</sub> |      |            | 4.5                   | 5.5                   | V     |

| Input Low Voltage  | V <sub>IL</sub> |      |            | 0                     | V <sub>CC</sub> × 0.3 | V     |

| Input High Voltage | V <sub>iH</sub> |      |            | V <sub>CC</sub> × 0.7 | V <sub>cc</sub>       | ٧     |

D.C. CHARACTERISTICS

(GND = 0V, Topr = 0 to 70°C)

| PARAMETER              | SYMBOL           | CONDITIONS                                    | Min. | Тур. | Max. | UNITS |

|------------------------|------------------|-----------------------------------------------|------|------|------|-------|

| Input Current          | ել               |                                               | -    | _    | ± 10 | μΑ    |

| Output Leakage Voltage | llo              |                                               | -    | -    | ± 10 | μΑ    |

| Output Low Voltage     | V <sub>OL</sub>  | V <sub>CC</sub> = 4.5V, I <sub>OL</sub> = 3mA | -    | -    | 0.4  | V     |

|                        | lcco             | f <sub>SCL</sub> = 100KHz                     | -    | -    | 2.0  | mA    |

| Supply Current         | I <sub>CCP</sub> | Program                                       |      | _    | 10   | mA    |

|                        | I <sub>CCS</sub> | Standby                                       | -    | -    | 100  | μΑ    |

170991

5-22

9097249 0028480 484 📟

## A.C. CHARACTERISTICS

| PARAMETER                                                        | SYMBOL               | Min. | Тур.         | Max. | UNITS |

|------------------------------------------------------------------|----------------------|------|--------------|------|-------|

| SCL Clock Frequency                                              | f <sub>SCL</sub>     | 0    | -            | 100  | KHz   |

| Noise Suppression Time Constant at SCL and SDA Input             | t <sub>l</sub>       | -    | 100          | -    | ns    |

| Time the Bus Must Be Free Before a New<br>Transmission Can Start | t <sub>BUF</sub>     | 4.7  |              | _    | μs    |

| Start Condition Hold Time                                        | t <sub>HD;</sub> sta | 4.0  | -            | -    | μS    |

| SCL LowTime                                                      | t <sub>LOW</sub>     | 4.7  | <del>-</del> | -    | μ\$   |

| SCL High Time                                                    | t <sub>нібн</sub>    | 4.0  |              | -    | μs    |

| Start Condition Setup Time                                       | tsu; sta             | 4.7  | _            | -    | μs    |

| Data Hold Time (Note)                                            | t <sub>HD; DAT</sub> | 0    | -            |      | μ\$   |

| Data Setup Time                                                  | t <sub>SU; DAT</sub> | 250  | -            | -    | ns    |

| SDA, SCL Rise Time                                               | t <sub>R</sub>       | -    | _            | 1    | μS    |

| SDA, SCL Fall Time                                               | t <sub>F</sub>       | -    | _            | 300  | ns    |

| Stop Condition Setup Time                                        | ŧ <sub>su; sто</sub> | 4.7  | _            | -    | μs    |

| Output Data Delay Time                                           | t <sub>DD</sub>      | -    | _            | 300  | ns    |

| Output Data Hold Time                                            | t <sub>DH</sub>      | -    |              | 300  | ns    |

| Write Cycle Time                                                 | t <sub>P</sub>       |      | _            | 20   | ms    |

| Erase / Write Cycle                                              | N <sub>EW</sub>      | 105  | _            | _    | Cycle |

| Data Retention Time                                              | t <sub>RET</sub>     | 10   |              |      | Years |

Note: Hold the data at least for the SCL fall time (max. 300ns).

## A.C. CHARACTERISTICS TIMING DIAGRAMS

170991

9097249 0028481 310

# INPUT/OUTPUT CIRCUITRY

| PIN NAME              | 1/0   | CIRCUITRY | REMARKS          |

|-----------------------|-------|-----------|------------------|

| A0<br>A1<br>A2<br>SCL | Input |           |                  |

| TEST                  | Input |           | Hysteresis input |

| SDA                   | 1/0   |           | Sink open drain  |

170991

5-24

9097249 0028482 257 📟