## LED LAMPS CLUSTER DRIVER

- FULLY MONOLITHIC FIXED FREQUENCY SMPS

- THREE LOW SIDE DRIVERS FOR STOP TAIL AND TURN LED LAMPS ARRAYS DRIVING

- PROGRAMMABLE LOW SIDE DRIVER OVER CURRENT LIMIT PROTECTION

- UNDER CURRENT DIAGNOSTIC

- INPUT OVERVOLTAGE PROTECTION

- VERY LOW STAND-BY CURRENT

- THERMAL PROTECTION WITH HYSTERESIS

#### **DESCRIPTION**

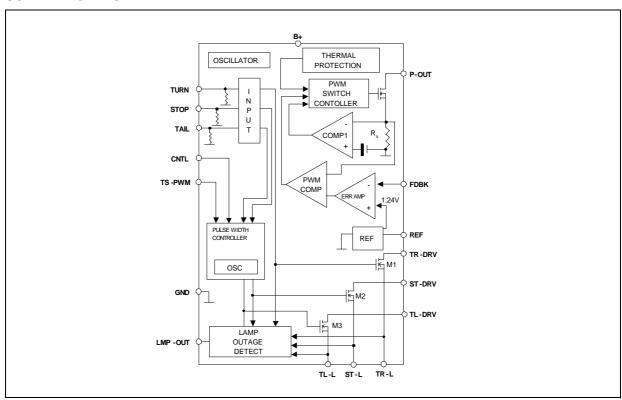

The STLC1, a device realized with the well established BCD technology, is a fixed frequency fully monolithic SMPS, with three independent smart low side driver, primarily intended for automotive rear led lamps driving.

The output voltage is set using a simple resistor divider. Thermal shutdown with hysteresis, input over-voltage and overcurrent protections give robust design solutions.

#### **SCHEMATIC DIAGRAM**

September 2002 1/16

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                                              | Parameter                                   | Value                 | Unit |

|---------------------------------------------------------------------|---------------------------------------------|-----------------------|------|

| V <sub>B+</sub>                                                     | Transient Supply Voltage (load dump)        | 60                    | V    |

| V <sub>B+</sub>                                                     | Operating Supply Voltage                    | 24                    | V    |

| V <sub>TURN,</sub><br>V <sub>STOP,</sub><br>V <sub>TAIL</sub>       | TURN, STOP and TAIL input pins voltage      | V <sub>B+</sub> + 0.3 | V    |

| I <sub>TURN,</sub><br>I <sub>STOP,</sub><br>I <sub>TAIL</sub>       | TURN, STOP and TAIL pins current            | ± 10                  | mA   |

| I <sub>TR-DRV,</sub><br>I <sub>TL-DRV,</sub><br>I <sub>ST-DRV</sub> | TR-DRV, TL-DRV and ST-DRV pins sink current | 1.5                   | A    |

| I <sub>LMP-OUT</sub>                                                | LMP-OUT pin sink current                    | 120                   | mA   |

| V <sub>P-OUT</sub>                                                  | P-OUT DC Voltage                            | 60                    | V    |

| I <sub>P-OUT</sub>                                                  | P-OUT pin sink current                      | Internally Limited    | А    |

| T <sub>stg</sub>                                                    | Storage Temperature Range                   | -55 to +150           | °C   |

| $T_J$                                                               | Operating Junction Temperature Range        | -40 to +125           | °C   |

#### THERMAL DATA

| Symbol                | Parameter                           | PowerSO-20 <sup>TM</sup> | Unit |

|-----------------------|-------------------------------------|--------------------------|------|

| R <sub>thj-case</sub> | Thermal Resistance Junction-case    | 2                        | °C/W |

| R <sub>thj-amb</sub>  | Thermal Resistance Junction-Ambient | 50                       | °C/W |

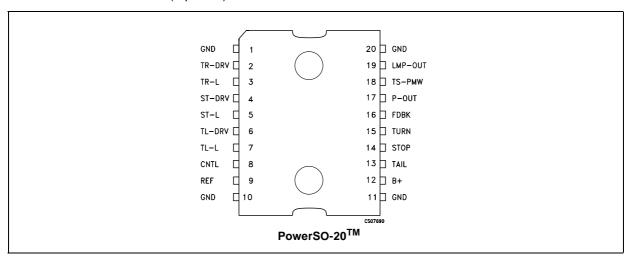

## **CONNECTION DIAGRAM** (top view)

## **PIN DESCRIPTION**

| Pin N° | Symbol  | Name and Function                                                                                                       |  |

|--------|---------|-------------------------------------------------------------------------------------------------------------------------|--|

| 1      | GND     | Ground                                                                                                                  |  |

| 2      | TR-DRV  | The Low Side Driver drain pin for the TURN LED array                                                                    |  |

| 3      | TR-L    | The Low Side Driver source pin, used to detect either a lamp outage or an over-current condition for the TURN LED array |  |

| 4      | ST-DRV  | The Low Side Driver drain pin for the STOP LED array                                                                    |  |

| 5      | ST-L    | The Low Side Driver source pin, used to detect either a lamp outage or an over-current condition for the STOP LED array |  |

| 6      | TL-DRV  | The Low Side Driver drain pin for the TAIL LED array                                                                    |  |

| 7      | TL-L    | The Low Side Driver source pin, used to detect either a lamp outage or an over-current condition for the TAIL LED array |  |

| 8      | CNTL    | Determines, according to a percentange of VREF, the Pulse Width Controller internal oscillator duty cycle               |  |

| 9      | REF     | Stable Reference Voltage                                                                                                |  |

| 10     | GND     | Ground                                                                                                                  |  |

| 11     | GND     | Ground                                                                                                                  |  |

| 12     | B+      | Power Supply                                                                                                            |  |

| 13     | TAIL    | TAIL input pin. When brought high, TAIL activates the IC and drives the TAIL led array.                                 |  |

| 14     | STOP    | STOP input pin. When brought high, STOP activates the IC and drives the STOP led array.                                 |  |

| 15     | TURN    | TURN input pin. When brought high, TURN activates the IC and drives the TURN led array.                                 |  |

| 16     | FDBK    | Internal Error Amplifier Inverting Pin                                                                                  |  |

| 17     | P-OUT   | Power MOSFET drain pin                                                                                                  |  |

| 18     | TS-PWM  | A Three State Input. It determine the control logic for TAIL and STOP Low Side Drivers.                                 |  |

| 19     | LMP-OUT | A weak pulled up signal during lamps No Fault condition and an active pulldown when a Fault condition is detected.      |  |

| 20     | GND     | Ground                                                                                                                  |  |

## ORDERING INFORMATION

| TYPE  | PowerSO-20 <sup>TM</sup> |  |

|-------|--------------------------|--|

| STLC1 | STLC1PD                  |  |

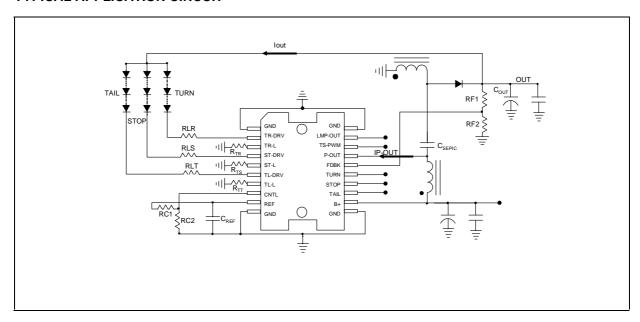

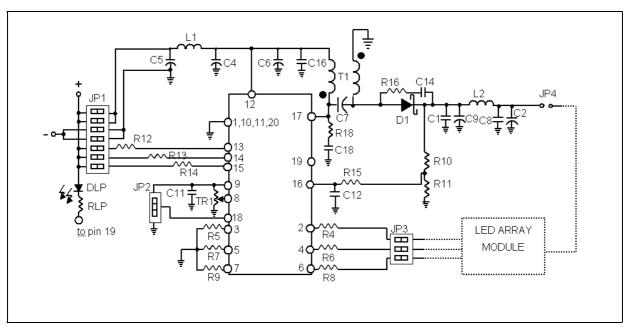

#### **TYPICAL APPLICATION CIRCUIT**

**ELECTRICAL CHARACTERISTICS FOR SMPD SECTION** ( $T_J$ =-40 to 125°C unless otherwise specified. Typical values are referred at  $T_J$ =25°C,  $V_{B+}$ =14V)

| Symbol               | Parameter                            | Test Conditions                                                 | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------|-----------------------------------------------------------------|------|------|------|------|

| V <sub>B+</sub>      | Supply Operating Voltage             | Normal Operating Range                                          | 9    |      | 24   | V    |

|                      |                                      | Normal Operating Range - TAIL only                              | 6    |      | 24   |      |

| V <sub>SD</sub>      | B+ Input Overvoltage<br>Shutdown     |                                                                 | 28   | 30   | 32   | V    |

| I <sub>SQ</sub>      | Total Off State Quiescent<br>Current | $V_{B+} = 14V$ , $V_{TURN} = V_{STOP} = V_{TAIL}$<br>=0V        |      | 120  | 180  | μА   |

| f <sub>osc</sub>     | PWM Oscillator Frequency             | V <sub>B+</sub> = 14V                                           | 140  | 180  | 240  | kHz  |

| R <sub>P(on)</sub>   | Static drain to ground               | $V_{B+} = 9V$ , $I_{P-OUT} = 4A$                                |      | 180  |      | mΩ   |

|                      | SMPS N-channel switch on resistance  | $V_{B+} = 14V$ , $I_{P-OUT}=4A$                                 |      | 170  |      | mΩ   |

| I <sub>D(off)</sub>  | P-OUT Off State leakage<br>Current   | V <sub>B+</sub> = 16V,                                          |      |      | 20   | μА   |

| I <sub>LIMIT</sub>   | I <sub>P-OUT</sub> Current Limit     | V <sub>B+</sub> = 14V, V <sub>FDBK</sub> = 1V                   | 8    | 12   | 16   | Α    |

| t <sub>SMPS-ON</sub> | SMPS Turn On Delay                   | $C_{REF} = 1\mu F$ (see note 1,4 and Fig 1, 2)                  |      | 1.6  |      | ms   |

| $V_{LOAD}$           | Load Regulation                      | $V_{B+} = 14V$ , $I_{OUT} = 0.6$ to 3A<br>$V_{OUT} = 10V$       |      | 60   |      | mV   |

| V <sub>LINE</sub>    | Line Regulation                      | $V_{B+} = 9 \text{ to } 16V, I_{OUT} = 1.5A$<br>$V_{OUT} = 10V$ |      | 15   |      | mV   |

# **ELECTRICAL CHARACTERISTICS FOR LOW SIDE DRIVER SECTION** ( $T_J$ =-40 to 125°C unless otherwise specified. Typical values are referred at $T_J$ =25°C, $V_{B+}$ =14V)

| Symbol                | Parameter                                                  |                                                                                          | Test Conditions                                          | Min. | Тур.                | Max. | Unit |

|-----------------------|------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------|------|---------------------|------|------|

| R <sub>(on)</sub>     | Static drain to source LSD<br>N-channel switch on          | V <sub>B+</sub> = 9V,                                                                    | $V_{TURN} = V_{B+} V_{TR-L} = 0V$<br>$I_{TR-DRV} = 1A$   |      | 500                 |      | mΩ   |

|                       | resistance                                                 |                                                                                          | $V_{STOP} = V_{B+} V_{ST-L} = 0V$<br>$I_{ST-DRV} = 1A$   |      | 500                 |      | mΩ   |

|                       |                                                            |                                                                                          | $V_{TAIL} = V_{B+}$ $V_{TL-L} = 0V$<br>$I_{TL-DRV} = 1A$ |      | 500                 |      | mΩ   |

| I <sub>LSD(off)</sub> | OFF State LSD'S leakage current                            | $V_{TURN} = V_{STOP} = V_{TAIL} = 0V$<br>$V_{TR-DRV} = V_{ST-DRV} = V_{TL-DRV} = V_{B+}$ |                                                          |      |                     | 10   | μΑ   |

| t <sub>LSD-ON</sub>   | LSD Turn On Delay                                          | $C_{REF} = 1 \mu F$ $C_{OUT} = 220 \mu F$ (see note 2,4 and Fig 1, 2)                    |                                                          |      | 2                   |      | ms   |

| V <sub>LS-ON</sub>    | FDBK Voltage over which LSD's are enabled                  |                                                                                          |                                                          |      | 0.95V <sub>FB</sub> |      | ٧    |

| V <sub>LS-OFF</sub>   | FDBK Voltage over which LSD's are disabled                 |                                                                                          |                                                          |      | 0.5V <sub>FB</sub>  |      | >    |

| f <sub>LSD</sub>      | Pulse Width Controller<br>Internal Oscillator<br>Frequency | $V_{TAIL} = V_{B+}$                                                                      | $V_{TS-PWM} = V_{REF}/2$                                 | 200  | 380                 | 500  | Hz   |

| V <sub>IN(ON)</sub>   | Input Threshold voltage to enable LSD                      | $V_{B+} = 9 \text{ to } 10$                                                              | 6V                                                       |      | 0.6V <sub>B+</sub>  |      | V    |

| V <sub>IN(OFF)</sub>  | Input Threshold voltage to disable LSD                     | $V_{B+} = 9 \text{ to } 10$                                                              | 6V                                                       |      | 0.4V <sub>B+</sub>  |      | V    |

## **ELECTRICAL CHARACTERISTICS FOR FEEDBACK AND CONTROL** ( $T_J$ =-40 to 125°C unless otherwise specified. Typical values are referred at $T_J$ =25°C, $V_{B+}$ =14V)

| Symbol                 | Parameter                                                         | Test Conditions                                                                            | Min.                 | Тур. | Max.                 | Unit        |

|------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------|------|----------------------|-------------|

| V <sub>LOUT</sub>      | Lamp Outage Detect<br>Threshold Voltage                           | T <sub>J</sub> =25°C                                                                       | 150                  | 200  | 250                  | mV          |

| V <sub>H-SHORT</sub>   | Output Overcurrent<br>Threshold Voltage                           | T <sub>J</sub> =25°C                                                                       | 1.2                  | 1.3  | 1.6                  | ٧           |

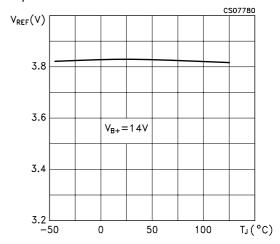

| V <sub>REF</sub>       | External Voltage<br>Reference                                     | $V_{TURN} = V_{STOP} = V_{TAIL} = V_{B+}$<br>$I_{REF} = 500\mu A$                          | 3.6                  | 3.8  | 4                    | V           |

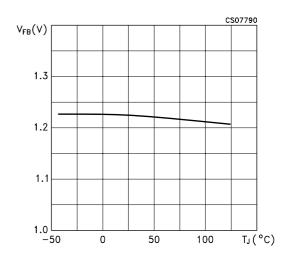

| V <sub>FB</sub>        | Internal Band-gap Voltage<br>Reference (see schematic<br>diagram) | $V_{TURN} = V_{STOP} = V_{TAIL} = V_{B+}$                                                  | 1.15                 | 1.24 | 1.3                  | V           |

| V <sub>LH(en)</sub>    | Device Enabled Lamp<br>Outage no fault High<br>Voltage            | $V_{B+} = 9$ to 16V, $I_{LMP-OUT} < -4$ mA At least one input enabled. No fault condition. | V <sub>B+</sub> -2   |      | V <sub>B+</sub>      | V           |

| V <sub>LH(dis)</sub>   | Device Disabled Lamp<br>Outage no fault High<br>Voltage           | $V_{B+} = 9$ to 16V, $I_{LMP-OUT} < -2mA$<br>$V_{TURN} = V_{STOP} = V_{TAIL} = 0V$         | V <sub>B+</sub> -2   |      | V <sub>B+</sub>      | V           |

| V <sub>LL</sub>        | Lamp Outage fault Low<br>Voltage                                  | $V_{B+} = 9$ to 16V $I_{LMP-OUT} < 100$ mA At least one input enabled. Fault condition.    |                      | 1.5  |                      | V           |

| R <sub>(IN)</sub>      | TURN, STOP and TAIL Input Resistance                              | V <sub>B+</sub> = 12V,                                                                     |                      | 18.5 |                      | kΩ          |

| T <sub>SHDN</sub>      | Thermal Shutdown<br>Threshold                                     | (see Note 4)                                                                               |                      | 150  |                      | ç           |

| T <sub>HYST</sub>      | Thermal Shutdown<br>Hysteresis                                    | (see Note 4)                                                                               |                      | 10   |                      | ç           |

| t <sub>F(on)</sub>     | Time to Fault Indication ON                                       |                                                                                            |                      | 60   |                      | μs          |

| t <sub>F(off)</sub>    | Time to Fault Indication OFF                                      |                                                                                            |                      | 8    |                      | ms          |

| V <sub>TS-PWM(L)</sub> | TS-PWM Low State<br>Voltage (see table 1)                         |                                                                                            |                      |      | 0.1V <sub>REF</sub>  | <b>&gt;</b> |

| V <sub>TS-PWM(M)</sub> | TS-PWM Mid State<br>Voltage (see table 1)                         |                                                                                            | 0.21V <sub>REF</sub> |      | 0.79V <sub>REF</sub> | V           |

| V <sub>TS-PWM(H)</sub> | TS-PWM High State<br>Voltage (see table 1)                        |                                                                                            | 0.98V <sub>REF</sub> |      |                      | V           |

Note 1: The device is powered. If only one of the three inputs is enabled (the remaining inputs are shorted to ground),  $t_{SMPS-ON}$  is the time required for the OUT voltage to reach the 10% of its own steady state value

#### **FUNCTIONAL DESCRIPTION**

#### **SMPS**

The N-channel Power MOSFET is source grounded, thus it is possible to use any converter configuration with the power switch connected to ground. A SEPIC topology (Single Ended Primary Inductor Current) is shown in the typical application schematic.

#### **INPUTS PINS**

The IC's inputs are TURN, STOP and TAIL. If all inputs are disabled, SMPS and most of the  $\,$

internal control and diagnostic circuitry are not active. This is done in order to maintain the stand-by quiescent current at very low values.

When only one of these inputs is put high (e.g connected to  $V_{B+}),\; a$  device start-up phase begins. First the  $C_{REF}$  capacitor is charged and, once the voltage on it has reached about 95% of its steady state value ( $V_{REF}),\; the$  SMPS is enabled. In order to allow the output to reach the regulated voltage value faster, the LSD corresponding to the input enabled will conduct

Note 2: The device is powered. If only one of the three inputs is brought high (the remaining inputs are shorted to ground), T<sub>LSD-ON</sub> is the time required for the current to flow in the enabled LSD

Note 3: The device is powered and at least one input is enabled. If this input is disabled, T<sub>LSD-OFF</sub> is the time required for the current to become zero in the previously enabled LSD.

Note 4: Guaranteed by design, not tested in production.

only when the OUT voltage is about 95% of its final value. Such a start-up phase takes place when only one input is enabled.

#### LOW SIDE DRIVER:

The purpose of the low side drivers is to connect the LED cluster to ground, creating a path for the current. Using external resistors, current flowing into the LED cluster is set according to the following formula:

$$I_{ARRAY} = \frac{V_{OUT} - V_{ARRAY}}{R_T + R_L + R_{(on)}}$$

where (see typical application schematic):

$R_L = R_{LT}, R_{LS}, or R_{LR}$

$R_T = R_{TT}$ ,  $R_{TS}$ , or  $R_{TR}$

$R_{(on)}$  = Static drain to source LSD on resistance  $V_{OUT}$  = Output Voltage

V<sub>ARRAY</sub> = Expected LED array voltage drop.

LSD over-current protection and under-current diagnostic (see LAMP OUTAGE DETECTION section) is performed by sensing the voltage on resistors, when the corresponding LSD are enabled.

If the voltage on exceeds  $V_{\text{H-SHORT}}$ , the over-current protection acts by reducing the LSD average current by switching ON and OFF the LSD itself.

#### LAMP OUTAGE DETECTION

Resistors are used to sense the LED array current. In case one or more LEDs fail (open circuit) the current on the corresponding resistor will drop due to the increased LED array resistance. As soon as the voltage drop on is lower than  $V_{L\,O\,LT}$ , a LED lamp fault condition is

detected and the LMP-OUT pin becomes active (low). The LAMP-OUTAGE functionality is AND-ed with each input, that is a fault condition can be detected only when the LED arrays are enabled.

#### **DIMMING**

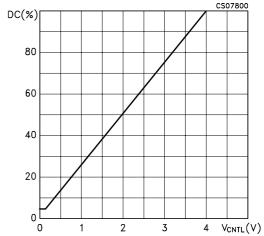

The dimming of the LED lamps can be obtained by using the internal PULSE WIDTH controller (it drives the LSD TAIL and STOP gates). The duty cycle of this internal oscillator (whose frequency is 380Hz typical) can be set, forcing the voltage of the CNTL pin to be a fraction of  $V_{REF}$ , by using a simple resistor divider (as shown in the typical application scheme).

In this case the duty cycle percentage can be calculated with the following approximated formula:

$$DC\% \cong \left( \begin{array}{c} 3.8 \text{ if } \frac{R_{C1}}{R_{C1} + R_{C2}} \leq \frac{0.2}{V_{REF}} \\ \frac{R_{C1}}{R_{C1} + R_{C2}} \bullet 100 \text{ Elsewhere} \end{array} \right)$$

The TS-PWM pin voltage, according to the TABLE1 determines which LSD is PULSE WIDTH CONTROLLER driven. Internal dimming can only be performed on the TAIL and STOP arrays. The TURN array can be externally dimmed (as well as TAIL and STOP) by driving the corresponding input witha a square pulse signal whose maximum frequency must be 200Hz.

#### **TS-PWM ENCODING TABLE**

| TYPE                                                  | INPUTS ACTIVATED | DRIVE TYPE |           |  |

|-------------------------------------------------------|------------------|------------|-----------|--|

| ITPE                                                  | INPUIS ACTIVATED | TAIL ARRAY | STOP ARRY |  |

| LOW                                                   | TAIL             | PWM        | PWM       |  |

| LOW<br>(V <sub>TS-PWM</sub> <0.1V <sub>REF</sub> )    | STOP             | OFF        | ON        |  |

| (* IS-PWM \O. I * REF)                                | TAIL AND STOP    | PWM        | ON        |  |

| MID                                                   | TAIL             | PWM        | OFF       |  |

| MID $(V_{TS-PWM} < 0.1V_{REF}/2 \text{ or floating})$ | STOP             | OFF        | ON        |  |

| (* 18-PWM 10.11 REF/2 01 Hoading)                     | TAIL AND STOP    | PWM        | ON        |  |

| HICH                                                  | TAIL             | PWM        | PWM       |  |

| HIGH<br>(V <sub>TS-PWM</sub> >0.98V <sub>REF</sub> )  | STOP             | ON         | ON        |  |

| (* 12-500M- 2:20 4 KEE)                               | TAIL AND STOP    | ON         | ON        |  |

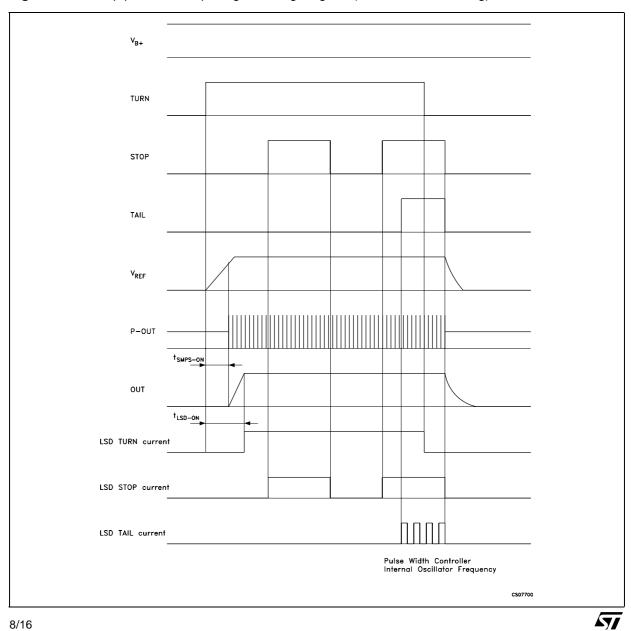

Figure 1 : Start-up phase and input signal timing diagram (with TS-PWM floating)

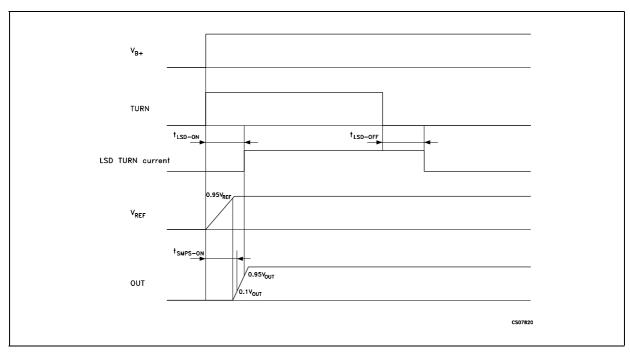

Figure 2: Magnified start-up phase timing diagram

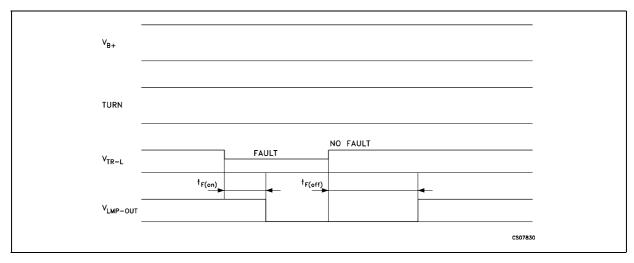

Figure 3: Fault indication on and off timing diagram

#### TYPICAL CHARACTERISTICS (See PCB BOM)

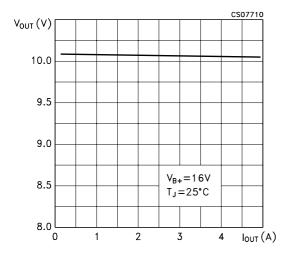

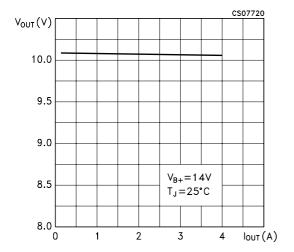

Figure 4 : Output Voltage vs Output Current

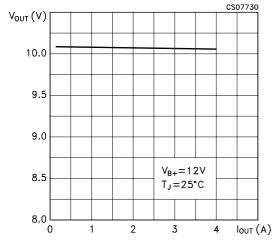

Figure 5 : Output Voltage vs Output Current

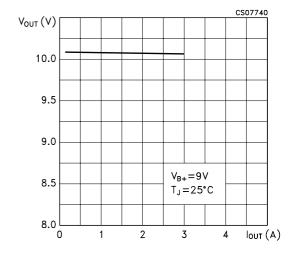

Figure 6 : Output Voltage vs Output Current

Figure 7 : Output Voltage vs Output Current

**Figure 8 :** Duty Cycle Oscillator Frequency vs CNTL Voltage

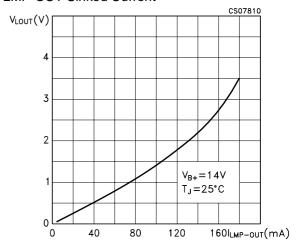

**Figure 9 :** LMP-OUT Voltage (Fault Condition) vs LMP-OUT Sinked Current

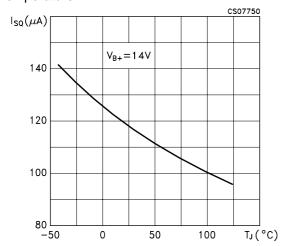

**Figure 10 :** Total OFF State Quiescent Current vs Temperature

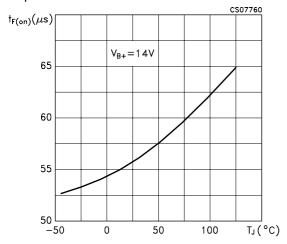

**Figure 11 :** Time to Fault Indication ON vs Temperature

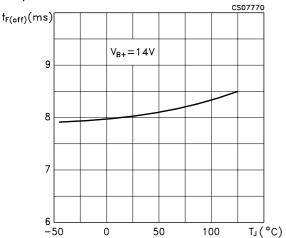

**Figure 12 :** Time to Fault Indication OFF vs Temperature

**Figure 13 :** External Reference Voltage vs Temperature

Figure 14 : V<sub>FB</sub> Voltage vs Temperature

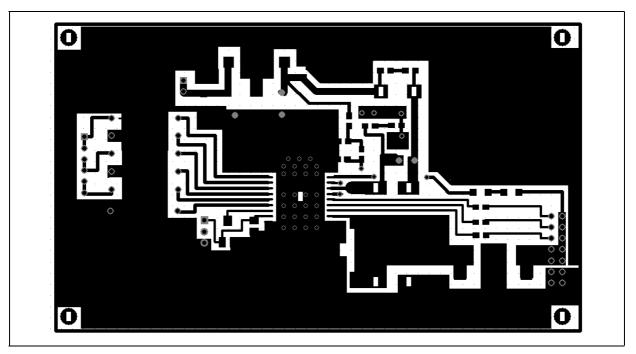

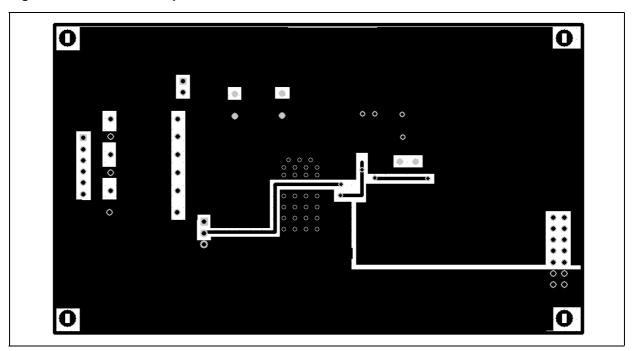

Figure 15: Demoboard Schematic

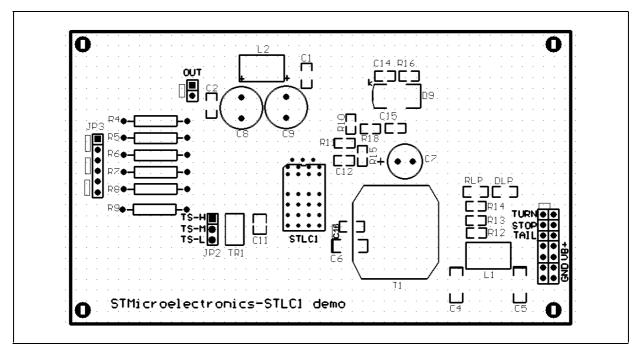

Figure 16: PCB Components outline

Figure 17: PBC Top Layer

Figure 18: PBC Bottom Layer

## **PCB BOM**

| REFERENCE     | DESCRIPTION                                                  |

|---------------|--------------------------------------------------------------|

| L1, L2        | VK200                                                        |

| C4, C5, C6    | 22μF-35V Electrolytic Capacitor Low ESR                      |

| C16           | 220nF-35V Ceramic Capacitor X7R Dielectric                   |

| C7            | 47μF-35V Electrolytic Capacitor                              |

| C1, C2        | 4.7nF-35V Ceramic Capacitor X7R Dielectric                   |

| C8, C9        | 220μF-35V Electrolytic Capacitor Low ESR                     |

| C14           | 560pF                                                        |

| C18           | 560pF-50V                                                    |

| C11           | 1μF-35V Tantalium Capacitor                                  |

| C12           | 220pF Ceramic Capacitor                                      |

| R10           | 9.1kΩ Resistor 125mW 0.1%                                    |

| R11           | 1.3kΩ Resistor 125mW 0.1%                                    |

| R15           | 4.7kΩ Resistor 125mW 5%                                      |

| R16           | 56Ω Resistor 125mW 5%                                        |

| R18           | 10Ω Resistor 250mW 5%                                        |

| R12, R13, R14 | 1.2kΩ Resistor 125mW 5%                                      |

| R4, R6, R8    | 2.2Ω Resistor 1W 5%                                          |

| R5, R7, R9    | 1Ω Resistor 1W 5%                                            |

| TR1           | 10kΩ Trimmer                                                 |

| RLP           | 1.5kΩ Resistor 125mW 5%                                      |

| D1            | Schottky Diode STPS3L40S                                     |

| DLP           | Led Diode                                                    |

| T1            | SEPIC inductor, Toroid Horizontal THT 20μH@10ADC, 200-250KHz |

| JP1, JP2, JP3 | Jumper                                                       |

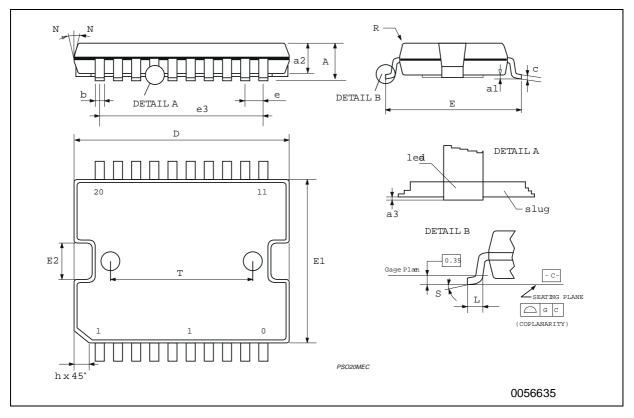

## **PowerSO-20 MECHANICAL DATA**

| DIM.   |       | mm.   |       |        | inch   |        |

|--------|-------|-------|-------|--------|--------|--------|

| DIWI.  | MIN.  | TYP   | MAX.  | MIN.   | TYP.   | MAX.   |

| Α      |       |       | 3.60  |        |        | 0.1417 |

| a1     | 0.10  |       | 0.30  | 0.0039 |        | 0.0118 |

| a2     |       |       | 3.30  |        |        | 0.1299 |

| a3     | 0     |       | 0.10  | 0      |        | 0.0039 |

| b      | 0.40  |       | 0.53  | 0.0157 |        | 0.0209 |

| С      | 0.23  |       | 0.32  | 0.0090 |        | 0.0013 |

| D (1)  | 15.80 |       | 16.00 | 0.6220 |        | 0.630  |

| Е      | 13.90 |       | 14.50 | 0.5472 |        | 0.5710 |

| е      |       | 1.27  |       |        | 0.0500 |        |

| e3     |       | 11.43 |       |        | 0.4500 |        |

| E1 (1) | 10.90 |       | 11.10 | 0.4291 |        | 0.4370 |

| E2     |       |       | 2.90  |        |        | 0.1141 |

| G      | 0     |       | 0.10  | 0.0000 |        | 0.0039 |

| h      |       |       | 1.10  |        |        | 0.0433 |

| L      | 0.80  |       | 1.10  | 0.0314 |        | 0.0433 |

| N      |       |       | 10°   |        |        | 10°    |

| S      | 0°    |       | 8°    | 0°     |        | 8°     |

| Т      |       | 10.0  |       |        | 0.3937 |        |

(1) "D and E1" do not include mold flash or protusions - Mold flash or protusions shall not exceed 0.15mm (0.006")

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

© The ST logo is a registered trademark of STMicroelectronics

© 2002 STMicroelectronics - Printed in Italy - All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco Singapore - Spain - Sweden - Switzerland - United Kingdom - United States. © http://www.st.com