**NOVEMBER 1996**

PRELIMINARY INFORMATION

DS4032 1.6

# SL1711 QUADRATURE DOWNCONVERTER

The SL1711 is a quadrature downconverter, intended primarily for application in professional and consumer digital satellite tuners.

IIII GEC PLESSEY

SEMICONDUCTORS

The device contains all elements necessary, with the exception of external local oscillator tank to form a complete system operating at standard satellite receiver intermediate frequencies. It is intended for use with external carrier recovery.

The device includes a low noise RF input amplifier, a reference VCO with prescaler output buffer and In-phase and Quadrature mixers with baseband buffer amplifiers containing AGC gain control.

The SL1711 is optimised to drive a dual ADC converter such as the VP216.

# FEATURES

- Single chip system for wideband quadrature downconversion

- Compatible with all standard high IF frequencies

- Excellent gain and phase match up to 30MHz baseband

- High output referred linearity for low distortion and multi channel application

- Simple low component application

- Fully balanced low radiation design with fully integrated quadrature generation

- High operating input sensitivity

- On-board AGC facility

- Varactor tuned VCO with prescaler for control of external synthesis loop

- ESD protection (Normal ESD handling procedures should be observed)

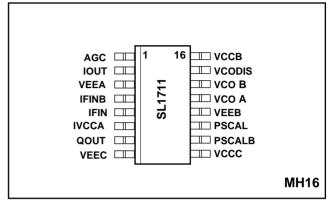

Fig. 1 Pin allocation

# **APPLICATIONS**

- Satellite receiver systems

- Data communications systems

- Cable systems

# **ORDERING INFORMATION**

SL1711/KG/MH1P (Sticks) SL1711/KG/MH1Q (Tape and Reel)

# QUICK REFERENCE DATA

| Characteristic                      | Value | Units  |

|-------------------------------------|-------|--------|

| Input noise figure, DSB             | 17    | dB     |

| Maximum conversion gain             | 44    | dB     |

| Minimum conversion gain             | 28    | dB     |

| $IP3_{2T}$ output referred          | +8    | dBV    |

| Output clip voltage                 | 1.5   | Vp-р   |

| Gain match up to 22MHz              | ± 0.3 | dB     |

| Gain match up to 30MHz              | + 0.5 | dB     |

| Phase match up to 30MHz             | ± 1.5 | deg    |

| Gain flatness up to 30MHz           | ± 0.5 | deg    |

| VCO phase noise, SSB @ 10kHz offset | - 96  | dBc/Hz |

| Prescaler division ratio            | 32    |        |

| Prescaler output swing              | 1.6   | Vp-р   |

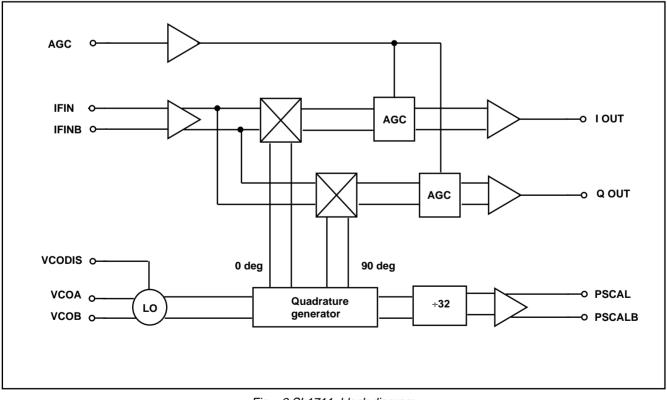

Fig. 2 SL1711 block diagram

# FUNCTIONAL DESCRIPTION

The SL1711 is a wideband quadrature downconverter, optimised for application in both professional and consumer digital satellite receiver systems and requiring a minimum external component count. It contains all the elements required for construction of a quadrature demodulator, with the exception of tank circuit for the local oscillator.

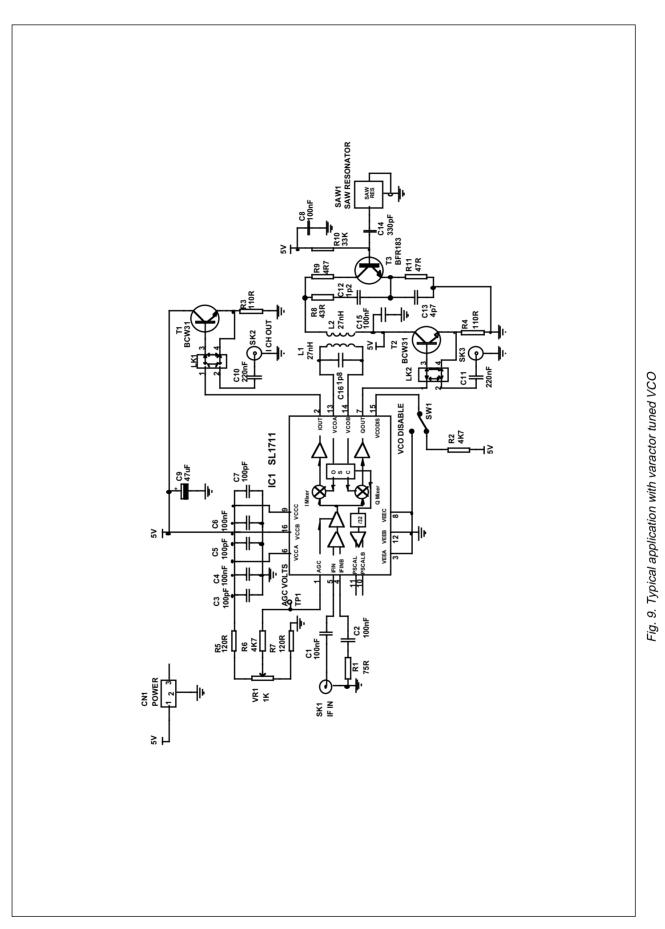

A block diagram is contained in Fig. (2) and a typical application with varactor tuned LO in Fig. (3).

The 1711 can also be used with a SAW resonator controlled oscillator; in this case an external oscillator transistor is required, which is buffered in to the SL1711 VCO pins. A recommended SAW resonator application is contained in Fig.(9).

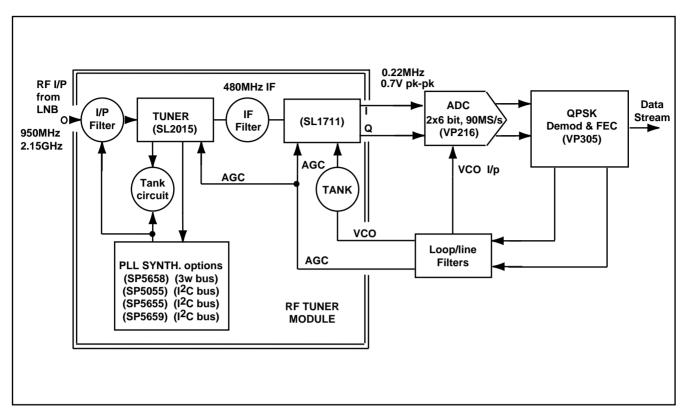

A typical digital satellite tuner application from tuner input to data transport stream is shown in Fig. (10)

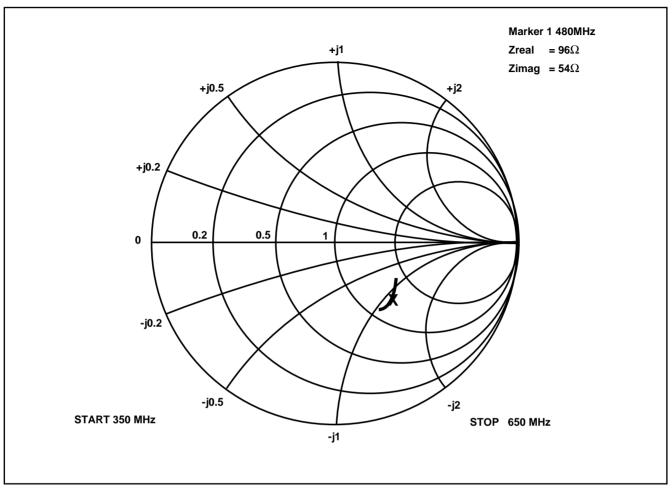

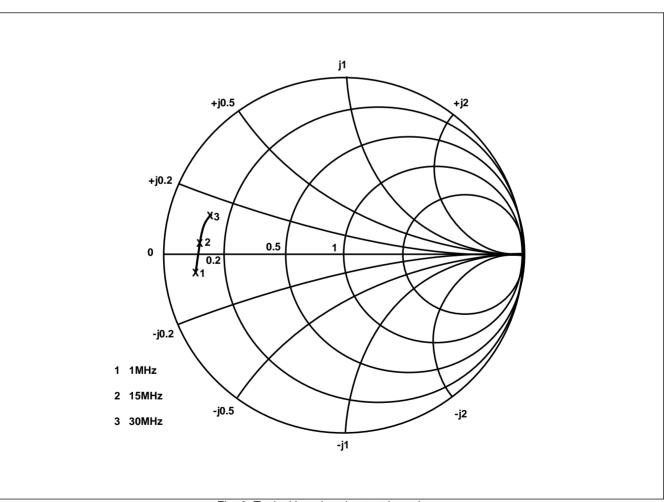

In normal application the second satellite IF frequency of typically 402.75 or 479.5 MHz is fed from the tuner SAW filter to the RF preamplifier, which is optimised for impedance match and signal handling. The amplifier output signal is then split into two balanced channels to drive the In-phase and Quadrature mixers. The typical RF input impedance is shown in Fig. (4)

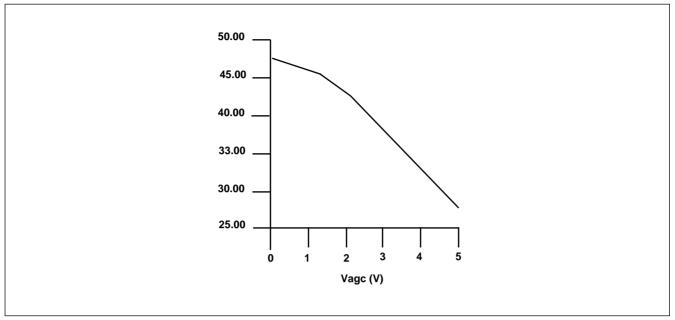

In-phase and Quadrature LO signals for the mixers are derived from the on board local oscillator, which uses an external varactor tuned resonant network and is optimised for low phase noise. The VCO also drives an on board divide by 32 prescaler whose outputs can be used for driving an external PLL control loop for the VCO, where the PLL loop is contained within the QPSK demodulator, for example the VP305. For optimum performance in the varactor tuned application the VCO should be fully symmetric. The VCO has a disable facility by grounding pin 15, VCODIS; in normal application this pin is pulled to Vcc via a 4K7 resistor. The mixer outputs are fed to balanced baseband AGC amplifier stages, which provide for a minimum of 16 dB of AGC control. The typical AGC characteristic is shown in Fig. (5).

These amplifiers then feed a low output impedance true differential to single-ended converter output stage. In normal application the output can be either directly AC coupled to the ADC converter such as the VP216, which will generally have a high input impedance, or to drive an anti alias filter. In this later case the maximum load presented to the SL1711 must not exceed a parallel combination of  $1K\Omega$  and 20pF. The typical baseband output impedance is contained in Fig. (6).

It is recommended that the device is operated with an output amplitude of 760mV under lock conditions.

Under transient conditions the output should not exceed the clipping voltage.

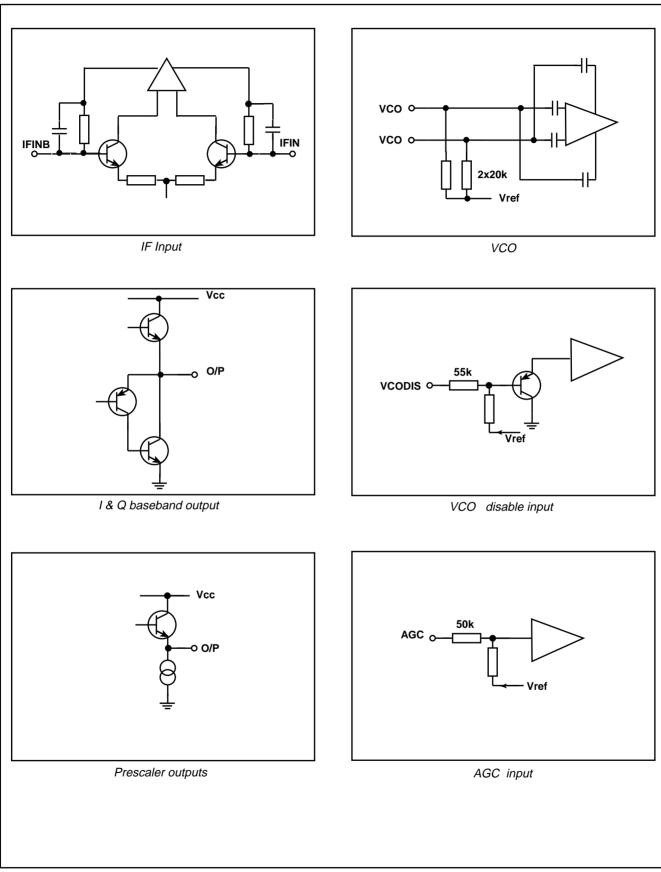

Input and output interface circuitry is contained in Fig. (7).

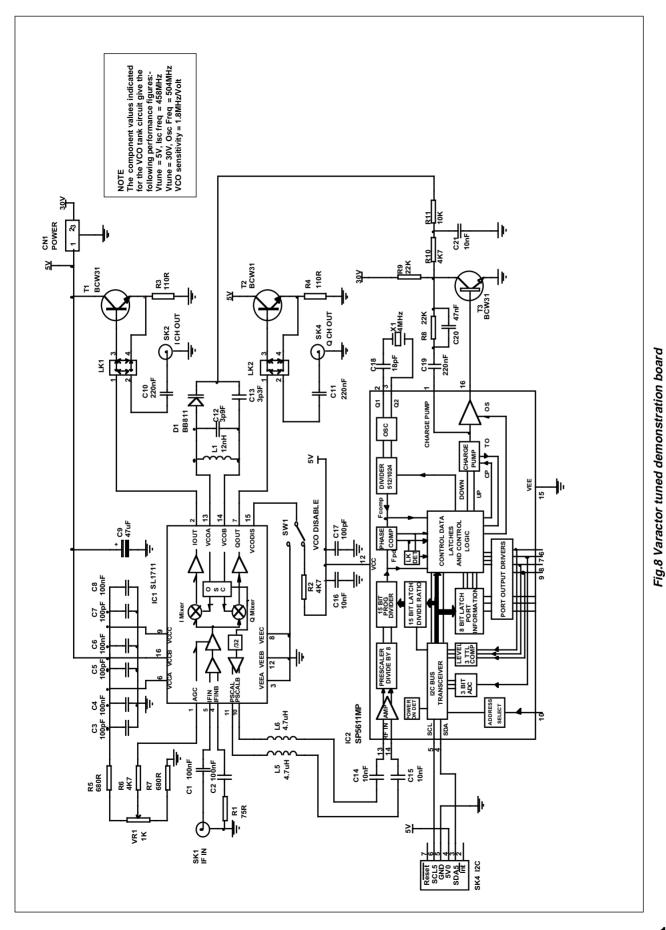

An application description for both SAWR and varactor tuned VCO, accompanying Fig. (8) and (9), are contained in section titled 'APPLICATION NOTES'.

The typical key performance numbers at 480 MHz IF, 5V Vcc, 1 k $\Omega$  load and 25 deg C ambient are contained in table headed ('QUICK REFERENCE DATA'). With SAWR oscillator application the gain and phase match performance will typically exceed these numbers.

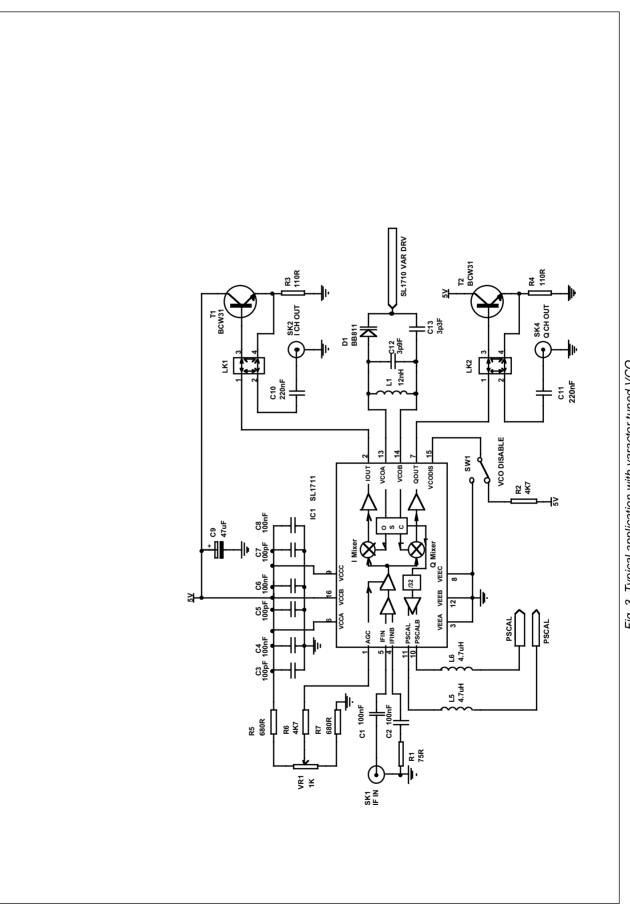

Fig. 3. Typical application with varactor tuned VCO

Fig.4 Typical RF input impedance

Fig.5 Typical AGC characteristic

Fig. 6 Typical baseband output impedance

Fig. 7 I/O port peripheral circuitry

# **APPLICATION NOTES**

These application notes should be read in conjunction with circuit diagrams contained in Fig. (8) and (9), and a recommended front end tuner solution contained in Fig. (10). These boards have been designed to demonstrate performance and to allow for initial evaluation of the SL1711.

## **Oscillator (varactor tuned)**

This application uses a synthesised VCO with a tuning range of 460 MHz to 500 MHz. The surface mount inductor L1 is 12 nH. The VCO frequency is controlled by the SP5611 synthesiser which is programmed via an  $I^{2}C$  bus. The RF input to the synthesiser is from the SL1711 prescaler outputs coupled via RF inductors L3 and L4.

For functional checking the VCO can be tuned by physically shorting the base of transistor T3 to ground and then adjusting the +30 volt supply to tune the VCO. Under these conditions, due to the unlocked state of the LO, the board WILL NOT BE representative of locked gain and phase match or phase noise performance.

In real applications such as in Fig. (3), the VCO control voltage will be provided by the QPSK demodulator circuit, such as the VP305. This circuit provides a line voltage to align the reference LO in the 1711 in both frequency and phase to the centre of the modulation bandwidth, normally 402.75 or 479.5 MHz.

As in all feedback loops the bandwidth of the varactor line must be optimised for the symbol rate of the received modulation.

It is recommended for optimum performance that the VCO application is implemented symmetrically, in presented drive and impedance to the VCO ports, as demonstrated in the evaluation schematic and PCB.

In the recommended application the varactor diodes are referenced to the VCO port DC bias voltages. This limits the minimum tuning voltage on the varactor line to 3V. If lower tuning voltage is required the tank can be AC coupled to the VCO ports by 390pF capacitor and a DC reference voltage for the varactor diodes applied by centre tapping the tank inductors. NB the varactor diodes require a minimum of 1V reverse bias for correct operation.

In real applications the maximum tuning range required for the VCO will be determined by the required lock range of the tuner and the manufacturing tolerance of the tank, assuming the quadrature downconverter section will be alignment free. This tuning range will be typically be much smaller than the demonstration board, which will consequently improve the VCO phase noise performance.

This application can be ported direct to real system implementations. Normal good RF practice must be applied to the layout implementation.

## Prescaler Outputs (varactor tuned VCO)

The VCO frequency divided by 32 is available at the differential prescaler outputs, pins 10 and 11. These enable the VCO frequency to be synthesised by a PLL frequency synthesiser; on the demo board an SP5611 is used for this function however in a real application this function will be provided by the QPSK demodulator function contained in for example the VP305

It is recommended that the prescaler outputs are loaded symmetrically to balance radiation effects.

## **Oscillator (SAWR tuned)**

This application uses a discrete SAWR controlled local oscillator which is buffered in to the VCO ports of the SL1711 and is tuned to 479.5 MHz.

This application can be ported direct to real system implementations. Normal good RF practise must be applied to the layout implementation.

## Prescaler Outputs (SAWR tuned VCO)

The VCO frequency divided by 32 is available at the differential prescaler outputs, pins 10 and 11. Normally these outputs will not be required since the derotation and fine tuning required will be processed by the QPSK demodulator. However these frequencies could be used if required for other system reference frequencies or clocks.

If used it is recommended that the prescaler outputs are loaded symmetrically to balance radiation effects.

#### **VCO** Disable

The on-chip oscillator can be disabled by connecting VCODIS, pin 15, to ground and enabled by connecting to Vcc via a 4k7  $\Omega$  pull up resistor.

# AGC

The AGC facility can be used to control the conversion gain of the SL1711

On the demonstration boards the conversion gain is adjusted by means of a potentiometer, which is set to 2.5V so giving a conversion gain of 38 dB. The voltage adjustment range for the AGC is approximately 1.5 to 3.5 V.

It is important that the AGC voltage minimum does not give a conversion gain of greater than 44dBs otherwise the channel amplitude match may be degradded. In real applications the AGC can be either set at a fixed control voltage or controlled by means of the AGC control signal from the QPSK demodulator dependant on the overall dynamic range requirement of the tuner and it's gain distribution.

# I & Q baseband outputs

The SL1711 offers a greatly improved drive capability over the SL1710 and as such is much less sensitive to the load conditions.

It is still important however to carefully balance the loads presented to the SL1711 to ensure no differential gain or phase degradation is introduced by the load circuits, which will also include effects due to track striplines etc.

For demonstration purposes the output is unsuitable for connection via co-axial cables to standard test equipment, where such equipment is normally 50  $\Omega$  or highly capacitive.

To overcome this problem the outputs of the SL1711 are therefore buffered through emitter followers which are optimised to drive 50  $\Omega$  loads without appreciable degradation in the SL1711 performance. These buffer stages are selectable so enabling the outputs to be loaded directly for interfacing direct with an ADC via a low capacitive link.

In most applications the SL1711 will normally interface direct into the ADC converter such as the VP216, which will present a >1 k $\Omega$  low capacitive load, though it can interface with lower impedances if desired.

The output is optimised for typical drive levels of 760 mVp-p and the onset of clipping is typically > 1.5V.

## SL1711 Evaluation Board

This board has been created to show the operation of the SL1711 I/Q downconverter.

It does not attempt to simulate a real system, since in practice the 479.5MHz IF oscillator on the SL1711 (and the 60MHz clock on the subsequent ADC) would be controlled via the baseband IQ demodulator chip such as the VP305 which follows the dual channel ADC. For simplicity, the VCO is locked using GPS SP5611 synthesiser, controlled via an I2C bus.

For full evaluation, 30V and 5V supplies are necessary.

# Supplies

The board must be provided with the following supplies:

A) 5V for the SL1711 and SP5611 and 30V for the varactor line.

The supply connector is a 3 pin 0.1" pitch pin header. The centre pin of the connector is GND.

Outputs driven into hard clipping can exhibit amplitude decline. AGC loops should be designed to take account of this.

#### **I2C Bus connections**

The board is provided with an RJ11 I2C bus connector which feeds directly to the SP5611 synthesiser.

This connects to a standard 6-way connector cable which is supplied with the I2C/3-wire bus interface box.

#### Input and Output connections

The board is provided with the following connectors:

- A) IF I/P SMA connector (SK1) which is AC coupled to the RF input of the SL1711.

- B) I CH OUT (SK2) and Q CH OUT (SK3) which provide either a buffered or direct baseband output signal from the SL1711 (depending on which way the links LK1 and LK2 are set). The output buffers should be used when driving  $50\Omega$  test equipment or co-axial lines.

#### Links and Switches

The board is provided with the following:

VCO DISABLE switch

This disables the VCO of the SL1711. It does NOT power down the chip.

#### AGC ADJUST potentiometer

The potentiometer sets the AGC input voltage of the SL1711 which controls the gain of the chip. TP1 is provided as a means of monitoring the AGC voltage.

# LK1 and LK2

These are links which may be placed either vertically or horizontally to connect the outputs of the SL1711 either directly or via buffers to the SMA output connectors of the board.

If the links are placed vertically (1-2 and 3-4) the outputs are connected directly.

If the links are placed horizontally (1-3 and 2-4) the ouputs are connected via buffers.

# **Programming of Synthesisers**

A SP5611 synthesiser is used to set the frequency of the SL1711 VCO (480MHz). Since the SL1711 incorporates a divide by 32 the synthesised frequency that the SP5611 must be programmed to is 480/32=15MHz.

## Example

a) To program the SL1711 to 480MHz.

| I2C Byte                             | Hex Code |

|--------------------------------------|----------|

| Byte 1 (address)                     | C2       |

| Byte 2 (programmable divider 8 MSBs) | 00       |

| Byte 3 (programmable divider 8 LSBs) | F0       |

| Byte 4 (control data)                | CE       |

| Byte 5 (port data)                   | 00       |

C2 is the address byte (byte 1).

0F00 is the programmable divider information (bytes 2 and 3).

CE is the control data information (byte 4).

\*\*Note - the programmable divider information should be set to program 480MHz /32 = 15MHz since the SL1711 provides a divide by 32 prescaler output rather than the VCO carrier frequency.

It is not possible to program the VCO to 479.5MHz when using a 7.8125kHz phase comparator frequency. The minimum step size is 7.8125kHz x 8 (RF prescaler inside SP5611) x 32 (SL1711 output prescaler) = 2MHz.

If the reference divider is set to 1024 mode (3.90625kHz phase comparator frequency), the minimum step size will be 1MHz.

This may be achieved by programming the control byte to CC and modifying the programmable divider information for the new step size.

# SL1711 Operation

The SL1711 will mix an IF input with its own local oscillator. This is controlled as above via a SP5611 synthesiser.

Normally the VCO will be set to the same frequency as the IF input, and the signal mixed directly down to baseband.

Alternatively, a CW RF source may be fed into the input of the SL1711 which is deliberately offset from the VCO. By varying the offset from 0-20MHz and monitoring the I and Q channel baseband outputs, the flatness response of the chip/ output filter can be measured.

The SL1711 oscillator may also be disabled by setting the ON-VCO-OFF switch to the OFF position.

An AGC voltage adjust pot marked AGC ADJUST is provided, together with a test point.

# Measurement of Gain and Phase Match.

a) Synthesise the required frequency (480MHz is used in the example above).

b) Connect an RF signal generator to the input.

c)Input a signal which should give an output of approx 0dBm (0.707V p-p), in combination with the appropriate AGC setting.

d) Connect a vector voltmeter to the BUFFERED outputs when using  $50\Omega$  inputs. When using high impedance probes, the direct outputs may be used. Selection of outputs is covered in a paragraph above.

e) CALIBRATE the vector voltmeter and the leads to be used.

The calibration should be performed at the chosen baseband frequency and level for maximum accuracy.

f) Vary the RF input frequency either side of the LO and note the relative I and Q gain and phase reading.

If you experience any difficulties with this board, or require further help, please contact *Robert Marsh* on 01793 518234 or *Fred Herman* on 01793 518423

11

# SL1711 SAW RESONATOR

# **APPLICATION NOTES**

The SL1711 is an I & Q quadrature downconvertor which comprises an IF input amplifier, with AGC control, an on chip oscillator, two mixers and two output amplifiers. In addition the device has a prescaler output which is the on board oscillator frequency divided by 32.

In the standard application the oscillator uses a varactor diode tuned tank circuit which allows fine tuning of the oscillator frequency via a voltage control line. This control voltage is usually derived from the QPSK/FEC decoder (VP305/VP306).

Certain applications do not require this fine tune facility so a fixed frequency application using a SAW resonator has been developed. This application is described below.

## **DESCRIPTION.**

Reference should be made to the circuit diagram (Fig 9) when reading these notes.

The main differences between the circuit shown in figure 1 and the standard SL1711 application are the oscillator and the prescaler outputs. Because the oscillator is operated at a fixed frequency the prescaler outputs are not used.

The oscillator circuit T3, SAW1 and associated components comprise a colpitts oscillator. The inductors L1 and L2 act as a balun providing single ended to balanced differential drive from the oscillator into the VCO pins (13 & 14) of the SL1711.

L1 & L2 can be loosely coupled wound inductors of approximately 27nH inductance, but in this application two chip inductors were used, mounted side by side. The capacitor C16 is used to make L1 resonate at the required VCO frequency, in this instance the frequency is 479.5 MHz.

The resonant frequency of the SAW oscillator is determined by the value of the capacitors C12, C13 and SAW1.

Physical construction of the oscillator should follow good RF procedure with precautions taken to minimise parasitic capacitance effects. If double sided PCB is being used it is advantageous to remove the ground plane that is in close proximity to the oscillator circuitry.

# SETTING UP.

To finalise the values of the components C12 and C13 proceed as follows;

1. Replace the SAW resonator with a resistor of  $22\Omega$  in parallel with a capacitor of 2p7 or 3p3.

2. Monitor the frequency of oscillation of the oscillator using a loosely coupled spectrum analyser. In this instance the frequency should be near to 479.5MHz.

3. Vary the values of C12 and C13 to obtain an output frequency as close as possible to 479.5MHz.

4. Remove the parallel resistor and capacitor combination and replace the SAW resonator.

The oscillator will now operate at the required frequency with a typical accuracy of  $\pm$  a few 10s of KHz.

It is recommended that the final circuit is tested with a selection of SAW resonators to confirm that the required frequency accuracy is obtained. In production no trimming of the capacitors will be required as the frequency of oscillation will be determined by the tolerance of the SAW resonators.

Fig. 10 Example digital front end architecture

Note: All IC's shown in Fig. 5 are available from GPS Plessey Semiconductors.

# **ELECTRICAL CHARACTERISTICS**

Test conditions (unless otherwise stated)

$T_{amb}=0^{O}C$  to  $85^{O}C$ ,  $V_{ee}=0V$ , Vcc = 4.75 to 5.25 V, Fif = 479.5 MHz, IF bandwidth ± 22 MHz, output amplitude -11dBV These characteristics are guaranteed by either production test or design. They apply within the specified ambient temperature and supply voltage unless otherwise stated.

| Characteristic               | Pin    | Min  | Тур  | Max      | Units  | Conditions                      |

|------------------------------|--------|------|------|----------|--------|---------------------------------|

| Supply voltage               | 6,9,16 | 4.75 |      | 5.25     | V      |                                 |

| Supply current               | 6,9,16 |      | 109  | 125      | mA     |                                 |

| IF input operating           | 4, 5   | 350  |      | 650      | MHz    |                                 |

| frequency (1)                |        |      |      |          |        |                                 |

| IF input impedance           | 4, 5   |      | 75   |          | Ω      | Over specified frequency        |

|                              |        |      |      |          |        | operating range, see Fig. 6.    |

| Input return loss            | 4, 5   | 12   |      |          | dB     | Over specified frequency        |

|                              |        |      |      |          |        | operating range, see Fig. 6.    |

| Input noise figure, DSB      | 4, 5   |      | 17   | 19       | dB     | Maximum gain setting            |

| Variation in NF with gain    |        |      |      | 1        | dB/dB  |                                 |

| setting                      |        |      |      |          |        |                                 |

| VCO operation range          |        | 350  |      | 650      | MHz    | Centre frequency and tuning     |

|                              |        |      |      |          |        | range determined by             |

|                              |        |      |      |          |        | application.                    |

| VCO phase noise, SSB         |        |      | 96   | -85      | dBc/Hz | Varactor tuned, determined      |

| @ 10kHz offset               |        |      |      |          |        | by application.                 |

| VCO Vcc sensitivity          |        |      |      | 2E3      | ppm/V  | Free running                    |

| VCO temperature              |        |      |      | 100      | ppm/°C | Uncompensated                   |

| stability                    |        |      |      |          |        | ·                               |

| Prescaler output swing       | 10, 11 | 1.2  | 1.6  |          | Vp-p   |                                 |

| Prescaler output duty        | 10, 11 | 40   | 50   | 60       | %      |                                 |

| cycle                        | -,     | -    |      |          |        |                                 |

| Conversion gain for          |        |      |      |          |        | See Fig. 4                      |

| AGC setting of;              |        |      |      |          |        | 5                               |

| 1.5V                         |        | 44   |      |          | dB     | Terminated voltage              |

|                              |        |      |      |          |        | conversion gain from $50\Omega$ |

|                              |        |      |      |          |        | source to $1k\Omega$ load       |

| 2.5V                         |        |      | 38   |          | dB     |                                 |

| 3.5V                         |        |      |      | 28       | d/B    |                                 |

| AGC input current            | 1      |      |      | 100      | μΑ     | All AGC settings                |

| I Q gain match               | -      |      | ±0.3 | ±1       | dB     | See Note 3.                     |

| I Q gain match               |        |      | ±0.5 | ±1       | dB     | See Note 4.                     |

| I Q phase match              |        |      | ±1.5 | ±-3      | deg    | See Note 4.                     |

| I & Q channel in band ripple |        |      | ±0.3 | ±0<br>±1 | dB     | see Note 3.                     |

| I & Q channel in band ripple |        |      | ±0.5 | ±1       | dB     | See Note 4.                     |

| I Q crosstalk                |        |      | -29  | -20      | dB     | See Note 4 and Note 2 for       |

|                              |        |      | _    |          |        | deviation of cross modulation   |

|                              |        |      |      |          |        |                                 |

|                              |        |      |      |          |        |                                 |

|                              |        |      |      |          |        |                                 |

|                              |        |      |      |          |        |                                 |

|                              |        |      |      |          |        |                                 |

# ELECTRICAL CHARACTERISTICS (continued)

Test conditions (unless otherwise stated)

$T_{amb} = 0^{\circ}C$  to  $85^{\circ}C$ ,  $V_{ee} = 0V$ , Vcc = 4.75 to 5.25 V, Fif = 479.5 MHz, IF bandwidth +- 22 MHz

These characteristics are guaranteed by either production test or design. They apply within the specified ambient temperature and supply voltage unless otherwise stated.

| Characteristic                      | Pin  | Min | Тур | Max | Units | Conditions                        |

|-------------------------------------|------|-----|-----|-----|-------|-----------------------------------|

| I & Q baseband output               | 2,7  |     | 8   | 20  | Ω     | See note (5), and Fig. 5.         |

| impedance                           |      |     |     |     |       |                                   |

| I & Q baseband output               | 2, 7 | 1.2 | 1.5 |     | Vp-р  | See note(6)                       |

| clipping level                      |      |     |     |     |       |                                   |

| IP3 <sub>2T</sub> , output referred |      | +3  | +9  |     | dBV   | 2 input carriers at -39 dBV       |

|                                     |      |     |     |     |       | within IF bandwidth of ±22MHz     |

|                                     |      |     |     |     |       | AGC set to give composite         |

|                                     |      |     |     |     |       | output of -11 dBV, IM3 tone       |

|                                     |      |     |     |     |       | within baseband bandwidth         |

| IM3 <sub>2T</sub> output referred   |      |     |     | -40 | dBc   | 2 input carriers within IF        |

|                                     |      |     |     |     |       | bandwidth of ±22MHz, AGC          |

|                                     |      |     |     |     |       | set to give composite output      |

|                                     |      |     |     |     |       | of -11 dBV, IM3 tone within       |

|                                     |      |     |     |     |       | baseband bandwidth                |

| All prescaler and other             |      |     |     | -30 | dBc   | 0.1 - 100MHz, referred to output  |

| spurs in I & Q baseband             |      |     |     |     |       | amplitude of - 11 dBV.            |

| output.                             |      |     |     |     |       |                                   |

| Power supply rejection              |      | 20  |     |     | dBc   | Attenuation Vcc to I & Q outputs, |

|                                     |      |     |     |     |       | over 0-500kHz                     |

Notes: 1. Performance not guaranteed over full specified IF input operating range

2. I Q crosstalk is determined from the gain and phase match by the following formula Crosstalk = 20\* Log (tan(phase error + Atan (1+amplitude imbalance) -45°))

3. Over specified gain dynamic,  $1k\Omega$  load up to 22MHz baseband

4. Over specified gain dynamic range,  $1k\Omega$  load up to 30MHz baseband

5. Baseband bandwidth 0.1 to 22MHz

6. The device should not be operated beyond the point of output clipping since gain match may be compromised

# **ABSOLUTE MAXIMUM RATINGS**

All voltages are reffered to Vee at 0V

| Characteristics              | Min  | Max     | Units | Conditions                     |

|------------------------------|------|---------|-------|--------------------------------|

| Supply voltage, Vcc          | -0.3 | 7       | V     |                                |

| IFFIN &IFINB input voltage   |      | 2.5     | Vp-р  |                                |

| IFIN & IFINB input DC offset | -0.3 | Vcc+0.3 | V     |                                |

| IOUT & QOUT DC offset        | -0.3 | Vcc+0.3 | V     |                                |

| AGC DC offset                | -0.3 | Vcc+0.3 | V     |                                |

| VCO1 & 2 DC offset           | -0.3 | Vcc+0.3 | V     |                                |

| VCODDIS DC offset            | -0.3 | Vcc+0.3 | V     |                                |

| PSCAL & PSCALB DC offset     | -0.3 | Vcc+0.3 |       |                                |

| Storage temperature          | -55  | 125     | °C    |                                |

| Junction temperature         |      | 150     | °C    |                                |

| PSOP16 package thermal       |      | ТВА     | °C/W  |                                |

| resistance, chip to ambient  |      |         |       |                                |

| PSOP16 package thermal       |      | ТВА     | °C/W  |                                |

| resitance, chip to case      |      |         |       |                                |

| Power consumption at 5.25V   |      | TBA     | mW    |                                |

| ESD protection               | 2    |         | kV    | Mil std 883B method 3015 cat 1 |

# ADDITIONAL INFORMATION REGARDING THE PSOP PACKAGE.

The following information should be noted when using the PSOP package fitted to the SL1711.

- (a) This package uses the standard SOIC 16 footprint.

- (b) There is no need to make a thermal connection between the package and the board. If such a connection is made using a thermal adhesive this will enhance the long term reliability of the product by reducing the junction temperature.

- (c) The heatsink that is evident on the base of the package is solderable.

- (d) There is no direct electrical connection between any of the device pins and the metal heatsinkslug. However if the heatsink is to be electrically connected to the PCB these connections should be confined to the ground plane.

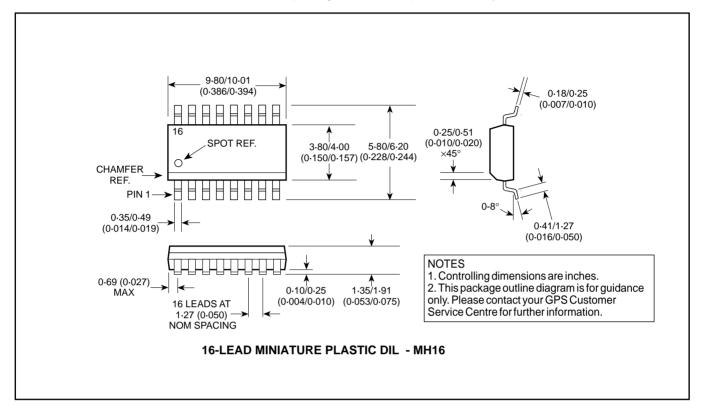

# PACKAGE DETAILS

Dimensions are shown thus: mm (in). For further package information, please contact your local Customer Service Centre.

| GEC PLESSE<br>SEMICONDUCTOR                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HEADQUARTERS OPERATIONS<br>GEC PLESSEY SEMICONDUCTORS<br>Cheney Manor, Swindon,<br>Wiltshire SN2 2QW, United Kingdom.<br>Tel: (01793) 518000<br>Fax: (01793) 518411                         | CUSTOMER SERVICE CENTRES<br>• FRANCE & BENELUX Les Ulis Cedex Tel: (1) 69 18 90 00 Fax : (1) 64 46 06 07<br>• GERMANY Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55<br>• ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993<br>• JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510<br>• KOREA Seoul Tel: (2) 5668141 Fax: (2) 5697933<br>• NORTH AMERICA Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023. |

| GEC PLESSEY SEMICONDUCTORS<br>P.O. Box 660017<br>1500 Green Hills Road,<br>Scotts Valley, California 95067-0017,<br>United States of America.<br>Tel: (408) 438 2900<br>Fax: (408) 438 5576 | <ul> <li>NORTH AMERICA Cochistration, Coort 16, 1007 101 100 101 100 101 100 100 100 10</li></ul>                                                                                                                                                                                                                                                                                                                         |

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been subpreseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.