#### **GENERAL DESCRIPTION**

The S-2444R is a 256-bit Non Volatile CMOS Memory, one to one combination of static CMOS RAM and Non Volatile Electric Erasable Programmable Read Only Memory (E<sup>2</sup>PROM) as a back up. The device is organized as 16 words of 16 bits each. Serial access allows the use of a cost-effective 8-pin package, making the S2444R ideal for cost sensitive and compact design applications.

STORE signal, RECALL signal and instructions sent from the processor transfer data between RAM and E<sup>2</sup>PROM. Non Volatile data is retained in the E<sup>2</sup>PROM while data in the RAM can be accessed and updated.

There is no need of high voltage pulses and supplies. A signal 5V supply is the only power source needed, and all I/O are TTL compatible.

The S-2444R offers many modes to minimize the current consumption. When it is deselected, the chip is placed in the STANDBY mode. And when the sleep instruction is carried out, the chip is placed in the SLEEP mode. The chip will automatically return active from STANDBY mode when selected by CE, and will exit the SLEEP mode when the next RECALL operation is performed, either by the RCL instruction or by taking the RECALL input low.

#### FEATURES

Ideal use for Periphery of Microcomputers.

Static Timing Minimum I/O Interface Serial Port Compatible (8051) **Minimum Support Circuits**

• Software and Hardware Control of Nonvolatile Functions

**False Store Protection**

TTL Compatible

High Drive Ability Output

- Constitution 16 words x 16 bits

- CMOS Floating Gate Process

- 5V Single Power Supply (5V±10%)

Low Current Consumption

Power Supply Current 10mA TYP Store Current 8mA TYP Standby Current 5μA TYP Sleep Current **5μΑ ΤΥΡ**

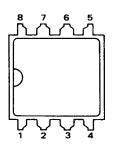

8 Pin-Dip

Low Cost, Compact

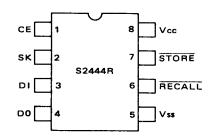

#### PIN CONFIGURATION

#### PIN NAMES

| CE     | CHIP ENABLE     |  |

|--------|-----------------|--|

| SK     | SERIAL CLOCK    |  |

| D1     | SERIAL DATA IN  |  |

| D0     | SERIAL DATA OUT |  |

| RECALL | RECALL          |  |

| STORE  | STORE           |  |

| Vcc    | +5V             |  |

| Vss    | GROUND          |  |

| L      |                 |  |

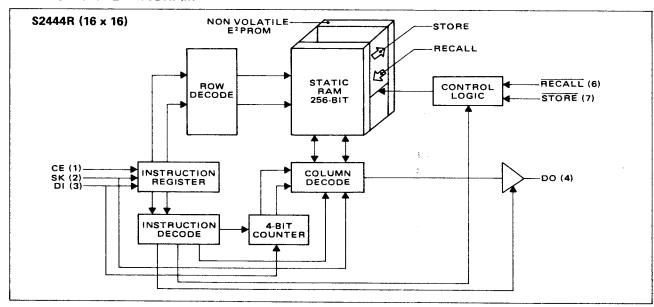

#### FUNCTIONAL DIAGRAM

#### ■ ABSOLUTE MAXIMUM RATINGS

| Symbol | Item                                  | Condition        | Unit |

|--------|---------------------------------------|------------------|------|

| TSTG   | Storage Temperature -65 to +125       |                  | °C   |

| TOPR   | TOPR Operating Temperature -10 to +85 |                  | °C   |

| Vcc    | Power Supply Voltage                  | -0.3 to +6.0     | V    |

| VIN    | Input Voltage                         | -0.3 to Vcc +0.3 | V    |

| Vout   | Output Voltage                        | -0.0 to VCC      | V    |

#### ■ D.C. ELECTRIC CHARACTERISTICS (Ta = $0 \sim 70^{\circ}$ C, V CC = +5V $\pm 10\%$ )

| Symbol | İtem                   | Condition    | MIN          | TYP | MAX | Unit |

|--------|------------------------|--------------|--------------|-----|-----|------|

| Vcc    | Operating Voltage      |              | 4.5          |     | 5.5 | V    |

| Icc    | Power Supply Current   | 11/0 = 0mA   |              | 10  | 20  | mΑ   |

| ISL    | Sleep Current          |              | _            | 5   | 30  | μA   |

| ISB    | Standby Current        | CE = VIL     | _            | 5   | 30  | μΑ   |

| ISTO   | Store Current          |              | _            | 8   | 15  | mA   |

| ILI    | Input Load Current     | VIN = 5.5V   | <del>-</del> | 0.1 | 10  | μΑ   |

| 1LO    | Output Leakage Current | Vout = 5.5V  | -            | 0.1 | 10  | μΑ   |

| VIL    | Input Low Voltage      |              | 0.0          | _   | 0.8 | V    |

| VIH    | Input High Voltage     |              | 2.0          |     | Vcc | V    |

| VOL    | Output Low Voltage     | 10L = 4.2mA  | _            | -   | 0.4 | V    |

| Voн    | Output High Voltage    | IOH = -2.0mA | 2.4          | _   | -   | V    |

| VDH    | Data Holding Voltage   |              | 1.5          |     | 5.5 | V    |

## ■ CAPACITANCE (Ta = 25°C, f = 1.0MHz, VCC = 5V)

| Symbol | Item               | Condition | MIN | TYP | MAX | Unit |

|--------|--------------------|-----------|-----|-----|-----|------|

| Co     | Output Capacitance | Vo = 0V   |     |     | 8   | pF   |

| CIN    | Input Capacitance  | VIN = 0V  |     |     | 6   | pF   |

#### ■ A.C. CONDITIONS OF TEST

| Input Pulse Levels             | VIL = 0.65V, VIH = 2.2V |

|--------------------------------|-------------------------|

| Input Rise and Fall Times      | 10ns                    |

| Input and Output Timing Levels | Vol = 0.65V, VoH = 2.2V |

| Output Load                    | 1 TTL + 100PF           |

#### OPERATING MODE

| MODE            | STORE | RECALL | INST. | WRITE<br>ENABLE<br>LATCH | PREVIOUS<br>RECALL<br>LATCH |

|-----------------|-------|--------|-------|--------------------------|-----------------------------|

| Hardware Recall | 1     | 0      | NOP   | ×                        | ×                           |

| Software Recall | 1     | 1      | RCL   | ×                        | ×                           |

| Hardware Store  | 0     | 1      | NOP   | SET                      | TRUE                        |

| Software Store  | 1     | 1      | STO   | SET                      | TRUE                        |

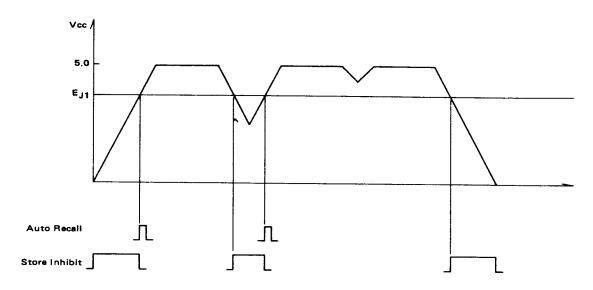

# ■ AUTO RECALL AND FALSE STORE PROTECTION ARE TRIGGERED ON POWER UP AND POWER DOWN RESPECTIVELY.

Conditions . . . . . Vcc Rise and Fall times should be between 10ms and 1000ms.

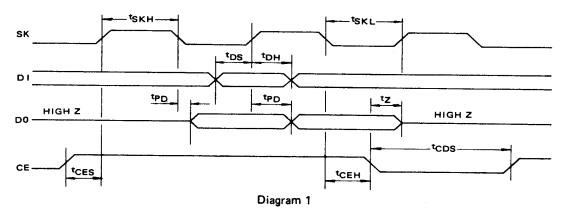

## ■ A.C. ELECTRIC CHARACTERISTICS (Ta = 0 ~ 70°C, Vcc = 5V ±10%)

| Symbol           | Item                    | MIN  | TYP | MAX  | Unit |

|------------------|-------------------------|------|-----|------|------|

| Fsk              | SK Frequency            | 1    |     | 1.0  | MHz  |

| <sup>t</sup> SKH | SK Positive Pulse Width | 0.4  |     |      | μs   |

| tskL             | SK Negative Pulse Width | 0.4  |     |      | μs   |

| t <sub>DS</sub>  | Data Setup Time         | 0.4  |     |      | μs   |

| t <sub>DH</sub>  | Data Hold Time          | 0.08 |     |      | μs   |

| tPD              | SK to Data Valid Time   |      |     | 0.75 | μs   |

| tz               | Chip Disable Time       |      |     | 1.0  | μs   |

| tces             | Chip Enable Setup Time  | 0.8  |     |      | μs   |

| tCEH             | Chip Enable Hold Time   | 0.4  |     |      | μs   |

| tcds             | Chip De-select Time     | 0.8  |     |      | μs   |

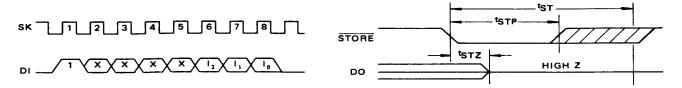

#### **■ CONTROL/DATA TIMING**

- CE must be taken high between instructions.

- Once the chip has been selected with CE, the first logic "1" clocked by the rising edge of SK into the DI input marks the beginning of an instruction. All previous logic "0" is ignored.

|                   | INSTRUCTION SET                                      |                                                       |  |  |  |

|-------------------|------------------------------------------------------|-------------------------------------------------------|--|--|--|

| Instruction       | Format, I <sub>2</sub> I <sub>1</sub> I <sub>0</sub> | Operation                                             |  |  |  |

| WRDS (Diagram 5)  | 1XXXX000                                             | Reset Write Enable Latch (Disables writes and stores) |  |  |  |

| STO (Diagram 5)   | 1XXXX001                                             | Store RAM data in E <sup>2</sup> PROM                 |  |  |  |

| SLEEP (Diagram 5) | 1XXXX010                                             | Enter SLEEP Mode                                      |  |  |  |

| WRITE (Diagram 3) | 1AAAA011                                             | Write Data into RAM Address AAAA                      |  |  |  |

| WREN (Diagram 5)  | 1XXXX100                                             | Set Write Enable Latch (Enables writes and stores)    |  |  |  |

| RCL (Diagram 5)   | 1XXXX101                                             | Recall E <sup>2</sup> PROM Data into RAM              |  |  |  |

| READ (Diagram 2)  | 1AAAA11X                                             | Read Data from RAM Address AAAA                       |  |  |  |

X = Don't Care

#### **■ DATA OPERATIONS**

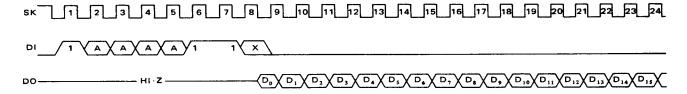

Diagram 2. RAM Read

Diagram 3. RAM Write

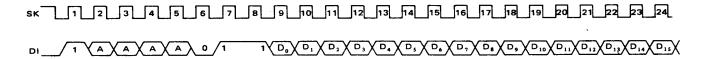

Diagram 4. Hardware Recall

A = Address Bit

<sup>\*</sup> Bit 8 of Read Instruction is Don't Care.

#### ARRAY RECALL CYCLE

| Symbol           | Item                     | MIN  | TYP | MAX | Unit |  |

|------------------|--------------------------|------|-----|-----|------|--|

| <sup>†</sup> RCC | CC Recall Cycle Time 2.5 |      |     |     | μs   |  |

| tRCP             | Recall Pulse Width       | 0.5  |     |     | μs   |  |

| <sup>†</sup> RCZ | Recall to Output High Z  |      |     | 0.5 | μs   |  |

| torc             | Recall Enable Time       | 0.01 |     |     | μs   |  |

| tARC             | Recall Data Access Time  |      |     | 1.5 | μs   |  |

Recall Time is not limited.

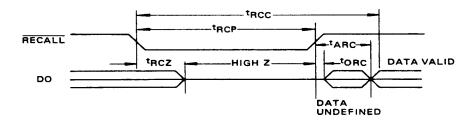

Diagram 5. Non-Data Operations

Diagram 6. Hardware Store

#### STORE CYCLE

| Symbol | Item                   | MIN | TYP | MAX | Unit |

|--------|------------------------|-----|-----|-----|------|

| tsT    | Store Time             |     |     | 10  | ms   |

| tstp   | Store Pulse Width      | 0.2 |     |     | μs   |

| tstz   | Store to Output High Z |     |     | 1.0 | μs   |

Minimum store cycle is 10,000.

10,000 data change per bit.

10 years' Data Retention.

#### ■ RECALL OPERATIONS

RECALL operation transfers the data currently in the nonvolatile E<sup>2</sup>PROM into the RAM section of the S2444R. RECALL operation can be initiated either from the RECALL input driven low, or the execution of the RCL instruction. Once operated, all other operations are inhibited, and the previous data in the RAM is overwritten. If the chip had been already placed in SLEEP mode, the RECALL operation will put the chip in Active mode. The first Recall after power-on will set the previous latch, which must be set in order to do set STORE operations.

#### STORE OPERATION

STORE operation transfers the data currently in the RAM to E<sup>2</sup>PROM. The data currently in the E<sup>2</sup>PROM is overwritten. The STORE operation can be initiated from either the STORE input being driven low, or the execution of a STO instruction in order to protect against inadvertent stores which destroy important information in the E<sup>2</sup>PROM, several conditions must be true in order to perform the STORE OPERATION.

- 1. STO Command issued or STORE driven low

- 2. Write Enable Latch must be set.

- 3. Privious Recall Latch must be set.

STORE operation inhibits all other operations, and any data spread the part during a STORE operation will result in the output remaining in the high impedance state. The STORE operation clears the Write Enable latch. If the S2444R is performing a WRITE operation, the STORE input is ignored until CE is taken low.

#### WRITE/STORE PROTECTION

WRITE/STORE protection is provided by the S2444R internal Write Enable Latch. This latch must be set in order to do the WRITE or STORE operation. The latch can be set with the WREN instruction and reset with the WRDS instruction. The Write Enable latch is automatically reset after a STORE operation is performed.

#### READ/WRITE MEMORY

The RAM in the chip is accessed by the READ and WRITE instructions. These instructions include a 4-bit address, which selects which word is to be written or read. After the instruction and address have been sent, serial data (16-bits) will be either output on the DO pin in the case of a read, or input through the DI pin in the case of a write. S2444R design allows the connection of the DI and DO lines together form a bi-directional serial interface.

The least significant bit of the READ instruction is a don't care to enhance the use of the shared I/O capability of the DI and DO lines.

#### SLEEP MODE

The SLEEP mode places the S2444 into a low power quiescent mode. Internal RAM is turned off, and any data currently in RAM becomes invalid. Data is maintained in E<sup>2</sup>PROM, as it was saved in the last STORE operation. The SLEEP mode can only be exited by a hardware or software initiated Recall operation.

#### ORDERING INFORMATION

| Model    | Overwrite Times | Overwrite Times/Bit | Temperature Range | Package |

|----------|-----------------|---------------------|-------------------|---------|

| S2444R01 | 10 <sup>4</sup> | 10 <sup>4</sup>     | 0°C ~ +70°C       | Plastic |

| S2444R10 | 10 <sup>5</sup> | 10 <sup>5</sup>     | 0°C ~ +70°C       | Plastic |

Note: All values are typical.

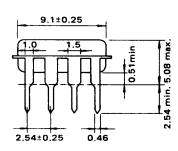

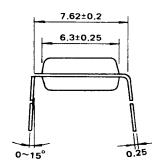

#### **■ DIMENSIONS (Unit: mm)**

(Specifications subject to change without notice.)

## Seiko Instruments Inc.

31-1, 6-chome, Kameido, Koto-ku, Tokyo 136, Japan Telex: 2622162 DSEIKO J

IC Sales Section Phone: (03) 636-3821

Seiko Instruments U.S.A. Inc.:

2990 W. Lomita Blvd., Torrance Calif. 90505 Phone: 213-530-8777 Telex: 910 - 347 - 7307 Fax: (213) 539 - 8621

Seiko Instruments GmbH:

Arabella Center 13 OG Lyoner Strasse 44-48, 6000 Frankfurt/Main 71 W. Germany

Phone: 069-6666971 Telex: 413045 SIG D

Precision Engineering Ltd. Sales Division:

7th, 9th Fl., Koon Wah Industrial Building, 40-46 Lam Tin Street, Kwai Chung, N.T., Kowloon, Hong Kong Phone: 0-218611 Telex: 40211 PELSD HX

7