# ICs for Communications

Subscriber Access Controller for U<sub>pn</sub>-Interface Terminals SmartLink-P

PSB 2197

Addendum to User's Manual 08.95

#### Edition 08.95

This edition was realized using the software system FrameMaker<sup>®</sup>.

#### Published by Siemens AG, Bereich Halbleiter, Marketing-Kommunikation, Balanstraße 73, 81541 München

© Siemens AG 1995.

All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

For questions on technology, delivery and prices please contact the Semiconductor Group Offices in Germany or the Siemens Companies and Representatives worldwide (see address list).

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Siemens Office, Semiconductor Group.

Siemens AG is an approved CECC manufacturer.

#### Packing

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Semiconductor Group of Siemens AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Semiconductor Group of Siemens AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

### Subscriber Access Controller for U<sub>pn</sub>-Interface Terminals SmartLink-P

This addendum contains additions to the User's Manual 02.95, Ordering No. B115-H6826-X-X-7600

| Page (in<br>User's<br>Manual) | Page (in<br>Addendum) | Subjects (major changes since last revision)                      |

|-------------------------------|-----------------------|-------------------------------------------------------------------|

| 9                             | 4                     | Pin Definitions and Functions                                     |

| 16                            | 5                     | Logic Symbol of the SmartLink-P TR-Mode                           |

| 17                            | 6                     | Logic Symbol of the SmartLink-P HDLC-Controller Mode              |

| 57                            | 7                     | Device Architecture in TR Mode                                    |

| 64                            | 8                     | Device Architecture of the SmartLink-P in HDLC-Controller<br>Mode |

| 67                            | 9                     | Reset                                                             |

|                               | 9                     | Jitter (TE Mode)                                                  |

|                               | 9                     | Jitter (TR Mode)                                                  |

| 71                            | 10                    | TE-Mode State Description                                         |

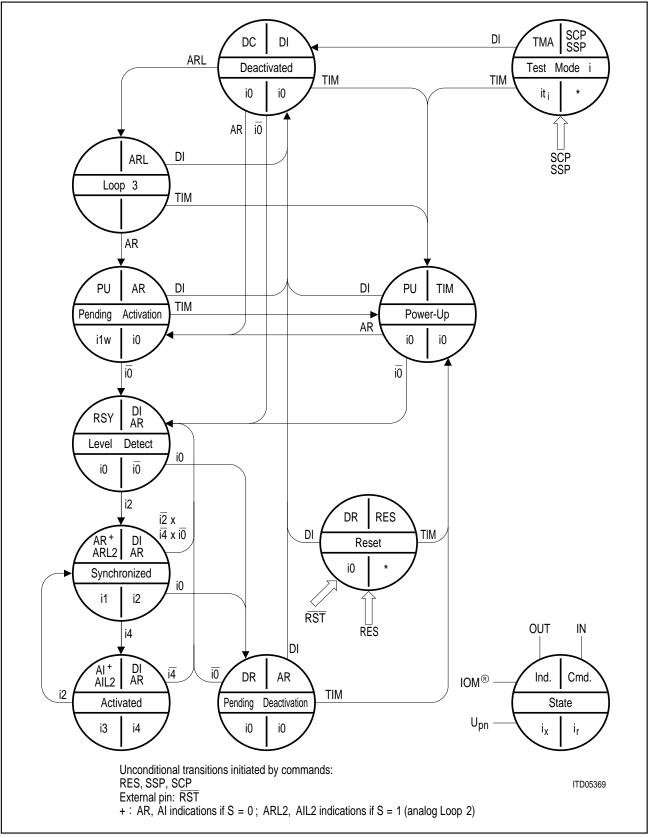

| 73                            | 11                    | State Diagram TE-Mode                                             |

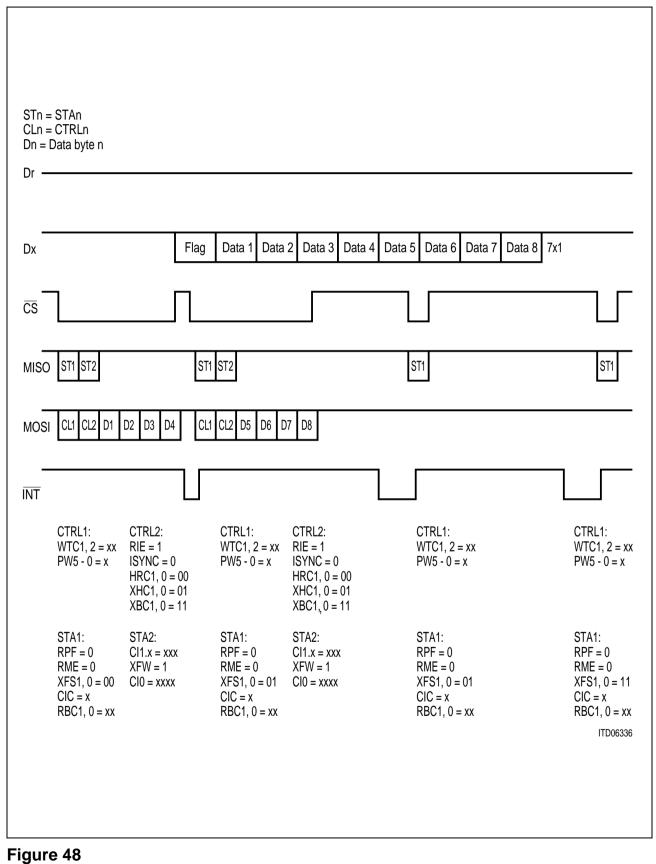

| 76                            | 10                    | Operation of the Serial Control Interface                         |

| 87                            | 12                    | Transmit Data Underrun                                            |

| 88                            | 13                    | Reception of Frames                                               |

| 96                            | 14                    | Reset                                                             |

| 98                            | 14                    | Layer-1 Command/Indication Codes in TR Mode                       |

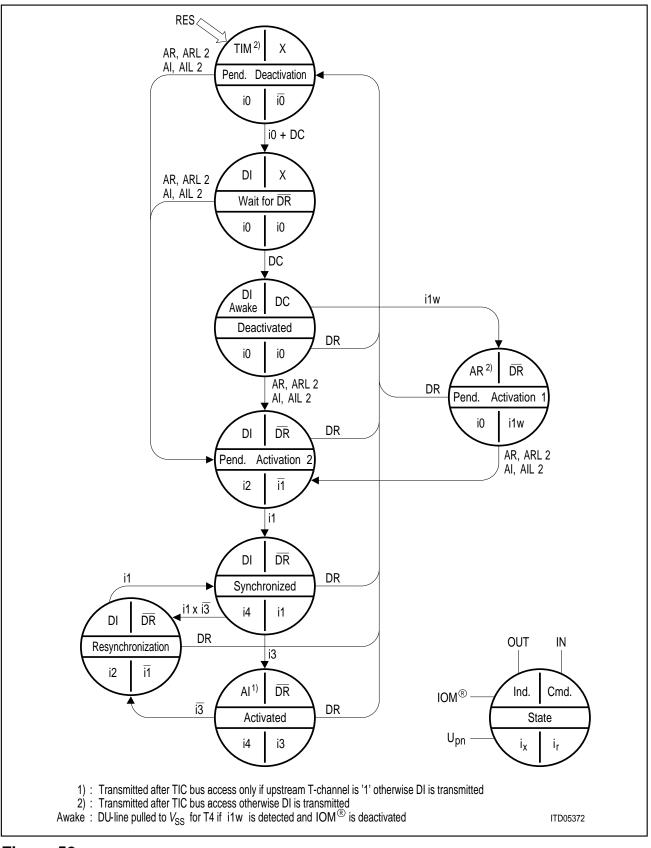

| 101                           | 15                    | State Diagram TR-Mode                                             |

| 120                           | 16                    | Electrical Characteristics                                        |

| 122                           | 17                    | Capacitances                                                      |

| 124                           | 18                    | AC Characteristics                                                |

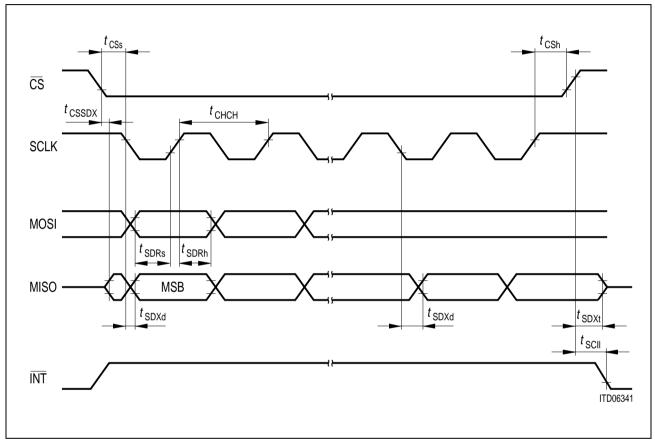

| 124                           | 18                    | SCI-Switching Characteristics                                     |

| 126                           | 19                    | IOM®-2 Bus Switching Characteristics                              |

| 129                           | 19                    | MCLK-Timing                                                       |

| 130                           | 19                    | Reset Timings                                                     |

PSB 2197

| Pin No. TE-Mode |        | TR-Mo                                         | de HDLC-<br>Controll<br>Mode |                                               | ler    | Function                                      |                                                                                                                                  |

|-----------------|--------|-----------------------------------------------|------------------------------|-----------------------------------------------|--------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| P-DSO-28        | Symbol | Input (I)<br>Output (O)<br>Open<br>Drain (OD) | Symbol                       | Input (I)<br>Output (O)<br>Open<br>Drain (OD) | Symbol | Input (I)<br>Output (O)<br>Open<br>Drain (OD) |                                                                                                                                  |

| 2               | RST    | I/O(OD)                                       | RST                          | I                                             | RST    | I/O(OD)                                       | <b>RESET.</b> Low active<br>reset output and<br>input (TE, HDLC,<br>open drain output),<br>low active reset<br>input in TR mode. |

#### 1.1 Pin Definitions and Functions

**Note:** The possibility to use the undervoltage detection in HDLC controller mode is listed for completeness. The pulse width of the reset output in HDLC controller mode if the undervoltage detection is used is not specified in the electrical characteristics but may be as short as 200 ns.

If  $\overline{RST}$  is configured as reset input, it must be driven to a valid  $V_{IL}$  during power-up.

The first note on page 14 is incorrect in regards to pin 7. All  $V_{DD}$  pins are internally connected via the chip substrate.

The second note on page 14 is for information only, and the series resistors referred to have no effect on the AC and DC characteristics shown in chapter 5.

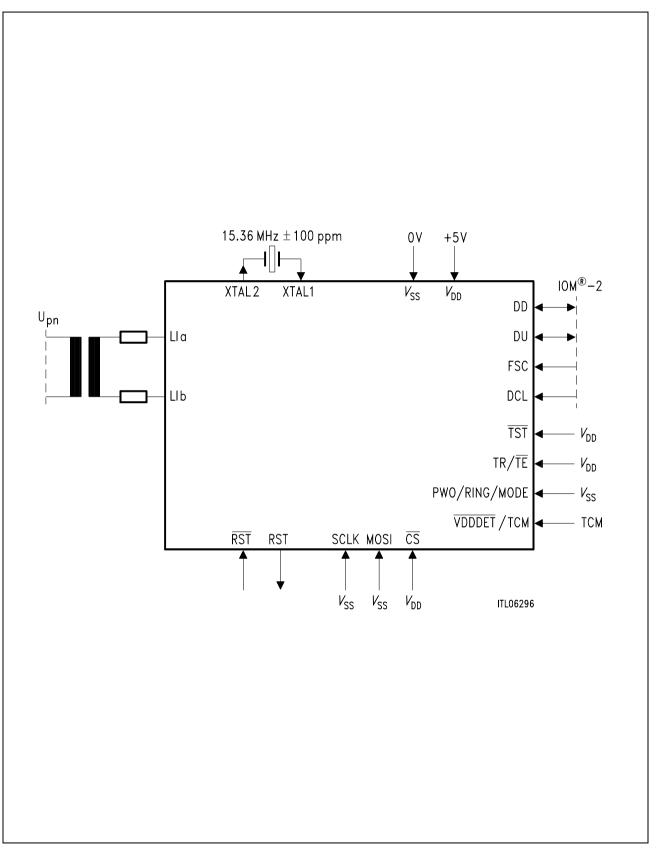

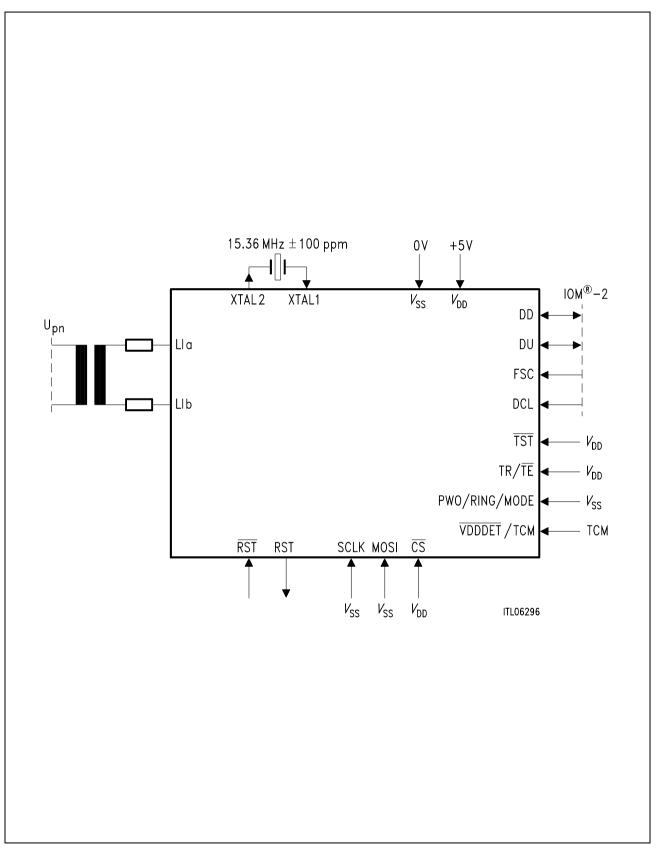

#### Figure 2 Logic Symbol of the SmartLink-P TR-Mode

### Logic Symbol of the SmartLink-P HDLC-Controller Mode

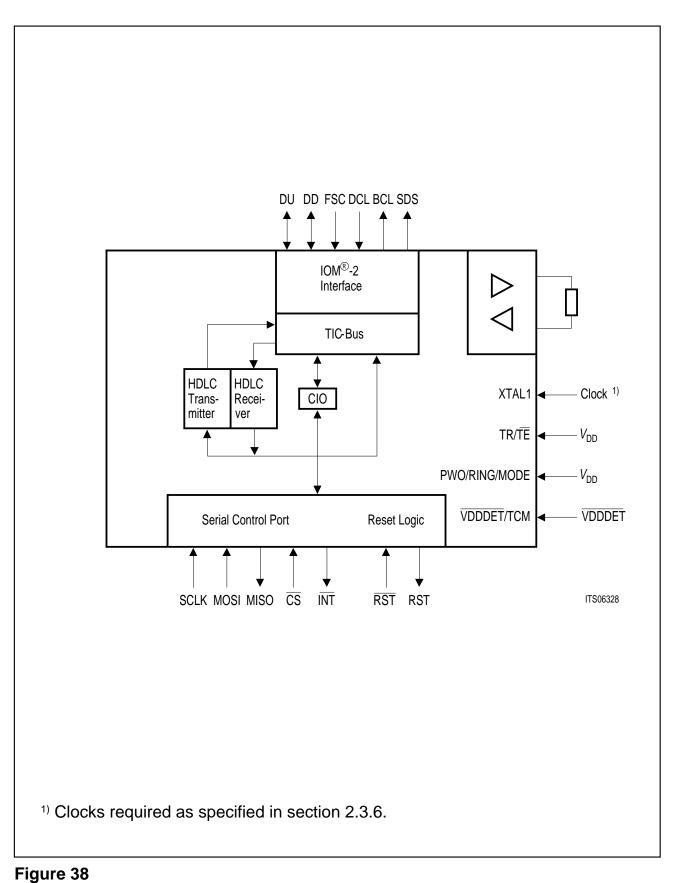

#### Figure 32 Device Architecture in TR Mode

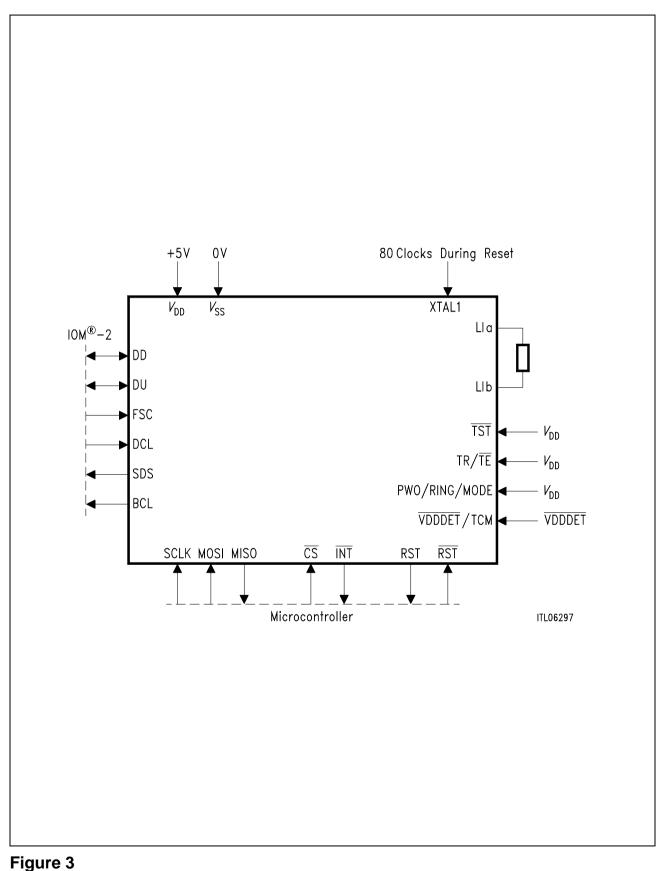

### Device Architecture of the SmartLink-P in HDLC-Controller Mode

Semiconductor Group

### 2.1.2.1 Jitter (TE Mode)

#### Jitter on IOM<sup>®</sup>-2

The IOM-2 clocks are derived from a receive PLL which adjusts the clock to all pulses that are received. The receive PLL recovers bit timing from a comparator output signal. The comparator has a threshold of 80 % with respect to the signal stored by the peak detector. The RPLL adjust the IOM clocks by one oscillator period (65 ns) every four positive pulses that are offset in the same direction. At maximum four oscillator periods may be adjusted in one IOM-2 frame if every bit of the U<sub>pn</sub> frame is a '1' (38 frame bits with every second positive pulse result in an average of 19 pulses, 19/4 = 4). Due to the scrambler it is very unlikely that continuous pulses occur, thus the actual adjustment will be less than the maximum.

In the following IOM-2 frame, no adjustment is done since the SmartLink transmits in uplink direction.

### Jitter on U<sub>pn</sub>

Jitter on  $U_{pn}$  is directly related to the crystal tolerance. There is no transmit PLL involved.

#### Jitter on MCLK, Pulse Width Modulator, LCD Contrast

Jitter on these clocks is directly related to the crystal tolerance. Only clock dividers are involved.

#### 2.2.2.1 Jitter (TR Mode)

#### Jitter on U<sub>pn</sub>

Jitter on  $U_{pn}$  is directly related to the jitter on the IOM-2 clocks. A fixed divider is used to generate the  $U_{pn}$  data rate of 384 kbit/s.

#### 2.3.6 Reset

The HDLC-controller mode is reset by applying a reset pulse to the  $\overline{RST}$  input.

To bring the  $U_{pn}$ -transceiver to a low power state, the following requirements must be fulfilled: While reset is active, at least 40 clock pulses must be applied to XTAL1. After reset is released, another 10 clock pulses are required. The  $U_{pn}$ -transceiver enters its low power deactivated state after 6 IOM-frames which are generated after the 50 clock pulses on XTAL1 have elapsed.

This procedure is necessary only after power-cycle. Resetting SmartLink while the power remains active doesn't require the procedure to be performed again.

### 3.1.2.5 TE-Mode State Description

#### Level Detect, Resynchronization

During the first period of receiving info 2 or under severe disturbances on the line the  $U_{pn}$ -receiver recognizes the receipt of a signal but is not (yet) synchronized. In extremely rare situations of severe line disturbances, the  $U_{pn}$ -receiver might become locked in this state. To avoid this, it is recommended that the software issue an RES command to restart activation if SmartLink remains in this state longer than an acceptable period. This timeout period should be at least 110 ms, but the exact period should be chosen by the user based on system concerns.

#### Analog Loop 2

The states for analog loop 2 are identical to the states of the regular TE operation. The analog loop 2 indications are output if the S-bit of the  $U_{pn}$ -frame is '1'.

| State        | S-bit = 0 | S-bit = 1 |

|--------------|-----------|-----------|

| Synchronized | AR        | ARL2      |

| Activated    | AI        | AIL2      |

#### 3.1.3 Operation of the Serial Control Interface

The first falling edge of SCLK will force the state machine to load the current value of STA1 into the shift register and output the MSB. The following clocks shift the contents of STA1 over the MISO line. At the same time, the MOSI line receives the value of CTRL1. Its value is stored in the CTRL1 register with the rising edge of the last clock period.

Figure 43 State Diagram TE-Mode

#### Transmit Data Underrun

| Dr Flag Data 1 Data 2 Data 3 CRC CRC Flag Dx CS MISO STA1 STA2 Data 1 Data 2 Data 3 RSTA MOSI CTRL1 CTRL2 INT CTRL1: CTRL2: WTC1,2 = xx XHC1,0 = 00 RIE = 1 ISYNG = 0 HRC1,0 = 01 (RMC) STA1: STA2: RPF = 0 C11 x = xxx RME = 1 XFS1,0 = 00 C10 = xxx RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = xxx C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x RBC1,0 = 00 C10 = x C1C = x C1C = x RBC1,0 = 00 C10 = x C1C |          |                 |                                                      |                                               |      |     |       |             |            |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------------|------------------------------------------------------|-----------------------------------------------|------|-----|-------|-------------|------------|------|

| CS<br>MISO<br>STA1 STA2 Data 1 Data 2 Data 3 RSTA<br>MOSI<br>INT<br>CTRL1: CTRL2:<br>WTC1, 2 = xx XHC1, 0 = 00<br>PW5 - 0 = x XHC1, 0 = 00<br>RIE = 1<br>ISYNG = 0<br>HRC1, 0 = 01 (RMC)<br>STA1: STA2:<br>RPF = 0 Cl1 x = xxx<br>RME = 1 XFW = 1<br>XFS1, 0 = 00 Cl0 = xxxx<br>CIC = x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |                 |                                                      |                                               | Flag | CRC | 3 CRC | Data 2 Data | lag Data 1 | r    |

| MISO       STA1       STA2       Data 1       Data 2       Data 3       RSTA         MOSI       CTRL1       CTRL2         INT       CTRL1:       CTRL2:         WTC1, 2 = xx       XHC1, 0 = 00         PW5 - 0 = x       XBC1, 0 = 00         RIE = 1       ISYNG = 0         HRC1, 0 = 01 (RMC)       STA1:       STA2:         RPF = 0       Cl1 x = xxx         RME = 1       XFW = 1         XF51, 0 = 00       Cl0 = xxxx         ClC = x       Cl0 = xxxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |                 |                                                      |                                               |      |     |       |             |            | × —  |

| MOSI<br>$\begin{array}{c} CTRL1 \ CTRL2 \\ \hline \\ INT \\ \hline \\ CTRL1: \ CTRL2: \\ WTC1, 2 = xx \ XHC1, 0 = 00 \\ PW5 - 0 = x \ XBC1, 0 = 00 \\ RIE = 1 \\ ISYNG = 0 \\ HRC1, 0 = 01 \ (RMC) \\ \hline \\ STA1: \ STA2: \\ RPF = 0 \ C11 x = xxx \\ RME = 1 \ XFW = 1 \\ XFS1, 0 = 00 \ C10 = xxxx \\ CIC = x \\ \hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |                 |                                                      |                                               |      |     |       |             |            | s    |

| INT<br>CTRL1: CTRL2: WTC1, 2 = xx XHC1, 0 = 00 PW5 - 0 = x XBC1, 0 = 00 RIE = 1 ISYNG = 0 HRC1, 0 = 01 (RMC) $STA1: STA2: RPF = 0 C11.x = xxx RME = 1 XFW = 1 XFW = 1 XFS1, 0 = 00 CI0 = xxxx CIC = x$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          | a 2 Data 3 RSTA | Data 1 Data 2 Dat                                    | STA1 STA2                                     |      |     |       |             |            | 1ISO |

| CTRL1: CTRL2: WTC1, 2 = xx XHC1, 0 = 00PW5 - 0 = x XBC1, 0 = 00RIE = 1ISYNG = 0HRC1, 0 = 01 (RMC)STA1: STA2:RPF = 0 CI1.x = xxxRME = 1 XFW = 1XFS1, 0 = 00 CI0 = xxxxCIC = x CID = xxx                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |                 |                                                      | CTRL1 CTRL2                                   |      |     |       |             |            | 10SI |

| RPF = 0 Cl1.x = xxx<br>RME = 1 XFW = 1<br>XFS1, 0 = 00 Cl0 = xxxx<br>ClC = x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          | 00              | XHC1, 0 = 00<br>XBC1, 0 = 00<br>RIE = 1<br>ISYNG = 0 | WTC1, $2 = xx$                                |      |     |       |             |            | NT   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ITD06337 |                 | CI1.x = xxx<br>XFW = 1                               | RPF = 0<br>RME = 1<br>XFS1, 0 = 00<br>CIC = x |      |     |       |             |            |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                 |                                                      |                                               |      |     |       |             |            |      |

#### Figure 49a Reception of Frames

#### 3.1.5 Reset

#### **Reset Logic**

#### Table 3

#### Reset State of the SmartLink-P Registers

| Register | Value after<br>Reset               | Meaning                                                                                                                                                                                                   |

|----------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STA1     | 00 <sub>H</sub>                    | No C/I-change, no status change, no data in RFIFO.                                                                                                                                                        |

| STA2     | 0F <sub>H</sub> (00 <sub>H</sub> ) | C/I is '1111' ('0000' if undervoltage detection is used, see Note)                                                                                                                                        |

| CTRL1    | 00 <sub>H</sub>                    | MCLK = 3.84 MHz, Watchdog disabled, PW = '000000'.                                                                                                                                                        |

| CTRL2    | 00 <sub>H</sub>                    | No HDLC-controller operation, no XFIFO-data.                                                                                                                                                              |

| CTRL3    | 00 <sub>H</sub>                    | Permanent D-channel access, permanent access to C/I0<br>and D-channel. T-channel mapped on S/G, PW-output<br>operates as LCD-contrast, TIC-bus access during<br>D-channel transmission only, TAD = '000'. |

| CTRL4    | 00 <sub>H</sub>                    | Normal operation of DU-line, Serial Strobe = '000' (OFF),<br>Cl0 = '0000'.                                                                                                                                |

**Note:** If the undervoltage detection is used to generate the reset signal for SmartLink, the value in STA2 will read "00". Please refer to **figure 21** for details.

#### 3.2.1.2 Layer-1 Command/Indication Codes in TR Mode

In TR mode, the U<sub>pn</sub>-interface is activated if the C/I code Activate Request (AR, ARL2) or Activate Indication (AI, AIL2) has been detected in downstream direction. It stays activated until the C/I code Deactivation Confirmation (DC) is received in downstream direction.

#### Figure 52 State Diagram TR-Mode

Semiconductor Group

#### 5 Electrical Characteristics

#### **DC-Characteristics**

$T_{\rm A} = 0$  to 70 °C;  $V_{\rm DD} = 5 \text{ V} \pm 5 \text{ \%}$ ,  $V_{\rm SS} = 0 \text{ V}$

| Parameter                                             | Symbol                             | Limit Values |      |      | Unit     | Test                                                                                             | Remarks                                                                              |

|-------------------------------------------------------|------------------------------------|--------------|------|------|----------|--------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                                       |                                    | min.         | typ. | max. |          | Condition                                                                                        |                                                                                      |

| H-output voltage<br>L-output voltage                  | V <sub>OH</sub><br>V <sub>OL</sub> | 4.5          |      | 0.4  | V<br>V   | $I_{OH} = 100 \ \mu A$<br>$C_{LD} \le 60 \ pF$<br>$I_{OL} = 100 \ \mu A$<br>$C_{LD} \le 60 \ pF$ | XTAL2<br>XTAL2                                                                       |

| Input leakage<br>current<br>Output leakage<br>current | I <sub>LI</sub><br>I <sub>LO</sub> |              |      | 1    | μΑ<br>μΑ | $0 V < V_{IN} < V_{DD}$ $0 V \leq V_{OUT} \leq V_{DD}$                                           | All pins except<br>Lla, Llb, XTAL1,<br>XTAL2, <b>TST</b> ,<br>RST, MCLK,<br>BCL, SDS |

All power consumption values are integrated values and not instantaneous currents. The currents for Lla and Llb in the remarks column of the power consumption parameters are instantaneous values.

All HDLC power consumption values are measured after the  $\rm U_{pn}\mbox{-}transceiver$  is in the power-down state.

#### Capacitances

$T_{\rm A}$  = 0 to 70 °C;  $V_{\rm DD}$  = 5 V  $\pm$  5 %,  $V_{\rm SS}$  = 0 V

| Parameter                            | Symbol                              | Limit Values |        | Unit     | Remarks                  |

|--------------------------------------|-------------------------------------|--------------|--------|----------|--------------------------|

|                                      |                                     | min.         | max.   |          |                          |

| Input capacitance<br>I/O-capacitance | C <sub>IN</sub><br>C <sub>I/O</sub> |              | 7<br>7 | pF<br>pF | All pins except Lla, Llb |

| Output capacitance                   | $C_{OUT}$                           |              | 25     | pF       | Lla, Llb                 |

| Load capacitance                     | $C_{\rm LD}$                        |              | 60     | pF       | XTAL1, XTAL2             |

| <b>ATALI,</b> Recommended <b>(ypical</b> crystal parameters) | XTAL1,2 | Recommended typical crystal parameters. |

|--------------------------------------------------------------|---------|-----------------------------------------|

|--------------------------------------------------------------|---------|-----------------------------------------|

| Parameter            | Symbol Limit Values   |      | Unit | Remarks |  |

|----------------------|-----------------------|------|------|---------|--|

|                      |                       | typ. |      |         |  |

| Motional capacitance | <i>C</i> <sub>1</sub> | 20   |      | fF      |  |

| Shunt                | $C_0$                 | 7    |      | pF      |  |

| Load                 | CL                    | ≤ 30 |      | pF      |  |

| Resonance resistor   | R <sub>r</sub>        | ≤ 65 |      | Ω       |  |

**Note:** The crystal tolerance of ± 100 ppm is the total tolerance required including adjustment, temperature and aging tolerances.

Start-up of the oscillator has been simulated and works with crystals which meet the above specifications.

#### **AC Characteristics**

There are no requirements regarding rise and fall times of input signals as long as all other AC timing requirements are met.

### Serial Control Interface Timing

#### Figure 56 SCI-Switching Characteristics

| Parameter                 | Symbol            | Limit Values |      | Unit |

|---------------------------|-------------------|--------------|------|------|

|                           |                   | min.         | max. |      |

| Chip select setup time    | t <sub>CSs</sub>  | 15           |      | ns   |

| Chip select hold time     | t <sub>CSh</sub>  | 25           |      | ns   |

| CSQ high to MISO tristate | t <sub>SDXt</sub> |              | 70   | ns   |

#### **IOM®-2 Bus Switching Characteristics**

| Parameter       | Symbol           | Limit | Values | Unit |

|-----------------|------------------|-------|--------|------|

|                 |                  | min.  | max.   |      |

| Bit clock delay | t <sub>bcd</sub> | - 20  | 50     | ns   |

#### MCLK-Timing

The MCLK generator is designed to start with a complete clock cycle. Thus the minimum high or low period is n (n = 1, 2, 4, 8) × oscillator period (65 ns). Only if the undervoltage detection is active and it generates a reset signal due to voltage drop, MCLK will immediately be stopped at the same time the reset outputs become active. As a result, for that MCLK period, the minimum pulse width may be as low as 0 ns (see Reset Timings).

#### **Reset Timings**

| Parameter  | Symbol                      | Limit | Values | Unit |

|------------|-----------------------------|-------|--------|------|

|            |                             | min.  | max.   |      |

| Hysteresis | $V_{\rm HH}$ - $V_{\rm HL}$ | 50    | 230    | mV   |

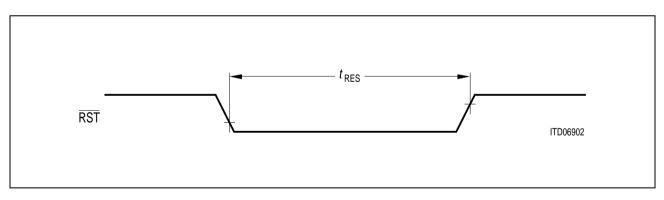

#### **External Reset Timings**

| Parameter         | Symbol           | Limit Values |      | Unit |

|-------------------|------------------|--------------|------|------|

|                   |                  | min.         | max. |      |

| Reset pulse width | T <sub>RES</sub> | 2            |      | μs   |

**Note:** If  $\overline{RST}$  is configured as reset input, it must be driven to a valid  $V_{IL}$  during power-up.