# **USB-to-ATAPI-4 Bridge Controller**

## 1. FEATURES

- □ Full compliance with the Universal Serial Bus Specification

- □ Support ATAPI-4 PIO and PACKET commands

- □ On chip transceivers and 5V-3.3V regulator for USB interface

- □ 512 Bytes unified data buffer dynamically allocated for upstream and downstream data transfer

- □ Drivers provided for Microsoft Windows 98/NT 5.0

#### 2. PRODUCT INTRODUCTION

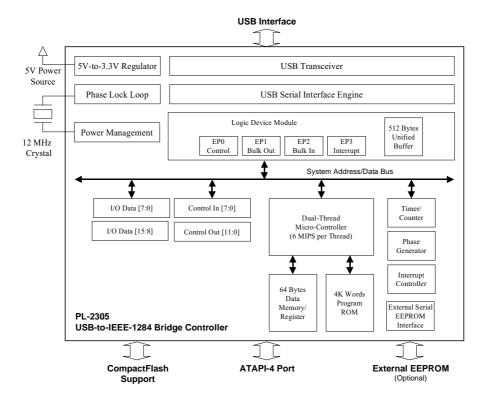

The PL-2307 integrated circuit provides a high-speed bridge between the Universal Serial Bus (USB) system and ATAPI-4 compliant peripheral devices. It is designed to be a flexible, high performance, and low-cost single-chip solution for USB-to-IDE cable as well as USB ready external "IDE Box" manufacturers. The PL-2305B also adds "CompactFlash Card Detection" and "CompactFlash Power On Enable" feature for CompactFlash Reader support.

PL-2307 supports most commands and features as defined by ATAPI-4 commands. However, DMA/Ultra DMA is not supported – since the bottleneck for data transfer is on the USB side, so the PIO mode data transfer is good enough. The queued command and command overly are not supported neither.

The external serial EEPROM support gives the user of PL-2307 options to customize this chip to show their identity. The user could modify the Vendor ID, Product ID, Language ID, manufacturer string, product string, and serial number strings of the final product. They could also use this EEPROM to store authorization/security codes. For large quantity orders, it is also possible to modify the Mask ROM (Read Only Memory) of PL-2307 to better represent the final product manufacturer and thus eliminate the need for external EEPROM.

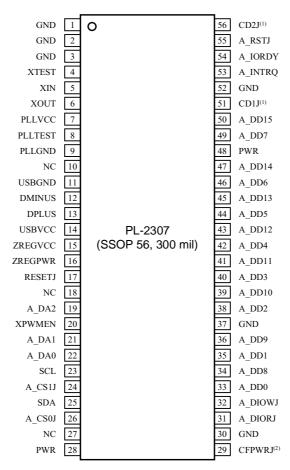

#### 3. PIN ASSIGNMENT & DESCRIPTION

USB-to-ATAPI Bridge Controller Pin Assignment

### **PIN Description**

| Pin | Symbol   | Type | Description                                                |

|-----|----------|------|------------------------------------------------------------|

| 1   | GND      | P    | Ground.                                                    |

| 2   | Reserved | ı    | Reserved, must be tied to ground.                          |

| 3   | Reserved | I    | Reserved, must be tied to ground.                          |

| 4   | XTEST    | I    | Core test pin must be tied to ground for normal operation. |

| 5   | XIN      | I    | Crystal in or CMOS oscillator input.                       |

| 6   | XOUT     | О    | Crystal out or no connection.                              |

| 7   | PLLVCC   | P    | 5V Analog Power Supply for on-chip PLL.                    |

| 8   | PLLTEST  | I    | PLL test pin must be tied to ground for normal operation.  |

| 9   | PLLGND   | P    | Analog Ground for on-chip PLL.                             |

| 10  | NC       | ı    | No connection.                                             |

| 11  | USBGND   | P    | Ground for on-chip USB transceiver.                        |

| 12  | DMINUS   | I/O  | USB D- signal.                                             |

| 13  | DPLUS    | I/O  | USB D+ signal.                                             |

| 14  | USBVCC   | P    | 3.3V Power Supply for on-chip USB transceiver.             |

| 15  | ZREGVCC  | P    | 3.3V output from on-chip 5V-to-3.3V regulator.             |

| 16  | ZREGPWR  | P    | 5V Power Supply for on-chip 5V-to-3.3V regulator.          |

| 17 | RESETJ                | I           | Ontional automal Dayyar On Daget gional active law   |

|----|-----------------------|-------------|------------------------------------------------------|

| 18 | NC                    | 1           | Optional external Power-On-Reset signal, active low. |

| 19 | A DA2                 | _           | No connection. ATAPI Device Address bit 2.           |

|    |                       | O           |                                                      |

| 20 | XPWMEN                | <del></del> | USB power management mode enable.                    |

| 21 | A_DA1                 | 0           | ATAPI Device Address bit 1.                          |

| 22 | A_DA0                 | 0           | ATAPI Device Address bit 0.                          |

| 23 | SCL                   | I/O         | Clock for external Serial EEPROM.                    |

| 24 | A_CS1J                | 0           | ATAPI Chip Select 1, active low.                     |

| 25 | SDA                   | I/O         | Data/Address for external Serial EEPROM.             |

| 26 | A_CS0J                | О           | ATAPI Chip Select 0, active low.                     |

| 27 | NC                    | _<br>       | No connection.                                       |

| 28 | VCC                   | P           | 5V Power Supply.                                     |

| 29 | CFPWRJ <sup>(2)</sup> | О           | CompactFlash Power Enable, active low.               |

| 30 | Reserved              | _           | Reserved, must be tied to ground.                    |

| 31 | A_DIORJ               | 0           | ATAPI I/O Read signal, active low.                   |

| 32 | A_DIOWJ               | 0           | ATAPI I/O Write signal, active low.                  |

| 33 | A_DD0                 | I/O         | ATAPI Data Bus bit 0.                                |

| 34 | A_DD8                 | I/O         | ATAPI Data Bus bit 8.                                |

| 33 | A_DD1                 | I/O         | ATAPI Data Bus bit 1.                                |

| 36 | A_DD9                 | I/O         | ATAPI Data Bus bit 9.                                |

| 37 | GND                   | P           | Ground.                                              |

| 38 | A_DD2                 | I/O         | ATAPI Data Bus bit 2.                                |

| 39 | A_DD10                | I/O         | ATAPI Data Bus bit 10.                               |

| 40 | A_DD3                 | I/O         | ATAPI Data Bus bit 3.                                |

| 41 | A_DD11                | I/O         | ATAPI Data Bus bit 11.                               |

| 42 | A_DD4                 | I/O         | ATAPI Data Bus bit 4.                                |

| 43 | A_DD12                | I/O         | ATAPI Data Bus bit 12.                               |

| 44 | A_DD5                 | I/O         | ATAPI Data Bus bit 5.                                |

| 45 | A_DD13                | I/O         | ATAPI Data Bus bit 13.                               |

| 46 | A_DD6                 | I/O         | ATAPI Data Bus bit 6.                                |

| 47 | A_DD14                | I/O         | ATAPI Data Bus bit 14.                               |

| 48 | VCC                   | P           | 5V Power Supply.                                     |

| 49 | A_DD7                 | I/O         | ATAPI Data Bus bit 7.                                |

| 50 | A_DD15                | I/O         | ATAPI Data Bus bit 15.                               |

| 51 | $CD1J^{(1)}$          | I           | CompactFlash Card Detection 1, active low.           |

| 52 | Reserved              | _           | Reserved, must be tied to ground.                    |

| 53 | A_INTRQ               | I           | ATAPI interrupt request.                             |

| 54 | Reserved              |             | Reserved, must be tied to ground.                    |

| 55 | A_RSTJ                | О           | ATAPI reset, active low.                             |

| 56 | $CD2J^{(1)}$          | I           | CompactFlash Card Detection 1, active low.           |