| PIC16F87X                                           |  |

|-----------------------------------------------------|--|

| Порты ввода/вывода<br>в микроконтроллерах PIC16F87X |  |

Перевод основывается на технической документации DS30292C компании Microchip Technology Incorporated, USA.

© ООО "Микро-Чип" Москва - 2002

Распространяется бесплатно.

Полное или частичное воспроизведение материала допускается только с письменного разрешения ООО «Микро-Чип» тел. (095) 737-7545 www.microchip.ru

# Содержание

| 3.0 Порты ввода/вывода        | 3 |

|-------------------------------|---|

| 3.1 Регистры PORTA и TRISA    |   |

| 3.2 Регистры PORTB и TRISB    |   |

| 3.3 Регистры PORTC и TRISC    |   |

| 3.4 Регистры PORTD и TRISD    |   |

| 3.5 Регистры PORTE и TRISE    |   |

| 3.6 Ведомый параллельный порт |   |

# 3.0 Порты ввода/вывода

Некоторые каналы портов ввода/вывода мультиплицированы с периферийными модулями микроконтроллера. Когда периферийный модуль включен, вывод не может использоваться как универсальный канал ввода/вывода.

Дополнительную информацию по работе с портами ввода/вывода смотрите в технической документации DS33023 "PICmicro™ Mid-Range Reference Manual".

# 3.1 Регистры PORTA и TRISA

PORTA — 6-разрядный порт ввода вывода. Все каналы PORTA имеют соответствующие биты направления в регистре TRISA, позволяющие настраивать канал как вход или выход. Запись '1' в TRISA переводит соответствующий выходной буфер 3-е состояние. Запись '0' в регистр TRISA определяет соответствующий канал как выход, содержимое защелки PORTA передается на вывод микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Чтение регистра PORTA возвращает состояние на выводах порта, а запись производится в защелку PORTA. Все операции записи в порт выполняются по принципу «чтение – модификация - запись», т.е. сначала производится чтение состояния выводов порта, затем изменение и запись в защелку.

RA4 - имеет триггер Шмидта на входе и открытый сток на выходе, мультиплицирован с тактовым входом ТОСКІ. Все остальные каналы PORTA имеют TTL буфер на входе и полнофункциональные выходные КМОП буферы.

Каналы PORTA мультиплицированы с аналоговыми входами АЦП и аналоговым входом источника опорного напряжения  $V_{REF}$ . Биты управления режимов работы каналов порта ввода/вывода PORTA находятся в регистре ADCON1.

**Примечание.** После сброса по включению питания выводы настраиваются как аналоговые входы, а чтение дает результат '0'.

Биты регистра TRISA управляют направлением каналов PORTA, даже когда они используются как аналоговые входы. Пользователь должен удостовериться, что соответствующие каналы PORTA настроены на вход при использовании их в качестве аналоговых входов.

Пример 3-1 Инициализация PORTA

| BCF<br>BCF<br>CLRF    | STATUS, RP1<br>STATUS, RP0<br>PORTA | ; Выбрать банк 0<br>; Инициализация защелок PORTA                                            |

|-----------------------|-------------------------------------|----------------------------------------------------------------------------------------------|

| BSF<br>MOVLW<br>MOVWF | STATUS, RP0<br>0X06<br>ADCON1       | ; Выбрать банк 1<br>; Выключить компаратор,<br>; каналы PORTA – цифровые входы/выходы        |

| MOVLW                 | 0xCF                                | ; Значение для инициализации<br>; направления каналов PORTA                                  |

| MOVWF                 | TRISA                               | ; Настроить RA<3:0> как входы,<br>; настроить RA<5:4> как выходы<br>; Биты TRISA<7:6> всегда |

; читаются как '0'.

Puc. 3-1 Структурная схема выводов RA3:RA0 и RA5 Шина Защелка данных данных D Q WR порт Q CK → I/O Защелка TRIS Ν D Q WR **TRIS** Vss  $\overline{\mathsf{q}}$ CK аналогового входа Входной RD буфер **TRIS** TTL Q D ΕN RD порт к АЦП

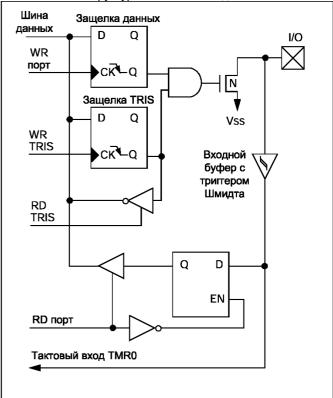

Puc. 3-2 Структурная схема вывода RA4/T0CKI

**Примечание.** Вывод имеет защитный диоды, подключенный только к  $V_{SS}$ .

**Примечание.** Выводы портов имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

Таблица 3-1 Функциональное назначение выводов PORTA

| Обозначение<br>вывода | № бита | Тип<br>буфера | Описание                                                                                                    |

|-----------------------|--------|---------------|-------------------------------------------------------------------------------------------------------------|

| RA0/AN0               | бит 0  | TTL           | Двух направленный порт ввода/вывода или аналоговый вход                                                     |

| RA1/AN1               | бит 1  | TTL           | Двух направленный порт ввода/вывода или аналоговый вход                                                     |

| RA2/AN2               | бит 2  | TTL           | Двух направленный порт ввода/вывода или аналоговый вход                                                     |

| RA3/AN3               | бит 3  | TTL           | Двух направленный порт ввода/вывода или аналоговый вход                                                     |

| RA4/T0CKI             | бит 4  | ST            | Двух направленный порт ввода/вывода, может использоваться как T0CKI, выход с открытым стоком                |

| RA5/-SS/AN4           | бит 5  | TTL           | Двух направленный порт ввода/вывода или вход выбора синхронного последовательного порта или аналоговый вход |

Обозначение: ST = вход с триггером Шмидта; TTL = входной буфер TTL.

**Таблица 3-2** Регистры и биты связанные с работой PORTA

| Адрес | Имя    | Бит 7 | Бит 6 | Бит 5  | Бит 4     | Бит 3     | Бит 2    | Бит 1 | Бит 0 | Сброс<br>POR, BOR | Другие<br>сбросы |

|-------|--------|-------|-------|--------|-----------|-----------|----------|-------|-------|-------------------|------------------|

| 05h   | PORTA  | -     | -     | RA5    | RA4       | RA3       | RA2      | RA1   | RA0   | 0x 0000           | 0u 0000          |

| 85h   | TRISA  | -     | -     | Регист | р направл | ения данн | ых PORTA | 1     |       | 11 1111           | 11 1111          |

| 9Fh   | ADCON1 | ADFM  | -     | -      | -         | PCFG3     | PCFG2    | PCFG1 | PCFG0 | 0 0000            | 0 0000           |

Обозначения: - = не используется, читается как 0; u = не изменяется; x = не известно; q = зависит от условий. Затененные биты на работу не влияют.

**Примечание.** При работе модуля MSSP в ведомом режиме SPI с использованием вывода -SS, АЦП должно работать в одном из следующих режимов PCFG3:PCFG0 = 0100, 0101, 011x, 1101, 1110, 1111.

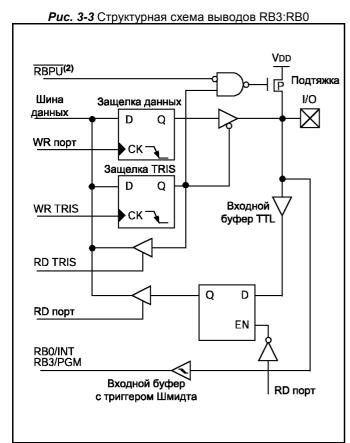

#### 3.2 Регистры PORTB и TRISB

PORTB — 8-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISB определяют направление каналов порта. Установка битва в '1' регистра TRISB переводит выходной буфер в 3-е состояние. Запись '0' в регистр TRISB настраивает соответствующий канал как выход, содержимое защелки PORTB передается на вывод микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Три вывода PORTB мультиплицированы со схемой низковольтного программирования: RB3/PGM, RB6/PGC, RB7/PGD. Описание режима низковольтного программирования смотрите в разделе 12.0.

К каждому выводу PORTB подключен внутренний подтягивающий резистор. Бит -RBPU (OPTION\_REG <7>) определяет, подключены (-RBPU=0) или нет (-RBPU=1) подтягивающие резисторы. Подтягивающие резисторы автоматически отключаются, когда каналы порта настраиваются на выход и после сброса по включению питания POR.

Четыре канала PORTB RB7:RB4 настроенные на вход могут генерировать прерывания по изменению логического уровня сигнала на входе. Если один из каналов RB7:RB4 настроен на выход, то он не может быть источником прерываний. Сигнал на выводах RB7:RB4 сравнивается со значением, сохраненным при последнем чтении PORTB. В случае несовпадения одного из значений устанавливается флаг RBIF (INTCON<0>), если разрешено, генерируется прерывание.

Это прерывание может ввести микроконтроллер из режима SLEEP. В подпрограмме обработки прерываний необходимо сделать следующие действия:

- выполнить чтение или запись в PORTB исключив несоответствие;

- сбросить флаг RBIF и'0'.

Несоответствие сохраненного значения с сигналом на входе PORTB всегда устанавливает бит RBIF в '1'. Чтение из PORTB прервет условие несоответствия и позволит сбросить флаг RBIF в '0'.

Прерывания по изменению сигнала на входах рекомендуется использовать для определения нажатия клавиш, и когда PORTB полностью задействован для реализации клавиатуры. Не рекомендуется опрашивать PORTB при использовании прерываний по изменению входного сигнала.

Прерывания по изменению сигнала на входах PORTB и программа переключения конфигурации этих каналов позволяет реализовать простой интерфейс обслуживания клавиатуры, с выходом из режима SLEEP по нажатию клавиш (см. пример AN552 в книге Microchip *Embedded Control Handbook* или на WEB узлах технической поддержки www.microchip.com и www.microchip.ru).

RB0/INT вход внешнего источника прерываний, настраиваемых битом INTEDG (OPTION\_REG<6>). Подробное описание использования прерываний INT смотрите в разделе 12.10.1.

Puc. 3-4 Структурная схема выводов RB7:RB4 Vdd RBPU(2) Подтяжка Шина I/O Защелка данных данных WR порт Входной буфер тригтером Шмидта CK Защелка TRIS D Q WR TRIS Входной буфер TTL **RD TRIS** Защелка Q D RD порт ΕN Q1 RBIF Q D RD порт От других выводов RB7:RB4 ΕN Q3 RB7:RB6 Вход последовательного программирования

Примечания:

- 1. Выводы портов имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

- 2. Для включения подтягивающих резисторов необходимо установить в '1' соответствующий бит TRIS и сбросить в '0' бит -RBPU (OPTION\_REG<7>).

**Таблица 3-3** Функциональное назначение выводов PORTB

| Обозначение<br>вывода | № бита | Тип<br>буфера         | Описание                                                                                                                                                                    |

|-----------------------|--------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT               | бит 0  | TTL/ST <sup>(1)</sup> | Двух направленный порт ввода/вывода с программным включением подтягивающего резистора, вход внешнего прерывания.                                                            |

| RB1                   | бит 1  | TTL                   | Двух направленный порт ввода/вывода с программным включением подтягивающего резистора.                                                                                      |

| RB2                   | бит 2  | TTL                   | Двух направленный порт ввода/вывода с программным включением подтягивающего резистора.                                                                                      |

| RB3/PGM               | бит 3  | TTL                   | Двух направленный порт ввода/вывода с программным включением подтягивающего резистора или вход программирования в режиме LVP.                                               |

| RB4                   | бит 4  | TTL                   | Двух направленный порт ввода/вывода с программным включением подтягивающего резистора и прерыванием по изменению входного сигнала.                                          |

| RB5                   | бит 5  | TTL                   | Двух направленный порт ввода/вывода с программным включением подтягивающего резистора и прерыванием по изменению входного сигнала.                                          |

| RB6/PGC               | бит 6  | TTL/ST <sup>(2)</sup> | Двух направленный порт ввода/вывода с программным включением подтягивающего резистора и прерыванием по изменению входного сигнала. Тактовый вход в режиме программирования. |

| RB7/PGD               | бит 7  | TTL/ST <sup>(2)</sup> | Двух направленный порт ввода/вывода с программным включением подтягивающего резистора и прерыванием по изменению входного сигнала. Вывод данных в режиме программирования.  |

Обозначение: ST = вход с триггером Шмидта; TTL = входной буфер TTL.

#### Примечания:

- 1. Входной буфер с триггером Шмидта при использовании внешних прерываний.

- 2. Входной буфер с триггером Шмидта при работе в режиме последовательного программирования.

- 3. Низковольтное программирование (LVP) ICSP разрешено по умолчанию, что отключает функцию цифрового порта ввода/вывода RB3. Для использования RB3 в качестве цифрового ввода/вывода необходимо выключить режим низковольтного программирования.

Таблица 3-4 Регистры и биты связанные с работой PORTB

| Адрес     | Имя        | Бит 7  | Бит 6      | Бит 5     | Бит 4    | Бит 3 | Бит 2 | Бит 1 | Бит 0 | Сброс<br>POR, BOR | Другие<br>сбросы |

|-----------|------------|--------|------------|-----------|----------|-------|-------|-------|-------|-------------------|------------------|

| 06h, 106h | PORTB      | RB7    | RB6        | RB5       | RB4      | RB3   | RB2   | RB1   | RB0   | xxxx xxxx         | uuuu uuuu        |

| 86h, 186h | TRISB      | Регист | р направле | ения данн | ых PORTE | 3     |       |       |       | 1111 1111         | 1111 1111        |

| 81h, 181h | OPTION_REG | -RBPU  | INTEDG     | TOCS      | T0SE     | PSA   | PS2   | PS1   | PS0   | 1111 1111         | 1111 1111        |

Обозначения: - = не используется, читается как 0; u = не изменяется; x = не известно; q = зависит от условий. Затененные биты на работу не влияют.

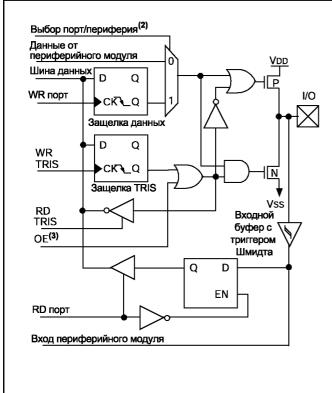

# 3.3 Регистры PORTC и TRISC

PORTC – 8-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISC определяют направление каналов порта. Установка битва в '1' регистра TRISC переводит выходной буфер в 3-е состояние. Запись '0' в регистр TRISC настраивает соответствующий канал как выход, содержимое защелки PORTC передается на вывод микроконтроллера (если выходная защелка подключена к выводу микроконтроллера).

Выводы PORTC мультиплицированы с несколькими периферийными модулями (см. таблицу 3-5). На каналах PORTC присутствует входной буфер с триггером Шмидта.

Когда модуль MSSP включен в режиме  $I^2$ C, выводы PORTC<4:3> могут поддерживать уровни выходных сигналов по спецификации  $I^2$ C или SMBus в зависимости от состояния бита CKE(SSPSTAT<6>).

При использовании периферийных модулей необходимо соответствующим образом настраивать биты регистра TRISC для каждого вывода PORTC (см. описание периферийных модулей). Некоторые периферийные модули отменяют действие битов TRISC принудительно настраивая вывод на вход или выход. В связи с чем, не рекомендуется использовать команды "чтение - модификация - запись" с регистром TRISC.

**Рис. 3-5** Структурная схема выводов RC7:RC5, RC2:RC0

**Рис. 3-6** Структурная схема выводов RC4:RC3 В<u>ыбор</u> порт/периферия<sup>(2)</sup> Данные от периферийного модуля <u>Vdd</u> Шина данных D Q I/O WR порт ·ck³–q Защелка данн D Q WR TRIS ·CK**₹**\_Q Защелка TRIS Vss RD Входные TRIS буферы с OE<sup>(3)</sup> триггером Шмидта Q D ΕN RD порт 0 **Вход SSPI** CKE SSPSTAT<6>

Примечания:

- 1. Выводы портов имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

- 2. Сигнал режима канала вывод используется периферийным модулем или цифровой порт ввода/вывода.

- 3. Сигнал разрешения (ОЕ) от периферийного модуля, настраивать канал как выход.

Таблица 3-5 Функциональное назначение выводов PORTC

| Обозначение<br>вывода | № бита | Тип<br>буфера | Описание                                                                                                                                    |

|-----------------------|--------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/T1CKI       | бит 0  | ST            | Двух направленный порт ввода/вывода или выход резонатора TMR1 / вход тактового сигнала для TMR1.                                            |

| RC1/T1OSI/CCP2        | бит 1  | ST            | Двух направленный порт ввода/вывода или вход резонатора TMR1 или вход захвата 2 / выход сравнения 2 / выход ШИМ 2.                          |

| RC2/CCP1              | бит 2  | ST            | Двух направленный порт ввода/вывода или вход захвата 1 / выход сравнения 1 / выход ШИМ 1.                                                   |

| RC3/SCK/SCL           | бит 3  | ST            | Двух направленный порт ввода/вывода или вход/выход тактового сигнала модуля MSSP в SPI, I <sup>2</sup> C режиме.                            |

| RC4/SDI/SDA           | бит 4  | ST            | Двух направленный порт ввода/вывода или вход данных в режиме SPI или вход/выход данных в режиме I <sup>2</sup> C.                           |

| RC5/SDO               | бит 5  | ST            | Двух направленный порт ввода/вывода или выход данных в режиме SPI.                                                                          |

| RC6/TX/CK             | бит 6  | ST            | Двух направленный порт ввода/вывода или выход передатчика USART в асинхронном режиме или линия тактового сигнала USART в синхронном режиме. |

| RC7/RX/DT             | бит 7  | ST            | Двух направленный порт ввода/вывода или вход приемника USART в асинхронном режиме или линия данных USART в синхронном режиме.               |

Обозначение: ST = вход с триггером Шмидта.

Таблица 3-6 Регистры и биты связанные с работой PORTC

| Адрес | Имя   | Бит 7  | Бит 6     | Бит 5     | Бит 4    | Бит 3 | Бит 2 | Бит 1 | Бит 0 | Сброс<br>POR, BOR | Другие<br>сбросы |

|-------|-------|--------|-----------|-----------|----------|-------|-------|-------|-------|-------------------|------------------|

| 07h   | PORTC | RC7    | RC6       | RC5       | RC4      | RC3   | RC2   | RC1   | RC0   | xxxx xxxx         | uuuu uuuu        |

| 87h   | TRISC | Регист | р направл | ения данн | ых PORTO |       |       |       |       | 1111 1111         | 1111 1111        |

Обозначения: - = не используется, читается как 0; и = не изменяется; х = не известно; q = зависит от условий.

# 3.4 Регистры PORTD и TRISD

PORTD и TRISD не реализованы в микроконтроллерах PIC16F873 и PIC16F876.

PORTD - 8-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISD определяют направление каналов порта.

PORTD может работать как 8-разрядный микропроцессорный порт (ведомый параллельный порт), если бит PSPMODE (TRISE<4>) установлен в '1'. В режиме ведомого параллельного порта ко входу подключены буферы TTL.

(режим цифрового порта ввода/вывода) I/O Шина Защелка данных данных D 0 WR порт ▶CK ̄\ Защелка TRIS D O WR **TRIS** CK Входной буфер с триггером Шмидта RD **TRIS** Q D ΕN RD порт

**Рис. 3-7** Структурная схема выводов PORTD

**Примечание.** Выводы портов имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

Таблица 3-7 Функциональное назначение выводов PORTD

| Обозначение<br>вывода | № бита | Тип<br>буфера         | Описание                                                                          |

|-----------------------|--------|-----------------------|-----------------------------------------------------------------------------------|

| RD0/PSP0              | бит 0  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вывод ведомого параллельного порта бит 0. |

| RD1/PSP1              | бит 1  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вывод ведомого параллельного порта бит 1. |

| RD2/PSP2              | бит 2  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вывод ведомого параллельного порта бит 2. |

| RD3/PSP3              | бит 3  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вывод ведомого параллельного порта бит 3. |

| RD4/PSP4              | бит 4  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вывод ведомого параллельного порта бит 4. |

| RD5/PSP5              | бит 5  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вывод ведомого параллельного порта бит 5. |

| RD6/PSP6              | бит 6  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вывод ведомого параллельного порта бит 6. |

| RD7/PSP7              | бит 7  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вывод ведомого параллельного порта бит 7. |

Обозначение: ST = вход с триггером Шмидта; TTL = входной буфер TTL.

Примечание 1. В режиме цифрового ввода/вывода подключен буфер с триггером Шмидта, а в режиме ведомого параллельного порта подключен входной буфер TTL.

**Таблица 3-8** Регистры и биты связанные с работой PORTD

| i a   | <i>олица 3-</i> 0 г е | пистры и | ONLIDE CEX                                         | ізаппыс ( | <i>-</i> расстои | IONID |         |           |         |                   |                  |

|-------|-----------------------|----------|----------------------------------------------------|-----------|------------------|-------|---------|-----------|---------|-------------------|------------------|

| Адрес | Имя                   | Бит 7    | Бит 6                                              | Бит 5     | Бит 4            | Бит 3 | Бит 2   | Бит 1     | Бит 0   | Сброс<br>POR, BOR | Другие<br>сбросы |

| 08h   | PORTD                 | RD7      | RD6                                                | RD5       | RD4              | RD3   | RD2     | RD1       | RD0     | xxxx xxxx         | uuuu uuuu        |

|       |                       |          |                                                    |           |                  |       | 1102    | 1101      | TABO    |                   |                  |

| 88h   | TRISD                 | Регист   | Регистр направления данных PORTD   1111   1111   1 |           |                  |       |         |           |         |                   | 1111 1111        |

| 89h   | TRISE                 | IBF      | OBF                                                | IBOV      | PSPMOD           | E -   | Рег. на | пр. данны | x PORTE | 0000 -111         | 0000 -111        |

Обозначения: - = не используется, читается как 0; u = не изменяется; x = не известно; q = зависит от условий. Затененные биты на работу не влияют.

# 3.5 Регистры PORTE и TRISE

PORTE и TRISE не реализованы в микроконтроллерах PIC16F873 и PIC16F876.

PORTE имеет три вывода (RE0/-RD/AN5, RE1/-WR/AN6, RE2/-CS/AN7) индивидуально настраиваемые на вход или выход. Выводы PORTE имеют входной буфер Шмидта.

Каналы PORTE станут управляющими выводами ведомого параллельного порта когда бит PSPMODE(TRISE<4>) установлен в '1'. В этом режиме биты TRISE<2:0> должны быть установлены в '1'. Также в регистре ADCON1 необходимо настроить выводе PORTE как цифровые каналы ввода/вывода. В режиме ведомого параллельного порта к выводам PORTE подключены входные буферы TTL.

Выводы PORTE мультиплицированы с аналоговыми входами. Когда каналы PORTE настроены как аналоговые входы, биты регистра TRISE также управляют направлением данных PORTE (чтение будет давать результат '0').

**Примечание.** После сброса по включению питания выводы настраиваются как аналоговые входы, а чтение дает результат '0'.

(режим цифрового порта ввода/вывода) I/O Шина Защелка данных данных D WR порт ·CK ¯₹ Защелка TRIS D WR **TRIS** ·CK ₹ Входной буфер с триггером Шмидта RD **TRIS** Q D ΕN RD порт

**Puc. 3-8** Структурная схема выводов PORTE

*Примечание.* Выводы портов имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

**Таблица 3-9** Функциональное назначение выволов PORTE

| Обозначение<br>вывода | № бита | Тип<br>буфера         | Описание                                                                                                                                                                                                                              |

|-----------------------|--------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RE0/-RD/AN5           | бит 0  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вход управления чтением ведомого параллельного порта или аналоговый вход: -RD 1 = Ожидание 0 = Операция чтения. Защелка PORTD подключена к выводам PORTD (если -CS = 0)                       |

| RE1/-WR/AN6           | бит 1  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вход управления записью ведомого параллельного порта или аналоговый вход: -WR 1 = Ожидание 0 = Операция записи. Данные с выводов PORTD сохраняются во внутренней защелке PORTD (если -CS = 0) |

| RE2/-CS/AN7           | бит 2  | ST/TTL <sup>(1)</sup> | Двух направленный порт ввода/вывода или вход выбора микросхемы ведомого параллельного порта или аналоговый вход: -CS 1 = Микросхема не выбрана 0 = Микросхема выбрана                                                                 |

Обозначение: ST = вход с триггером Шмидта; TTL = входной буфер TTL.

**Примечание 1.** В режиме цифрового ввода/вывода подключен буфер с триггером Шмидта, а в режиме ведомого параллельного порта подключен входной буфер TTL.

#### Регистр TRISE (адрес 89h)

| R-0   | R-0 | R-0  | R/W-0   | U-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|------|---------|-----|-------|-------|-------|

| IBF   | OBF | IBOV | PSPMODE | -   | BIT2  | BIT1  | BIT0  |

| Бит 7 |     |      |         |     |       |       | Бит 0 |

R – чтение бита

W – запись бита

U – не реализовано, читается как 0

-n - значение после POR

-x - неизвестное значение после POR

#### Биты управления и статуса ведомого параллельного порта

бит 7: **IBF**: Бит статуса приемного буфера

1 = принят байт данных

0 = байт данных не был получен

бит 6: **ОВF**: Бит статуса передающего буфера

1 = предварительно записанный байт данных еще не прочитан

0 = выходной буфер был прочитан

бит 5: ІВОУ: Флаг переполнения приемного буфера

1 = произошла новая запись, а предыдущий байт не был прочитан (сбрасывается программно)

0 = переполнения не было

бит 4: PSPMODE: Режим работы PORTD

1 = PORTD работает как ведомый параллельный порт

0 = PORTD работает в режиме цифровых каналов ввода/вывода

бит 3: Не реализован: читается как '0'

#### Биты управления направлением данных PORTE

бит 2: BIT2: Направление вывода RE2/-CS/AN7

1 = вход 0 = выход

бит 1: BIT1: Направление вывода RE1/-WR/AN6

1 = вход 0 = выход

бит 0: **BIT0**: Направление вывода RE0/-RD/AN5

1 = вход 0 = выход

Таблица 3-10 Регистры и биты связанные с работой PORTE

| Адрес | Имя    | Бит 7 | Бит 6 | Бит 5 | Бит 4     | Бит 3 | Бит 2                   | Бит 1 | Бит 0 | Сброс<br>POR, BOR | Другие<br>сбросы |

|-------|--------|-------|-------|-------|-----------|-------|-------------------------|-------|-------|-------------------|------------------|

| 09h   | PORTE  | -     | -     | -     | -         | -     | RE2                     | RE1   | RE0   | xxx               | uuu              |

| 89h   | TRISE  | IBF   | OBF   | IBOV  | PSPMODE - |       | Рег. напр. данных PORTE |       |       | 0000 -111         | 0000 -111        |

| 9Fh   | ADCON1 | ADFM  | -     | -     | -         | PCFG3 | PCFG2                   | PCFG1 | PCFG0 | 0 0000            | 0 0000           |

Обозначения: - = не используется, читается как 0; u = не изменяется; x = не известно; q = зависит от условий. Затененные биты на работу не влияют.

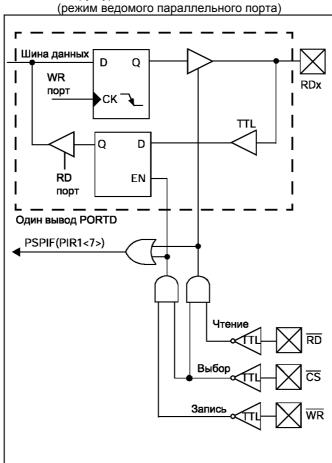

# 3.6 Ведомый параллельный порт

Ведомый параллельный порт (PSP) не реализован в микроконтроллерах PIC16F873 и PIC16F876.

PORTD работает как 8-разрядный параллельный порт (или порт микропроцессора) когда бит PSPMODE(TRISE<4>) установлен в '1'. В режиме ведомого данные асинхронно читаются или записываются внешними сигналами -RD (RE0/-RD) или -WR(RE1/-WR) соответственно.

Внешний микропроцессор может читать/записывать данные в PORTD. Операции чтения записи выполняются при низком логическом уровне сигналов на входах -RD, -WR и низким логическим уровнем сигнала на входе выбора микросхемы -CS. Биты TRISE (TRISE<2:0>) должны быть установлены в '1'. В регистре ADCON1 выводы RE2:RE0 должны быть настроены как цифровые каналы ввода/вывода (биты PCFG3:PCFG0).

Фактически существуют два 8-разрядных регистра, один для приема данных другой для передачи. Пользователь записывает 8-разрядные данные в выходную защелку PORTD, а читает данные со входной защелки (обратите внимание, выходная и входная защелка имеют один и тот же адрес). В этом режиме значение битов регистра TRISE игнорируется, т.к. направлением данных управляет внешнее устройство.

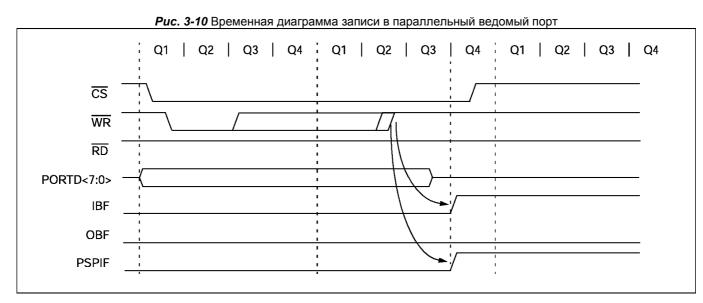

Запись в PSP происходит, если выводы -CS и -WR имеют низкий уровень сигнала. После перехода сигнала на выводе -CS или -WR в высокий уровень данные сохраняются во входной защелке на такте Q2 (см. рисунок 3-10). На такте Q4 устанавливаются в '1' бит IBF(TRISE<7>) и флаг прерываний PSPIF(PIR<7>). Бит IBF может быть сброшен в '0' только чтением регистра PORTD. Бит переполнения IBOV(TRISE<5>) устанавливается в '1', если произошла следующая запись в PSP, а предыдущий байт не был прочитан.

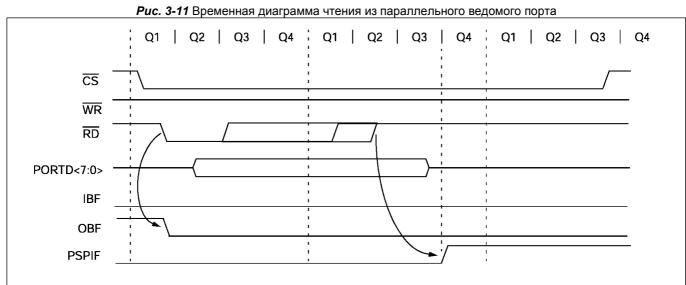

Чтение из PSP происходит, если выводы -CS и -RD имеют низкий уровень сигнала. Немедленно сбрасывается в '0' бит OBF(TRISE<6>), указывающий, что PORTD ожидает чтение внешней шиной (см. рисунок 3-11). После перехода сигнала на выводе -CS или -RD в высокий уровень устанавливается флаг прерывания PSPIF на такте Q4 (только после такта Q2), указывая, что чтение завершено. Бит OBF остается сброшенным в '0' пока не будут загружены новые данные в PORTD.

Когда режим PSP выключен, биты IBF и OBF равняются нулю, а предварительно установленный в '1' бит IBOV должен быть сброшен программно.

Флаг прерывания PSPIF устанавливается в '1' по завершению каждой операции чтения или записи (сбрасывается в '0' программно). Разрешить/запретить прерывания от модуля PSP можно установкой/сбросом бита PSPIE (PIE1<7>).

**Рис. 3-9** Структурная схема выводов PORTD и PORTE

*Примечание.* Выводы портов имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

**Таблица 3-11** Регистры и биты связанные с работой ведомого параллельного порта

| Адрес | Имя    | Бит 7  | Бит 6     | Бит 5 | Бит 4     | Бит 3                         | Бит 2 | Бит 1  | Бит 0     | Сброс<br>POR, BOR | Другие<br>сбросы |

|-------|--------|--------|-----------|-------|-----------|-------------------------------|-------|--------|-----------|-------------------|------------------|

| 001   | DODED  | _      |           |       |           |                               |       |        |           |                   |                  |

| 08h   | PORTD  | Запись | в выходну | RID   | XXXX XXXX | uuuu uuuu                     |       |        |           |                   |                  |

| 09h   | PORTE  | _      | _         | -     | _         | _                             | RE2   | RE1    | RE0       | xxx               | uuu              |

|       |        |        |           |       |           | _                             |       |        | _         |                   |                  |

| 89h   | TRISE  | IBF    | OBF       | IBOV  | PSPMOD    | E   - Per. напр. данных PORTE |       |        | 0000 -111 | 0000 -111         |                  |

| 0Ch   | PIR1   | PSPIF* | ADIF      | RCIF  | TXIF      | SSPIF                         | CCP1F | TMR2IF | TMR1IF    | 0000 0000         | 0000 0000        |

| 8Ch   | PIE1   | PSPIE* | ADIE      | RCIE  | TXIE      | SSPIE                         | CCP1E | TMR2IE | TMR1IE    | 0000 0000         | 0000 0000        |

| 9Fh   | ADCON1 | ADFM   | -         | -     | -         | PCFG3                         | PCFG2 | PCFG1  | PCFG0     | 0 0000            | 0 0000           |

Обозначения: - = не используется, читается как 0; u = не изменяется; x = не известно; q = зависит от условий. Затененные биты на работу не влияют.

*Примечание\**. Биты PSPIE и PSPIF в микроконтроллерах PIC16F873, PIC16F876 не используются.

# Уважаемые господа!

OOO «Микро-Чип» поставляет полную номенклатуру комплектующих фирмы Microchip Technology Inc

и осуществляет качественную техническую поддержку на русском языке.

С техническими вопросами Вы можете обращаться по адресу <a href="mailto:support@microchip.ru">support@microchip.ru</a>

По вопросам поставок комплектующих Вы можете обращаться к нам по телефонам:

(095) 963-9601 (095) 737-7545

и адресу sales@microchip.ru

На сайте www.microchip.ru

Вы можете узнать последние новости нашей фирмы, найти техническую документацию и информацию по наличию комплектующих на складе.