## PIC18FXX2

Однокристальные 8-разрядные FLASH CMOS микроконтроллеры с 10 — разрядным АЦП компании Microchip Technology Incorporated

- PIC18F242

- PIC18F252

- PIC18F442

- PIC18F452

Часть 5 (Порты ввода/вывода)

Перевод основывается на технической документации DS39564A компании Microchip Technology Incorporated, USA.

© ООО "Микро-Чип" Москва - 2003

Распространяется бесплатно.

Полное или частичное воспроизведение материала допускается только с письменного разрешения ООО «Микро-Чип»

тел. (095) 737-7545

www.microchip.ru

# PIC18FXX2 Data Sheet

High Performance, Enhanced FLASH Microcontrollers with 10-Bit A/D

**Trademarks:** The Microchip name, logo, PIC, PICmicro, PICMASTER, PIC-START, PRO MATE, KEELOQ, SEEVAL, MPLAB and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

Total Endurance, ICSP, In-Circuit Serial Programming, Filter-Lab, MXDEV, microID, FlexROM, fuzzyLAB, MPASM, MPLINK, MPLIB, PICDEM, ICEPIC, Migratable Memory, FanSense, ECONOMONITOR and SelectMode are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Term Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

### 28/40-выводные высокоскоростные FLASH микроконтроллеры с 10-разрядным АЦП

### Высокоскоростной RISC микроконтроллер:

- Оптимизированная архитектура и система команд для написания программ на языке С

- Система команд совместима с командами семейств PIC16C, PIC17C и PIC18C

- Линейное адресное пространство памяти программ 32кбайта

- Линейное адресное пространство памяти данных 1 5кбайт

|            | Память п        | рограмм | Память | EEPROM                     |  |

|------------|-----------------|---------|--------|----------------------------|--|

| Устройство | Flash<br>(байт) | КОМАНП  |        | память<br>данных<br>(байт) |  |

| PIC18F242  | 16к             | 8192    | 768    | 256                        |  |

| PIC18F252  | 32к             | 16384   | 1536   | 256                        |  |

| PIC18F442  | 16к             | 8192    | 768    | 256                        |  |

| PIC18F452  | 32к             | 16384   | 1536   | 256                        |  |

- Быстродействие до 10MIPS:

- Тактовая частота от DC до 40МГц

- Частота генератора с вкл. PLL от 4МГц до 10МГц

- 16-разрядные команды, 8-разрядные данные

- Система приоритетов прерываний

- Аппаратное умножение 8х8 за один машинный цикл

### Характеристика периферийных модулей:

- Высокая нагрузочная способность портов ввода/ вывода

- Три входа внешних прерываний

- Модуль ТМR0: 8/16-разрядный таймер/счетчик с программируемым 8-разрядным предделителем

- Модуль TMR1: 16-разрядный таймер/счетчик

- Модуль TMR2: 8-разрядный таймер/счетчик с 8-разрядным регистром периода (основной для ШИМ)

- Модуль TMR3: 16-разрядный таймер/счетчик

- Вторичный генератор тактового сигнала на основе TMR1/TMR3

- Два модуля ССР

- Выводы модуля ССР могут работать как:

- 16-разрядный захват, максимальная разрешающая способность 6.25нс (TCY/16)

- 16-разрядное сравнение, максимальная разрешающая способность 100нс (ТСҮ)

- ШИМ, разрядность от 1 до 10 бит, Максимальная частота ШИМ 156кГц@8 бит; 39кГЦ@10 бит

## Характеристика периферийных модулей (продолжение):

- Модуль ведущего последовательного синхронного порта (MSSP)

- 3-х проводной интерфейс SPITM (поддерживает 4 режима)

- I2СТМ (ведущий и ведомый режим)

- Адресуемый модуль USART, поддержка интерфейса RS-485 и RS-232

- Модуль PSP, ведомый параллельный порт

### Аналоговые периферийные модули:

- Модуль 10-разрядного АЦП:

- Высокая скорость преобразования

- Работа модуля АЦП в SLEEP режиме микроконтроллера

- DNL =  $\pm 1$ Lsb, INL =  $\pm 1$ Lsb

- Программируемый детектор пониженного напряжения (PLVD)

- При обнаружении снижения напряжения возможна генерация прерываний

- Программируемый сброс по снижению напряжения питания

### Особенности микроконтроллеров

- 100 000 гарантированных циклов стирание/запись памяти программ

- 1 000 000 гарантированных циклов стирание/запись EEPROM памяти данных

- Возможность самопрограммирования

- Сброс по включению питания (POR), таймер включения питания (PWRT), таймер запуска генератора (OST)

- Сторожевой таймер WDT с отдельным RC генератором

- Программируемая защита кода программы

- Режим пониженного энергопотребления и режим SLEEP

- Выбор режима работы тактового генератора, включая:

- 4 x PLL (от основного генератора)

- Вторичный генератор (32кГц)

- Внутрисхемное программирование по двухпроводной линии (ICSP) с одним напряжением питания 5В

- Внутрисхемная отладка по двухпроводной линии (ICD)

### КМОП технология

- Высокоскоростная энергосберегающая КМОП технология

- Полностью статическая архитектура

- Широкий диапазон напряжений питания (от 2.0B до 5.5R)

- Промышленный и расширенный температурные диапазоны

## Содержание

| 9.  | Порты ввода/вывода              |    |

|-----|---------------------------------|----|

|     | Регистры PORTA, TRISA, LATA     |    |

|     | Perистры PORTB, TRISB, LATB     |    |

| 9.3 | В Регистры PORTC, TRISC, LATC   | 10 |

| 9.4 | Регистры PORTD, TRISD, LATD     | 12 |

| 9.5 | 5 Регистры PORTE, TRISE, LATE   | 14 |

| 9.6 | В Ведомый параллельный порт PSP |    |

### 9. Порты ввода/вывода

В зависимости от типа микроконтроллера реализовано пять или три порта ввода/вывода. Некоторые каналы портов ввода/вывода мультиплексированы с дополнительными функциями периферийных модулей микроконтроллера. В общем случае, когда используется периферийная функция, вывод не может использоваться как канал порта ввода/вывода.

Каждому порту соответствует три управляющих регистра:

- TRIS регистр выбора направления данных в каналах порта ввода/вывода

- РОRТ регистр порта (результатом чтения является логический уровень сигнала на выводах)

- LAT защелка порта ввода/вывода

Защелка порта ввода/вывода LAT особенно полезна при использовании команд со структурой «чтение - модификация - запись».

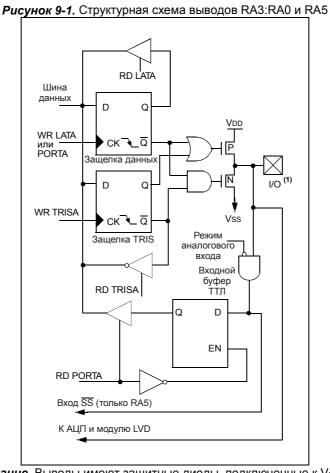

### 9.1 Регистры PORTA, TRISA, LATA

PORTA – 7-разрядный порт ввода/вывода. Все каналы PORTA имеют соответствующие биты направления в регистре TRISA, позволяющие настраивать канал как вход или выход. Запись '1' в TRISA переводит соответствующий выходной буфер в 3-е состояние. Запись '0' в регистр TRISA определяет соответствующий канал как выход, содержимое защелки PORTA передается на вывод микроконтроллера.

Чтение регистра PORTA возвращает состояние на выводах порта, а запись производится в защелку PORTA.

Регистр защелки LATA отображается на память данных. Операция типа «чтение – модификация – запись» с регистром LATA будет выполнена с данными, записанными в порт ввода/вывода PORTA.

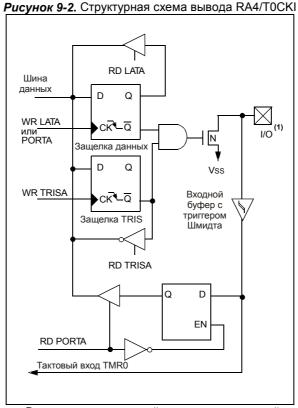

Вывод RA4/T0CKI имеет триггер Шмидта на входе и открытый сток на выходе, мультиплексирован с тактовым входом таймера TMR0. Все остальные каналы PORTA имеют TTL буфер на входе и полнофункциональные выходные КМОП буферы.

Другие каналы PORTA мультиплексированы с аналоговыми входами АЦП и аналоговым входом источника опорного напряжения V<sub>REF+</sub> и V<sub>REF-</sub>. Биты управления режимом работы каналов порта ввода/вывода PORTA находятся в регистре ADCON1 (управляющий регистр АЦП).

*Примечание.* После сброса по включению питания выводы RA5, RA3:RA0 настраиваются как аналоговые входы, чтение дает результат '0'. Выводы RA4, RA6 при сбросе POR настраиваются как цифровые входы.

Биты регистра TRISA управляют направлением каналов PORTA, даже когда они используются как аналоговые входы. Пользователь должен удостовериться, что соответствующие каналы PORTA настроены на вход при использовании их в качестве аналоговых входов.

**Пример 9-1.** Инициализация PORTA

| <b>р э- і.</b> иіні | ициализация г | ONIA                         |

|---------------------|---------------|------------------------------|

| CLRF                | PORTA         | ; Инициализация PORTA        |

|                     |               | ; с очисткой выходной        |

|                     |               | ; защелки данных             |

| CLRF                | LATA          | ; Альтернативный метод       |

|                     |               | ; очистки выходной           |

|                     |               | ; защелки данных             |

| MOVLW               | 0x07          | ; Настройка АЦП              |

| MOVWF               | ADCON1        | ; как цифровых входов        |

| MOVLW               | 0xCF          | ; Значение                   |

|                     |               | ; инициализации              |

|                     |               | ; направления данных         |

| MOVWF               | TRISA         | ; Установить RA<3:0> входами |

|                     |               | ; RA<5:4> выходами           |

*Примечание.* Выводы имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

*Примечание.* Вывод имеет защитный диод, подключенный только к V<sub>SS</sub>.

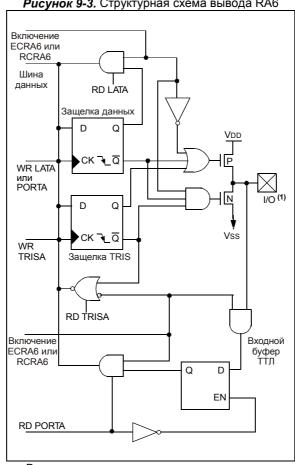

**Рисунок 9-3.** Структурная схема вывода RA6

*Примечание.* Вывод имеет защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

**Таблица 9-1.** Функциональное назначение выволов PORTA

| Обозначение               | № бита | Буфер | Описание                                                       |

|---------------------------|--------|-------|----------------------------------------------------------------|

| RA0/AN0                   | 0      | TTL   | Вход/выход или аналоговый вход.                                |

| RA1/AN1                   | 1      | TTL   | Вход/выход или аналоговый вход.                                |

| RA2/AN2/V <sub>REF-</sub> | 2      | TTL   | Вход/выход, аналоговый вход или V <sub>REF-</sub> .            |

| RA3/AN3/V <sub>REF+</sub> | 3      | TTL   | Вход/выход, аналоговый вход или V <sub>REF+</sub> .            |

| RA4/T0CKI                 | 4      | ST    | Вход/выход или вход тактового сигнала для TMR0.                |

|                           |        |       | Выход с открытым коллектором.                                  |

| RA5/AN4/-SS/LVDIN         | 5      | TTL   | Вход/выход, вход выбора ведомого SPI, аналоговый вход или вход |

|                           |        |       | детектора пониженного напряжения.                              |

| OSC2/CLKO/RA6             | 6      | TTL   | OSC2, выход тактового сигнала или канал порта ввода/вывода.    |

Обозначение: ST = вход с триггером Шмидта; TTL = входной буфер ТТЛ

**Таблица 9-2.** Регистры и биты, связанные с работой PORTA

| Адрес | Имя    | Бит 7 | Бит 6      | Бит 5                      | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0     | Значение<br>после<br>POR, BOR |

|-------|--------|-------|------------|----------------------------|-------|-------|-------|-------|-----------|-------------------------------|

| F80h  | PORTA  | -     | RA6        | RA5                        | RA4   | RA3   | RA2   | RA1   | RA0       | -x0x 0000                     |

| F89h  | LATA   | -     | Регистр вы | Регистр выходных данных    |       |       |       |       |           | -xxx xxxx                     |

| F92h  | TRISA  | -     | Регистр на | Регистр направления данных |       |       |       |       | -111 1111 |                               |

| FC1h  | ADCON1 | ADFM  | ADCS2      | -                          | -     | PCFG3 | PCFG2 | PCFG1 | PCFG0     | 00 0000                       |

Обозначения: х = неизвестно; и = не изменяется; г = резерв; - = не реализован, читается как '0'. Затененные ячейки на работу не влияют.

### 9.2 Регистры PORTB, TRISB, LATB

PORTB – 8-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISB определяют направление каналов порта. Установка битва в '1' регистра TRISB переводит выходной буфер в 3-е состояние. Запись '0' в регистр TRISB настраивает соответствующий канал как выход, содержимое защелки PORTB передается на вывод микроконтроллера.

Регистр защелки LATB отображается на память данных. Операция типа «чтение – модификация – запись» с регистром LATB будет выполнена с данными, записанными в порт ввода/вывода PORTB.

Пример 9-2. Инициализация PORTB

| ~ ~ _, , , , , , , , | I ANICO HICO ANICO I |   |                            |

|----------------------|----------------------|---|----------------------------|

| CLRF                 | PORTB                | ; | Инициализация PORTB        |

|                      |                      | ; | с очисткой выходной        |

|                      |                      | ; | защелки данных             |

| CLRF                 | LATB                 | ; | Альтернативный метод       |

|                      |                      | ; | очистки выходной           |

|                      |                      | ; | защелки данных             |

| MOVLW                | 0xCF                 | ; | Значение                   |

|                      |                      | ; | инициализации              |

|                      |                      | ; | направления данных         |

| MOVWF                | TRISB                | ; | Установить RB<3:0> входами |

|                      |                      | ; | RB<5:4> выходами           |

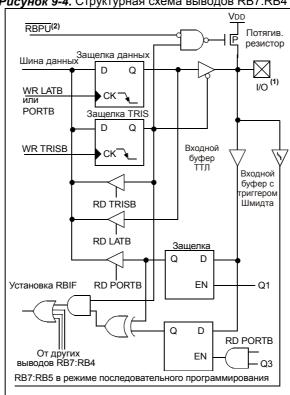

|                      |                      | ; | RB<7:6> входами            |

К каждому выводу PORTB подключен внутренний подтягивающий резистор. Бит -RBPU (INTCON2<7>) определяет, подключены (-RBPU=0) или нет (-RBPU=1) подтягивающие резисторы. Подтягивающие резисторы автоматически отключаются после сброса по включению питания POR, и когда каналы порта настраиваются на выход.

### Примечание. При сбросе POR каналы порта ввода/вывода PORTB настраиваются как цифровые входы.

Четыре канала PORTB RB7:RB4, настроенные на вход, могут генерировать прерывания по изменению логического уровня сигнала на входе. Если один из каналов RB7:RB4 настроен на выход, то он не может быть источником прерываний. Сигнал на выводах RB7:RB4 сравнивается со значением, сохраненным при последнем чтении PORTB. В случае несовпадения одного из значений устанавливается флаг RBIF (INTCON<0>), и если разрешено, генерируется прерывание.

Это прерывание может вывести микроконтроллер из режима SLEEP. В подпрограмме обработки прерываний необходимо сделать следующие действия:

- Выполнить чтение или запись в PORTB, исключив несоответствие

- Сбросить флаг RBIF в '0'

Несоответствие сохраненного значения с сигналом на входе PORTB всегда устанавливает бит RBIF в '1'. Чтение из PORTB прервет условие несоответствия и позволит сбросить флаг RBIF в '0'.

Прерывания по изменению сигнала на входах рекомендуется использовать для определения нажатия клавиш, когда PORTB полностью задействован для реализации клавиатуры. Не рекомендуется опрашивать PORTB при использовании прерываний по изменению входного сигнала.

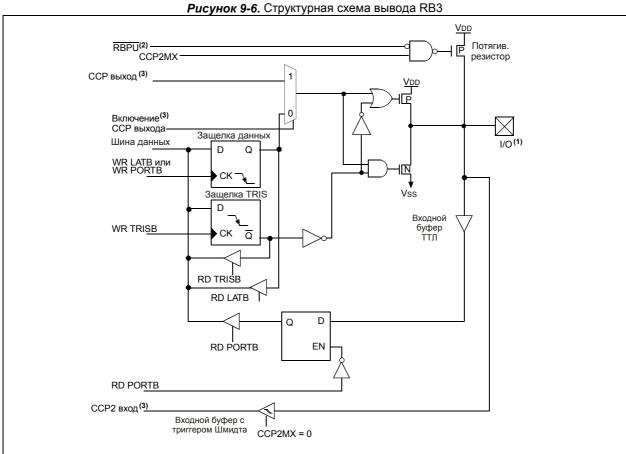

Вывод RB3 может быть настроен битом конфигурации CCP2MX как дополнительный периферийный вывод модуля CCP2 (CCP2MX=0).

### Рисунок 9-4. Структурная схема выводов RB7:RB4

### Примечания:

- 1. Выводы имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

- Для включения подтягивающих резисторов необходимо установить в '1' соответствующий бит TRISB и сбросить в '0' бит -RBPU (INTCON2<7>).

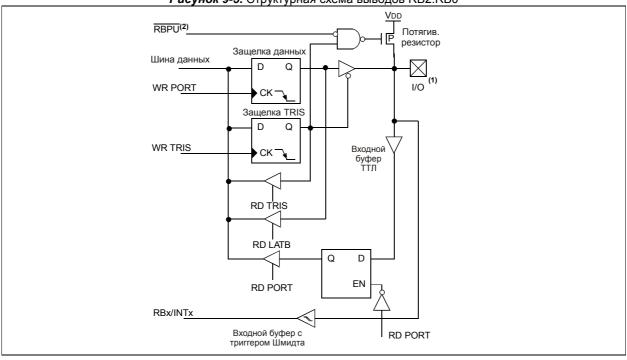

Рисунок 9-5. Структурная схема выводов RB2:RB0

### Примечания:

- 1. Выводы имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

- Для включения подтягивающих резисторов необходимо установить в '1' соответствующий бит TRISB и сбросить в '0' бит -RBPU (INTCON2<7>).

### Примечания:

- 1. Выводы имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

- Для включения подтягивающих резисторов необходимо установить в '1' соответствующий бит TRISB и сбросить в '0' бит -RBPU (INTCON2<7>).

- 3. ССР2 мультиплексирован с RB3, если ССР2МX=0 (в регистре конфигурации).

**Таблица 9-3.** Функциональное назначение выводов PORTB

| Обозначение                  | № бита | Буфер                 | Описание                                                         |

|------------------------------|--------|-----------------------|------------------------------------------------------------------|

| RB0/INT0                     | 0      | TTL/ST <sup>(1)</sup> | Вход/выход или внешнее прерывание INT0.                          |

|                              |        |                       | Внутренние подтягивающие резисторы.                              |

| RB1/INT1                     | 1      | TTL/ST <sup>(1)</sup> | Вход/выход или внешнее прерывание INT1.                          |

|                              |        |                       | Внутренние подтягивающие резисторы.                              |

| RB2/INT2                     | 2      | TTL/ST <sup>(1)</sup> | Вход/выход или внешнее прерывание INT2.                          |

|                              |        |                       | Внутренние подтягивающие резисторы.                              |

| RB3/CCP2/INT3 <sup>(3)</sup> | 3      | TTL/ST <sup>(4)</sup> | Вход/выход или внешнее прерывание INT3. Вход захвата 2, выход    |

|                              |        |                       | сравнения 2, выход ШИМ 2, если бит ССР2МХ = 0 в битах            |

|                              |        |                       | конфигурации. Внутренние подтягивающие резисторы.                |

| RB4                          | 4      | TTL                   | Вход/выход (прерывание по изменению сигнала на входе).           |

|                              |        |                       | Внутренние подтягивающие резисторы.                              |

| RB5/PGM                      | 5      | TTL/ST <sup>(2)</sup> | Вход/выход (прерывание по изменению сигнала на входе).           |

|                              |        |                       | Внутренние подтягивающие резисторы.                              |

|                              |        |                       | Включение режима низковольтного программирования ICSP.           |

| RB6/PGC                      | 6      | TTL/ST <sup>(2)</sup> | Вход/выход (прерывание по изменению сигнала на входе).           |

|                              |        |                       | Внутренние подтягивающие резисторы.                              |

|                              |        |                       | Вход тактового сигнала для внутрисхемного программирования ICSP. |

| RB7/PGD                      | 7      | TTL/ST <sup>(2)</sup> | Вход/выход (прерывание по изменению сигнала на входе).           |

|                              |        |                       | Внутренние подтягивающие резисторы.                              |

|                              |        |                       | Вывод данных для внутрисхемного программирования ICSP.           |

Обозначение: ST = вход с триггером Шмидта; TTL = входной буфер ТТЛ

### Примечания:

- 1. Входной буфер с триггером Шмидта при использовании внешних прерываний.

- 2. Входной буфер с триггером Шмидта при работе в режиме последовательного программирования.

- 3. Режим работы вывода (RB3 или ССР2) определяется битом ССР2МХ в регистре конфигурации.

- 4. Входной буфер с триггером Шмидта при использовании вывода как ССР2.

Таблица 9-4. Регистры и биты, связанные с работой PORTB

| Адрес | Имя     | Бит 7      | Бит 6                      | Бит 5   | Бит 4   | Бит 3  | Бит 2  | Бит 1  | Бит 0  | Значение<br>после<br>POR, BOR |

|-------|---------|------------|----------------------------|---------|---------|--------|--------|--------|--------|-------------------------------|

| F81h  | PORTB   | RB7        | RB6                        | RB5     | RB4     | RB3    | RB2    | RB1    | RB0    | xxxx xxxx                     |

| F8Ah  | LATB    | Регистр вы | Регистр выходных данных    |         |         |        |        |        |        | XXXX XXXX                     |

| F93h  | TRISB   | Регистр на | Регистр направления данных |         |         |        |        |        |        | 1111 1111                     |

| FF2h  | INTCON  | GIE/GIEH   | PEIE/GIEL                  | TMR0IE  | INT0IE  | RBIE   | TMR0IF | INT0IF | RBIF   | 0000 000x                     |

| FF1h  | INTCON2 | RBPU       | INTEDG0                    | INTEDG1 | INTEDG2 | -      | TMR0IP | -      | RBIP   | 1111 -1-1                     |

| FF0h  | INTCON3 | INT2IP     | INT1IP                     | -       | INT2IE  | INT1IE | -      | INT2IF | INT1IF | 11-0 0-00                     |

Обозначения: x = неизвестно; u = не изменяется; r = резерв; - = не реализован, читается как '0'. Затененные ячейки на работу не влияют.

### 9.3 Регистры PORTC, TRISC, LATC

PORTC – 8-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISC определяют направление каналов порта. Установка бита в '1' регистра TRISC переводит выходной буфер в 3-е состояние. Запись '0' в регистр TRISC настраивает соответствующий канал как выход, содержимое защелки PORTC передается на вывод микроконтроллера.

Регистр защелки LATC отображается на память данных. Операция типа «чтение – модификация – запись» с регистром LATC будет выполнена с данными, записанными в порт ввода/вывода PORTC.

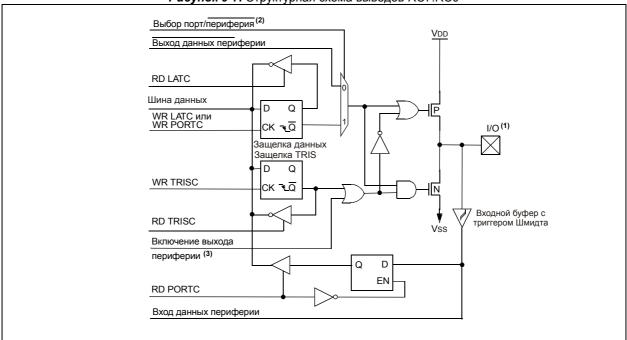

Выводы PORTC мультиплексированы с несколькими периферийными модулями (см. таблицу 9-5). На каналах PORTC присутствует входной буфер с триггером Шмидта.

При использовании периферийных модулей необходимо соответствующим образом настраивать биты регистра TRISC для каждого вывода PORTC. Некоторые периферийные модули отменяют действие битов TRISC, принудительно настраивая вывод на вход или выход. Требования к настройке битов TRISC смотрите в описании на соответствующий периферийный модуль.

### *Примечание*. При сбросе POR каналы порта ввода/вывода PORTC настраиваются как цифровые входы.

Реальное направление данных канала порта ввода/вывода не загружается в регистр TRISC, что позволяет использовать команды «чтение – модификация – запись» при обращении к регистру TRISC без ограничений.

Режим работы вывода RC1 управляется битом CCP2MX в регистрах конфигурации. По умолчанию вывод RC1 мультиплексирован с выводом периферийного модуля CCP2 (CCP2MX=1).

Пример 9-3. Инициализация PORTC

| p 3-3, vini | лциализация т | OKIO                         |

|-------------|---------------|------------------------------|

| CLRF        | PORTC         | ; Инициализация PORTC        |

|             |               | ; с очисткой выходной        |

|             |               | ; защелки данных             |

| CLRF        | LATC          | ; Альтернативный метод       |

|             |               | ; очистки выходной           |

|             |               | ; защелки данных             |

| MOVLW       | 0xCF          | ; Значение                   |

|             |               | ; инициализации              |

|             |               | ; направления данных         |

| MOVWF       | TRISC         | ; Установить RC<3:0> входами |

|             |               | ; RC<5:4> выходами           |

|             |               | ; RC<7:6> входами            |

Рисунок 9-7. Структурная схема выводов RC7:RC0

### Примечания:

- 1. Выводы имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

- 2. Режима канала вывод используется периферийным модулем или цифровой порт ввода/вывода.

- 3. Сигнал разрешения (ОЕ) от периферийного модуля, настраивать канал как выход.

**Таблица 9-5.** Функциональное назначение выводов PORTC

| Обозначение     | № бита | Буфер | Описание                                                |

|-----------------|--------|-------|---------------------------------------------------------|

| RC0/T1OSO/T1CKI | 0      | ST    | Цифровой канал порта ввода/вывода.                      |

|                 |        |       | Выход для подключения кварцевого резонатора TMR1.       |

|                 |        |       | Вход тактового сигнала для TMR1/TMR3.                   |

| RC1/T1OSI/CCP2  | 1      | ST    | Цифровой канал порта ввода/вывода.                      |

|                 |        |       | Вход для подключения кварцевого резонатора TMR1.        |

|                 |        |       | Вход захвата 2, выход сравнения 2, выход ШИМ.           |

| RC2/CCP1        | 2      | ST    | Цифровой канал порта ввода/вывода.                      |

|                 |        |       | Вход захвата 1, выход сравнения 1, выход ШИМ 1.         |

| RC3/SCK/SCL     | 3      | ST    | Цифровой канал порта ввода/вывода.                      |

|                 |        |       | Вход/выход тактового сигнала в режиме SPI.              |

|                 |        |       | Вход/выход тактового сигнала в режиме I <sup>2</sup> C. |

| RC4/SDI/SDA     | 4      | ST    | Цифровой канал порта ввода/вывода.                      |

|                 |        |       | Вход данных в режиме SPI.                               |

|                 |        |       | Вход/выход данных в режиме I <sup>2</sup> C.            |

| RC5/SDO         | 5      | ST    | Цифровой канал порта ввода/вывода.                      |

|                 |        |       | Выход данных в режиме SPI.                              |

| RC6/TX/CK       | 6      | ST    | Цифровой канал порта ввода/вывода.                      |

|                 |        |       | Выход передатчика USART в асинхронном режиме.           |

|                 |        |       | Вывод синхронизации в синхронном режиме USART.          |

| RC7/RX/DT       | 7      | ST    | Цифровой канал порта ввода/вывода.                      |

|                 |        |       | Вход приемника USART в асинхронном режиме.              |

|                 |        |       | Вывод данных USART в синхронном режиме.                 |

Обозначение: ST = вход с триггером Шмидта

Таблица 9-6. Регистры и биты, связанные с работой PORTC

| Адрес | Имя   | Бит 7      | Бит 6                      | Бит 5 | Бит 4 | Бит 3 | Бит 2 | Бит 1 | Бит 0     | Значение<br>после<br>POR, BOR |

|-------|-------|------------|----------------------------|-------|-------|-------|-------|-------|-----------|-------------------------------|

| F82h  | PORTC | RC7        | RC6                        | RC5   | RC4   | RC3   | RC2   | RC1   | RC0       | xxxx xxxx                     |

| F8Bh  | LATC  | Регистр вы | Регистр выходных данных    |       |       |       |       |       | xxxx xxxx |                               |

| F94h  | TRISC | Регистр на | Регистр направления данных |       |       |       |       |       |           | 1111 1111                     |

Обозначения: x = неизвестно; u = не изменяется; r = резерв; - = не реализован, читается как '0'. Затененные ячейки на работу не влияют.

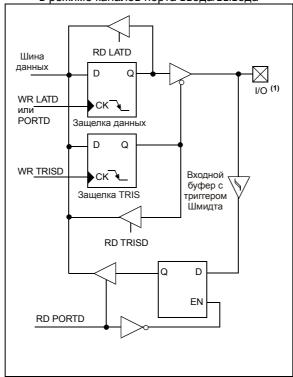

### 9.4 Регистры PORTD, TRISD, LATD

Этот раздел предназначен только для микроконтроллеров PIC18F4X2.

PORTD – 8-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISD определяют направление каналов порта. Установка бита в '1' регистра TRISD переводит выходной буфер в 3-е состояние. Запись '0' в регистр TRISD настраивает соответствующий канал как выход, содержимое защелки PORTD передается на вывод микроконтроллера.

Регистр защелки LATD отображается на память данных. Операция типа «чтение – модификация – запись» с регистром LATD будет выполнена с данными, записанными в порт ввода/вывода PORTD.

На каналах PORTD присутствует входной буфер с триггером Шмидта. Каждый канал PORTD индивидуально настраивается на вход или выход.

### *Примечание.* При сбросе POR каналы порта ввода/вывода PORTD настраиваются как цифровые входы.

PORTD может работать как 8-разрядный микропроцессорный порт (ведомый параллельный порт), если бит PSPMODE (TRISE<4>) установлен в '1'. В режиме ведомого параллельного порта к входам подключены буферы ТТЛ. Подробное описание работы с ведомым параллельным портом смотрите в разделе 9.6.

*Пример 9-4.* Инициализация PORTD

| CLRF  | PORTD | ; Инициализация PORTD        |

|-------|-------|------------------------------|

|       |       | ; с очисткой выходной        |

|       |       | ; защелки данных             |

| CLRF  | LATD  | ; Альтернативный метод       |

|       |       | ; очистки выходной           |

|       |       | ; защелки данных             |

| MOVLW | 0xCF  | ; Значение                   |

|       |       | ; инициализации              |

|       |       | ; направления данных         |

| MOVWF | TRISD | ; Установить RD<3:0> входами |

|       |       | ; RD<5:4> выходами           |

|       |       | ; RD<7:6> входами            |

**Рисунок 9-8.** Структурная схема выводов RD7:RD0 в режиме каналов порта ввода/вывода

**Примечание 1.** Выводы имеют защитные диоды, подключенные к V<sub>DD</sub> и V<sub>SS</sub>.

**Таблица 9-7.** Функциональное назначение выводов PORTD

| Обозначение | № бита | Буфер                 | Описание                                        |  |  |  |  |

|-------------|--------|-----------------------|-------------------------------------------------|--|--|--|--|

| RD0/PSP0    | 0      | ST/TTL <sup>(1)</sup> | Вход/выход или параллельный ведомый порт бит 0. |  |  |  |  |

| RD1/PSP1    | 1      | ST/TTL <sup>(1)</sup> | Вход/выход или параллельный ведомый порт бит 1. |  |  |  |  |

| RD2/PSP2    | 2      | ST/TTL <sup>(1)</sup> | Вход/выход или параллельный ведомый порт бит 2. |  |  |  |  |

| RD3/PSP3    | 3      | ST/TTL <sup>(1)</sup> | Вход/выход или параллельный ведомый порт бит 3. |  |  |  |  |

| RD4/PSP4    | 4      | ST/TTL <sup>(1)</sup> | Вход/выход или параллельный ведомый порт бит 4. |  |  |  |  |

| RD5/PSP5    | 5      | ST/TTL <sup>(1)</sup> | Вход/выход или параллельный ведомый порт бит 5. |  |  |  |  |

| RD6/PSP6    | 6      | ST/TTL <sup>(1)</sup> | Вход/выход или параллельный ведомый порт бит 6. |  |  |  |  |

| RD7/PSP7    | 7      | ST/TTL <sup>(1)</sup> | Вход/выход или параллельный ведомый порт бит 7. |  |  |  |  |

Обозначение: ST = вход с триггером Шмидта; TTL = входной буфер ТТЛ

**Примечание 1.** Входной буфер с триггером Шмидта в режиме каналов порта ввода/вывода, входной буфер ТТЛ в режиме ведомого параллельного порта.

Таблица 9-8. Регистры и биты, связанные с работой PORTD

| Адрес                             | Имя   | Бит 7      | Бит 6                      | Бит 5   | Бит 4 | Бит 3 | Бит 2      | Бит 1        | Бит 0 | Значение<br>после<br>POR, BOR |  |

|-----------------------------------|-------|------------|----------------------------|---------|-------|-------|------------|--------------|-------|-------------------------------|--|

| F83h                              | PORD  | RD7        | RD6                        | RD5     | RD4   | RD3   | RD2        | RD1          | RD0   | xxxx xxxx                     |  |

| F8Dh LATD Регистр выходных данных |       |            |                            |         |       |       |            |              |       |                               |  |

| F95h                              | TRISD | Регистр на | Регистр направления данных |         |       |       |            |              |       |                               |  |

| F96h                              | TRISE | IBF        | OBF                        | PSPMODE | -     | -     | Регистр на | правления да | анных | 0000 -111                     |  |

Обозначения: x = неизвестно; u = не изменяется; r = резерв; - = не реализован, читается как '0'. Затененные ячейки на работу не влияют.

### 9.5 Perucmpы PORTE, TRISE, LATE

Этот раздел предназначен только для микроконтроллеров PIC18F4X2.

PORTE – 3-разрядный двунаправленный порт ввода/вывода. Биты регистра TRISE определяют направление каналов порта. Установка бита в '1' регистра TRISE переводит выходной буфер в 3-е состояние. Запись '0' в регистр TRISE настраивает соответствующий канал как выход, содержимое защелки PORTE передается на вывод микроконтроллера.

Регистр защелки LATE отображается на память данных. Операция типа «чтение – модификация – запись» с регистром LATE будет выполнена с данными, записанными в порт ввода/вывода PORTE.

PORTE имеет три вывода (RE0/-RD/AN5, RE1/-WR/AN6, RE2/-CS/AN7), индивидуально настраиваемые на вход или выход. Выводы PORTE имеют входной буфер Шмидта.

В регистре TRISE размещаются биты управления ведомым параллельным портом.

Выводы PORTE мультиплексированы с аналоговыми входами. Когда каналы PORTE настроены как аналоговые входы, чтение PORTE чтение будет давать результат '0'.

Биты регистра TRISE управляют направлением каналов PORTE, даже когда они используются как аналоговые входы. Пользователь должен удостовериться, что соответствующие каналы PORTE настроены на вход при использовании их в качестве аналоговых входов.

### *Примечание.* После сброса по включению питания выводы PORTE настраиваются как аналоговые входы.

### Пример 9-5. Инициализация PORTE

| :p 3-3. VIIII | ициализация т | OITIL                     |

|---------------|---------------|---------------------------|

| CLRF          | PORTE         | ; Инициализация PORTE     |

|               |               | ; с очисткой выходной     |

|               |               | ; защелки данных          |

| CLRF          | LATE          | ; Альтернативный метод    |

|               |               | ; очистки выходной        |

|               |               | ; защелки данных          |

| MOVLW         | $0 \times 07$ | ; Настройка АЦП           |

| MOVWF         | ADCON1        | ; как цифровых входов     |

| MOVLW         | 0x05          | ; Значение                |

|               |               | ; инициализации           |

|               |               | ; направления данных      |

| MOVWF         | TRISE         | ; Установить RE<0> входом |

|               |               | ; RA<1> выходом           |

|               |               | ; RE<2> входом            |

**Рисунок 9-9.** Структурная схема выводов RE2:RE0 в режиме каналов порта ввода/вывода

Примечание 1. Выводы имеют защитные диоды, подключенные к V<sub>DD</sub> и V<sub>SS</sub>.

**Таблица 9-9.** Функциональное назначение выводов PORTE

| Обозначение | № бита | Буфер                 | Описание                                                                        |

|-------------|--------|-----------------------|---------------------------------------------------------------------------------|

| RE0/-RD/AN5 | 0      | ST/TTL <sup>(1)</sup> | Вход/выход, вход управления чтением ведомого параллельного порта или аналоговый |

|             |        |                       | вход:                                                                           |

|             |        |                       | -RD                                                                             |

|             |        |                       | 1 = Ожидание                                                                    |

|             |        |                       | 0 = Операция чтения. Защелка PORTD подключена к выводам PORTD (если -CS = 0)    |

| RE1/-WR/AN6 | 1      | ST/TTL <sup>(1)</sup> | Вход/выход, вход управления записью ведомого параллельного порта или аналоговый |

|             |        |                       | вход:                                                                           |

|             |        |                       | -WR                                                                             |

|             |        |                       | 1 = Ожидание                                                                    |

|             |        |                       | 0 = Операция записи. Данные с выводов PORTD сохраняются во внутренней защелке   |

|             |        |                       | PORTD (если -CS = 0)                                                            |

| RE2/-CS/AN7 | 2      | ST/TTL <sup>(1)</sup> | Вход/выход, вход выбора микросхемы ведомого параллельного порта или аналоговый  |

|             |        |                       | вход:                                                                           |

|             |        |                       | -CS                                                                             |

|             |        |                       | 1 = Микросхема не выбрана                                                       |

| I           |        |                       | 0 = Микросхема выбрана                                                          |

Обозначение: ST = вход с триггером Шмидта; TTL = входной буфер ТТЛ

Примечание 1. Входной буфер с триггером Шмидта в режиме каналов порта ввода/вывода, входной буфер ТТЛ в режиме ведомого параллельного порта.

Таблица 9-10. Регистры и биты, связанные с работой PORTE

| Адрес | Имя    | Бит 7 | Бит 6 | Бит 5   | Бит 4 | Бит 3 | Бит 2                      | Бит 1 | Бит 0 | Значение<br>после<br>POR, BOR |

|-------|--------|-------|-------|---------|-------|-------|----------------------------|-------|-------|-------------------------------|

| F84h  | PORE   | -     | -     | -       | -     | -     | RE2                        | RE1   | RE0   | 000                           |

| F8Dh  | LATE   | -     | -     | -       | -     | -     | Регистр выходных данных    |       |       | xxx                           |

| F96h  | TRISE  | IBF   | OBF   | PSPMODE | -     | -     | Регистр направления данных |       |       | 0000 -111                     |

| FC1h  | ADCON1 | ADFM  | ADCS2 | -       | -     | PCFG3 | PCFG2                      | PCFG1 | PCFG0 | 00 0000                       |

Обозначения: х = неизвестно; и = не изменяется; г = резерв; - = не реализован, читается как '0'. Затененные ячейки на работу не влияют.

### **Регистр 9-1.** Peгистр TRISE

| R - 0 | R - 0 | R/W - 0 | R/W - 0 | U - 0 | R/W - 1 | R/W - 1 | R/W - 1 |

|-------|-------|---------|---------|-------|---------|---------|---------|

| IBF   | OBF   | IBOV    | PSPMODE | -     | TRISE2  | TRISE1  | TRISE0  |

| Бит 7 |       |         |         |       |         |         | Бит 0   |

Бит 7 **IBF**: Бит статуса приемного буфера ведомого параллельного порта

1 = принят байт данных

0 = байт данных не был получен

Бит 6 **ОВF**: Бит статуса передающего буфера ведомого параллельного порта

1 = предварительно записанный байт данных еще не прочитан

0 = выходной буфер был прочитан

Бит 5 **IBOV**: Флаг переполнения приемного буфера ведомого параллельного порта

1 = произошла новая запись, а предыдущий байт не был прочитан (сбрасывается программно)

0 = переполнения не было

Бит 4 **PSPMODE**: Выбор режима ведомого параллельного порта

1 = режим ведомого параллельного порта

0 = выводы работают как каналы портов ввода/вывода

Бит 3 Не используется: Читается как '0'

Бит 2 **TRISE2**: Направление вывода RE2

1 = вход

0 = выход

Бит 1 TRISE1: Направление вывода RE1

1 = вход

0 = выход

Бит 0 **TRISE0**: Направление вывода RE0

1 = вход

0 = выход

Обозначения

R = чтение бита W = запись бита U = не используется, читается как '0'

- n = значение после POR '1' = бит установлен '0' = бит сброшен X = неизвестное сост.

### 9.6 Ведомый параллельный порт PSP

Этот раздел предназначен только для микроконтроллеров PIC18F4X2.

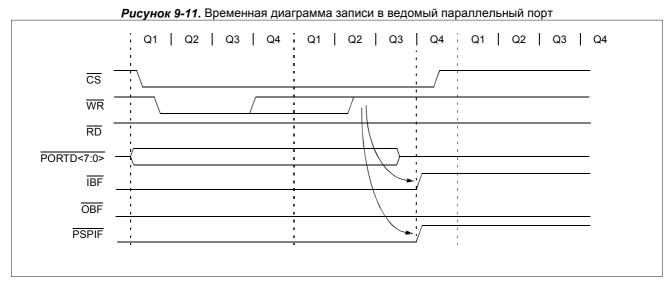

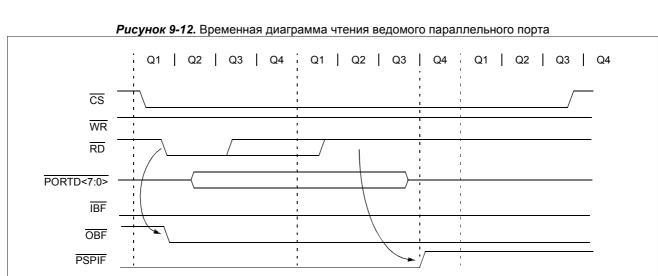

PORTD может работать как 8-разрядный параллельный порт (или порт микропроцессора), когда бит PSPMODE(TRISE<4>) установлен в '1'. В режиме ведомого параллельного порта данные асинхронно читаются или записываются внешними сигналами -RD (RE0/-RD) или -WR(RE1/-WR) соответственно.

Внешний микропроцессор может читать/записывать данные в PORTD. Операции чтения/записи выполняются при низком логическом уровне сигналов на входах -RD, -WR и низком логическом уровне сигнала на входе выбора микросхемы -CS. Биты TRISE (TRISE<2:0>) должны быть установлены в '1' (выводы настроены на вход). В регистре ADCON1<3:0> выводы RE2:RE0 должны быть настроены как цифровые каналы ввода/вывода (биты PCFG3:PCFG0).

Фактически существуют два 8-разрядных регистра: один регистр для приема данных, другой - для передачи. Пользователь записывает 8-разрядные данные в выходную защелку PORTD, а читает данные со входной защелки (обратите внимание, выходная и входная защелка имеют один и тот же адрес). В этом режиме значение битов регистра TRISE игнорируется, т.к. направлением данных управляет внешнее устройство.

Запись в PSP происходит, если выводы -CS и -WR имеют низкий уровень сигнала. Чтение из PSP происходит, если выводы -CS и -RD имеют низкий уровень сигнала.

Для работы выводов PORTE в качестве управляющих входов ведомого параллельного порта нужно установить в '1' бит PSPMODE(TRISE<4>). В этом режиме выводы должны работать как цифровые каналы ввода/вывода (регистр ADCON1) настроенные на вход (биты TRISE<2:0> должны быть установлены в '1'). Выводы ведомого параллельного порта имеют входные буферы ТТЛ.

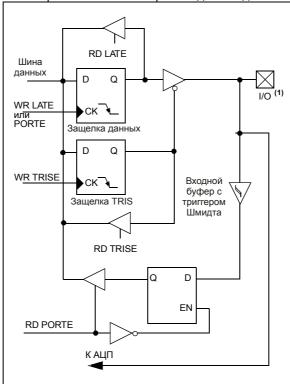

в режиме ведомого параллельного порта Шина данных RDx WR LATD PORTD I Зашелка данных ТТЛ I ı ı RD PORTD ΕN ı Защелка TRIS I I RD LATD ı ı Один бит PORTD Установка флага PSPIF (PIR1<7>)

**Рисунок 9-10.** Структурная схема выводов PORTD, PORTE

*Примечание 1.* Выводы имеют защитные диоды, подключенные к  $V_{DD}$  и  $V_{SS}$ .

| Адрес | Имя    | Бит 7                   | Бит 6        | Бит 5   | Бит 4  | Бит 3 | Бит 2       | Бит 1  | Бит 0     | Значение<br>после<br>POR, BOR |

|-------|--------|-------------------------|--------------|---------|--------|-------|-------------|--------|-----------|-------------------------------|

| F83h  | PORD   | RD7                     | RD6          | RD5     | RD4    | RD3   | RD2         | RD1    | RD0       | xxxx xxxx                     |

| F8Dh  | LATD   | Регистр выходных данных |              |         |        |       |             |        |           | xxxx xxxx                     |

| F95h  | TRISD  | Регистр на              | правления да | анных   |        |       |             |        | 1111 1111 |                               |

| F84h  | PORE   | -                       | -            | -       | -      | -     | RE2         | RE1    | RE0       | 000                           |

| F8Dh  | LATE   | -                       | -            | -       | -      | -     | Регистр вы  | xxx    |           |                               |

| F96h  | TRISE  | IBF                     | OBF          | PSPMODE | -      | -     | Регистр наг | анных  | 0000 -111 |                               |

| FF2h  | INTCON | GIE/GIEH                | PEIE/GIEL    | TMR0IE  | INT0IE | RBIE  | TMR0IF      | INT0IF | RBIF      | 0000 000x                     |

| F9Fh  | IRP1   | PSPIP                   | ADIP         | RCIP    | TXIP   | SSPIP | CCP1IP      | TMR2IP | TMR1IP    | 1111 1111                     |

| F9Eh  | PIR1   | PSPIF                   | ADIF         | RCIF    | TXIF   | SSPIF | CCP1IF      | TMR2IF | TMR1IF    | 0000 0000                     |

| F98h  | PIE1   | PSPIE                   | ADIE         | RCIE    | TXIE   | SSPIE | CCP1IE      | TMR2IE | TMR1IE    | 0000 0000                     |

| FC1h  | ADCON1 | ADFM                    | ADCS2        | -       | -      | PCFG3 | PCFG2       | PCFG1  | PCFG0     | 00 0000                       |

Обозначения: х = неизвестно; и = не изменяется; г = резерв; - = не реализован, читается как '0'. Затененные ячейки на работу не влияют.

## Уважаемые господа!

OOO «Микро-Чип» поставляет полную номенклатуру комплектующих фирмы Microchip Technology Inc

и осуществляет качественную техническую поддержку на русском языке.

С техническими вопросами Вы можете обращаться по адресу <a href="mailto:support@microchip.ru">support@microchip.ru</a>

По вопросам поставок комплектующих Вы можете обращаться к нам по телефонам:

(095) 963-9601 (095) 737-7545

и адресу sales@microchip.ru

Ha сайте www.microchip.ru

Вы можете узнать последние новости нашей фирмы, найти техническую документацию и информацию по наличию комплектующих на складе.