### PCF8570/8570C/8571

#### GENERAL DESCRIPTION

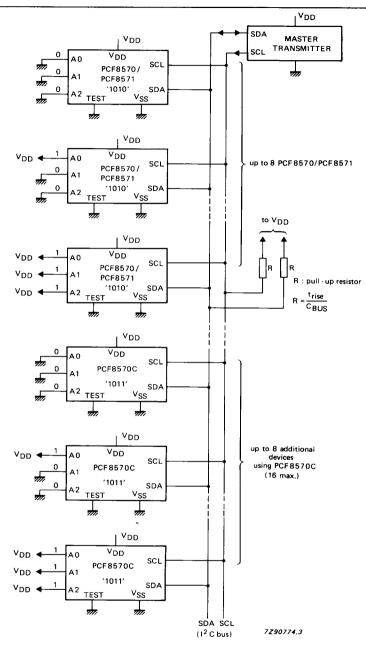

The PCF8570, PCF8570C and PCF8571 are low-power static CMOS RAMs. The PCF8570 and PCF8570C are organized as 256 words by 8-bits and the PCF8571 is organized as 128 words by 8-bits. Addresses and data are transferred serially via a two-line bidirectional bus (i<sup>2</sup>C). The built-in word address register is incremented automatically after each written or read data byte. Three address pins A0, A1 and A2 are used for hardware address, allowing the use of up to eight devices connected to the bus without additional hardware. For system expansion over 8 devices the PCF8570/71 can be used in conjunction with the PCF8750C which has an alternative slave address for memory extension up to 16 devices.

### **Features**

Operating supply voltage 2.5 V to 6 V Low data retention voltage min. 1.0 V Low standby current max.  $15 \mu A$  Power saving mode tvp. 50 nA

Serial input/output bus (I<sup>2</sup>C)

Address by 3 hardware address pins Automatic word address incrementing

8-lead DIL package

## **Applications**

Telephony

Radio and television Video cassette recorder

General purpose

RAM expansion for stored numbers in repertory dialling (e.g. PCD3343 applications)

channel presets

channel presets RAM expansion for the microcontroller families MAB8400.

PCF84CXX and most other microcontrollers

### PACKAGE OUTLINES

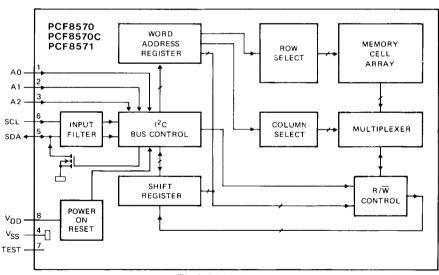

Fig.1 Block diagram.

7290775.3

PCF8570/PCF8570C/PCF8571/P: 8-lead DIL; plastic (SOT97). PCF8570/PCF8570C/PCF8571/T: 8-lead mini-pack (SO8L; SOT176C).

March 1989

116

PCF8570/8570C/8571

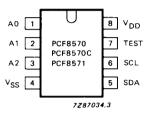

### **PINNING**

| 1 to 3 | A0 to A2 | address inputs                                                         |

|--------|----------|------------------------------------------------------------------------|

| 4      | $V_{SS}$ | negative supply                                                        |

| 5      | SDA      | serial data line   12 C-bus<br>serial clock line                       |

| 6      | SCL      |                                                                        |

| 7      | TEST     | test input for test speed-up; must be connected to VSS when not in use |

|        |          | (power saving mode, see Figs 12 and 13)                                |

| 8      | $V_{DD}$ | positive supply                                                        |

Fig.2 Pinning diagram.

### **RATINGS**

Limiting values in accordance with the Absolute Maximum System (IEC 134)

| parameter                           | symbol                                | min. | max.                  | unit |

|-------------------------------------|---------------------------------------|------|-----------------------|------|

| Supply voltage range                | $V_{DD}$                              | -0.8 | + 8.0                 | V    |

| Input voltage range                 | VI                                    | -0.8 | V <sub>DD</sub> + 0.8 | V    |

| DC input current                    | ± I <sub>I</sub>                      | _    | 10                    | mA   |

| DC output current                   | ± IO                                  | _    | 10                    | mA   |

| VDD or VSS current                  | ± I <sub>DD</sub> ; ± I <sub>SS</sub> | _    | 50                    | mA   |

| Total power dissipation             | P <sub>tot</sub>                      | _    | 300                   | mW   |

| Power dissipation per output        | PO                                    | _    | 50                    | mW   |

| Operating ambient temperature range | Tamb                                  | 40   | + 85                  | oC   |

| Storage temperature range           | T <sub>stg</sub>                      | -65  | + 150                 | oC   |

### **HANDLING**

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is good practice to take normal precautions appropriate to handling MOS devices (see 'Handling MOS Devices').

Purchase of Philips' 1<sup>2</sup>C components conveys a license under the Philips' 1<sup>2</sup>C patent to use the components in the 1<sup>2</sup>C-system provided the system conforms to the 1<sup>2</sup>C specifications defined by Philips.

March 1989 117

PCF8570/8570C/8571

#### CHARACTERISTICS

$V_{DD}$  = 2.5 to 6 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 to +85 °C unless otherwise specified

| parameter                          | conditions                                                                        | symbol           | min.                | typ.     | max,                 | unit     |

|------------------------------------|-----------------------------------------------------------------------------------|------------------|---------------------|----------|----------------------|----------|

| Supply                             |                                                                                   |                  |                     |          |                      |          |

| Supply voltage                     |                                                                                   | $V_{DD}$         | 2.5                 | _        | 6.0                  | V        |

| Supply current operating           | V <sub>I</sub> = V <sub>DD</sub> or V <sub>SS</sub><br>f <sub>SCL</sub> = 100 kHz | IDD              | _                   | _        | 200                  | μΑ       |

| standby                            | f <sub>SCL</sub> = 0 Hz<br>T <sub>amb</sub> = -25 to + 70 °C                      | IDDO<br>IDDO     | _                   | _        | 15<br>5              | μA<br>μA |

| Power-on reset level               | note 1                                                                            | VPOR             | 1.5                 | 1.9      | 2.3                  | ٧        |

| Inputs, input/output SDA           |                                                                                   |                  | !                   |          |                      |          |

| Input voltage LOW                  | note 2                                                                            | VIL              | -0.8                | _        | 0.3 V <sub>DD</sub>  | V        |

| Input voltage HIGH                 | note 2                                                                            | VIH              | 0.7 V <sub>DD</sub> | _        | V <sub>DD</sub> +0.8 | V        |

| Output current LOW                 | V <sub>OL</sub> = 0.4 V                                                           | IOL              | 3                   | _        | _                    | mΑ       |

| Leakage current                    | V <sub>I</sub> = V <sub>DD</sub> or V <sub>SS</sub>                               | _                |                     | -        | 1                    | μΑ       |

| Inputs A0 to A2; TEST              |                                                                                   |                  |                     | i        |                      |          |

| Input leakage current              | $V_I = V_{DD}$ or $V_{SS}$                                                        | ±   L            | _                   | -        | 250                  | nΑ       |

| Inputs SCL; SDA                    |                                                                                   |                  |                     |          |                      |          |

| Input capacitance                  | V <sub>I</sub> = V <sub>SS</sub>                                                  | Cl               | -                   | -        | 7                    | pΕ       |

| LOW V <sub>DD</sub> data retention |                                                                                   |                  | :<br>:<br>:         |          | <br>                 |          |

| Supply voltage for data retention  |                                                                                   | V <sub>DDR</sub> | 1                   | <u> </u> | 6                    | v        |

| Supply current                     | V <sub>DDR</sub> = 1 V                                                            | IDDR             | _                   | _        | 5                    | μΑ       |

| Supply current                     | V <sub>DDR</sub> = 1 V;                                                           |                  |                     |          |                      | •        |

|                                    | $T_{amb} = -25 \text{ to} + 70 \text{ °C}$                                        | IDDR             | -                   | -        | 2                    | μΑ       |

| Power saving mode                  | see Figs 12 and 13                                                                |                  |                     |          |                      |          |

| Supply current                     | TEST = V <sub>DD</sub> ;<br>T <sub>amb</sub> = 25 °C                              |                  | ·<br>!<br>!         |          |                      |          |

| PCF8570/PCF8570C<br>PCF8571        |                                                                                   | I <sub>DDR</sub> | _                   | 50<br>50 | 400<br>200           | nA<br>nA |

| Recovery time                      |                                                                                   | tHD2             | _                   | 50       | _                    | μs       |

#### Notes to the characteristics

- The power-on reset circuit resets the I<sup>2</sup>C-bus logic when V<sub>DD</sub> < V<sub>POR</sub>. The status of the device

after a power-on reset condition can be tested by sending the slave address and testing the

acknowledge bit.

- 2. If the input voltages are a diode voltage above or below the supply voltage V<sub>DD</sub> or V<sub>SS</sub> an input current will flow: this current must not exceed ± 0.5 mA.

PCF8570/8570C/8571

### CHARACTERISTICS OF THE 12C-BUS

The I<sup>2</sup>C-bus is for 2-way, 2-line communication between different ICs or modules. The two lines are a serial data line (SDA) and a serial clock line (SCL). Both lines must be connected to a positive supply via a pull-up resistor when connected to the output stages of a device. Data transfer may be initiated only when the bus is not busy.

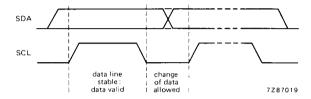

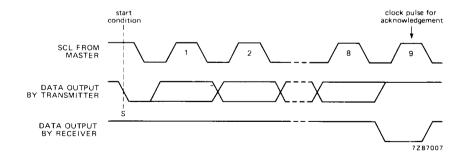

#### Bit transfer

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse as changes in the data line at this time will be interpreted as control signals.

Fig.3 Bit transfer.

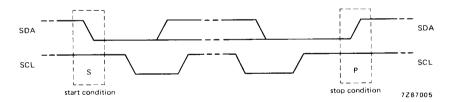

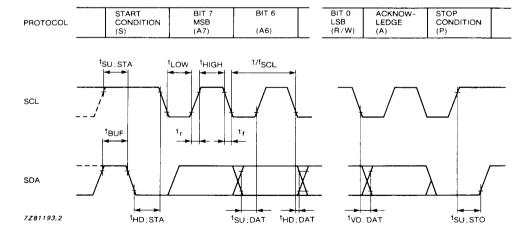

### Start and stop conditions

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the start condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the stop condition (P).

Fig.4 Definition of start and stop conditions.

March 1989 119

PCF8570/8570C/8571

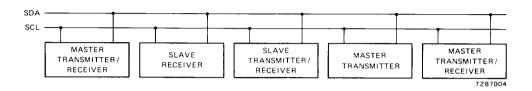

### System configuration

A device generating a message is a "transmitter", a device receiving a message is the "receiver". The device that controls the message is the "master" and the devices which are controlled by the master are the "slaves".

Fig.5 System configuration.

### Acknowledge

The number of data bytes transferred between the start and stop conditions from transmitter to receiver is not limited. Each byte of eight bits is followed by one acknowledge bit. The acknowledge bit is a HIGH level put on the bus by the transmitter whereas the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an acknowledge after the reception of each byte. Also a master must generate an acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges has to pull down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the acknowledge related clock pulse, set-up and hold times must be taken into account. A master receiver must signal an end of data to the transmitter by *not* generating an acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a stop condition.

Fig.6 Acknowledgement on the I<sup>2</sup>C-bus.

## **Timing specifications**

All the timing values are valid within the operating supply voltage and ambient temperature range and refer to  $V_{1L}$  and  $V_{1H}$  with an input voltage swing of  $V_{SS}$  to  $V_{DD}$ .

| parameter                    | symbol         | min. | typ. | max. | unit |

|------------------------------|----------------|------|------|------|------|

| SCL clock frequency          | fSCL           | _    | _    | 100  | kHz  |

| Tolerable spike width on bus | †SW            | -    | _    | 100  | ns   |

| Bus free time                | tBUF           | 4.7  | _    | _    | μs   |

| Start condition set-up time  | tSU; STA       | 4.7  | -    | -    | μs   |

| Start condition hold time    | tHD; STA       | 4.0  | _    | -    | μs   |

| SCL LOW time                 | tLOW           | 4.7  | _    | _    | μs   |

| SCL HIGH time                | tHIGH          | 4.0  | _    | -    | μs   |

| SCL and SDA rise time        | t <sub>r</sub> | _    | _    | 1.0  | μs   |

| SCL and SDA fall time        | tf             | _    | _    | 0.3  | μs   |

| Data set-up time             | tSU; DAT       | 250  | -    | _    | ns   |

| Data hold time               | tHD; DAT       | 0    | -    | -    | ns   |

| SCL LOW to data out valid    | tVD; DAT       | _    | _    | 3.4  | μs   |

| Stop condition set-up time   | tsu; sto       | 4.0  | _    | _    | μs   |

Fig.7 12 C-bus timing diagram.

PCF8570/8570C/8571

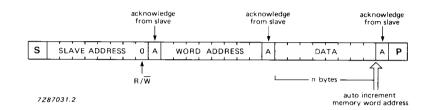

### **Bus protocol**

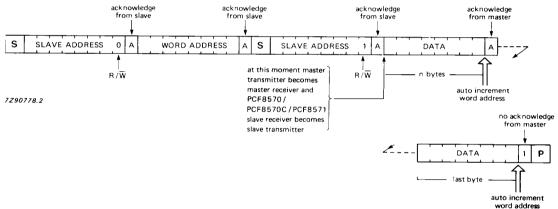

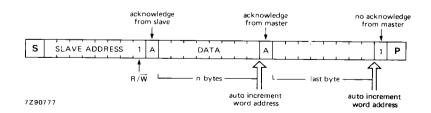

Before any data is transmitted on the I<sup>2</sup>C-bus, the device which should respond is addressed first. The addressing is always done with the first byte transmitted after the start procedure. The I<sup>2</sup>C-bus configuration for different PCF8570/PCF8570C/PCF8571 READ and WRITE cycles is shown in Fig.8.

Fig.8(a) Master transmits to slave receiver (WRITE mode).

Fig.8(b) Master reads after setting word address (WRITE word address; READ data).

Fig.8(c) Master reads slave immediately after first byte (READ mode).

PCF8570/8570C/8571

### **APPLICATION INFORMATION**

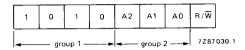

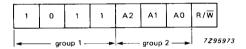

The PCF8570/PCF8571 slave address has a fixed combination 1010 as group 1, while group 2 is fully programmable (see Fig.9). The PCF8570C has slave address 1011 as group 1, while group 2 is fully programmable (see Fig.10).

Fig.9 PCF8570 and PCF8571 address.

Fig.10 PCF8570C address.

### Note

A0, A1, and A2 inputs must be connected to VDD or VSS but not left open-circuit.

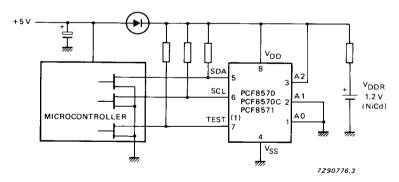

# PCF8570/8570C/8571

It is recommended that a 4.7  $\mu$ F/10 V solid aluminium capacitor (SAL) be connected between V<sub>DD</sub> and V<sub>SS</sub>.

Fig.11 Application diagram.

PCF8570/8570C/8571

### **POWER SAVING MODE**

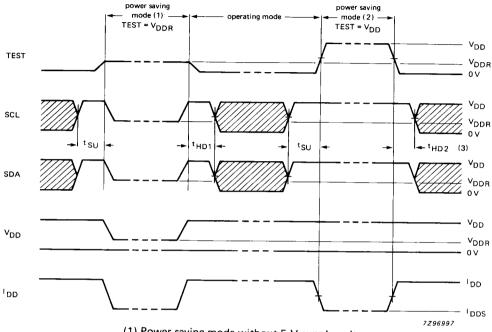

With the condition TEST = V<sub>DD</sub> or V<sub>DDR</sub> the PCF8570/PCF8570 goes into the power saving mode and I2 C-bus logic is reset.

- (1) Power saving mode without 5 V supply voltage.

- (2) Power saving mode with 5 V supply voltage.

- (3)  $t_{SU}$  and  $t_{HD1} \geqslant$  4  $\mu s$  and  $t_{HD2} \geqslant$  50  $\mu s$ .

Fig. 12 Timing for power saving mode.

(1) In the operating mode TEST = 0; In the power saving mode TEST =  $V_{DDR}$ .

It is recommended that a 4.7  $\mu$ F/10 V solid aluminium capacitor (SAL) be connected between V<sub>DD</sub> and VSS.

Fig.13 Application example for power saving mode.