# Low voltage 16-bit microcontroller

P90CL301

| CONTEN       | ITS                                                                                | 13           | PULSE WIDTH MODULATION OUTPUTS (PWM) |

|--------------|------------------------------------------------------------------------------------|--------------|--------------------------------------|

| 1            | FEATURES                                                                           | 13.1         | Prescaler PWM Register (PWMP)        |

| 2            | DESCRIPTION                                                                        | 13.2         | PWM Data Registers (PWM0 and PWM1)   |

| 2.1          | Note on supply voltage                                                             | 14           | ANALOG-TO-DIGITAL CONVERTER (ADC)    |

| 3            | ORDERING INFORMATION                                                               | 14.1         | ADC Control Register (ADCON)         |

| 4            | BLOCK DIAGRAM                                                                      | 15           | ON-BOARD TEST CONCEPT                |

| 5            | PINNING INFORMATION                                                                | 15.1         | ONCE mode                            |

| 5.1          | Pinning                                                                            | 15.2         | Test ROM                             |

| 5.2          | Pin description                                                                    | 16           | ON-CHIP RAM                          |

| 6            | SYSTEM CONTROL                                                                     | 17           | REGISTER MAPPING                     |

| 6.1          | Memory organization                                                                | 18           | ANOMALIES OF FIRST SAC1 VERSION      |

| 6.2<br>6.3   | Programmable chip-select Dynamic bus port sizing                                   | 18.1         | General                              |

| 6.4          | System Control Register (SYSCON)                                                   | 18.2         | Timer                                |

| 6.5          | Reset operation                                                                    | 18.3<br>18.4 | TAS instruction                      |

| 6.6          | Clock generation                                                                   | 18.5         | NMIN pin<br>Interrupts               |

| 6.7          | Interrupt controller                                                               | 18.6         | UART                                 |

| 6.8          | Power reduction modes                                                              | 18.7         | Watchdog                             |

| 7            | CPU FUNCTIONAL DESCRIPTION                                                         | 18.8         | Chip-select CS6 timing               |

| 7.1          | General                                                                            | 19           | LIMITING VALUES                      |

| 7.2<br>7.3   | Programming model and data organization Processing states and exception processing | 20           | DC CHARACTERISTICS                   |

| 7.4          | Tracing                                                                            | 21           | ADC CHARACTERISTICS                  |

| 7.5          | Stack format                                                                       | 22           | AC CHARACTERISTICS                   |

| 7.6<br>7.7   | CPU interrupt processing Bus arbitration                                           | 23           | 8051 BUS TIMING                      |

| 8            | PORTS                                                                              | 24           | TIMING DIAGRAMS                      |

| 8.1          | Port P Control Register (PCON)                                                     | 25           | CLOCK TIMING                         |

| 8.2          | Port SP                                                                            | 26           | PIN STATES IN VARIOUS MODES          |

| 9            | 8051 PERIPHERAL BUS                                                                | 27           | INSTRUCTION SET AND ADDRESSING MODES |

| 10           | ON-CHIP PERIPHERAL FUNCTIONS                                                       | 27.1         | Addressing modes                     |

| 10.1         | Peripheral interrupt control                                                       | 28           | INSTRUCTION TIMING                   |

| 11           | TIMERS                                                                             | 29           | PACKAGE OUTLINE                      |

| 11.1<br>11.2 | Timer array<br>Timebase                                                            | 30           | SOLDERING                            |

| 11.3         | Channel function                                                                   | 31           | DEFINITIONS                          |

| 11.4         | Pin parallel functions for the timer                                               | 32           | LIFE SUPPORT APPLICATIONS            |

| 11.5         | Timer Control Registers                                                            | 33           | PURCHASE OF PHILIPS I2C COMPONENTS   |

| 11.6         | Timer Status Register                                                              |              |                                      |

| 11.7         | Watchdog timer                                                                     |              |                                      |

| 12           | SERIAL INTERFACES                                                                  |              |                                      |

| 12.1         | UART interface                                                                     |              |                                      |

1995 Sep 21 1125

Baud rate generator

Serial Control Register (SCON)

I<sup>2</sup>C-bus interface

12.2

12.3

12.4

## Low voltage 16-bit microcontroller

P90CL301

#### 1 FEATURES

- Fully 68000 software compatible

- · Static design with 32-bit internal structure

- · Power saving modes: Power-down and Idle mode

- External clock input: 13.8 MHz at 2.7 V

- Single supply voltage of 2.7 to 5.5 V (see Section 2.1);

down to 1.8 V for RAM retention

- 68000-compatible bus interface

- Intel 8051-compatible bus interface

- · 16 Mbytes program/data address range

- · 8 programmable chip-selects

- · Dynamic bus sizing, 16 or 8-bit memory bus port size

- · 56 powerful instruction types:

- 5 basic data types, and

- 14 addressing modes

- · 7 programmable interrupt inputs:

- a Non-Maskable Interrupt input (NMIN)

- 14 auto-vectored interrupts and 7 interrupt priority levels

- 24 port pins (multiplexed with other functions)

- 2 UART serial interfaces; an independent baud rate generator with two programmable outputs (UART0 and UART1)

- I<sup>2</sup>C-bus serial interface

- · 2 timer arrays including:

- two 16-bit reference counter and 8-bit programmable prescaler

- six 16-bit match/capture registers with equality comparators

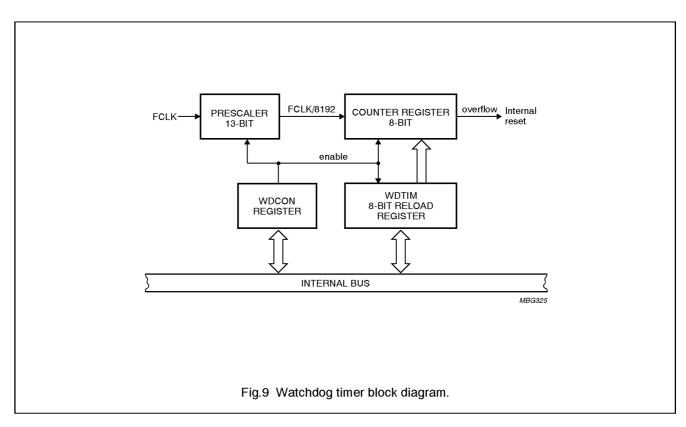

- · Watchdog timer with 21-bit resolution

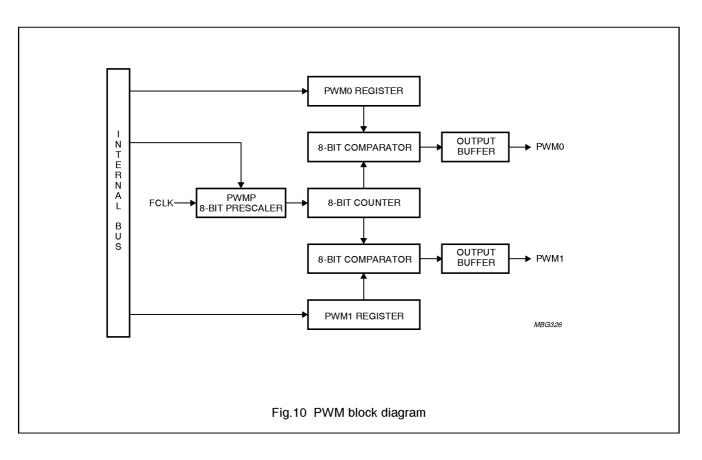

- Two 8-bit Pulse Width Modulation (PWM) outputs with 8-bit prescaler

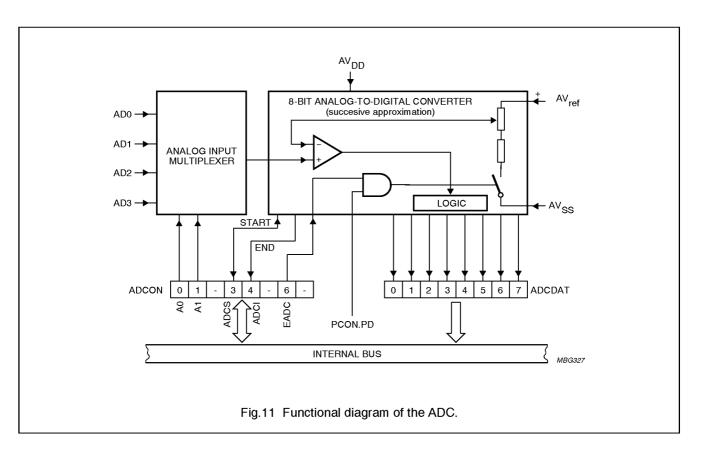

- Four 8-bit analog-to-digital converter (ADC) inputs with Power-down mode

- · 512 bytes RAM on-chip

- On-Circuit Emulation (ONCE) mode and internal test-ROM (256 bytes) for on-board testing

- 80-pin LQFP package (typical height 1.4 mm, pitch 0.5 mm)

- Temperature range -40 to +85 °C

- · 1 micron SACMOS low voltage technology.

#### 2 DESCRIPTION

The P90CL301 is a highly integrated low-voltage 16/32-bit microcontroller especially suitable for digital mobile systems such as GSM, DCS1900, IS54/95 and other applications requiring low voltage, low power consumption and high computing power. It is fully software compatible with the 68000.

The P90CL301 optimizes system cost by providing both standard as well as advanced peripheral functions on-chip. The P90CL301 has a full static design and special Idle and Power-down modes which allow further reduction of the total system power consumption. An 80-pin LQFP package dramatically reduces system size requirements.

#### 2.1 Note on supply voltage

The current version of P90CL301 will be replaced at the beginning of 1996 by a compatible version in C100 process with a supply voltage range of 2.7 to 3.6 V. Thus, designs with the P90CL301 should only be done for a maximum  $V_{DD}$  of 3.6 V.

### 3 ORDERING INFORMATION

| TYPE NUMBER  |        | TEMPERATURE                                                               |          |            |

|--------------|--------|---------------------------------------------------------------------------|----------|------------|

| I TPE NOWBER | NAME   | DESCRIPTION                                                               | VERSION  | RANGE (°C) |

| P90CL301AFH  | LQFP80 | plastic low profile quad flat package; 80 leads;<br>body 12 × 12 × 1.4 mm | SOT315-1 | -40 to +85 |

## Low voltage 16-bit microcontroller

P90CL301

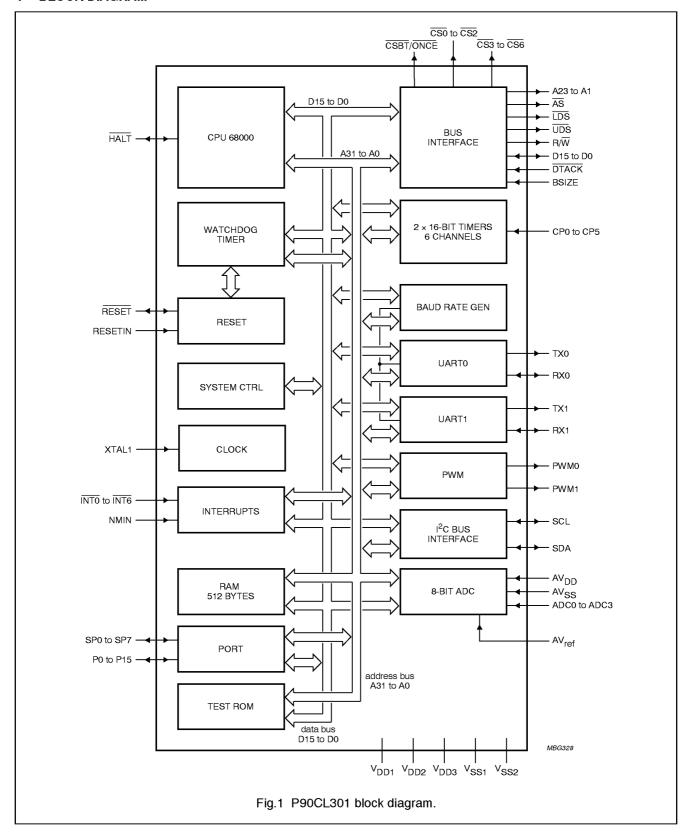

#### 4 BLOCK DIAGRAM

## Low voltage 16-bit microcontroller

P90CL301

#### 5 PINNING INFORMATION

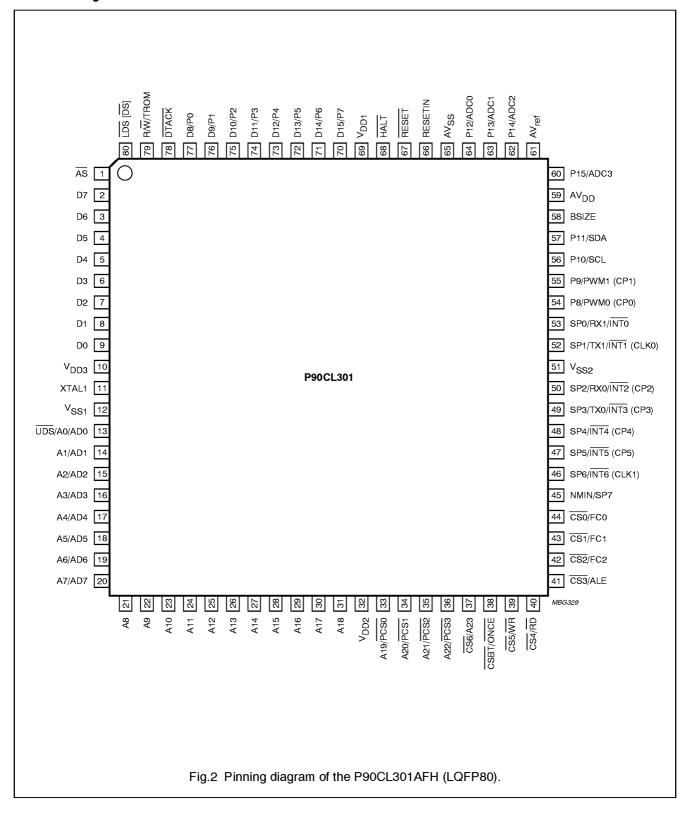

#### 5.1 Pinning

# Low voltage 16-bit microcontroller

P90CL301

## 5.2 Pin description

Table 1 Pin description for the P90CL301

| SYMBOL <sup>(1)</sup> | PIN      | FUNCTION                                                                                                       |

|-----------------------|----------|----------------------------------------------------------------------------------------------------------------|

| A22/PCS3 to A19/PCS0  | 36 to 33 | Upper 4-bits of the address bus or 8051 bus chip-select.                                                       |

| A18 to A8             | 31 to 21 | Upper 11-bits of the 68000 address bus.                                                                        |

| A7/AD7 to A1/AD1      | 20 to 14 | Lower 7-bits of the 68000 address bus or lower 7-bits of the 8051 bus.                                         |

| D7 to D0              | 2 to 9   | Lower 8-bits of data bus.                                                                                      |

| D15/P7 to D8/P0       | 70 to 77 | Upper 8-bits of data bus or 8-bit Port 7 to Port 0; the selected function after reset is defined by pin BSIZE. |

| ĀS                    | 1        | Address strobe.                                                                                                |

| LDS [DS]              | 80       | Lower Data strobe [word Data strobe].                                                                          |

| UDS/A0/AD0            | 13       | Upper data strobe or LSB of address bus or LSB of 8051 address/data.                                           |

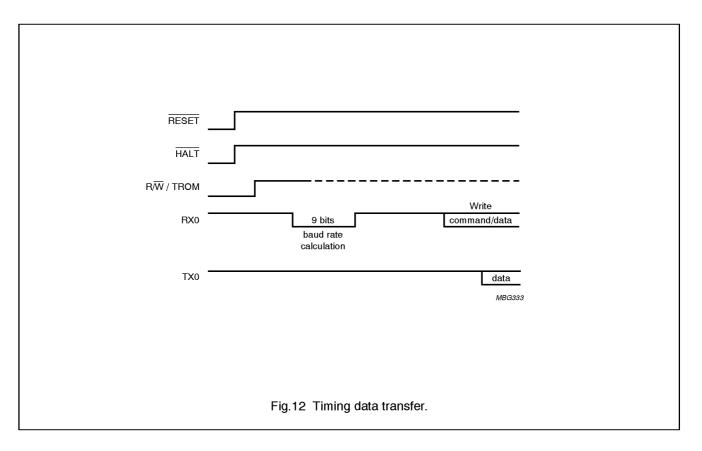

| R/W / TROM            | 79       | Read/Write bus control or test ROM forced input.                                                               |

| DTACK                 | 78       | Data transfer acknowledge.                                                                                     |

| RESET                 | 67       | Reset (bidirectional).                                                                                         |

| RESETIN               | 66       | External Power-on-reset input.                                                                                 |

| HALT                  | 68       | Halt (bidirectional).                                                                                          |

| BSIZE                 | 58       | Data bus size; 8 or 16-bit wide.                                                                               |

| SP0/RX1/INT0          | 53       | Second port pin (bit 0) or Receive data for UART1 or external interrupt input 0.                               |

| SP1/TX1/INT1 (CLK0)   | 52       | Second port pin (bit 1) or Transmit data for UART1 or external interrupt input 1 (external clock of Timer 0).  |

| SP2/RX0/INT2 (CP2)    | 50       | Second port pin (bit 2) or Receive data for UART0 or external interrupt input 2 (Timer 0 capture input 2).     |

| SP3/TX0/INT3 (CP3)    | 49       | Second port pin (bit 3) or Transmit data for UART0 or external interrupt input 3 (Timer 1 capture input 3).    |

| SP4/INT4 (CP4)        | 48       | Second port pin (bit 4) or external interrupt input 4 (Timer 1 capture input 4).                               |

| SP5/INT5 (CP5)        | 47       | Second port pin (bit 5) or external interrupt input 5 (Timer 1 capture input 5).                               |

| SP6/INT6 (CLK1)       | 46       | Second port pin (bit 6) external interrupt input 6 (external clock of timer 1).                                |

| NMIN/SP7              | 45       | Non-Maskable Interrupt or second port pin (bit 7).                                                             |

| P8/PWM0 (CP0)         | 54       | Port pin (bit 8) or PWM0 output (Timer 0 capture input 0).                                                     |

| P9/PWM1 (CP1)         | 55       | Port pin (bit 9) or PWM1 output (Timer 0 capture input 1).                                                     |

| $V_{DD1}$             | 69       | Supply voltage; first pin.                                                                                     |

| $V_{DD2}$             | 32       | Supply voltage; second pin.                                                                                    |

| V <sub>SS1</sub>      | 12       | Ground; first pin.                                                                                             |

| V <sub>SS2</sub>      | 51       | Ground; second pin.                                                                                            |

| XTAL1                 | 11       | External clock input.                                                                                          |

| $V_{\mathrm{DD3}}$    | 10       | Supply voltage; third pin.                                                                                     |

| CS0/FC0 to CS2/FC2    | 44 to 42 | Chip-select 0 to 2 or data bus function code 2 to 0.                                                           |

| CS3/ALE               | 41       | Chip-select 3 or 8051 bus address latch.                                                                       |

| CS4/RD                | 40       | Chip-select 4 or 8051 bus read strobe.                                                                         |

| CS5/WR                | 39       | Chip-select 5 or 8051 bus write strobe.                                                                        |

## Low voltage 16-bit microcontroller

P90CL301

| SYMBOL <sup>(1)</sup> | PIN          | FUNCTION                                                |

|-----------------------|--------------|---------------------------------------------------------|

| P10/SCL               | 56           | Port pin (bit 10) or I <sup>2</sup> C-bus Serial Clock. |

| P11/SDA               | 57           | Port pin (bit 11) or I <sup>2</sup> C-bus Serial Data.  |

| CS6/A23               | 37           | Chip-select 6 or address bit 23.                        |

| CSBT/ONCE             | 38           | Chip-select boot or ONCE mode forced input.             |

| $AV_{DD}$             | 59           | ADC supply voltage.                                     |

| AV <sub>ref</sub>     | 61           | ADC reference voltage.                                  |

| AV <sub>SS</sub>      | 65           | ADC ground.                                             |

| P12/ADC0 to P15/ADC3  | 64 to 62, 60 | Port pin (bit 12 to bit 15) or ADC inputs 0 to 3.       |

### Note

- 1. The following notation is used to describe the multiple pin definitions:

- a) Function1/Function2/Function3: multiplexed functions on the same pin; Function1 or Function2 or Function3. During and after reset the Function1 is selected.

- b) Function1 (Function2): function done in parallel.

- c) Function1 [Function2]: equivalent function.

## Low voltage 16-bit microcontroller

P90CL301

#### 6 SYSTEM CONTROL

### 6.1 Memory organization

The maximum external address space of the controller is 16 Mbytes. The function codes FC0 to FC2 define five address spaces. These address spaces are designated as either User or Supervisor space and as either Program or Data space or as interrupt acknowledge.

For slow memories the CPU can be programmed to insert a number of wait states. This is done via the eight Chip-select Control Registers CSnN. The number of inserted wait states can vary from 0 to 6, or wait states are inserted until the DTACK is pulled LOW by the external address decoding circuitry. If DTACK is asserted continuously, the P90CL301 will run without wait states using bus cycles of three or four clock periods depending on the state of the FBC bit in the SYSCON register.

#### 6.1.1 MEMORY MAP

The memory address space is divided as shown in Table 2; short addressing space with A31 to A15 = 1.

Table 2 Memory address space

| ADDRES    | SS (HEX)  | DESCRIPTION                       |

|-----------|-----------|-----------------------------------|

| FROM      | то        | DESCRIPTION                       |

| 0000 0000 | 00FF FFFF | external 16 Mbytes memory         |

| 0100 0000 | 8000 FFFF | not used                          |

| 8001 0000 | 8001 FFFF | off-chip 64 kbytes on 8051<br>bus |

| 8002 0000 | FFFF 7FFF | not used                          |

| FFFF 8000 | FFFF 8AFF | internal registers                |

| FFFF 8B00 | FFFF 8FFF | not used                          |

| FFFF 9000 | FFFF 91FF | internal 512 bytes RAM            |

| FFFF 9200 | FFFF BFFF | not used                          |

| FFFF C000 | FFFF C0FF | internal 256 bytes test ROM       |

| FFFF C100 | FFFF FFFF | not used                          |

#### 6.2 Programmable chip-select

In order to reduce the external components associated with memory interface, the 90CL301 provides 8 programmable chip-selects. A specific chip-select  $\overline{\text{CSBT}}$  provides default reset values to support a bootstrap operation.

Each chip-select can be programmed with:

- · A base address (A23 to A19)

- A memory bank width of 512 kbytes, 1, 2, 4 or 8 Mbytes memory size

- A number of wait states (0 to 6 states, or wait for <del>DTACK</del>) to adapt the bus cycle to the memory cycle time.

Chip-selects can be synchronized with read, write, or both read and write, either Address strobe or Data strobe. They can also be programmed to address low byte, high byte or word.

Each chip-select is controlled by a control register CSnN (n = 0 to 7). The control registers are described in Table 3 to 7.

The RESET instruction does not affect the content of the CSnN registers.

Register CS7N corresponds to register  $\overline{\text{CSBT}}$  (address FFFF 8A0EH). After reset  $\overline{\text{CSBT}}$  is programmed with a block size of 8 Mbytes with:

- A19 to A23 at logic 0,

- M19 to M22 at logic 1,

- · 6 wait states, and

- · read only mode.

The other chip-selects are held HIGH and will be activated after initialization of their control registers.

When programmed in reduced access mode (read only, write only, low byte, high byte), the wait states are generated internally and if there is any access-violation when the bit WD in the SYSCON register is set to a logic 1 (time-out), the processor will execute a bus error after the time-out delay.

## Low voltage 16-bit microcontroller

P90CL301

### 6.2.1 CHIP SELECT CONTROL REGISTERS (CSNN)

**Table 3** Chip Select Control Registers; n = 0 to 7 (address FFFF 8A00H to FFFF 8A0CH)

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| M22 | M21 | M20 | M19 | RW1 | RW0 | MD1 | MD0 | A23 | A22 | A21 | A20 | A19 | WS2 | WS1 | WS0 |

### Table 4 Description of CSnN bits

| BIT      | SYMBOL     | FUNCTION                                                                                                                                                                                      |

|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 12 | M22 to M19 | Address mask for block size selection; see Table 5.                                                                                                                                           |

| 11 to 10 | RW1 to RW0 | Read/Write bus control (R/ $\overline{W}$ ); see Table 6.                                                                                                                                     |

| 9 to 8   | MD1 to MD0 | MODE selection; see Table 7.                                                                                                                                                                  |

| 7 to 3   | A23 to A19 | Decoded base address; this should be a multiple of the block size (other codes are reserved for test or reset state); after reset: A23 to A19 = 11111 except for CSBT.                        |

| 2 to 0   | WS2 to WS0 | Wait states 0 to 6 (see Table 8); 7 wait for DTACK to be pulled LOW by the external address decoding circuitry. The default value after reset is 6 for CSBT and 7 for the other chip-selects. |

Table 5 Address mask for block size selection

| M22 | M21 | M20 | M19 | BLOCK SIZE       |

|-----|-----|-----|-----|------------------|

| 0   | 0   | 0   | 0   | 512 kbytes       |

| 0   | 0   | 0   | 1   | 1 Mbyte          |

| 0   | 0   | 1   | 1   | 2 Mbytes         |

| 0   | 1   | 1   | 1   | 4 Mbytes         |

| 1   | 1   | 1   | 1   | 8 Mbytes; note 1 |

Table 6 Read/Write bits (R/W)

| RW1 | RWO | FUNCTION                                 |

|-----|-----|------------------------------------------|

| 0   | 0   | Read only with length of $\overline{AS}$ |

| 0   | 1   | Write only with length of DS             |

| 1   | 0   | Write only with length of AS             |

| 1   | 1   | Read/write with length of AS; note 1     |

Table 7 Mode selection

| MD1 | MDo | FUNCTION              |

|-----|-----|-----------------------|

| 0   | 0   | Alternate function    |

| 0   | 1   | Low byte access only  |

| 1   | 0   | High byte access only |

| 1   | 1   | Word access; note 1   |

Table 8 Wait states selection

| WS2 | WS1 | WS0 | WAIT STATES      |

|-----|-----|-----|------------------|

| 0   | 0   | 0   | 0                |

| 0   | 0   | 1   | 1                |

| 0   | 1   | 0   | 2                |

| 0   | 1   | 1   | 3                |

| 1   | 0   | 0   | 4                |

| 1   | 0   | 1   | 5                |

| 1   | 1   | 0   | 6 <sup>(1)</sup> |

#### Note to Tables 4 to 8

1. The default value after a CPU-reset.

## Low voltage 16-bit microcontroller

P90CL301

Table 9 Number of clock periods per bus cycle

Number of clock periods per bus cycle, dependent on the programmed length of FBC (Fast Bus Cycle bit in the SYSCON register) and CSn (chip-select).

|                | LENGTH O | F CSn = LENC | GTH OF AS | LENGTH OF $\overline{\text{CSn}}$ = LENGTH OF $\overline{\text{DS}}$ |       |         |       |

|----------------|----------|--------------|-----------|----------------------------------------------------------------------|-------|---------|-------|

| WAIT<br>STATES | FBC = 1  |              | FBC = 0   | FBC = 1                                                              |       | FBC = 0 |       |

|                | READ     | WRITE        | R/W       | READ                                                                 | WRITE | READ    | WRITE |

| 0              | 3        | 4            | 4         | 3                                                                    | 4     | 4       | 4     |

| 1              | 4        | 4            | 4         | 4                                                                    | 5     | 4       | 5     |

| 2              | 5        | 5            | 5         | 5                                                                    | 6     | 5       | 6     |

| 3              | 6        | 6            | 6         | 6                                                                    | 7     | 6       | 7     |

| 4              | 7        | 7            | 7         | 7                                                                    | 8     | 7       | 8     |

| 5              | 8        | 8            | 8         | 8                                                                    | 9     | 8       | 9     |

| 6              | 9        | 9            | 9         | 9                                                                    | 10    | 9       | 10    |

#### 6.3 Dynamic bus port sizing

The memory bus size can be selected to be 16 or 8-bit wide depending on the ports width of external memories and peripherals. When the external pin BSIZE is LOW, it is possible via register BSREG to define for each chip-select the bus width to 16-bit or 8-bit used for the transfer of data to or from external memory.

If the pin BSIZE is HIGH, the only possible transfers are in 8-bit mode and the upper bits (15 to 8) of the data bus are used as port pins. The state of the pin BSIZE is latched at the end of the reset sequence.

The 7-bit register BSREG defines the bus size affected to each chip-select function (except for CS7).

The bus size of the chip-select boot CS7 is hardware defined by the pin BSIZE. See also Section 6.2 for more information on the programmable chip-selects.

When an address generated by the CPU is identified by a chip-select block as belonging to its address segment, the corresponding bit of the register BSREG is used to define the sequence of bus transfer in 16 or 8-bit mode. Several chip-selects with different bus sizes should not address the same memory segment. For each case the number of bus cycles necessary to transfer a byte, word or long word is a function of the bus size. For example, a word read on a 8-bit bus will take 2 bus cycles and the high byte is read first. The 8-bit port uses the pins D7 to D0.

### 6.3.1 Bus Size Register (BSREG)

Table 10 Bus Size Register (address FFFF A811H)

| 7 | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---|-----|-----|-----|-----|-----|-----|-----|

| _ | BS6 | BS5 | BS4 | BS3 | BS2 | BS1 | BS0 |

Table 11 Description of BSREG bits; see note 1

| ВІТ    | SYMBOL     | DESCRIPTION                                                                         |

|--------|------------|-------------------------------------------------------------------------------------|

| 7      | _          | Reserved.                                                                           |

| 6 to 0 | BS6 to BS0 | Bus size for the data transfer with respect to the corresponding chip-select (CSn): |

|        |            | If BSn = 0, then the bus size is in 16-bit mode; note 2.                            |

|        |            | If BSn = 1, then the bus size is in 8-bit mode.                                     |

### Notes

- 1. n = 0 to 6.

- The default value after a CPU reset.

## Low voltage 16-bit microcontroller

P90CL301

### 6.4 System Control Register (SYSCON)

The P90CL301 uses a System Control Register (SYSCON) for adjusting system parameters.

Table 12 System Control Register (address FFFF 8000H); see note 1

| 10    | 9   | 8  | <b>7</b> <sup>(2)</sup> | <b>6</b> <sup>(2)</sup> | 5  | 4  | 3   | 2  | <b>1</b> <sup>(3)</sup> | 0    |

|-------|-----|----|-------------------------|-------------------------|----|----|-----|----|-------------------------|------|

| PCLK2 | PDE | GF | PCLK1                   | PCLK0                   | IM | WD | FBC | PD | IDL                     | DOFF |

#### **Notes**

- 1. The bits 11 to 15 in SYSCON are reserved and should not be used.

- The default values after a CPU-reset: PCLK1 = 1 and PCLK0 = 1; all the other bits = 0.

- 3. All bits are reset by the RESET instruction, except the IDL bit which is only reset by a CPU-reset.

### Table 13 Description of SYSCON bits

| BIT | SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

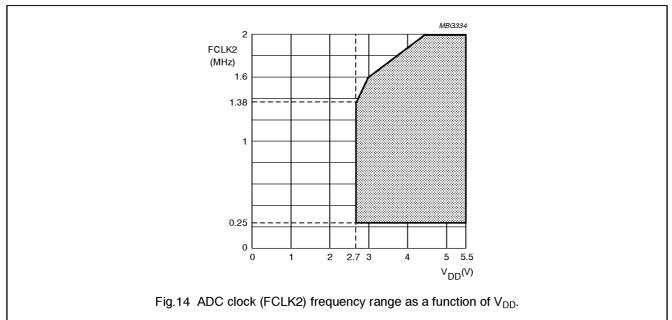

| 10  | PCLK2  | Prescaler for secondary peripheral clock FCLK2 (derived from the primary peripheral clock FCLK), used for the ADC; the maximum value of the FCLK2 clock is dependent on the supply voltage $V_{DD}$ ; see Section 20. If PCLK = 0, then FCLK is divided by 2; if If PCLK = 1, then FCLK is divided by 4.                                                                                    |

| 9   | PDE    | If PDE = 0, then bits A22 to A19 are in normal operation; If PDE =1, then bits A22 to A19 are used as 8051 peripheral chip-select $\overline{PCS3}$ to $\overline{PCS0}$ .                                                                                                                                                                                                                  |

| 8   | GF     | General purpose flag bit; reset to a logic 0 after CPU-reset.20                                                                                                                                                                                                                                                                                                                             |

| 7   | PCLK1  | Prescaler for primary peripheral clock (FCLK). The CPU clock = CLK; FCLK = $\frac{1}{\text{divisor}} \times \text{CLK}$ .                                                                                                                                                                                                                                                                   |

| 6   | PCLK0  | See Table 14 for divisor values.                                                                                                                                                                                                                                                                                                                                                            |

| 5   | IM     | For IM = 0, level 7 is loaded into the Status Register during interrupt processing to prevent the CPU from being interrupted by another interrupt source. For IM = 1, the current interrupt level is loaded into the Status Register allowing nested interrupts.                                                                                                                            |

| 4   | WD     | For WD = 0, the time-out for bus error detection is switched off. If the time-out is not used, the Watchdog timer can be used to stop a non-acknowledged bus transfer. For WD = 1, the time-out for bus error detection is activated. If no $\overline{\text{DTACK}}$ has been sent by the addressed device after 128 × 16 internal clock cycles the on-chip bus error signal is activated. |

| 3   | FBC    | FBC = 0, normal bus cycle; FBC = 1, fast bus cycle. An external read bus cycle can take a minimum of 3 clock periods; the minimum write cycle is still 4 clock periods; in order to get this access time DTACK should be asserted on time.                                                                                                                                                  |

| 2   | PD     | PD = 0, for normal mode; PD = 1, for Power-down mode (see Section 6.8).                                                                                                                                                                                                                                                                                                                     |

| 1   | IDL    | IDL = 0, for normal mode; IDL = 1, for Idle mode (see Section 6.8).                                                                                                                                                                                                                                                                                                                         |

| 0   | DOFF   | DOFF = 0, for normal mode. DOFF = 1, for delay counter off; if set at Wake-up from Power-down the delay counter waiting period is skipped.                                                                                                                                                                                                                                                  |

Table 14 Prescaler divisor values

| PCLK1 | PCLK0 | DIVISOR (D)                         |

|-------|-------|-------------------------------------|

| 0     | 0     | 2                                   |

| 0     | 1     | 3                                   |

| 1     | 0     | 4                                   |

| 1     | 1     | 5 (default value after a CPU-reset) |

## Low voltage 16-bit microcontroller

P90CL301

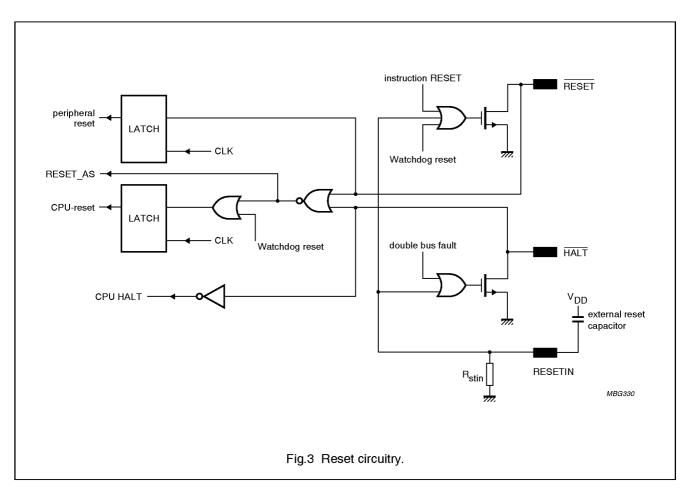

### 6.5 Reset operation

The reset circuitry of the P90CL301 is connected to the pins RESET, HALT, RESETIN and to the internal Watchdog timer. A Schmitt trigger is used at the input pin for noise rejection. After Power-on a CPU reset is accomplished by holding the RESET pin and the HALT pin LOW for at least 50 oscillator clocks after the oscillator has stabilized.

For further information on the clock generation, see Section 6.6. The CPU responds by reading the reset vectors, the long word at address 000000H is loaded into the Supervisor stack, the data at address 000004H is loaded into the program counter PC. The interrupt level is set to 7 in the Status Register and execution starts at the PC location. By pulling the RESET pin LOW and keeping HALT HIGH, only the peripherals are reset.

When  $V_{DD}$  is turned on and its rise time does not exceed 10 ms, an automatic reset can be performed by connecting the RESETIN pin to  $V_{DD}$  via an external capacitor. The external capacitor is charged via an internal pull-down resistor.

The RESET pin can also be pulled LOW internally by a pull-down transistor activated by an overflow of the Watchdog timer. When the CPU executes a RESET instruction, the RESET pin is pulled LOW. When the CPU is internally halted (at double bus fault), the HALT pin is pulled LOW and only a CPU reset can restart the processor.

The signal RESET\_AS (Reset Asynchronous) resets the core and all registers.

When an internal Watchdog timer overflow occurs, an internal CPU reset is generated which resets all registers except the SYSCON, PCON, PRL and PRH registers and pulls the RESET pin LOW during 12 clock cycles.

## Low voltage 16-bit microcontroller

P90CL301

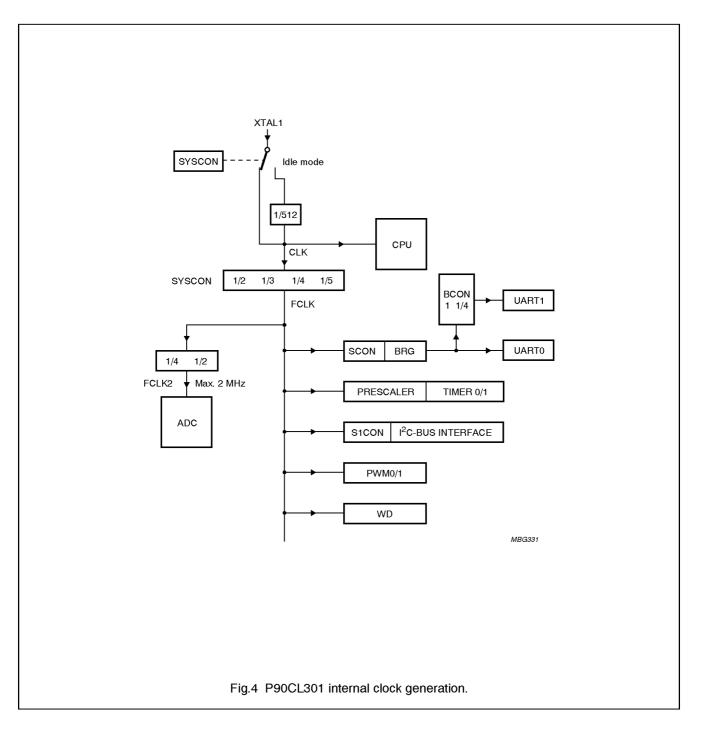

#### 6.6 Clock generation

The P90CL301 can be used where an external clock is available. The duty cycle of the external clock should be  $50/50 \pm 5\%$  over the full temperature and voltage range.

For peripherals like Watchdog timer, I<sup>2</sup>C, PWM, TIMER, and baud rate generator, a programmable prescaler generates a peripheral clock FCLK.

The prescaler is controlled by the System Control Register (SYSCON). The internal clock is divided by a factor 2, 3, 4, or 5 (function of bits PCLK1 and PCLK0; see Table 14). For the ADC a secondary peripheral clock FCLK2 is derived from the peripheral clock by dividing it either by 4 or 2 (function of the bit PCLK2; see Table 13).

## Low voltage 16-bit microcontroller

P90CL301

#### 6.7 Interrupt controller

An interrupt controller handles all internal and external interrupts. It delivers the interrupt with the highest priority level to the CPU. The following interrupt requests are generated by the on-chip peripherals:

- I<sup>2</sup>C

- · UARTs: received data / transmitted data

- · TIMERs: two flags for the timers T0 and T1

- · ADC: analog-to-digital conversion completed.

The external interrupt requests are generated with the pins NMIN and the seven external interrupts  $\overline{\text{INT0}}$  to  $\overline{\text{INT6}}$ .

#### 6.7.1 INTERRUPT ARBITRATION

The interrupt priority levels are programmable with a value between 0 and 7. Level 7 has the highest priority, level 0 disables the corresponding interrupt source. In case of interrupt requests of equal priority level at the same time a hardware priority mechanism gives priority order as shown in Table 15.

The execution of interrupt routines can be interrupted by another interrupt request of a higher priority level. In 68070 mode (in SYSCON bit IM = 1) when an interrupt is serviced by the CPU, the corresponding level is loaded into the Status Register. This prevents the current interrupt from getting interrupted by any other interrupt request on the same or a lower priority level. If IM is reset, priority level 7 will always be loaded into the Status Register and so the current interrupt cannot be interrupted by an interrupt request of a level less than 7.

Each on-chip peripheral unit including the eight interrupt lines generates only auto-vectored interrupts. No acknowledge is necessary. For external interrupts the vectors 25 to 31 are used, for on-chip peripheral circuits a second table of 7 vectors are used (57 to 63); see Section 7.3.2.

Table 15 Priority order

| SIGNAL            | PRIORITY ORDER |

|-------------------|----------------|

| NMIN              | highest        |

| ĪNT6              |                |

| ĪNT5              |                |

| ĪNT4              |                |

| ĪNT3              |                |

| ĪNT2              |                |

| ĪNT1              |                |

| ĪNT0              |                |

| I <sup>2</sup> C  |                |

| ADC               |                |

| UART1 receiver    |                |

| UART1 transmitter |                |

| UART0 receiver    |                |

| UART0 transmitter |                |

| TIMER 1           |                |

| TIMER 0           | lowest         |

#### 6.7.2 EXTERNAL LATCHED INTERRUPTS

NMIN and INTO to INT6 are 8 external interrupt inputs. These pins are connected to the interrupt function only when the corresponding bit in the SPCON control register is set (see SP port description). Seven interrupt inputs INTO to INT6 are edge sensitive on HIGH-to-LOW transition and their priority levels are programmable. The interrupt NMIN is non-maskable (except if it is programmed as a port) and its level is fixed to 7.

The external interrupts are controlled by the registers LIR0 to LIR3; see Tables 16 and 17.

## Low voltage 16-bit microcontroller

P90CL301

#### 6.7.2.1 Latched Interrupt Registers (LIR0 to LIR3)

### Table 16 Latched Interrupt Registers

| ADDRESS   | REGISTER | 7    | 6      | 5      | 4      | 3    | 2      | 1      | 0      |

|-----------|----------|------|--------|--------|--------|------|--------|--------|--------|

| FFF 8101H | LIR0     | PIR1 | IPL1.2 | IPL1.1 | IPL1.0 | PIR0 | IPL0.2 | IPL0.1 | IPL0.0 |

| FFF 8103H | LIR1     | PIR3 | IPL3.2 | IPL3.1 | IPL3.0 | PIR2 | IPL2.2 | IPL2.1 | IPL2.0 |

| FFF 8105H | LIR2     | PIR5 | IPL5.2 | IPL5.1 | IPL5.0 | PIR4 | IPL4.2 | IPL4.1 | IPL4.0 |

| FFF 8107H | LIR3     | PIR7 | 1      | 1      | 1      | PIR6 | IPL6.2 | IPL6.1 | IPL6.0 |

#### Table 17 Description of LIR0 to LIR3 bits

| BIT     | SYMBOL               | FUNCTION                                                                                                                                                                                         |

|---------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 and 3 | PIRn                 | Pending interrupt request. $n = 0$ to 7; INT7 corresponds to the interrupt NMIN; PIRn = 1, pending interrupt request for pin $\overline{INTn}$ ; PIRn = $0^{(1)}$ , no pending interrupt; note 2 |

| 6 to 4  | IPLm.2 to IPLm.0     | Interrupt priority level of pins INT0 to INT6 (fixed to 111 for NMIN in LIR3);                                                                                                                   |

| 2 to 0  | IFLIII.2 to IFLIII.0 | m = 0 to 6.                                                                                                                                                                                      |

#### **Notes**

- 1. The default value after a CPU-reset.

- 2. When a valid interrupt request has been detected this bit is set. It is automatically reset by the interrupt acknowledge cycle from the CPU. It can be reset by software by writing a logic 0, however writing a logic 1 has no effect on the flag. To reset only one flag, a logic 0 should be written to the bit address and a logic 1 to the other interrupt requests. The use of BCLR instruction should be avoided (PIR7 is cleared when the pin NMIN is set HIGH).

## Low voltage 16-bit microcontroller

P90CL301

#### 6.8 Power reduction modes

The P90CL301 supports two power reduction modes. A Power-down mode were the clock is frozen, and an Idle mode were the clock is divided by 512 (see Fig.4).

#### 6.8.1 POWER-DOWN MODE

The Power-down operation freezes the oscillator. The Power-down mode can only be activated by setting the PD bit in the SYSCON register and thereafter execute the STOP instruction.

The instruction flow to enter the Power-down mode is:

BSET #PD, SYSCON

STOP #\$2700.

In this state all the register contents are preserved. The CPU remains in this state until an external reset occurs or a LOW level is present on any of the external interrupt pins INTO to INT6 or NMIN. If the Wake-up is done via an external interrupt, the processor will first execute an external interrupt of level 7.

In Power-down mode  $V_{DD}$  may be reduced to minimize power consumption. However, the supply voltage must not be reduced until Power-down mode is active, and must be restored before a external reset or an interrupt is activated.

In case of an external reset, the pin should be held active until the oscillator has restarted and stabilized. To exit the Power-down mode the level interrupt registers LIRn of the corresponding pin should be programmed to level 7 and the interrupt mask of the Status Register set to 7.

For the use of an external interrupt Wake-up, this is done as soon as any INTn or NMIN pin goes LOW. If the DOFF bit in the SYSCON is not set, an internal delay counter ensures that the internal clock is not active before 1536 clock cycles. After that time the oscillator is stable and normal exception processing can be executed.

If an external oscillator is used, and in order to have a fast start-up the DOFF bit should be set, switching off the delay counter and enabling the immediate clocking and restart of the controller.

For minimum power consumption during Power-down mode, the address and data pins should be pulled HIGH externally. The port pins with internal pull-up's can also be pulled HIGH externally during Power-down mode for the same reason.

#### 6.8.2 IDLE MODE

In the Idle mode the crystal or external clock is divided by a factor 512. The current is reduced drastically but the controller continues to operate. This mode is entered by setting the bit IDL in the SYSCON register. The next instruction will be executed at a slower speed. To return to normal mode the IDL bit should be reset.

It should be noted that all peripheral functions are also slowed down, and some cannot be used normally for example UART, I<sup>2</sup>C, ADC and PWM. The Power-down mode can also be entered from the Idle mode. After a Wake-up the controller restarts in Idle mode.

## Low voltage 16-bit microcontroller

P90CL301

#### 7 CPU FUNCTIONAL DESCRIPTION

#### 7.1 General

The CPU of the 90CL301 is software compatible with the Motorola MC68000, meaning programs written for the MC68000 will run on the 90CL301 without modifications. However, for certain applications the following differences between processors should be noted:

- Differences exist in the address/bus error exception processing since the 90CL301 can provide full error recovery.

- The timing is different for the P90CL301 due to a new internal architecture and technology. The instruction execution timing is different for the same reasons.

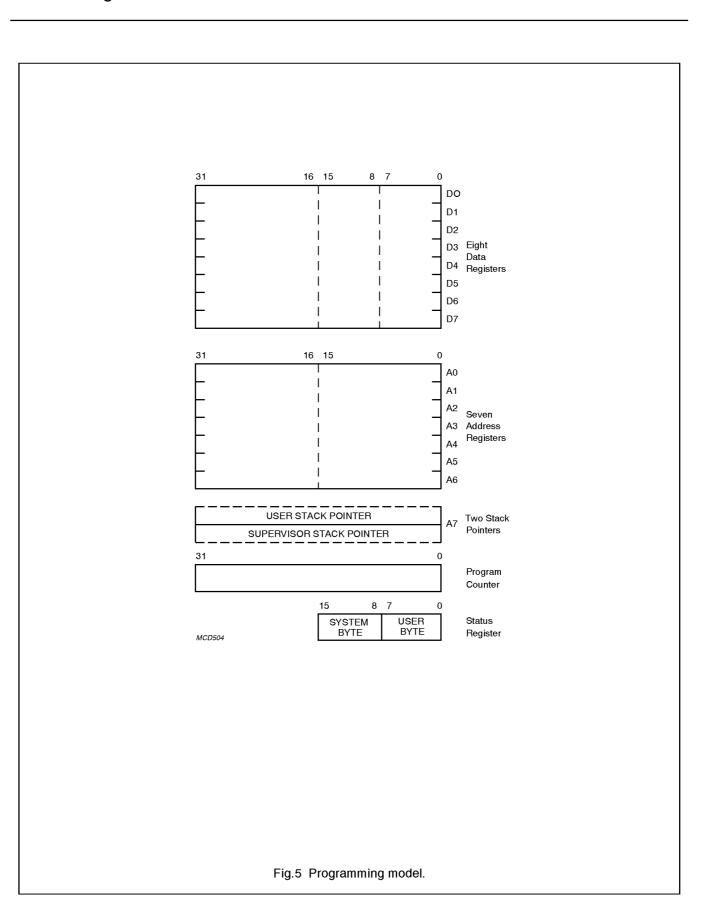

### 7.2 Programming model and data organization

The programming model is identical to the MC68000 one as shown below with seventeen 32-bit registers, a 32-bit Program Counter and a 16-bit Status Register. The eight data registers (D0 to D7) are used for byte, word and long-word operations. The address registers (A0 to A6) and the system stack pointer A7 can be used as software stack pointers and base address registers. In addition, these registers can be used for word and long-word address operations. All seventeen registers can be used as index registers.

The 90CL301 supports 8, 16 and 32-bit integers as well as BCD data and 32-bit addresses. Each data type is arranged in the memory as shown in Fig.6.

**Table 18** Format of the Status Register and description of the bits; r = reserved

| 15         | 14 | 13         | 12 | 11 | 10 | 9              | 8  | 7 | 6 | 5 | 4      | 3        | 2    | 1        | 0     |

|------------|----|------------|----|----|----|----------------|----|---|---|---|--------|----------|------|----------|-------|

| Т          | 1  | S          | 1  | -  | 12 | 11             | 10 | ı | 1 | - | Х      | N        | Z    | V        | С     |

| Trace mode | r  | Supervisor | ı  | r  |    | Interrupt mask |    |   | r |   | Extend | Negative | Zero | Overflow | Carry |

## Low voltage 16-bit microcontroller

P90CL301

# Low voltage 16-bit microcontroller

P90CL301

(a) Bit data (1 Byte = 8 bits).

| bit | 15     | 14 | 13     | 12 | 11 | 10 | 9 | 8   | 7         | 6 | 5  | 4    | 3 | 2 | 1 | 0 |

|-----|--------|----|--------|----|----|----|---|-----|-----------|---|----|------|---|---|---|---|

|     | мѕ     | В  | BYTE 0 |    |    |    |   | LSB | SB BYTE 1 |   |    |      |   |   |   |   |

|     | BYTE 2 |    |        |    |    |    |   |     |           |   | B١ | /TE: | 3 |   |   |   |

(b) Integer data (1 Byte = 8 bits).

| bit | 15         | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4   | 3 | 2 | 1 | 0 |

|-----|------------|----|----|----|----|----|---|---|---|---|---|-----|---|---|---|---|

|     | MSB WORD 0 |    |    |    |    |    |   |   |   |   |   | LSB |   |   |   |   |

|     | WORD 1     |    |    |    |    |    |   |   |   |   |   |     |   |   |   |   |

|     | WORD 2     |    |    |    |    |    |   |   |   |   |   |     |   |   |   |   |

(c) Word data (16 bits).

| bit | 15 | 14 | 13 | 12            | 11    | 10          | 9   | 8 | 7          | 6    | 5    | 4        | 3 | 2  | 1 | 0 |  |

|-----|----|----|----|---------------|-------|-------------|-----|---|------------|------|------|----------|---|----|---|---|--|

|     | MS | В  |    | LON           | C 14/ | ∆DD.        | Λ - |   | HIGH ORDER |      |      |          |   |    |   |   |  |

|     |    |    |    | LON           | G VV  | טחט         | 0 - |   | LOW        | OR   |      |          |   | SB |   |   |  |

|     |    |    |    | LON           | C 14/ | ∩DN         | 1 - |   | HIGI       | I OF | RDEF | <u> </u> |   |    |   |   |  |

|     |    |    |    | LON           | G VV  | UND         | '   |   | LOW        | OR   | DER  |          |   |    |   |   |  |

|     |    |    |    | LON           | C 14/ | <b>O</b> DD | 0 - |   | HIGI       | I OF | RDEF | }        |   |    |   |   |  |

|     |    |    |    | LONG WORD 2 — |       |             |     |   | LOW        | OR   |      |          |   |    |   |   |  |

(d) Long-word data (32 bits).

| bit | 15              | 14 | 13 | 12 | 11        | 10 | 9    | 8    | 7         | 6    | 5        | 4        | 3 | 2 | 1   | 0  |

|-----|-----------------|----|----|----|-----------|----|------|------|-----------|------|----------|----------|---|---|-----|----|

|     | MSB — ADDRESS 0 |    |    |    |           |    |      |      | HIGI      | I OF | RDEF     | <u> </u> |   |   |     | _] |

|     | ADDRESS 0       |    |    |    |           |    |      |      | LOV       | OR   | DER      |          |   |   | L   | SB |

|     | ADDRESS 1       |    |    |    |           |    |      | HIGI | I OF      | RDEF | <u> </u> |          |   |   | _ ] |    |

|     |                 |    |    |    | ADDRESS 1 |    |      |      | LOW ORDER |      |          |          |   |   |     |    |

|     | ADDDE00.0       |    |    |    |           |    | HIGI | I OF | RDEF      | 3    |          |          |   |   |     |    |

|     | — — — ADDRESS 2 |    |    |    |           |    |      | LOV  | OR        | DER  |          |          |   |   |     |    |

(e) Addresses (1 address =32 bits).

| bit | 15 | 14 | 13  | 12 | 11 | 10   | 9        | 8   | 7 | 6 | 5   | 4 | 3 | 2     | 1 | 0 |

|-----|----|----|-----|----|----|------|----------|-----|---|---|-----|---|---|-------|---|---|

|     | MS | SB | BCD | 0  | В  | CD 1 |          | LSB |   |   | BCD | 2 | Е | BCD ( | 3 |   |

|     |    |    | BCD | 4  | В  | CD 5 | <u> </u> |     |   |   | BCD | 6 | Е | BCD 7 | 7 |   |

(f) BCD data (2 BCD digits = 1 Byte).

MCD505

Fig.6 Memory data organization.

## Low voltage 16-bit microcontroller

P90CL301

#### 7.3 Processing states and exception processing

The 90CL301 operates with a maximum internal clock frequency of 20 MHz ( $f_{xtal}$  = 40 MHz) down to static operation. Each clock cycle is divided into 2 states. A non-access machine cycle has 3 clock cycles or 6 states (S0 to S5). A minimum bus cycle normally consists of 3 clock cycles (6 states). When  $\overline{DTACK}$  is not asserted, indicating that data transfer has not yet been terminated, wait states (WS) are inserted in multiples of 2.

The CPU is always in one of the four processing states:

- · Normal,

- · Exception,

- · Halt, or

- · Stopped.

The Normal processing state is associated with instruction execution; the memory references fetch instructions or load/save results. A special case of the Normal state is the Stopped state which is entered by the processor when a STOP instruction is executed. In this state the CPU does not make any further memory references.

The Exception state is associated with interrupts, trap instruction, tracing and other exceptional conditions. The exception may be generated internally by an instruction or by any unusual condition arising during the execution of an instruction. Externally, exception processing can be forced by an interrupt or by reset.

The halted processing state is an indication of a catastrophic hardware failure. For example, if during exception processing of a bus error another bus error occurs, the CPU assumes that the system is unusable and halts. Only an external reset can restart a halted processor. Note that a CPU in the stopped state is not in the halted state or vice versa.

The Supervisor can work in the User or Supervisor state determined by the state of bit S in the Status Register. Accesses to the on-chip peripherals are achieved in the Supervisor state.

All exception processing is performed in the Supervisor state once the current contents of the Status Register has been saved. Then the exception vector number is determined and copies of the Status Register, the program counter and the format/vector number are saved on the Supervisor stack using the Supervisor Stack Pointer (SSP). Finally the contents of the exception vector location is fetched and loaded into the Program Counter (PC).

#### 7.3.1 REFERENCE CLASSIFICATION

When the processor makes a reference, it classifies the kind of reference begin made, using the encoding of the three function code output lines. This allows external translation of addresses, control of access, and differentiation of special processor states, such as interrupt acknowledge. Table 19 shows the classification of references.

Table 19 Reference classification

| FUNCTION | ON CODE | OUTPUT | REFERENCE CLASS       |

|----------|---------|--------|-----------------------|

| FC2      | FC1     | FC0    | REFERENCE CLASS       |

| 0        | 0       | 0      | unassigned            |

| 0        | 0       | 1      | User Data             |

| 0        | 1       | 0      | User Program          |

| 0        | 1       | 1      | unassigned            |

| 1        | 0       | 0      | unassigned            |

| 1        | 0       | 1      | Supervisor Data       |

| 1        | 1       | 0      | Supervisor Program    |

| 1        | 1       | 1      | interrupt acknowledge |

#### 7.3.2 EXCEPTION VECTORS

Exception vectors are memory locations from where the CPU fetches the address of a routine that will handle that exception. All exception vectors are 2 words long, except for the reset vector which consists of 4 words, containing the PC and the SSP. All exception vectors are in the Supervisor Data space.

A vector number is an 8-bit number which, multiplied by 4, gives the address of an exception vector. Vector numbers are generated internally. The memory map for the exception vectors is shown in the Table 20.

# Low voltage 16-bit microcontroller

P90CL301

Table 20 Exception vector assignment

| VECTOR NO.              | DEC         | HEX        | ASSIGNMENT                             |

|-------------------------|-------------|------------|----------------------------------------|

| 0                       | 0           | 000        | reset: initial SSP                     |

| _                       | 4           | 004        | reset: initial PC                      |

| 2                       | 8           | 008        | bus error                              |

| 3                       | 12          | 00C        | address error                          |

| 4                       | 16          | 010        | illegal instruction                    |

| 5                       | 20          | 014        | zero divide                            |

| 6                       | 24          | 018        | CHK instruction                        |

| 7                       | 28          | 01C        | TRAPV instruction                      |

| 8                       | 32          | 020        | privilege violation                    |

| 9                       | 36          | 024        | trace                                  |

| 10                      | 40          | 028        | line 1010 emulator                     |

| 11                      | 44          | 02C        | line 1111 emulator                     |

| 12 <sup>(1)</sup>       | 48          | 030        | unassigned, reserved                   |

| 13 <sup>(1)</sup>       | 52          | 034        | unassigned, reserved                   |

| 14                      | 56          | 038        | format error                           |

| 15                      | 60          | 03C        | uninitialized interrupt vector         |

| 16 to 23 <sup>(1)</sup> | 64 to 95    | 040 to 05C | unassigned, reserved                   |

| 24                      | 96          | 060        | spurious interrupt                     |

| 25                      | 100         | 064        | level 1 external interrupt auto-vector |

| 26                      | 104         | 068        | level 2 external interrupt auto-vector |

| 27                      | 108         | 06C        | level 3 external interrupt auto-vector |

| 28                      | 112         | 070        | level 4 external interrupt auto-vector |

| 29                      | 116         | 074        | level 5 external interrupt auto-vector |

| 30                      | 120         | 078        | level 6 external interrupt auto-vector |

| 31                      | 124         | 07C        | level 7 external interrupt auto-vector |

| 32 to 47                | 128 to 191  | 080 to 0BF | TRAP instruction vectors               |

| 48 to 56 <sup>(1)</sup> | 192 to 227  | 0C0 to 0E3 | reserved                               |

| 57                      | 228         | 0E4        | level 1 on-chip interrupt auto-vector  |

| 58                      | 232         | 0E8        | level 2 on-chip interrupt auto-vector  |

| 59                      | 236         | 0EC        | level 3 on-chip interrupt auto-vector  |

| 60                      | 240         | 0F0        | level 4 on-chip interrupt auto-vector  |

| 61                      | 244         | 0F4        | level 5 on-chip interrupt auto-vector  |

| 62                      | 248         | 0F8        | level 6 on-chip interrupt auto-vector  |

| 63                      | 252         | 0FC        | level 7 on-chip interrupt auto-vector  |

| 64 to 255               | 256 to 1023 | 100 to 3FF | reserved                               |

### Note

1. Vectors 12, 13, 16 to 23 and 48 to 56 are reserved for future enhancements.

## Low voltage 16-bit microcontroller

P90CL301

#### 7.3.3 INSTRUCTION TRAPS

Traps are exceptions caused by instructions arising from CPU recognition of abnormal conditions during instruction execution or from instructions whose normal behaviour is to cause traps.

Some instructions are used specifically to generate traps. The TRAP instruction always forces an exception and is useful for implementing system calls for User Programs. The TRAPV and CHK instructions force an exception if the User Program detects a run-time error, possibly an arithmetic overflow or a subscript out of bounds. The signed divide (DIVS) and unsigned divide (DIVU) instructions will force an exception if a divide-by-zero operation is attempted.

#### 7.3.4 ILLEGAL AND UNIMPLEMENTED INSTRUCTIONS

Illegal instruction is the term used to refer to any word that is not the first word of a legal instruction. During execution, if such an instruction is fetched an illegal exception occurs.

Words with bits 15 to 12 equal to '1010' or '1111' are defined as unimplemented instructions and separate exception vectors are allocated to these patterns for efficient emulation. This facility means the operating system can detect program errors, or can emulate unimplemented instructions in software.

### 7.3.5 PRIVILEGE VIOLATIONS

To provide system security, various instructions are privileged and any attempt to execute one of the privileged instruction while the CPU is in the User state provokes an exception. The privileged instructions are:

- STOP

- RESET

- RTE

- MOVE to SR

- · AND (word) immediate to SR

- EOR (word) immediate to SR

- · OR (word) immediate to SR

- · MOVE to USP.

#### 7.4 Tracing

The CPU includes a facility to trace instructions one by one to assist in program development. In the trace state, after each instruction is executed, an exception is forced so that the debugging program can monitor execution of the program under test.

The trace facility uses the T-bit in the Supervisor part of the Status Register. If the T-bit is cleared, tracing is disabled and instructions are executed normally. If the T-bit is set at the beginning of the execution of an instruction, a trace exception will be generated once the instruction has been executed. If the instruction is not executed, either because of an interrupt, or because the instruction is illegal or privileged, the trace exception does also not occur if the instruction is aborted by a reset, bus error, or address error exception. If the instruction is executed, and an interrupt is pending, the trace exception is processed before the interrupt. If the execution of an instruction forces an exception, the forced exception is processed before the trace exception.

As an extreme illustration of the above rules, consider the arrival of an interrupt during the execution of a TRAP instruction, while tracing is enabled. First the trap exception is processed, followed by the trace exception, and finally the interrupt handling routine.

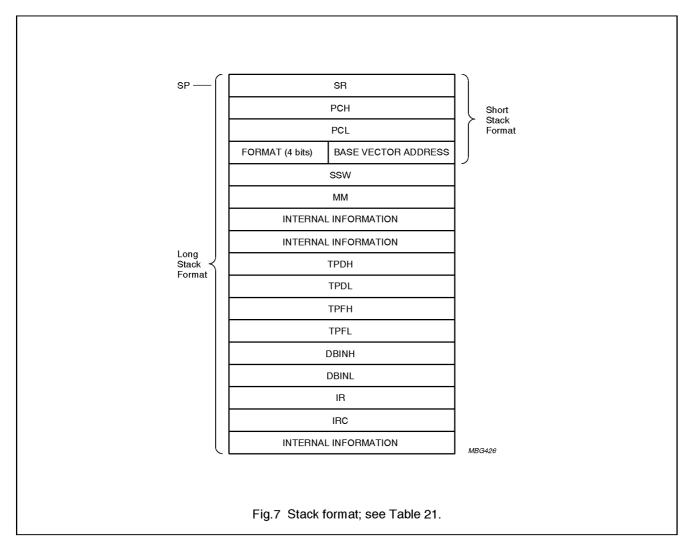

#### 7.5 Stack format

The stack format for exception processing is similar to the MC68010 although the instruction stored is not the same, due to the different architecture. To handle this format the 90CL301 differs from the MC68000 in that:

- · The stack format is changed.

- The minimum number of words put into or restored from stack is 4 (MC68010 compatible, not 3 as with the MC68000).

- The RTE instruction decides (with the aid of the 4 format bits) whether or not more information has to be restored as follows:

- The 90CL301 long format is used for bus errors and address error exceptions.

- All other exceptions use the short format.

- If another format code, other than those listed above, is detected during the restored action, a FORMAT ERROR occurs.

If the user wants to finish the instruction in which the bus or address error occurred, the 90CL301 format must be used on RTE. If no changes to the stack are required during exception processing, the stack format is transparent to the user.

## Low voltage 16-bit microcontroller

P90CL301

Table 21 Description of the stack format

| SYMBOL                 | DESCRIPTION                                                                                                      |

|------------------------|------------------------------------------------------------------------------------------------------------------|

| SR                     | Status Register                                                                                                  |

| PCH/PCL                | Program Counter High/Low Word                                                                                    |

| FORMAT                 | Indicating either a short stack (only the first four words), or the long for bus and address error exceptions    |

| BASE VECTOR<br>ADDRESS | The base vector address of the exception in the vector table; e.g. 8 for a bus error and 12 for an address error |

| SSW                    | Special Status Word                                                                                              |

| MM                     | Current Move Multiple Mask                                                                                       |

| TPDH/TPDL              | In the event of faulty write cycle, the data can be found here                                                   |

| TPFH/TPFL              | The address used during the faulty bus cycle                                                                     |

| DBINH/DBINL            | Data that has been read prior to the faulty bus cycle can in some cases be found here                            |

| IR                     | Holds the present instruction executed                                                                           |

| IRC                    | Holds either the present instruction executed or the prefetched instruction                                      |

## Low voltage 16-bit microcontroller

P90CL301

#### 7.6 CPU interrupt processing

The general interrupt handling mechanism is described in Section 6.7. An interrupt controller handles all interrupts, resolves the priority problem and passes the highest level interrupt to the CPU.

The CPU interrupt handling follows the same basic rules as in the MC68000. However, some remarks must be made:

- Interrupts with a priority level equal to or lower than the current priority level will not be accepted.

- During the acknowledge cycle of an interrupt, the IPL bits of the Status Register are set to the priority of the acknowledged interrupt or to 7. An exception occurs when bit IM = 0 (SYSCON bit 5). In this case level 7 is loaded into the Status Register (see Section 6.4; Table 13).

If the priority level of the pending interrupt is greater than the current processor priority then:

- · The exception processing sequence is started.

- · A copy of the Status Register is saved.

- The privilege level is set to Supervisor state.

- · Tracing is suppressed.

- The priority level of the processor is set to that of the interrupt being acknowledged or to 7 depending on the IM flag in the System Control Register.

The processor then gets the vector number from the interrupting device, classifies it as an interrupt acknowledge and displays the interrupt level number being acknowledged on the internal address bus.

As all 90CL301 interrupts are auto-vectored, the processor internally generates a vector number corresponding to the interrupt level number.

The processor starts normal exception processing by saving the format word, program counter and Status Register on the Supervisor stack. The value of the vector in the format word is an internally generated vector number multiplied by 4 (format is all zeros). The program counter value is the address of the instruction that would have been executed if the interrupt had not been present. Then the interrupt vector contents are fetched and loaded into the program counter. The interrupt handling routine starts with normal instruction execution.

#### 7.7 Bus arbitration

If the HALT pin is held LOW with RESET HIGH the CPU will stop after completion of the current bus cycle. As long as HALT is LOW, all control signals are inactive and all tri-state lines are placed in the high-impedance state. If the HALT pin is held LOW during the transfer of a word in 8-bit mode, the CPU will continue the transfer of the two bytes before it halts.

## Low voltage 16-bit microcontroller

P90CL301

#### 8 PORTS

16-bit bidirectional port lines P15 to P0 and 8-bit port lines SP7 to SP0 can be used for general purpose input/output operations. All port pins are multiplexed with other functions, but each one can be individually switched to the port function by setting the corresponding bit in the port control registers PCON for P and SPCON for SP.

The port P7 to P0 is multiplexed with the data bus D15 to D8 and is selected by the pin BSIZE. Each port pin consists of a latch, an output driver with pull-ups and an input buffer.

To use the port as input the port latch should be written with a logic 1. This means only a weak pull-up is on and can be overwritten by an external source logic 0. When outputting a logic 1, a strong pull-up is turned on only for 2 oscillator periods, and then only the weak pull-up maintains the HIGH level. In read mode, two different internal addresses correspond to the port latch or the port pin. The port values are read via register PPL and PPH.

After reset all ports are initialized as input, and the pins are connected to the port latch with exception for the pin NMIN/SP7 which is connected to the interrupt block.

#### 8.1 Port P Control Register (PCON)

The Port P is controlled via the Port Control Register (PCON). The register PCON is only reset by an external reset, and not by the RESET instruction. The port latches are accessed through the registers PRL and PRH.

Table 22 Port Control Register (address FFFF 8503H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| E15 | E14 | E13 | E12 | E11 | E10 | E09 | E08 |

#### Table 23 Description of PCON bits

| BIT    | SYMBOL | FUNCTION                                                                                                                           |

|--------|--------|------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 0 |        | If En = 0, then Portn is enabled; En = 1 then alternate function enabled (n = 08 to 15). The default value after reset is logic 0. |

#### 8.1.1 PORT LATCHES (PRL AND PRH)

#### Table 24 Port Latches

| ADDRESS    | REGISTER | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

|------------|----------|-----|-----|-----|-----|-----|-----|----|----|

| FFFF 8505H | PRL      | P7  | P6  | P5  | P4  | P3  | P2  | P1 | P0 |

| FFFF 8509H | PRH      | P15 | P14 | P13 | P12 | P11 | P10 | P9 | P8 |

#### 8.2 Port SP

The Special Port (SP) includes 8 I/O lines and is controlled via the two registers SPCON and SPR. The registers SPCON and SPR are reset also by a peripheral reset. The port latch is accessed through the register SPR.

### 8.2.1 PORT SP CONTROL REGISTER (SPCON)

### Table 25 Port SP Control Register (FFFF 8109H)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| ES7 | ES6 | ES5 | ES4 | ES3 | ES2 | ES1 | ES0 |

## Low voltage 16-bit microcontroller

P90CL301

Table 26 Description of SPCON bits

| BIT    | SYMBOL     | FUNCTION                                                                                    |

|--------|------------|---------------------------------------------------------------------------------------------|

| 7 to 0 | ES7 to ES0 | If ESn = 0, then Portn is enabled; if ESn = 1, then the alternate function is enabled;      |

|        |            | n = 0 to 7. The default value after reset is logic 0, except for ES7 which is set at reset. |

#### Table 27 SP port latch (FFFF 810BH)

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| SP7 | SP6 | SP5 | SP4 | SP3 | SP2 | SP1 | SP0 |

**Table 28** Alternate functions for P and SP pins Functions within brackets are parallel functions.

| PORT PIN | ALTERNATE FUNCTION |

|----------|--------------------|

| P0       | D8                 |

| P1       | D9                 |

| P2       | D10                |

| P3       | D11                |

| P4       | D12                |

| P5       | D13                |

| P6       | D14                |

| P7       | D15                |

| P8       | PWM0 (CP0)         |

| P9       | PWM1 (CP1)         |

| P10      | SCL                |

| P11      | SDA                |

| P12      | ADC0               |

| P13      | ADC1               |

| P14      | ADC2               |

| P15      | ADC3               |

| SP0      | RX1/INT0           |

| SP1      | TX1/INT1 (CLK0)    |

| SP2      | RX0/INT2 (CP2)     |

| SP3      | TX0/INT3 (CP3)     |

| SP4      | ĪNT4 (CP4)         |

| SP5      | INT5 (CP5)         |

| SP6      | INT6 (CLK1)        |

| SP7      | NMIN               |

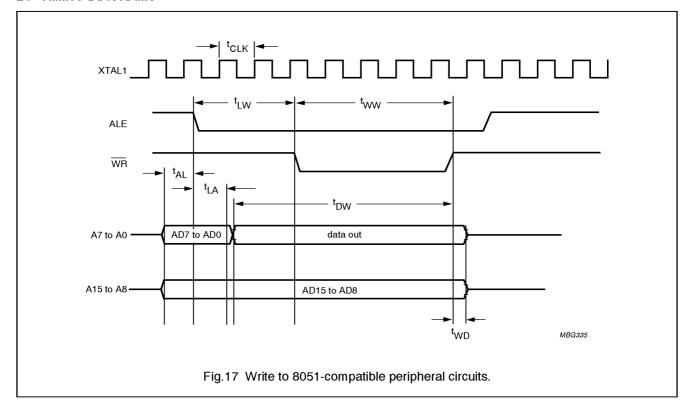

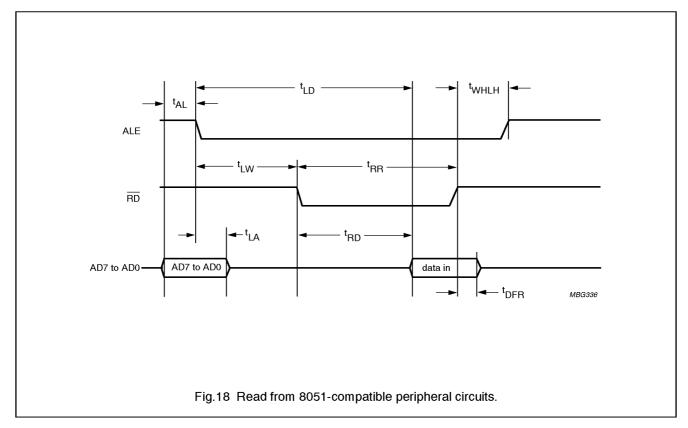

#### 9 8051 PERIPHERAL BUS

The P90CL301 can also directly access the peripheral circuits which are compatible with the 8048/8051 bus.

When the CPU accesses locations placed in the 64 kbytes peripheral space, an Address/Data multiplexed access is generated using the AD0 to AD7 lines, the non-multiplexed A8 to A15 lines and the 8051 control bus (ALE, RD, WR). In order to use these three signals the alternate mode of the CS5 to CS3 should be set. A 8051 bus access is performed by addressing a byte in the 8001 0000H to 8001 FFFFH range. To reduce the number of interface circuits, the address lines A22 to A19 can be used as peripheral chip-select outputs PCS0 to PCS3. This is done by setting the PDE bit (SYSCON) to a logic 1;

- PCS0 selects memory range 0 kbytes to 16 kbytes

- PCS1 selects memory range 16 kbytes to 32 kbytes

- PCS2 selects memory range 32 kbytes to 48 kbytes

- PCS3 selects memory range 48 kbytes to 64 kbytes.

The timing of the peripheral bus is fixed and compatible with the 8051 peripheral circuits.

## Low voltage 16-bit microcontroller

P90CL301

#### 10 ON-CHIP PERIPHERAL FUNCTIONS

The P90CL301 integrates a number of peripheral functions connected to the internal bus:

- · Timers (T0 and T1)

- · Watchdog

- UART interface

- I<sup>2</sup>C-bus interface

- · PWM (Pulse Width Modulation)

- ADC (analog-to-digital converter).

These functions are accessible as memory locations on a byte or word basis. The access is auto-acknowledged by on-chip logic. The on-chip peripheral functions can generate auto-vectored interrupts to the CPU using the second vector table (vectors 57 to 63).

### 10.1 Peripheral interrupt control

The timers T0 and T1, I<sup>2</sup>C-bus, UART and ADC use a common set of Peripheral Interrupt Control Registers (PICR). These registers are accessible from the CPU and contain the interrupt priority level IPL2 to IPL0 as well as the pending interrupt flags PIR.

PIR is set when a valid interrupt request has been detected. It is automatically reset by the interrupt acknowledge cycle from the CPU. The PIR flag can be reset by software.

The code 111 in IPL represents the interrupt with the highest priority. The code 000 inhibits the interrupt.

#### 10.1.1 TIMER INTERRUPT REGISTER (PICRO)

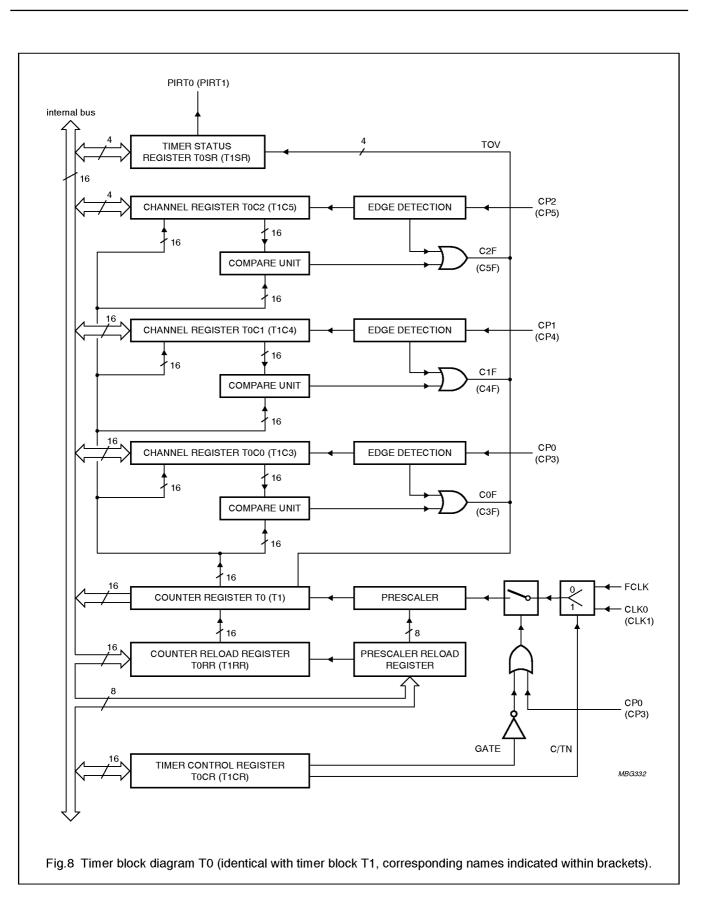

On timer overflow or on channel capture/match the pending interrupt request flag PIRTn is set. If the interrupt priority level is different from zero, the timer activates an interrupt to the CPU.

Table 29 Timer Interrupt Register (address FFFF 8701H)

| 7     | 6       | 5       | 4       | 3     | 2       | 1       | 0       |

|-------|---------|---------|---------|-------|---------|---------|---------|

| PIRT1 | IPLT1.2 | IPLT1.1 | IPLT1.0 | PIRT0 | IPLT0.2 | IPLT0.1 | IPLT0.0 |

Table 30 Description of PICR0 bits

| BIT    | SYMBOL             | FUNCTION                                                 |  |  |  |  |

|--------|--------------------|----------------------------------------------------------|--|--|--|--|

| 7      | PIRT1              | pending interrupt for timer T1                           |  |  |  |  |

| 6 to 4 | IPLT2.2 to IPLT1.0 | IPLT2.2 to IPLT1.0 interrupt priority level for timer T1 |  |  |  |  |

| 3      | PIRT0              | pending interrupt for timer T0                           |  |  |  |  |

| 2 to 0 | IPLT0.2 to IPLT0.0 | interrupt priority level for timer T0                    |  |  |  |  |

## Low voltage 16-bit microcontroller

P90CL301

### 10.1.2 UART INTERRUPT REGISTERS

Each UART can generate two interrupts in transmission and reception via the two registers PICR1 and PICR2.

### Table 31 UART Interrupt Registers PICR1 and PICR2

| ADDRESS    | REGISTER | 7     | 6       | 5       | 4       | 3     | 2       | 1       | 0       |

|------------|----------|-------|---------|---------|---------|-------|---------|---------|---------|

| FFFF 8703H | PICR1    | PIRR0 | IPLR0.2 | IPLR0.1 | IPLR0.0 | PIRT0 | IPLT0.2 | IPLT0.1 | IPLT0.0 |

| FFFF 8705H | PICR2    | PIRR1 | IPLR1.2 | IPLR1.2 | IPLR1.2 | PIRT1 | IPLT1.2 | IPLT1.1 | IPLT1.0 |

### **Table 32** Description of PICR1 and PICR2 register bits; n = 0 to 1.

| BIT    | SYMBOL             | FUNCTION                                           |

|--------|--------------------|----------------------------------------------------|

| 7      | PIRRn              | pending interrupt for UARTn in reception           |

| 6 to 4 | IPLRn.2 to IPLRn.0 | interrupt priority level for UARTn in reception    |

| 3      | PIRTn              | pending interrupt for UARTn in transmission        |

| 2 to 0 | IPLTn.2 to IPLTn.0 | interrupt priority level for UARTn in transmission |

### 10.1.3 I<sup>2</sup>C AND ADC INTERRUPT REGISTER (PICR3)

The I<sup>2</sup>C and the ADC can each generate one interrupt.

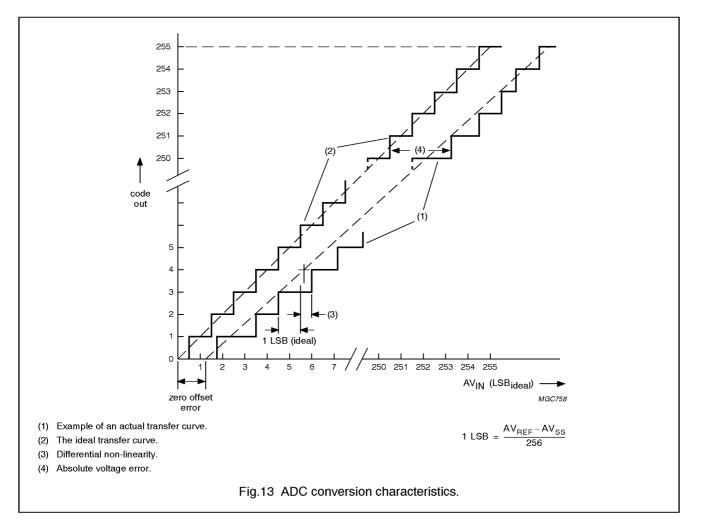

### Table 33 I<sup>2</sup>C and ADC Interrupt Register (address FFFF 8707H)