## General Description

The MXD1013 contains three independent, monolithic, logic-buffered delay lines with delays ranging from 10ns to 200ns. Nominal accuracy is ±2ns for a 10ns to 60ns delay, ±3% for a 70ns to 100ns delay, and ±5% for a 150ns to 200ns delay. Relative to hybrid solutions, these devices offer enhanced performance and higher reliability, and reduce overall cost. Each output can drive up to ten standard 74LS loads.

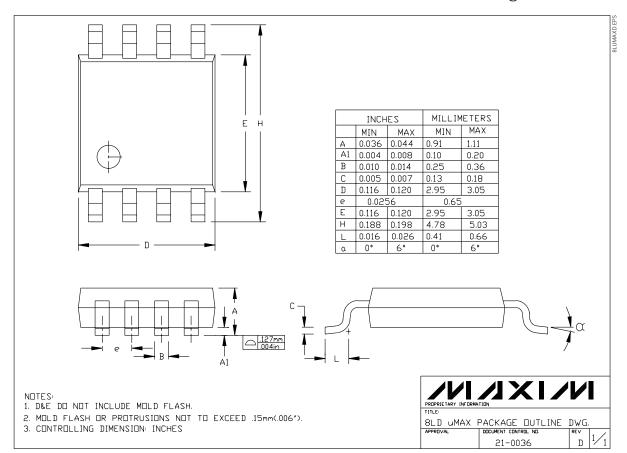

The MXD1013 is available in multiple versions, each offering a different combination of delay times. It comes in the space-saving 8-pin µMAX package, as well as a standard 8-pin SO and DIP. It is also offered in industry-standard 16-pin SO and 14-pin DIP packaging, allowing full compatibility with the DS1013 and other delay-line products.

**Applications**

Clock Synchronization Digital Systems

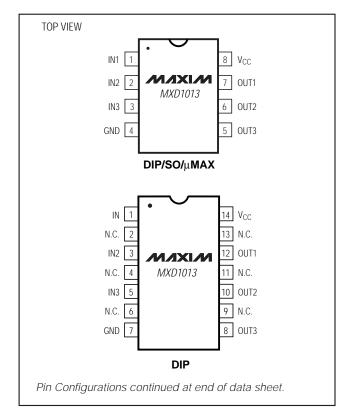

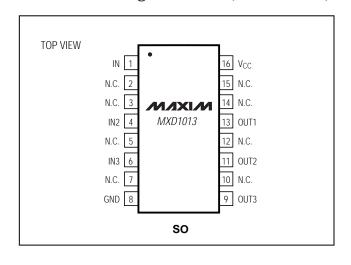

## Pin Configurations

#### **Features**

- **♦ Improved Second Source to DS1013**

- ♦ Available in Space-Saving 8-Pin µMAX Package

- ◆ 20mA Supply Current (vs. Dallas' 40mA)

- **♦ Low Cost**

- **♦ Three Separate Buffered Delays**

- ♦ Delay Tolerance of ±2ns for MXD1013 010 through MXD1013 060

- **♦ TTL/CMOS-Compatible Logic**

- ♦ Leading- and Trailing-Edge Accuracy

- ♦ Custom Delays Available

## Ordering Information

| PART       | TEMP. RANGE    | PIN-PACKAGE    |

|------------|----------------|----------------|

| MXD1013C/D | 0°C to +70°C   | Dice*          |

| MXD1013PA  | -40°C to +85°C | 8 Plastic DIP  |

| MXD1013PD  | -40°C to +85°C | 14 Plastic DIP |

| MXD1013SA  | -40°C to +85°C | 8 SO           |

| MXD1013SE  | -40°C to +85°C | 16 Narrow SO   |

| MXD1013UA  | -40°C to +85°C | 8 µMAX         |

<sup>\*</sup>Dice are tested at  $T_A = +25$ °C.

**Note:** To complete the ordering information, fill in the blank with the part number extension from the Part Numbers and Delay Times table to indicate the desired delay per output.

## Part Numbers and Delay Times

| PART NUMBER<br>EXTENSION<br>(MXD1013) | OUTPUT<br>DELAY<br>(ns) | PART NUMBER<br>EXTENSION<br>(MXD1013) | OUTPUT<br>DELAY<br>(ns) |

|---------------------------------------|-------------------------|---------------------------------------|-------------------------|

| 010                                   | 10                      | 050                                   | 50                      |

| 012                                   | 12                      | 060                                   | 60                      |

| 015                                   | 15                      | 070                                   | 70                      |

| 020                                   | 20                      | 075                                   | 75                      |

| 025                                   | 25                      | 080                                   | 80                      |

| 030                                   | 30                      | 090                                   | 90                      |

| 035                                   | 35                      | 100                                   | 100                     |

| 040                                   | 40                      | 150                                   | 150                     |

| 045                                   | 45                      | 200                                   | 200                     |

Functional Diagram appears at end of data sheet.

NIXIN

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| 14-Pin Plastic DIP (derate 10.0mW/°C above +70°C)800mW Lead Temperature (soldering, 10sec)+3 | All Other Pins0.5V to $(V_{CC} + 0.5V)$ 16-Short-Circuit Output Current (1sec) | Pin SO (derate 5.9mW/°C above +70°C) |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------|

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|--------------------------------------|

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +5.0V \pm 5\%, T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C.)$  (Note 1)

| PARAMETER             | SYMBOL | CONDITIONS                                         | MIN  | TYP  | MAX  | UNITS |

|-----------------------|--------|----------------------------------------------------|------|------|------|-------|

| Supply Voltage        | Vcc    | (Note 2)                                           | 4.75 | 5.00 | 5.25 | V     |

| Input Voltage High    | VIH    | (Note 2)                                           | 2.2  |      |      | V     |

| Input Voltage Low     | VIL    | (Note 2)                                           |      |      | 0.8  | V     |

| Input Leakage Current | IL     | OV ≤ V <sub>IN</sub> ≤ V <sub>CC</sub>             | -1   |      | 1    | μΑ    |

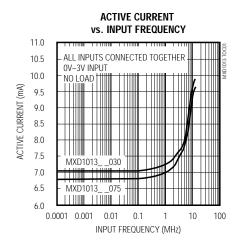

| Active Current        | Icc    | V <sub>CC</sub> = 5.25V, period = minimum (Note 3) |      | 20   | 70   | mA    |

| Output Current High   | Іон    | V <sub>CC</sub> = 4.75V, V <sub>OH</sub> = 4.0V    |      |      | -1   | mA    |

| Output Current Low    | loL    | VCC = 4.75V, V <sub>OL</sub> = 0.5V                |      |      |      | mA    |

| Input Capacitance     | CIN    | $T_A = +25$ °C (Note 4)                            |      | 5    | 10   | pF    |

#### TIMING CHARACTERISTICS

$(V_{CC} = +5.0V \pm 5\%, T_A = +25^{\circ}C, unless otherwise noted.)$

| PARAMETER                             | SYMBOL           | CONDITIONS      | MIN                 | TYP                                    | MAX | UNITS |

|---------------------------------------|------------------|-----------------|---------------------|----------------------------------------|-----|-------|

| Input Pulse Width                     | twı              | (Note 5)        | 100% of tplh        |                                        |     | ns    |

| Input-to-Output Delay (leading edge)  | tPLH             | (Notes 6, 7, 8) |                     | e Part Number and<br>Delay Times table |     | ns    |

| Input-to-Output Delay (trailing edge) | t <sub>PHL</sub> | (Notes 6, 7, 8) |                     | e Part Number and<br>Delay Times table |     | ns    |

| Power-Up Time                         | tpu              |                 |                     |                                        | 100 | ms    |

| Period                                |                  | (Note 5)        | 3(t <sub>WI</sub> ) |                                        |     | ns    |

- Note 1: Specifications to -40°C are guaranteed by design, not production tested.

- Note 2: All voltages referenced to GND.

- **Note 3:** Measured with outputs open.

- Note 4: Guaranteed by design.

- Note 5: Pulse width and/or period specifications may be exceeded, but accuracy is application sensitive (i.e., layout, decoupling, etc.).

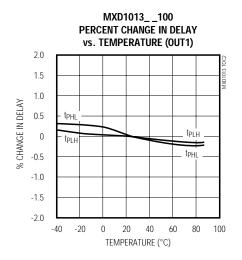

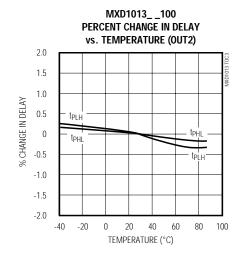

- **Note 6:**  $V_{CC} = +5V$  at  $+25^{\circ}C$ . Typical delays are accurate on both rising and falling edges within  $\pm 2$ ns for delays from 10ns to 60ns, within  $\pm 3\%$  for delays from 70ns to 100ns, and within  $\pm 5\%$  for delays from 150ns to 200ns.

- Note 7: The Part Number and Delay Times table provides typical delays at +25°C with V<sub>CC</sub> = +5V. The delays may shift with temperature and supply variations. The combination of temperature (from +25°C to 0°C, or +25°C to +70°C) and supply variation (from 5V to 4.75V, or 5V to 5.25V) could produce an additional typical delay of ±1.5ns or ±3%, whichever is greater.

- **Note 8:** All output delays tend to vary unidirectionally with temperature or supply voltage variations (i.e., if OUT1 slows down, all other outputs also slow down).

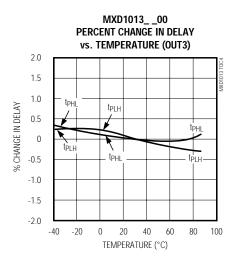

Typical Operating Characteristics

$(V_{CC} = +5V, T_A = +25^{\circ}C, unless otherwise noted.)$

Pin Description

|                      | PIN                   |                               |                  |                          |

|----------------------|-----------------------|-------------------------------|------------------|--------------------------|

| 8-PIN<br>DIP/SO/µMAX | 14-PIN DIP            | 16-PIN SO                     | NAME             | FUNCTION                 |

| 1                    | 1                     | 1                             | IN1              | First Independent Input  |

| 2                    | 3                     | 4                             | IN2              | Second Independent Input |

| 3                    | 5                     | 6                             | IN3              | Third Independent Input  |

| 4                    | 7                     | 8                             | GND              | Device Ground            |

| 5                    | 8                     | 9                             | OUT3             | Third Delayed Output     |

| 6                    | 10                    | 11                            | OUT2             | Second Delayed Output    |

| 7                    | 12                    | 13                            | OUT1             | First Delayed Output     |

| 8                    | 14                    | 16                            | V <sub>C</sub> C | Power-Supply Input       |

| _                    | 2, 4, 6, 9, 11,<br>13 | 2, 3, 5, 7, 10,<br>12, 14, 15 | N.C.             | Not Connected            |

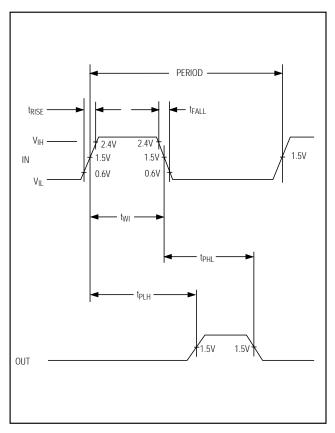

#### **Definitions of Terms**

**Period:** The time elapsed between the first pulse's leading edge and the following pulse's leading edge.

**Pulse Width (twi):** The time elapsed on the pulse between the 1.5V level on the leading edge and the 1.5V level on the trailing edge, or vice versa.

**Input Rise Time (trise):** The elapsed time between the 20% and 80% points on the input pulse's leading edge.

**Input Fall Time (tFALL):** The time elapsed between the 80% and 20% points on the input pulse's trailing edge.

**Time Delay, Rising (tplh):** The time elapsed between the 1.5V level on the input pulse's leading edge and the corresponding output pulse's leading edge.

**Time Delay, Falling (tPHL):** The time elapsed between the 1.5V level on the input pulse's trailing edge and the corresponding output pulse's trailing edge.

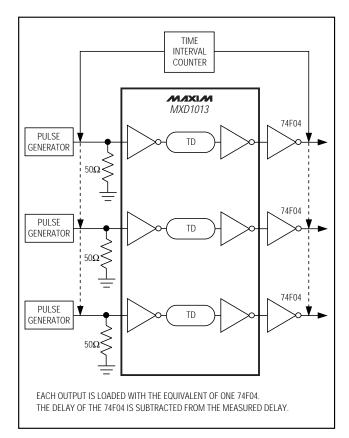

## Test Conditions

Ambient Temperature: +25°C Supply Voltage (V<sub>CC</sub>): 5.0V ±0.1V

Input Pulse: High =  $3.0V \pm 0.1V$

$Low = 0.0V \pm 0.1V$

Source Impedance:  $50\Omega$  max

Rise and Fall Times: 3.0ns max

Pulse Width: 500ns max

Period: 1µs

Each output is loaded with a 74F04 input gate. Delay is measured at the 1.5V level on the rising and falling edges. The time delay due to the 74F04 is subtracted from the measured delay.

Figure 1. Timing Diagram

Figure 2. Test Circuit

## Applications Information

#### Supply and Temperature Effects on Delay

Over the specified range, the MXD1013's delays are typically 2% accurate. Variations in supply voltage may affect the MXD1013's fixed output delays. Supply voltages beyond the specified range may result with larger variations. Although there might be a slight variance in delays over temperature, the MXD1013 is internally compensated to maintain its nominal values.

#### Loading Effect on Delay Lines

Capacitive loads increase delay times as they increase the rise and fall times of the delay lines. Other logic devices increase the capacitance at the output of the delays, which can affect device performance.

#### **Board Layout Considerations**

Bypass the MXD1013 with a  $0.1\mu F$  capacitor to minimize the impact of high-speed switching on the power supply. The power supply must be able to deliver the required switching currents for proper operation.

It is advisable to minimize trace lengths in order to reduce board capacitance as well as the traveling distance between devices. Sockets and wire-wrapped boards increase capacitance and should be avoided.

\_\_\_\_\_Chip Information

TRANSISTOR COUNT: 824

## \_\_Pin Configurations (continued)

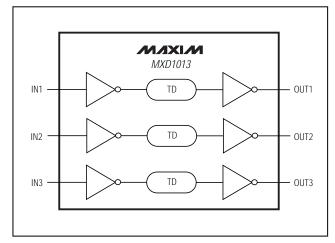

## \_Functional Diagram

Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

6 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600