DS3106 2.5

# **MV1820**

## VIDEO PROGRAMME DELIVERY CONTROL INTERFACE CIRCUIT

(Supersedes version in April 1994 Consumer IC Handbook, HB3120 - 2.0)

The MV1820 is a high speed CMOS receiver for Programme Delivery Control (PDC) messages broadcast in World System Teletext (WST) Format Two Broadcast Service Data Packets (BSDP). The PDC message can be read on an I<sup>2</sup>C bus with data format similar to standard Video Programming Service (VPS) decoders. Additional data is appended to include new PDC features.

It is intended for use in Video Cassette Recorders to provide automatic recording of suitably labelled Television programmes requested by the user.

#### **FEATURES**

- On chip data slicing

- Low external component count

- I<sup>2</sup>C bus for low cost interfacing

- Advanced CMOS technology gives low power dissipation and high reliability

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage        | 0.3V to 7V                    |

|-----------------------|-------------------------------|

| All inputs            | -0.3 to V <sub>DD</sub> +0.3V |

| Operating temperature | 0 to +70°C                    |

| Storage temperature   | -55 to 125°C                  |

|                       |                               |

#### ORDERING INFORMATION

MV1820E/CG/DPAS MV1820E/CG/MPES

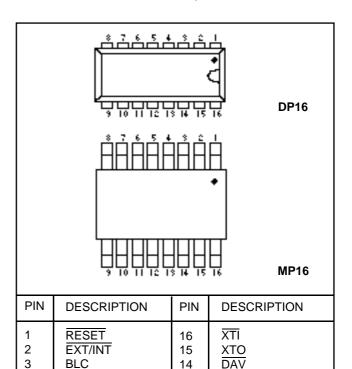

Fig.1 Pin connections - top view

13

12

11

10

SDA

**VDD**

SCL

SYNC I/O

DATA I/O

4

5

6

7

8

**WLC**

**GND**

**TCR**

AS

**VIDEO**

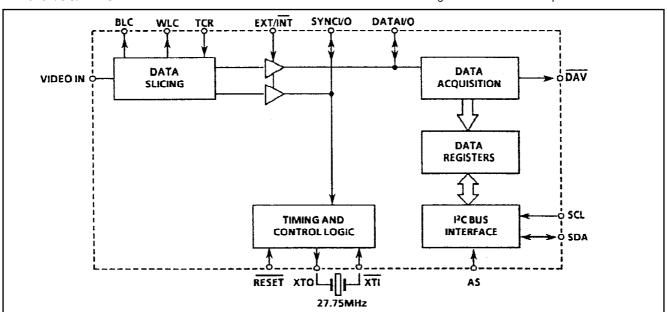

Fig.2 MV1820 block diagram

## MV1820

## **ELECTRICAL CHARACTERISTICS**

These characteristics are guaranteed over the following conditions (unless otherwise stated)  $T_{amb}$  = 0 to 70°C,  $V_{DD}$  = 5V  $\pm$  10%

|                             |        | Value                |        |      |       |                                                  |

|-----------------------------|--------|----------------------|--------|------|-------|--------------------------------------------------|

| Characteristic              | Pin    | Min                  | Тур    | Max  | Units | Conditions                                       |

| Supply voltage              | 12     | 4.5                  | 5.0    | 5.5  | V     |                                                  |

| Supply current              | 12     |                      | 20     | 25   | mA    |                                                  |

| Video input                 | 5      |                      |        |      |       |                                                  |

| Video amplitude             |        | 0.8                  |        | 3.0  | Vpp   | Bottom of sync to white (pk to pk)               |

| Source impedance            |        |                      |        | 250  |       |                                                  |

| TCR input                   | 7      |                      |        |      |       |                                                  |

| External resistance         |        | 4.7                  | 4.7    | 200  | k     | Connected to VDD                                 |

| BLC and WLC                 | 3 & 4  |                      |        |      |       |                                                  |

| Capacitor value             |        |                      | 10     |      | nF    | Connected to GND                                 |

| Capacitor tolerance         |        | -10%                 |        | +10% |       |                                                  |

| Effective series resistance |        |                      |        | 5    |       | 1MHz                                             |

| DATA I/O and SYNC I/O       | 9 & 10 |                      |        |      |       |                                                  |

| Output voltage High         |        | VDD-1.0              | 4.5    |      | V     | Iон = -1.2mA                                     |

| Output voltage Low          |        |                      | 0.2    | 0.4  | V     | IoL = 2.4mA                                      |

| Input voltage Low           |        | 0                    |        | 0.8  | V     |                                                  |

| Input voltage High          |        | V <sub>DD</sub> -1.0 |        | Vdd  | V     |                                                  |

| Input current               |        | -30                  |        | +30  | μΑ    | VIN = Vss or VDD                                 |

| EXT/INT                     | 2      |                      |        |      |       | 100k (nom) pull-down resistor                    |

| Input voltage Low           |        | 0                    |        | 0.8  | V     |                                                  |

| Input voltage High          |        | V <sub>DD</sub> -1.0 |        | Vdd  | V     |                                                  |

| Input current Low           |        | -10                  |        | +10  | μΑ    | VIN = Vss                                        |

| Input current High          |        | 22                   | 50     | 220  | μΑ    | VIN = VDD                                        |

| AS                          | 8      |                      |        |      |       | 100k (nom) pull-down resistor                    |

| Input voltage Low           |        | 0                    |        | 1.0  | V     |                                                  |

| Input voltage High          |        | V <sub>DD</sub> -1.0 |        | Vdd  | V     |                                                  |

| Input current Low           |        | -10                  |        | +10  | μΑ    | VIN = VSS                                        |

| Input current High          |        | 22                   | 50     | 220  | μΑ    | VIN = VDD                                        |

| XTI Input                   | 16     |                      |        |      |       |                                                  |

| Input current Low           |        | -0.5                 | -5.0   | -20  | μΑ    | -0.3 <vin<vil max<="" td=""></vin<vil>           |

| Input current High          |        | 0.5                  | 5.0    | 20   | μΑ    | Vihmin <vin<(vdd +="" 0.3)<="" td=""></vin<(vdd> |

| XTO Output                  | 15     |                      |        |      |       |                                                  |

| Output voltage High         |        | VDD-1.0              | 4.5    |      | V     | Iон = -1.0mA                                     |

| Output voltage Low          |        |                      | 0.2    | 0.4  | V     | lo <sub>L</sub> = 2.0mA                          |

| Frequency                   |        |                      | 27.750 |      | MHz   | ±100ppm                                          |

## **ELECTRICAL CHARACTERISTICS (continued)**

These characteristics are guaranteed over the following conditions (unless otherwise stated)  $T_{amb} = 0$  to  $70^{\circ}C$ ,  $V_{DD} = 5V \pm 10\%$

| Characteristic          | Pin    | Value   |     | Units | Conditions |                                |  |

|-------------------------|--------|---------|-----|-------|------------|--------------------------------|--|

| Characteristic          |        | Min     | Тур | Max   | Units      | Conditions                     |  |

| I2C bus                 |        |         |     |       |            |                                |  |

| SCL, SDA Schmitt inputs | 11, 13 |         |     |       |            | Not clamped when $V_{DD} = 0V$ |  |

| Input voltage Low       |        | 0       |     | 1.5   | V          |                                |  |

| Input voltage High      |        | 3.5     |     | VDD   | V          |                                |  |

| Output voltage Low      |        |         | 0.1 | 0.4   | V          | IoL = 3.0mA                    |  |

| SCL clock frequency     | 11     |         | 100 | 1000  | kHz        |                                |  |

| DAV data available      |        |         |     |       |            | 100k (nom) pull-up resistor    |  |

| Output voltage low      |        |         | 0.2 | 0.4   | V          | Iон = 2.4mA                    |  |

| RESET Schmitt input     | 1      |         |     |       |            | 100k (nom) pull-up resistor    |  |

| Input voltage Low       |        | 0       |     | 0.8   | V          |                                |  |

| Input voltage High      |        | VDD-1.0 |     | Vdd   | V          |                                |  |

| Input current Low       |        | -22     | -50 | -220  | μΑ         | Vin = Vss                      |  |

| Input current High      |        | -10     |     | +10   | μΑ         | VIN = VDD                      |  |

## NOTE

Input voltage low and input voltage high for  $\overline{\text{EXT/INT}}$ , AS and  $\overline{\text{XTI}}$  are as specified for DATA I/O.

| PIN DESCRIPTION |     |                                                                                                                                                                                                                                                        |

|-----------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol          | Pin | Pin Name and Description                                                                                                                                                                                                                               |

| RESET           | 1   | Active Low Reset. Includes a 100k pull - up resistor                                                                                                                                                                                                   |

| EXT/INT         | 2   | Control Pin for SYNC I/O and DATA I/O. Includes a 100k pull - down resistor. When low or not connected, internal SYNC and DATA are used, pins 9 and 10 are outputs. When high, supply SYNC and DATA from an external source, pins 9 and 10 are inputs. |

| BLC             | 3   | Black level capacitor.                                                                                                                                                                                                                                 |

| WLC             | 4   | White level capacitor.                                                                                                                                                                                                                                 |

| VIDEO           | 5   | Input for composite video signal with negative going syncs                                                                                                                                                                                             |

| GND             | 6   | Ground 0 volts.                                                                                                                                                                                                                                        |

| TCR             | 7   | <b>Time constant resistor.</b> Controlling discharge rate of black and white level capacitor voltages.                                                                                                                                                 |

| AS              | 8   | Address select for I <sup>2</sup> C bus. [0010 0001] with AS set high, or [0010 0011] with AS set low. Includes 100k pull - down resistor.                                                                                                             |

| DATA I/O        | 9   | Data input/output.                                                                                                                                                                                                                                     |

| SYNC I/O        | 10  | Sync input/output.                                                                                                                                                                                                                                     |

| SCL             | 11  | I <sup>2</sup> C bus serial clock.                                                                                                                                                                                                                     |

| VDD             | 12  | Positive supply voltage +5V ± 10%                                                                                                                                                                                                                      |

| SDA             | 13  | I <sup>2</sup> C bus bi-directional data port.                                                                                                                                                                                                         |

| DAV             | 14  | Active low open drain output data available signal to microprocessor. Includes 100k pull - up resistor                                                                                                                                                 |

| XTO             | 15  | Crystal out, 27.75MHz fundamental crystal with on-chip 1M resistor to XTI.                                                                                                                                                                             |

| XTI             | 16  | Crystal input.                                                                                                                                                                                                                                         |

#### **CRYSTAL SPECIFICATION**

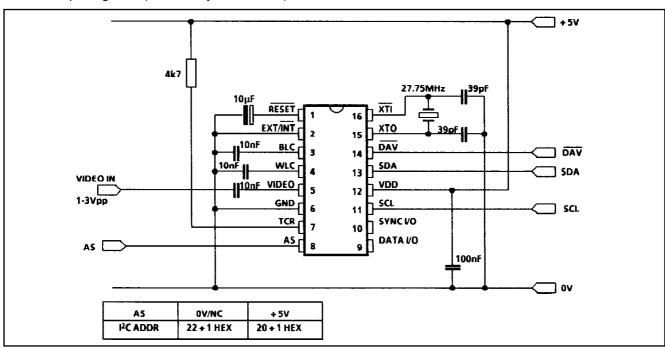

Parallel resonant fundamental frequency 27.750000MHz. AT cut. Tolerance at -10 $^{\circ}$ C to 60 $^{\circ}$ C ± 50ppm. Tolerance overall ± 100ppm.

Nominal load capacitance 20pF. Equivalent series resistance <20 .

#### **FUNCTIONAL DESCRIPTION**

The video signal is sliced to produce data and synchronising signals. Timing circuits monitor the sync signal to enable the MV1820 to lock onto the broadcast signal. A timing window, for the Vertical Blanking Interval (VBI) lines 6 - 22 and 318 - 335, is established to enable the acquisition circuit to monitor the sliced data signal for valid teletext data.

The framing code is checked for valid World System Teletext (WST) data. Magazine, packet and designation code bytes are checked and valid Broadcast Service Data Packets (BSDP) format two type only are accepted. These are known as packet 8/30. Format two is signalled by byte six, data bit two being set high and bits 3 and 4 set low. Bytes 13 to 25 inclusive are Hamming decoded (8,4) and stored in seven registers each of eight bits. If the complete message is correctly received with no uncorrectable Hamming errors, an interrupt to the microprocessor is signalled by the DAV (bar) pin going low. At the same time the data is transferred to a second bank of registers, reorganised with original numbered bytes 14, 15, 24, 25 and 13 placed after byte 23, to be read out on the PC bus when so requested. Subsequent valid messages will continue to be transferred to the output registers overwriting any existing data. In this way the output registers always contain the latest PDC message.

The MV1820 is configured as an  $I^2C$  bus slave transmitter with a selectable address. The  $I^2C$  bus address is 0010 0001 (20 + 1 hex) with the address select (AS) pin set high, or 0010 0011 (22 + 1 hex) with the AS pin set low. The read bit (LSB) must always be set, it is not possible to write to the MV1820.

On recognising its address, the MV1820 will send an acknowledge and then transmit on the SDA line the first byte from the output registers (decoded byte 16 and 17) most

significant bit (MSB) first. It will then monitor the SDA line for an acknowledge from the microprocessor. If the microprocessor does NOT send an acknowledge, the MV1820 will release the data line to allow the microprocessor to send a stop condition. If the microprocessor does send an acknowledge, the following bytes of the message will be output provided each byte is acknowledged. The final data will be byte 13 followed by the four '1's.

When readout is complete, the DAV (bar) pin is reset high and the output registers are all set high. If the microprocessor continues to send clocks on the SCL line, the MV1820 will output FF bytes on the SDA line. Also, if the MV1820 is readdressed before another PDC message is received, the MV1820 will output FF bytes on the SDA line. The microprocessor can prematurely stop the message by NOT sending an Acknowledge followed by a STOP condition after any byte has been sent by the MV1820. The registers will then be reset to FF bytes and the DAV pin will be reset high.

To prevent any corruption of the data in the output registers during  $I^2C$  bus activity, valid PDC messages are held in the incoming registers until  $I^2C$  bus activity ceases. Here they may be overwritten by new PDC messages until the  $I^2C$  bus activity ceases and they can then be transferred to the output registers.

System clock is provided by an on - chip 27.75MHz oscillator together with an external parallel resonant fundamental frequency AT cut crystal.

Following a reset, RESET pulled low, the output I<sup>2</sup>C bus registers will contain FF bytes and the DAV pin will be set high. When the power supply is removed, the I<sup>2</sup>C bus will not be clamped to ground, leaving it free for other I<sup>2</sup>C bus traffic.

Fig.3 Typical application diagram

## ORDER OF DATA OUTPUT ON THE I2C BUS

| Bit Ord            | ler            | EBU Nu  | mbering             | Bit       | Value                                 | VPS Equivalence |

|--------------------|----------------|---------|---------------------|-----------|---------------------------------------|-----------------|

| byte 1             | bit 7          | byte 16 | bit 0 - CNI b9      |           | _reserved                             | [byte 11        |

|                    | bit 6          |         | bit 1 - CNI b10     | <u>64</u> | _network (or programme provide        | r) l            |

|                    | bit 5          |         | bit 2 - PIL b1      | 16        |                                       | i               |

|                    | bit 4          |         | bit 3 - PIL b2      | 8         |                                       | İ               |

|                    | bit 3          | byte 17 | bit 0 - PIL b3      | 4         | day                                   | İ               |

|                    | bit 2          |         | bit 1 - PIL b4      | 2         |                                       | 1               |

|                    | bit 1          |         | bit 2 - PIL b5      | 1         |                                       | 1               |

|                    | bit 0          |         | bit 3 - PIL b6      | 8         | -                                     | ſ               |

| byte 2             | bit 7          | byte 18 | =<br>bit 0 - PIL b7 | 4         |                                       | = [ byte 12     |

| •                  | bit 6          | •       | bit 1 - PIL b8      | 2         | month                                 | 1               |

|                    | bit 5          |         | bit 2 - PIL b9      | 1         |                                       | 1               |

|                    | bit 4          |         | bit 3 - PIL b10     | 16        | =                                     | i               |

|                    | bit 3          | byte 19 | bit 0 - PIL b11     | 8         |                                       | ·               |

|                    | bit 2          | 5,10 15 | bit 1 - PIL b12     | 4         | hour                                  | 1               |

|                    | bit 1          |         | bit 2 - PIL b13     | 2         | noui                                  |                 |

|                    | bit 0          |         | bit 3 - PIL b14     | 1         |                                       | ſ               |

| byte 3             | bit 7          | byte 20 | bit 0 - PIL b15     | 32        |                                       | _ l<br>[buto 19 |

| Dyte 3             | bit 6          | Dyle 20 |                     | 16        |                                       | [byte 13        |

|                    | bit 5          |         | bit 1 - PIL b16     |           |                                       | •               |

|                    |                |         | bit 2 - PIL b17     | 8         | anta da                               | 1               |

|                    | bit 4          | b 4 04  | bit 3 - PIL b18     | 4         | minute                                | !               |

|                    | bit 3          | byte 21 | bit 0 - PIL b19     | 2         |                                       |                 |

|                    | bit 2          |         | bit 1 - PIL b20     | 1         | _                                     | !               |

|                    | bit 1          |         | bit 2 - CNI b5      | 8         |                                       | -               |

|                    | bit 0          |         | _bit 3 - CNI b6     | 4         |                                       | <b>_</b> [      |

| byt <del>e</del> 4 | bit 7          | byte 22 | bit 0 - CNI b7      | 2         | country                               | [ byte 14       |

|                    | bit 6          |         | bit 1 - CNI b8      | 1         | <del></del> -                         | l               |

|                    | bit 5          |         | bit 2 - CNI b11     | 32        |                                       |                 |

|                    | bit 4          |         | bit 3 - CNI b12     | 16        |                                       | l               |

|                    | bit 3          | byte 23 | bit 0 - CNI b13     | 8         | network (or programme provide         | r) l            |

|                    | bit 2          |         | bit 1 - CNI b14     | 4         |                                       | I               |

|                    | bit 1          |         | bit 2 - CNI b15     | 2         |                                       | 1               |

|                    | bit 0          |         | _bit 3 - CNI b16    | 1         |                                       | _ [             |

| byte 5             | bit 7          | byte 14 | bit 0 - PCS b1      | 2         | status (define the analog sound       | [ byte 5        |

|                    | bit 6          |         | bit 1 - PCS b2      | 1         | transmission system)                  | 1               |

|                    | bit 5          |         | bit 2 - unallocated |           |                                       | I               |

|                    | bit 4          |         | bit 3 - unallocated |           | _                                     | ı               |

|                    | bit 3          | byte 15 | bit 0 - CNI b1      | 128       | l .                                   | 1               |

|                    | bit 2          |         | bit 1 - CNI b2      | 64        |                                       | ı               |

|                    | bit 1          |         | bit 2 - CNI b3      | 32        | country                               | 1               |

|                    | bit 0          |         | bit 3 - CNI b4      | 16        | •                                     | ſ               |

| byte 6             | bit 7          | byte 24 | bit 0 - PTY b1      | 128       |                                       | [byte 15        |

| •                  | bit 6          | •       | bit 1 - PTY b2      | 64        |                                       | 1               |

|                    | bit 5          |         | bit 2 - PTY b3      | 32        |                                       | 1               |

|                    | bit 4          |         | bit 3 - PTY b4      | 16        | programme type                        | i               |

|                    | bit 3          | byte 25 | bit 0 - PTY b5      | 8         | programme type                        | i               |

|                    | bit 2          | 2,13 =0 | bit 1 - PTY b6      | 4         |                                       | ·               |

|                    | bit 1          |         | bit 2 - PTY b7      | 2         |                                       |                 |

|                    | bit 0          |         | _bit 3 - PTY b8     | 1         |                                       | ·               |

| byte 7             | bit 0<br>bit 7 | byte 13 | bit 0 - LCl b1      | 2         | Label Channel Identifier              | = '             |

| Dy 10 1            | bit 6          | Dylo 10 | bit 1 - LCI b2      | 1         | _Interleave up to four PIL messa      | 290             |

|                    |                |         |                     | 1         | <del></del> ''                        | นิดจ            |

|                    | bit 5          |         | bit 2 - LUF         | <u> </u>  | _Label Update Flag (LUF)              |                 |

|                    | bit 4          |         | bit 3 - unallocated |           |                                       |                 |

|                    | bit 3          |         | -set to 1           |           | NOTE: Bare to and the second          |                 |

|                    | bit 2          |         | -set to 1           |           | NOTE: Data is output on the           |                 |

|                    | bit 1          |         | -set to 1           |           | I <sup>2</sup> C bus <u>MSB</u> first |                 |

|                    | bit 0          |         | set to 1            |           |                                       | =               |

Purchase of GEC Plessey Semiconductors I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in an I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

HEADQUARTERS OPERATIONS

GEC PLESSEY SEMICONDUCTORS

Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom.

Tel: (0793) 518000 Fax: (0793) 518411

#### GEC PLESSEY SEMICONDUCTORS

P.O. Box 660017 1500 Green Hills Road, Scotts Valley, California 95067-0017, United States of America. Tel: (408) 438 2900 Fax: (408) 438 5576

#### **CUSTOMER SERVICE CENTRES**

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Fax: (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 66040867 Fax: (02) 66040993

- JAPAN Tokyo Tel: (03) 5276-5501 Fax: (03) 5276-5510

- NORTH AMERICA Scotts Valley, USA Tel (408) 438 2900 Fax: (408) 438 7023.

- SOUTH EAST ASIA Singapore Tel: (65) 3827708 Fax: (65) 3828872

- SWEDEN Stockholm Tel: 46 8 702 97 70 Fax: 46 8 640 47 36

- TAIWAN, ROC Taipei Tel: 886 2 5461260. Fax: 886 2 7190260

- UK, EIRE, DENMARK, FINLAND & NORWAY

Swindon Tel: (0793) 518510 Fax: (0793) 518582

These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1992 Publication No. DS3106 Issue No. 2.5 April 1995

TECHNICAL DOCUMENTATION - NOT FOR RESALE. PRINTED IN UNITED KINGDOM.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. The Company reserves the right to alter without prior notice the specification, design or price of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.