## MSP430 Family Serial Programming Adapter Manual

# User's Guide

August 2000

**Mixed Signal Products**

SLAU048

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2000, Texas Instruments Incorporated

#### Preface

## **Read This First**

#### About This Manual

This document describes the MSP430-family hardware and software installation and setup. It explains operation and EPROM programming

#### How to Use This Manual

This document contains the following chapters:

- □ Chapter 1 Installation and Setup

- □ Chapter 2 Operation

- □ Chapter 3 Hardware

- □ Chapter 4 EPROM Programming

- □ Chapter 5 Flash Memory

- Appendix A– Schematics

#### Notational Conventions

This document uses the following conventions.

Program code and program examples are shown in a special typeface similar to a typewriter's.

Here is an example of programming code:

long int VerifyFile(char\* lpszFileName, long int

iFileType)

#### Trademarks

Microsoft Windows is a trademark of Microsoft Corporation.

## Contents

| 1 | Insta | llation and Setup                                                                               |

|---|-------|-------------------------------------------------------------------------------------------------|

|   | 1.1   | Installing the Software 1-2                                                                     |

|   | 1.2   | Installing the Hardware 1-3                                                                     |

| 2 | Oper  | ation                                                                                           |

|   | 2.1   | Programming the MSP430 Devices 2-2                                                              |

|   |       | 2.1.1 Basic Procedure                                                                           |

|   |       | 2.1.2 Description of the MSP-PRGS430 GUI 2-3                                                    |

|   |       | 2.1.3 Error Messages 2-5                                                                        |

|   | 2.2   | Content of the PRGS430.ini File                                                                 |

|   | 2.3   | Use of a [Project].ini File 2-8                                                                 |

|   | 2.4   | Command Line Options 2-9                                                                        |

|   |       | 2.4.1 General Definitions 2-9                                                                   |

|   |       | 2.4.2 Return Values / Error Codes in the .ini File 2-11                                         |

|   | 2.5   | Software / Hardware Layers 2-12                                                                 |

|   | 2.6   | PRGS430.DLL—Description                                                                         |

|   |       | 2.6.1 Return Values / Error Codes From the PRGS430.DLL 2-22                                     |

| 3 | Hard  | ware                                                                                            |

|   | 3.1   | Specifications                                                                                  |

|   | 3.2   | Basic Hints                                                                                     |

|   | 3.3   | Programming Adapter Target Connector Signals 3-3                                                |

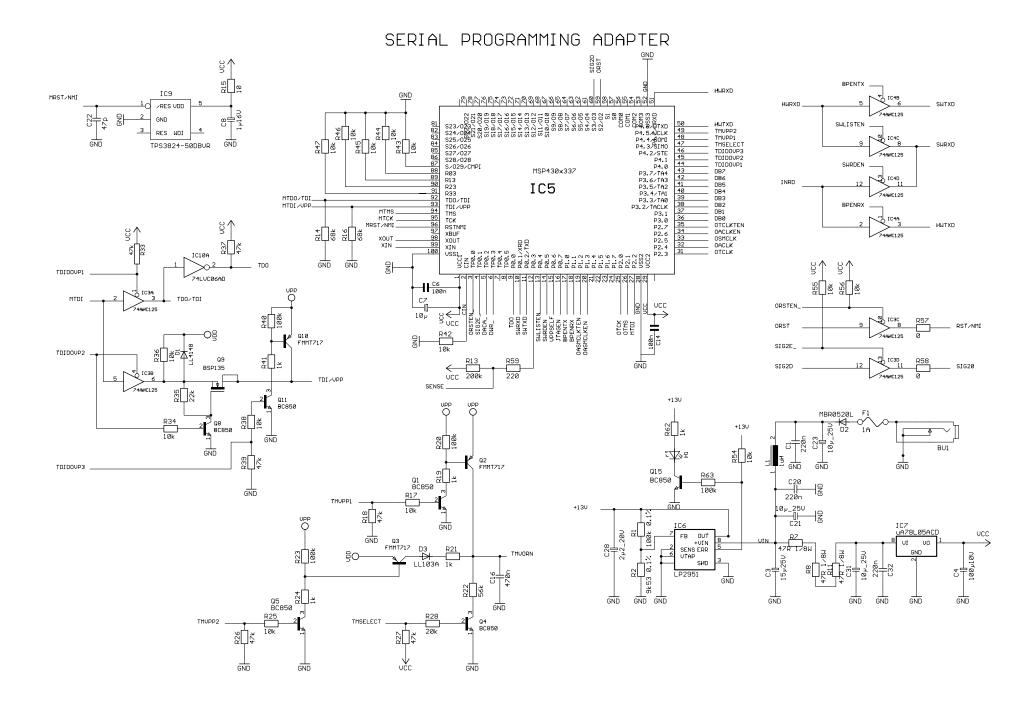

|   | 3.4   | MSP-PRGS430 Circuit Diagrams 3-5                                                                |

|   | 3.5   | Location of Components, MSP-PRGS430 3-5                                                         |

|   | 3.6   | Interconnection of MSP-PRGS430 to MSP430C313DL/430P313SDL,<br>MSP430C311SDL/P315SDL, or 'E313FZ |

|   | 3.7   | Interconnection of MSP-PRGS430 to MSP430C325PG, C325PM,                                         |

|   | 0.1   | MSP430P325PG, or 'P325PM                                                                        |

|   | 3.8   | Interconnection of MSP-PRGS430 to MSP430C336PJM/337PJM or                                       |

|   |       | MSP430E337CQFP                                                                                  |

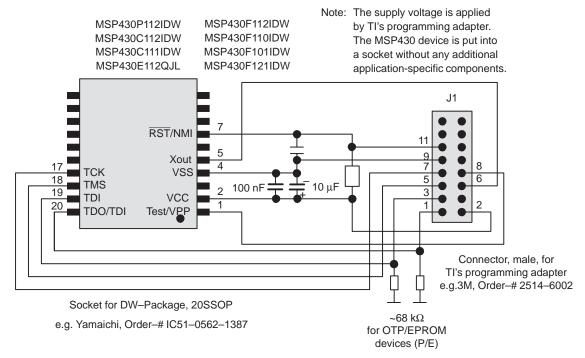

|   | 3.9   | Interconnection of MSP-PRGS430 to MSP430C111DW, MSP430C112DW, MSP430P112DW, or MSP430E112JL     |

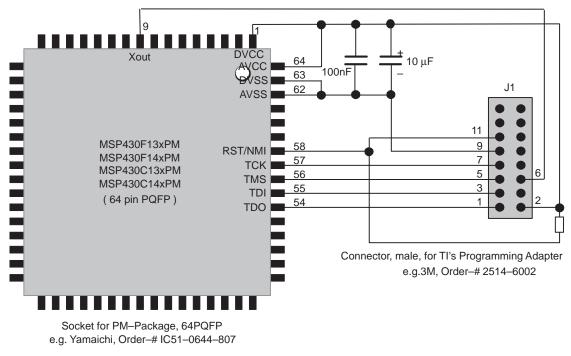

|   | 3.10  | Interconnection of MSP-PRGS430 to the MSP430F13xPM, MSP430C13xPM, MSP430F14xPM, or MSP430C14xPM |

|   |       |                                                                                                 |

| 4 | EPRO  | OM Programming                                                                                  |

|   | 4.1   | EPROM Operation 4-2                                                                             |

|   |       | 4.1.1 Erasure                                                                                   |

|   |       | 4.1.2 Programming Methods 4-2                                                                   |

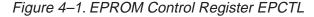

|   |       | 4.1.3 EPROM Control Register EPCTL 4-3                                                          |

|   |       | 4.1.4 EPROM Protect 4-4                                                                         |

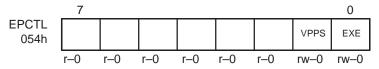

|   | 4.2   | FAST Programming Algorithm 4-4                                                                  |

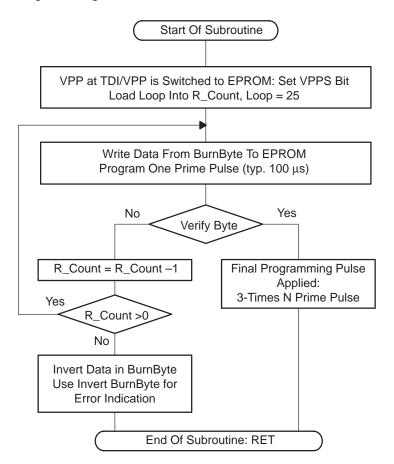

|   | 4.3   | Progra<br>JTAG | amming an EPROM Module Through a Serial Data Link Using the Feature | 4-5  |

|---|-------|----------------|---------------------------------------------------------------------|------|

|   | 4.4   |                | amming an EPROM Module With Controller's Software                   |      |

|   |       | 4.4.1          | •                                                                   |      |

|   | 4.5   | Code .         | · · · · · · · · · · · · · · · · · · ·                               | 4-8  |

| 5 | Flash | Memo           | ry                                                                  | 5-1  |

|   | 5.1   | Flash I        | Memory Organization                                                 | 5-2  |

|   |       | 5.1.1          | Why Is a Flash Memory Module Divided Into Several Segments?         | 5-5  |

|   | 5.2   | Flash I        | Memory Data Structure and Operation                                 | 5-5  |

|   |       | 5.2.1          | Flash Memory Basic Functions                                        | 5-6  |

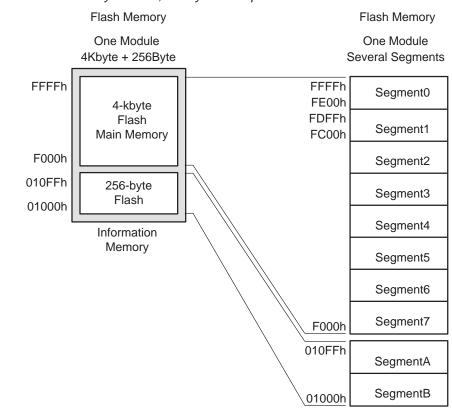

|   |       | 5.2.2          | Flash Memory Block Diagram                                          | 5-6  |

|   |       | 5.2.3          | Flash Memory, Basic Operation                                       | 5-6  |

|   |       | 5.2.4          | Flash Memory Status During Code Execution                           | 5-8  |

|   |       | 5.2.5          | Flash Memory Status During Erase                                    | 5-8  |

|   |       | 5.2.6          | Flash Memory Status During Write (Programming)                      | 5-10 |

|   | 5.3   | Flash I        | Memory Control Registers                                            | 5-13 |

|   |       | 5.3.1          | Flash Memory Control Register FCTL1                                 | 5-13 |

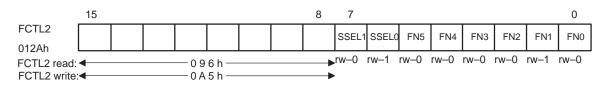

|   |       | 5.3.2          | Flash Memory Control Register FCTL2                                 | 5-15 |

|   |       | 5.3.3          | Flash Memory Control Register FCTL3                                 | 5-16 |

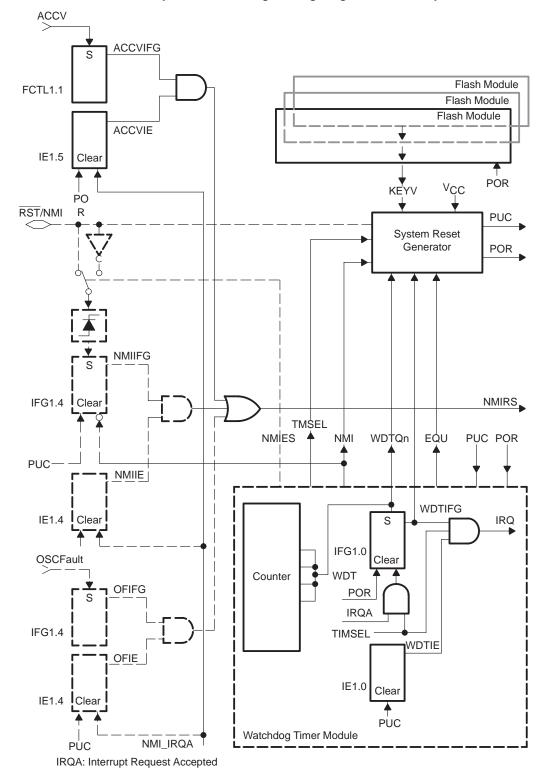

|   | 5.4   | Flash I        | Memory, Interrupt, and Security Key Violation                       | 5-18 |

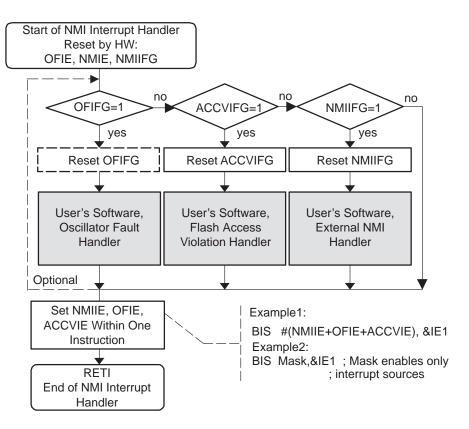

|   |       | 5.4.1          | Example of an NMI Interrupt Handler                                 | 5-20 |

|   |       | 5.4.2          | Protecting One-Flash Memory-Module Systems From Corruption          | 5-20 |

|   | 5.5   | Flash I        | Memory Access via JTAG and Software                                 | 5-22 |

|   |       | 5.5.1          | Flash Memory Protection                                             | 5-22 |

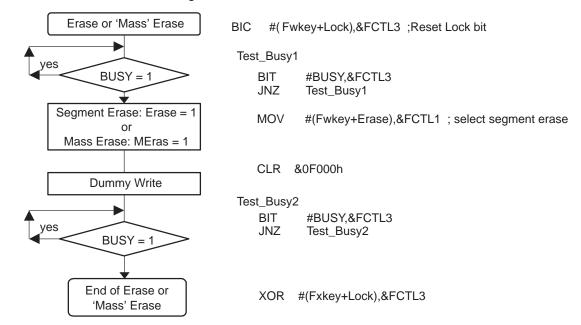

|   |       | 5.5.2          | Program Flash Memory Module via Serial Data Link Using JTAG Feature | 5-22 |

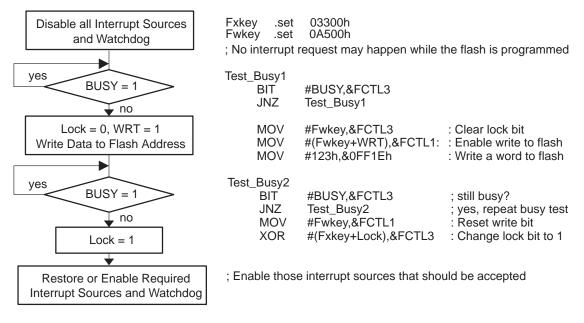

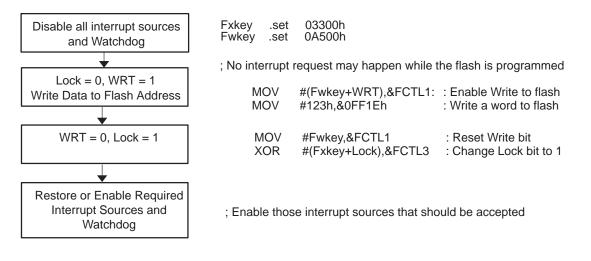

|   |       | 5.5.3          | Programming a Flash Memory Module via Controller Software           | 5-22 |

| Α | Sche  | matics         |                                                                     | A-1  |

## Figures

| 1–1  | ADT430 Program Icons                                                           | 1-2  |

|------|--------------------------------------------------------------------------------|------|

| 1–2  | Program Adapter                                                                |      |

| 2–1  | MSP430 Programmer Dialog Box                                                   |      |

| 2–2  | Communication Error Box                                                        |      |

| 2–3  | Communication Error Box for Blown Fuse                                         | 2-6  |

| 2–4  | Erase Check Error Message                                                      |      |

| 2–5  | Data Error                                                                     |      |

| 3–1  | 25-Pin Sub-D at the Programming Adapter                                        | 3-3  |

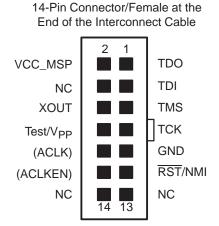

| 3–2  | 14-Pin Connector at the End of the Interconnect Cable                          |      |

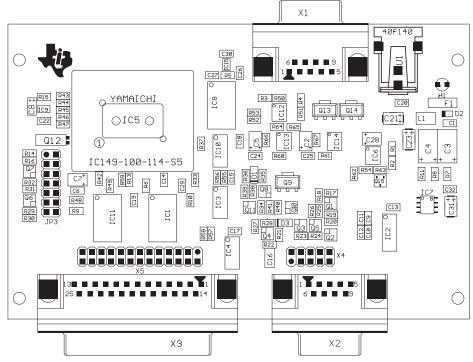

| 3–3  | MSP-PRGS430 Components                                                         | 3-5  |

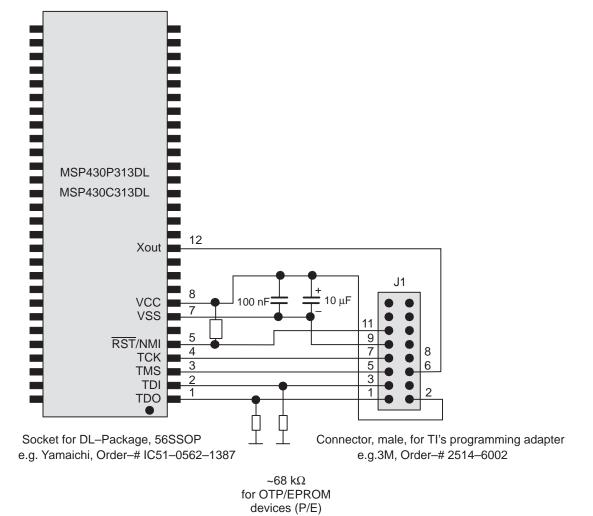

| 3–4  | MSP-PRGS430 Used to Program the MSP430P313DL Device                            |      |

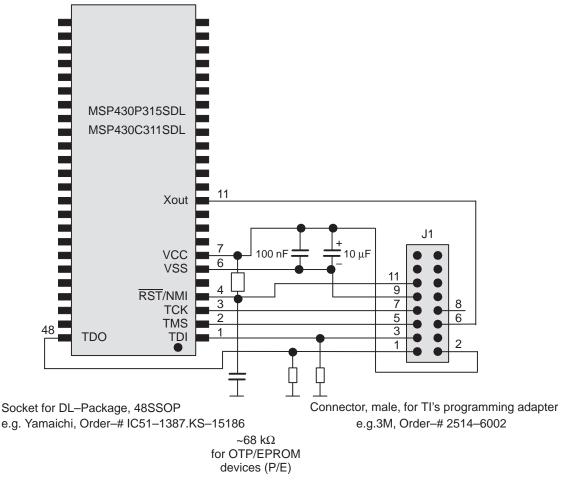

| 3–5  | MSP-PRGS430 Used to Program the MSP430P315SDL Device                           |      |

| 3–6  | MSP-PRGS430 Used to Program the MSP430E313FZ Device                            |      |

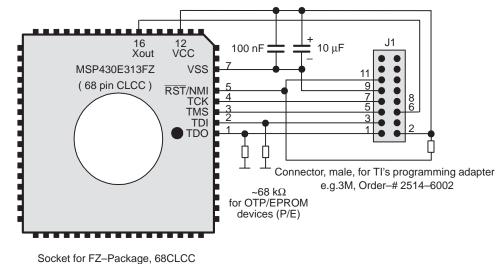

| 3–7  | MSP-PRGS430 Used to Program the MSP430P325PG or<br>MSP430P325APG Devices       |      |

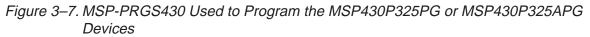

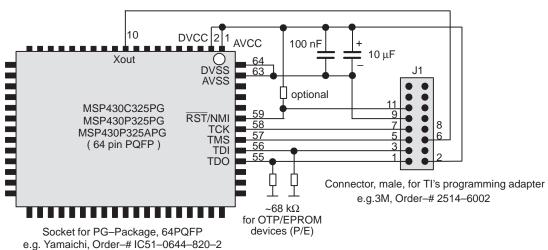

| 3–8  | MSP-PRGS430 Used to Program the MSP430P325PM or<br>MSP430P325APM Devices       |      |

| 3–9  | MSP-PRGS430 Used to Program the MSP430E325FZ Device                            |      |

| 3–10 | MSP-PRGS430 Used to Program the MSP430x33xPJM<br>or the MSP430E337CQFP Devices |      |

| 3–11 | MSP-PRGS430 Used to Program the MSP430x11xIDW<br>or the MSP430E112QJL Devices  | 3-13 |

| 3–12 | Interconnection of MSP-PRGS430 to MSP430x13xPM and<br>MSP430x14xPM             |      |

| 4–1  | EPROM Control Register EPCTL                                                   |      |

| 4–2  | EPROM Programming With Serial Data Link                                        |      |

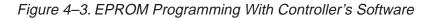

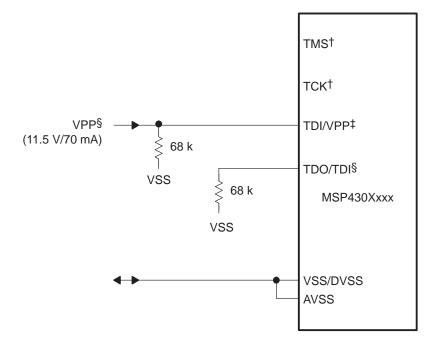

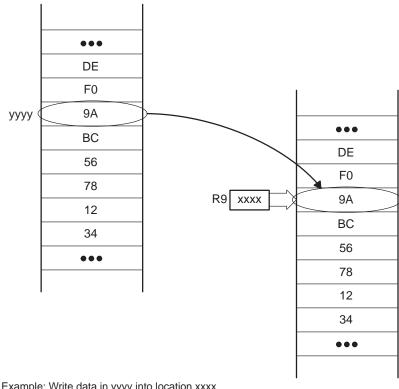

| 4–3  | EPROM Programming With Controller's Software                                   |      |

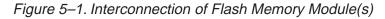

| 5–1  | Interconnection of Flash Memory Module(s)                                      |      |

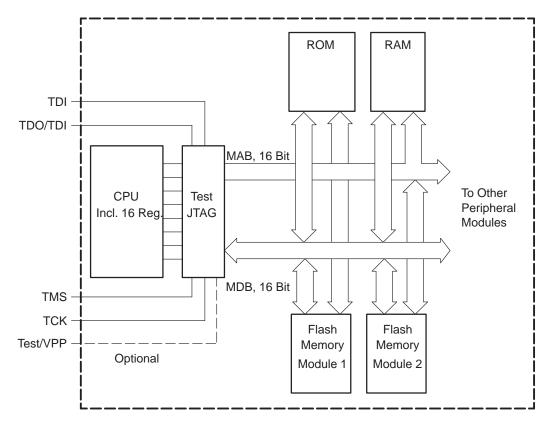

| 5–2  | Flash Memory Module1 Disabled, Module2 Can Execute Code Simultaneously         |      |

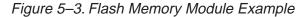

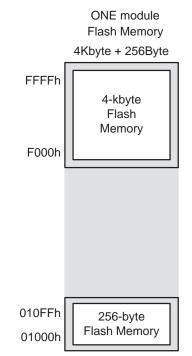

| 5–3  | Flash Memory Module Example                                                    |      |

| 5–4  | Segments in Flash Memory Module, 4K-Byte Example                               |      |

| 5–5  | Flash Memory Module Block Diagram                                              |      |

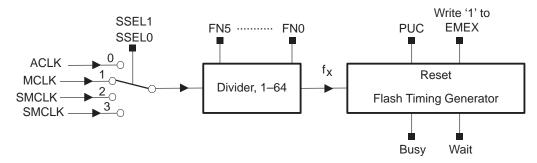

| 5-6  | Block Diagram of the Timing Generator in the Flash Memory Module               |      |

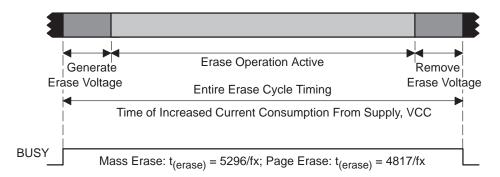

| 5–7  | Basic Flash EEPROM Module Timing During the Erase Cycle                        |      |

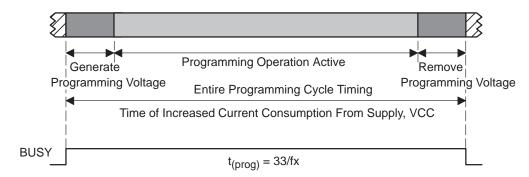

| 5–8  | Basic Flash Memory Module Timing During Write (Single Byte or Word) Cycle      |      |

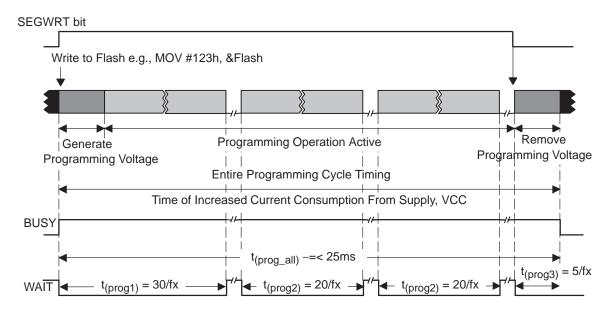

| 5–9  | Basic Flash Memory Module Timing During a Segment-Write Cycle                  |      |

| 5–10 | Basic Flash Memory Module Timing During Segment-Write Cycle                    |      |

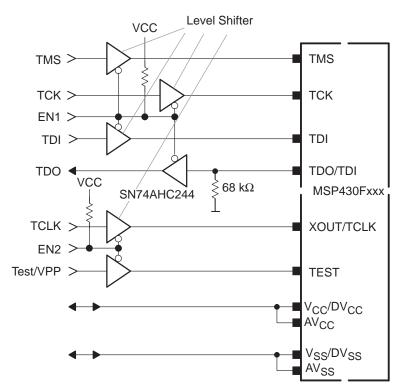

| 5–11 | Signal Connections to MSP430 JTAG Pins                                         |      |

## **Tables**

| 2–1 | MSP430 Function Buttons and Descriptions    | 2-4  |

|-----|---------------------------------------------|------|

| 2–2 | Error Messages                              | 2-7  |

| 2–3 | Command Line Options                        | 2-9  |

| 3–1 | MSP430 Hardware Specifications              | 3-2  |

| 3–2 | Target Connector Signal Functions           | 3-4  |

| 3–3 | Programming Adapter Signal Levels           | 3-4  |

| 5–1 | Control Bits for Write or Erase Operation   | 5-8  |

| 5–2 | Conditions to Read Data From Flash Memory 5 | 5-12 |

|     |                                             |      |

## Chapter 1

## Installation and Setup

This chapter describes the process of installing and programming the hardware and software for the MSP430–PRGS430 programming adapter used with the MSP430 family of microcontrollers.

| Topi | C Page                      |

|------|-----------------------------|

| 1.1  | Installing the Software 1-2 |

| 1.2  | Installing the Hardware 1-3 |

#### 1.1 Installing the Software

To install the MSP-PRGS430 software, perform the following steps:

- Insert the MSP-PRGS430 CD-ROM in the computer's CD drive. It should start automatically. A setup routine will check if you have an HTML browser installed on your computer. The MSP430 start page will then be displayed. (Alternatively, use a browser to open the file *index.htm* that is located in the root directory of the MSP430 CD-ROM. The MSP430 start page will then be displayed.)

- 2) Select Software

- 3) Select Serial Programming Adapter

- 4) Select Save it to disk. A Save As dialog will be displayed.

- 5) Use the Save As dialog to save *PRGS430\_inst.exe* to the computer. Note the directory path to this saved file.

- Navigate to this saved file (PRGS430\_inst.exe), and execute it. A welcoming message will be displayed.

- 7) Follow the setup instructions on the screen. The setup program guides you through the installation process.

- 8) After you run setup, the MSP430 program icons are displayed. Doubleclick the Read me PRGS430 icon, shown in Figure 1–1, to obtain important information about the program device hardware and software.

Figure 1–1. ADT430 Program Icons

| <b>C</b>      |                       | •                         |

|---------------|-----------------------|---------------------------|

| Programs      | 🗖 🛱 Adt430            | PRGS430 Help              |

|               | 🖡 🕞 Internet Explorer | 🕨 🗐 PRGS430 READ ME FIRST |

|               |                       | 430 PRGS430               |

| Documents     | •                     | aninstall MSP-PRGS430     |

| File Settings |                       |                           |

- 9) The appropriate program group and icons are added to the Windows program manager.

- 10) To start the programming adapter software, double-click the Program Device icon in the ADT430 program group.

#### 1.2 Installing the Hardware

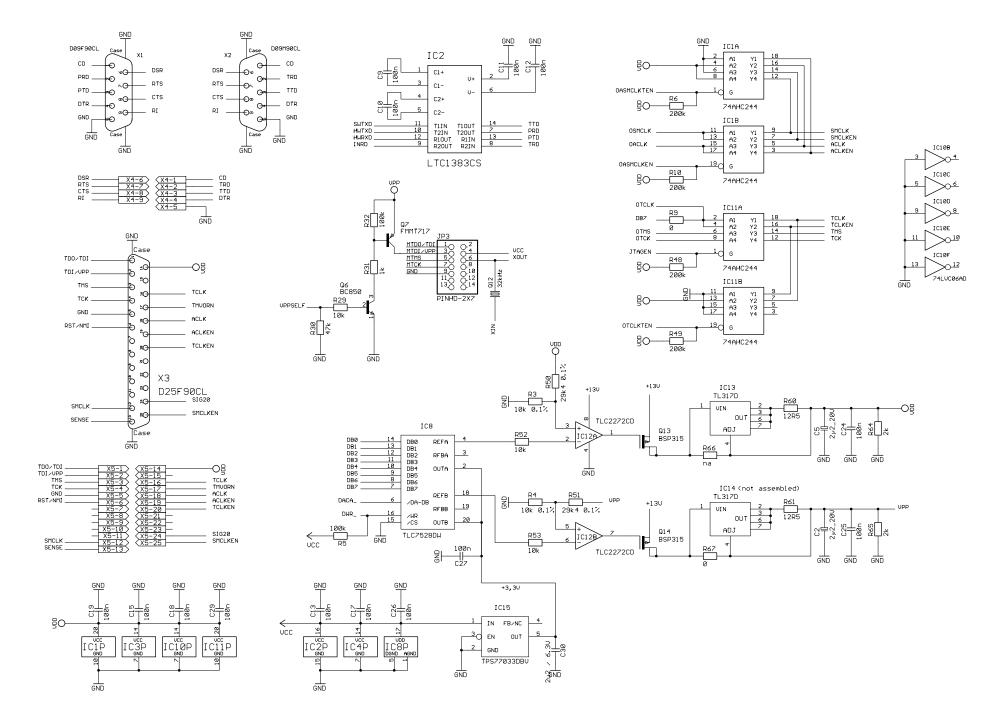

To install the programming adapter hardware, perform the following steps:

- 1) Using the 9-pin SUB-D connector, connect the programming adapter to the serial port (COM1–COM4) of the PC.

- 2) Connect an external power supply to the programming adapter. The voltage of the power supply must be between 14 V and 20 V dc and must provide a minimum of 200 mA of power. The center terminal of the supply connector at the programming adapter is the plus pole.

- 3) The red LED on the programming adapter lights if the power supply is properly connected. If the LED does not light and the power supply is properly connected, check the F1 fuse on the programming adapter printed wire board (PWB).

- 4) The MSP430 devices, in a socket or on a PWB, should be connected to the programming adapter through the 14-pin cable.

The programming adapter provides the selected supply voltage V<sub>CC</sub> at pin 14 of the 25-pin SUB-D connector, or at pin 2 of the 14-pin connector to supply the MSP430 device. The signal name is VCC\_MSP.

The voltage at MSP\_VCC should be set to the same voltage level of the external  $V_{CC}$  if the device is supplied externally, for example, during in-circuit programming.

Figure 1–2. Program Adapter

## Chapter 2

## Operation

This section describes the programming procedure for MSP430 devices and the error messages you may encounter during the procedure.

# TopicPage2.1Programming the MSP430 Devices2-22.2Content of the PRGS430.ini File2-82.3Use of a [Project].ini File2-82.4Command Line Options2-92.5Software/Hardware Layers2-122.6PRGS430.DLL—Description2-13

#### 2.1 Programming the MSP430 Devices

#### 2.1.1 Basic Procedure

The following steps should be used to program the MSP430 devices:

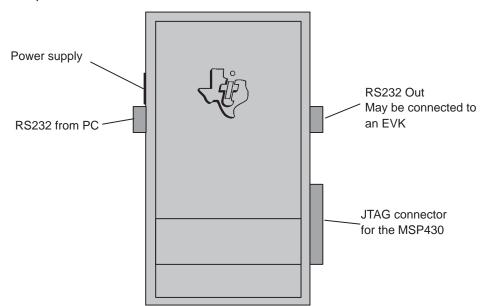

1) Click on the Program Device icon in the ADT430 program group. The MSP430 program device dialog box appears.

The status line at the bottom of the window shows the actual or the most recent activity (see Figure 2-1)

The status line displays the message *Connecting to adapter...* until the programming adapter is detected and the baud rate is set.

- 2) Select the correct device and supply voltage

- 3) Select the name of the object file

- 4) Select the additional options to program, if necessary (using Erase Flash/ Erase Check/Verify...)

- 5) Click on the *Program* button to start programming The status line at the bottom of the window shows the actual or most recent activity (see Figure 2–1)

Figure 2–1. MSP430 Programmer Dialog Box

| Source<br>File <u>N</u> ame<br>fet_1.txt                   |                                                                                                                      | Target<br>Device Select<br>MSP430F1121                                                          | Supply Voltage             |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------|

| Location<br>F:\\PrgS_x\Source\PRGS430                      | _SW\release\                                                                                                         | Device Information<br>RAM: 256B FLASH: 4kB (                                                    | ✓ Vcc switch off<br>+256B) |

| Program [1] Erase / Verify [2                              | ]] Read out [ <u>3]</u> ]                                                                                            | -                                                                                               |                            |

| Program with                                               | <ul> <li>□ Erase <u>F</u>lash</li> <li>☑ Erase <u>C</u>heck</li> <li>☑ <u>V</u>erify</li> <li>□ Bjow Fuse</li> </ul> | Flash Erase Options<br>Main and Information<br>Main Memory only<br>Code Protection<br>Blow Fuse | · Memory                   |

| Reset Device<br>Rese <u>t</u><br>With <u>J</u> TAG release | © P <u>U</u> C<br>© RST/N <u>M</u> I                                                                                 | Communication Settings<br>COM Port<br>COM2                                                      | Baud Rate                  |

| Status<br>Adapter connected.<br>%                          |                                                                                                                      |                                                                                                 |                            |

#### 2.1.2 Description of the MSP-PRGS430 GUI

An MSP430 device is commonly programmed as follows:

- 1) Select the file which contains the data to program from the MSP430 Programmer dialog box (see Figure 2–1).

- 2) Select the device. An error message appears on the screen if the device selected is different or not connected.

- 3) Set the required supply voltage, communication port COMx, and baud rate. The device configuration and memory type are selected automatically according to the selected device.

- 4) Use the program button to start the programming operation.

Table 2–1 describes the function of the buttons for different options and combinations for the MSP430 Programmer dialog box.

| Button Name    | Sub-Functions       | Description                                                                                                                                                                                                                                                                                |

|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Name      |                     | Selects the name of the file to program (intel-hex or TI-txt format)                                                                                                                                                                                                                       |

| Device Select  |                     | Selects the MSP430 device type to program via-pull-down menu                                                                                                                                                                                                                               |

| Supply Voltage |                     | Selects the supply voltage for the MSP430                                                                                                                                                                                                                                                  |

|                | $V_{CC}$ switch off | If selected (default), the supply voltage will be switched off after each MSP430 access; otherwise, the supply voltage remains connected.                                                                                                                                                  |

| Program        |                     | An object code is programmed to the on-chip memory using the select options.                                                                                                                                                                                                               |

|                | With Erase Flash    | Memory will be erased before programming (only with flash devices).<br>The following options are possible:<br>– Main and Information Memory<br>– Main Memory only                                                                                                                          |

|                | With Erase Check    | Erase check will be performed before programming operation is executed.                                                                                                                                                                                                                    |

|                | With Verify         | Each section is verified after it is programmed, or an error message is displayed if verification fails.                                                                                                                                                                                   |

|                | With Blow Fuse      | The code-protection fuse is blown after the entire object code, with verify, is programmed. This action is irreversible and disables future on-chip memory access (reading or programming). This step will not be performed if verify is disabled or verify fails. A warning is displayed. |

| Erase Flash    |                     | Erase operation can be done only with flash devices, according to the selected option.                                                                                                                                                                                                     |

|                | By file             | Only the memory locations corresponding to the selected object file are erased. All other memory locations keep their old data ( <i>smart erase</i> ).                                                                                                                                     |

|                | By device           | The entire flash memory of the device is erased.                                                                                                                                                                                                                                           |

|                | By range            | An erase is performed depending on the values entered in the range fields.                                                                                                                                                                                                                 |

| Erase Check    |                     | Checks if memory locations are erased.                                                                                                                                                                                                                                                     |

|                | By file             | Checks only the memory locations used by the selected object file.                                                                                                                                                                                                                         |

|                | By device           | Checks the entire programmable memory of the device. (No RAM will be checked).                                                                                                                                                                                                             |

|                | By range            | An erase check is performed according to the range of memory locations in the range for Erase Check/Readout field.                                                                                                                                                                         |

Table 2–1. MSP430 Function Buttons and Descriptions

| Button Name | Sub-Functions     | Description                                                                                                                                                                                                                                                                                                                 |  |

|-------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Verify      |                   | Verify the data in the MSP430 device according to the selected option                                                                                                                                                                                                                                                       |  |

|             | By file           | A verification of the memory locations vs. the selected object file is performed.                                                                                                                                                                                                                                           |  |

|             | By device         |                                                                                                                                                                                                                                                                                                                             |  |

|             | By range          | Verify memory locations defined in the <i>range field</i> versus the data in the selected file. The defined range should not contain memory locations outside the data stored in the selected file, otherwise an error will be reported.                                                                                    |  |

| Blow Fuse   |                   | The on-chip security fuse is irreversibly disabled and any access such as reading or programming of the MSP430 is impossible.                                                                                                                                                                                               |  |

| Read Out    |                   | Read out data from MSP430 device. When this function is executed, a dialog box will appear; the file name for the data to store should be selected.                                                                                                                                                                         |  |

|             | By device         | Read out the entire memory of the device and store the data into the file selected in the file name field.                                                                                                                                                                                                                  |  |

|             | By range          | Read out the memory locations selected by the <i>range field</i> and store the data in the file selected in the file name field.                                                                                                                                                                                            |  |

| Reset       |                   | The reset of a MSP430 can be performed in two ways. After reset, the MSP430 may remain under JTAG control or can be released to operate normally and execute the program.                                                                                                                                                   |  |

|             | PUC               | A software reset of the chip is generated.                                                                                                                                                                                                                                                                                  |  |

|             | RST/NMI           | Generates a hardware reset by applying a low pulse on RST/NMI pin.                                                                                                                                                                                                                                                          |  |

|             | With JTAG-release | JTAG will be released after the execution of the reset (via JTAG or RST/NMI).                                                                                                                                                                                                                                               |  |

| COM Port    |                   | Selects the Com port to which the programming adapter is connected                                                                                                                                                                                                                                                          |  |

| Baud Rate   |                   | Selects the baud rate for communication with the programming adapter hardware                                                                                                                                                                                                                                               |  |

| Help        |                   | Help is available for programming MSP430 devices, command<br>buttons, selectors, and the object file format used.<br>The Help menu can be found in the system menu of the serial<br>programming adapter software (right click on the symbol at the upper<br>left corner of the program window) or with the F1 function key. |  |

Table 2–1. MSP430 Function Buttons and Descriptions (Continued)

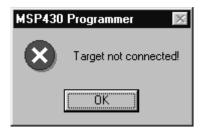

#### 2.1.3 Error Messages

One of the following messages may show up if JTAG communication is not established correctly:

If the MSP430 device to program could not be found, the following message appears (Figure 2–2):

Figure 2–2. Communication Error Box

If the fuse is already blown, the error message shown in Figure 2–3 appears.

Figure 2–3. Communication Error Box for Blown Fuse

| MSP430    | Programmer 🛛 🕅        |

|-----------|-----------------------|

| $\otimes$ | Target fuse is blown! |

| [         | OK )                  |

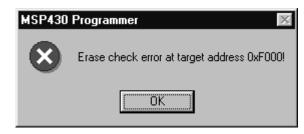

Additional message boxes appear for general error messages such as Erase Check (Figure 2–4).

Figure 2–4. Erase Check Error Message

When a read error is detected in the input file, such as a format error, the following message will be displayed (Figure 2–5):

#### Figure 2–5. Data Error

| Error Type    | Error Message                                          |

|---------------|--------------------------------------------------------|

| Communication | Communication failed!                                  |

| Communication | Adapter not connected!                                 |

| Communication | Synchronization with adapter failed!                   |

| Communication | The present adapter is not a MSP-PRGS430!              |

| Communication | Missing setting of V <sub>CC</sub> !                   |

| MSP430        | Target not connected!                                  |

| MSP430        | Wrong JTAG version!                                    |

| MSP430        | PUC failed!                                            |

| MSP430        | Wrong target!                                          |

| MSP430        | Target fuse is blown!                                  |

| MSP430        | Blown fuse failed!                                     |

| MSP430        | Supply voltage to low!                                 |

| MSP430        | Fuse not released for this device!                     |

| Setting       | Unknown target!                                        |

| Setting       | No target selected!                                    |

| Setting       | Wrong V <sub>CC</sub> selected!                        |

| Setting       | Wrong baud rate!                                       |

| Setting       | Communication port error!                              |

| Setting       | The selected range is invalid!                         |

| Setting       | Wrong argument!                                        |

| Setting       | Error at target address (during erase check or verify) |

| Setting       | Unknown command line option                            |

| Setting       | Command line option out of valid range                 |

| System        | DEVICE.CFG corrupted                                   |

| System        | General error!                                         |

| System        | File type could not be detected!                       |

| System        | Unexpected end of file!                                |

| System        | PROJECT.INI corrupted!                                 |

| System        | Filename mismatch                                      |

| System        | Error in DEVICE.CFG                                    |

| Windows       | Error during file I/O                                  |

|               |                                                        |

#### Table 2–2. Error Messages

#### 2.2 Content of the PRGS430.ini File

The last settings of the PRGS430 graphical user interface (GUI) will be stored in the .ini file before exiting the program. This information is stored under the [Program Device System] section.

Additionally, the following parameters are in the [Options] section and may be modified:

[Options]

LastResult =  $0 \rightarrow$  If the program is called with command-line parameter, the error code which is returned to the system when exiting the program will also be stored here.

#### 2.3 Use of a [Project].ini File

Some default options could be changed within a [Project].ini file. This file has to be in the same directory as the object code file. The following variables could be defined or redefined there.

The name of the file should have the same name as the object file with the extension .ini.

[ProgramDevice] UserMemProtect = Start, Size UserMemProtect2 = Start, Size UserMemProtect3 = Start, Size UserMemProtectn = Start, Size DisableTIMemProtect = 0

Memory ranges defined in the UserMemProtect and UserMemProtect [n] option will be read out and reprogrammed after erase (Flash devise only). [n] could be a number greater or equal then 2 and have to be in ascending order.

If a memory protection is activated in the device definition file from Texas Instruments, it could be switched off with the DisableTIMemProtect = 1 option.

#### 2.4 Command Line Options

#### 2.4.1 General Definitions

| 0: Off | 1: First selectable option |

|--------|----------------------------|

|--------|----------------------------|

1: On 2: Second selectable option

3: Third selectable option

The PRGS430.ini file options are used if they are not specified in the command line. The command line option overwrites the ini file options.

The program will exit automatically if a command is passed via the command line and the command was executed. There will only be a small status window opened during the execution.

Only one command identifier (/CMD:) is allowed within the command line. Otherwise the execution will be canceled and an error will be returned.

If an error in the command line parameter is detected the program will exit with an error message.

*filename* may also contain a path. If special characters are used then the string has to be inside quotes (for example, \\server\adt430\PRG files\test.txt). If an error is detected within the filename, the operation will be canceled and an error will be returned

| Commands:      |                                                                                                                               |

|----------------|-------------------------------------------------------------------------------------------------------------------------------|

| /cmd:PRG       | Program command                                                                                                               |

| /cmd:VFY       | Verify command                                                                                                                |

| /cmd:ERS       | Erase command                                                                                                                 |

| /cmd:CHK       | Erase check command                                                                                                           |

| /cmd:READ      | Read out command                                                                                                              |

| /cmd:RST       | Reset command                                                                                                                 |

| /cmd:BLOW      | Blow fuse command                                                                                                             |

| Options:       |                                                                                                                               |

| /COM:x         | Specifies the serial port: /COM:1, /COM:2 /COM:3, or /COM:4                                                                   |

| /BR:xxxxxx     | Sets baud rate to be used: 9600/19200/38400/57600/115200, e.g. /BR:57600                                                      |

| /Dev:          | Selects the device according to the name in the device.cfg file, e.g. /Dev:MSP430F1121                                        |

| /SVolt:x.x     | Selects supply voltage MSP_VCC of the programming adapter. The voltage is supplied between GND and MSP VCC, e.g., /Svolt: 3.0 |

| /SVoff:{0,1}   | Switches off supply voltage MSP_VCC after execution0:Disable (do not switch off)1:Enable (switch off)                         |

| filename       | Specifies name of the object file to be programmed or verified                                                                |

| /FILE filename | (Second way to define the filename - space separated)                                                                         |

Table 2–3. Command Line Options

| Options for Program Command: |                                                                                                                           |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| /PE:{0,1,2}                  | Option program with erase (flash only)<br>0: Without erase<br>1: Main and Info memory<br>2: Main memory only              |  |

| /PC:{0,1}                    | Option program with erase check<br>0: Disable<br>1: Enable                                                                |  |

| /PV:{0,1}                    | Option program with verify<br>0: Disable<br>1: Enable                                                                     |  |

| /PB:{0,1}                    | Option program with blow fuse (only valid with verify successful)<br>0: Disable<br>1: Enable                              |  |

| Options for Erase/           | Erase Check and Verify Command                                                                                            |  |

| /E:{1,2,}                    | Option erase/erasecheck/verify by file/device/range<br>1: File<br>2: Device<br>3: Range                                   |  |

| /ERange:0xXXX,<br>0xYYYY     | Option erase/erasecheck/verify range (start: 0xXXXX, length: 0xYYYY)                                                      |  |

| Options for Read 0           | Dut Command:                                                                                                              |  |

| /RO:{1,2}                    | Option read out by device/range<br>1: Device<br>2: Range                                                                  |  |

| /RRange:0xXXXX,<br>0xYYYY    | Option read out range (start: 0xXXXX, length: 0xYYYY)                                                                     |  |

| /Rfile:file-<br>name,{1,2}   | Specifies read out file name<br>1: TI–TXT<br>2: Intel–Hex<br>(Default directory should be the last object file directory) |  |

| Log Options:                 |                                                                                                                           |  |

| /Log:filename                | Specifies Log file name<br>(Default directory should be the PRGS430.exe directory)                                        |  |

| /ALog:{0,1}                  | Option accumulative Log file<br>0: Disable<br>1: Enable                                                                   |  |

|                              | Example:                                                                                                                  |  |

#### Table 2–3. Command Line Options (Continued)

Example:

PRGS430.exe "C:\adt430\test\test.txt" /Dev:MSP430F1121 /cmd:PRG /PE:1 /PC:0 /PV:1 /COM:2

This command programs the file test.txt, located in the directory C:adt430\test, into a MSP430F149 device. The device will be erased before programming. The erase check is disabled. The code will be verified after programming. The programming adapter is connected to ComPort 2. The baud rate is not passed with the command line, so the setting in the *PRGS430.ini* file will be used.

#### 2.4.2 Return Values / Error Codes in the .ini File

The error code will be returned to the PC operating system and is also stored in the 'PRGS430.ini'

File in the [Options] section:

| LastResult=0 |                                                        |

|--------------|--------------------------------------------------------|

| 0            | Ok                                                     |

| 2            | Communication failed!                                  |

| 3            | Target not connected!                                  |

| 4            | Adapter not connected!                                 |

| 5            | Wrong JTAG version!                                    |

| 6            | PUC failed!                                            |

| 7            | Synchronization with adapter failed!                   |

| 8            | The present adapter is not a MSP–PRGS430!              |

| 9            | Unknown target!                                        |

| 10           | Wrong target!                                          |

| 11           | No target selected!                                    |

| 12           | Target fuse is blown!                                  |

| 13           | Blow fuse failed!                                      |

| 14           | Missing setting of Vcc!                                |

| 15           | Wrong Vcc selected!                                    |

| 16           | Wrong baudrate!                                        |

| 17           | Communication port error!                              |

| 18           | DEVICE.CFG corrupted!                                  |

| 19           | General error!                                         |

| 20           | The selected range is invalid!                         |

| 21           | Wrong argument!                                        |

| 22           | Error during file I/O.                                 |

| 23           | File type could not be detected!                       |

| 24           | Unexpected end of file!                                |

| 25           | PROJECT.INI corrupted!                                 |

| 26           | Vcc Voltage to low for selected function!              |

| 27           | Fuse not release for this device!                      |

| 101          | Error at target address (during erase check or verify) |

| 102          | Unknown command line option                            |

| 103          | Command line option out of valid range                 |

| 104          | Filename mismatch                                      |

| 105          | Error in device.cfg                                    |

|              |                                                        |

LastResult=0

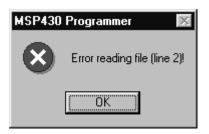

#### 2.5 Software / Hardware Layers

#### 2.6 PRGS430.DLL—Description

The PRGS430.dll is used to communicate with the MSP–PRGS430 hardware and the connected MSP430 device.

This dll could be used separately using the following conventions:

#### /FN0001/ InitCom

long int InitCom(char\* lpszComPort, long int lBaudRate)

InitCom initializes (opens) the given communications port, establishes communication with the PRGS430 hardware, and sets the baud rate of the MSP–PRGS430. If successful, the MSP–PRGS430 is reset and Vcc is set to 0.0 V (the voltage should be set after the first user action to validate the correct value).

IBaudRate: valid baud rates are: 9600, 19200, 38400, 56800, and 115200 baud. The default baud rate after installation is 115200 baud.

IpszComPort: the name of the communication port—COM1, COM2, COM3, or COM4.

Example: lFuncReturn = InitCom("COM1" 115200)

#### /FN0002/ ReleaseCom

long int ReleaseComm (void)

This new function is the counterpart to InitCom. It allows to close a communication with the MSP-PRGS430 hardware.

Vcc will be set to 0 and all outputs will be set to the HI-Z state.

Example: lFuncReturn = ReleaseComm()

#### /FN0003/ SetDeviceType

Example: lFuncReturn = SetDeviceType(char\* lpszDeviceName)

Selects the device type.

IpszDeviceName: name of the device in file device.cfg.

Example: lFuncReturn = SetDeviceType("MSP430F1121")

#### /FN0004/ InitTarget

long int InitTarget(char\* lpszDeviceName )

Initializes the JTAG access to the target device, detects the device type, and reports when the detected device does not match the parameter DeviceName passed.

IpszDeviceName: name of the device in file device.cfg.

Example: lFuncReturn = InitTarget ("MSP430F1121")

#### /FN0005/ ReleaseTarget

long int ReleaseTarget(void)

This function releases the JTAG access to the target device. All JTAG signals from the serial programming adapter will be switched to high impedance. The device will start program execution if it is still connected to Vcc.

Example: lFuncReturn = ReleaseTarget()

#### /FN0006/ Erase

long int Erase(long int wStart, long int wLength, long int Flags)

This function erases flash memory (if available). The protection of areas can be disabled by setting the DISABLE\_TI\_MEM\_PROTECT–Bit in Flags.

wStart: start address of the area to be erased. Allowed values : 0x0000 to 0xFFFE (see memory map of the corresponding device)

wLength: length of the area. Allowed values : 0x0000 to 0xFFFE (see memory map of the corresponding device)

Flags

DISABLE\_TI\_MEM\_PROTECT (0x01)

If this bit is set, the memory protection settings in device.cfg are ignored.

Example: lFuncReturn = Erase(long:0xF000, long:0x1000, long:1)

#### /FN0007/ EraseFile

long int EraseFile(char\* lpszFileName, long int Flags, char\* lpszProjectIni)

EraseFile() erases all addresses used in the specified file.

iFlags:

FILETYPE\_AUTO (0x00) – Autodetection of file type (intel-hex or titext)

FILETYPE\_TI\_TXT (0x01) - File type is TI txt

FILETYPE\_INTEL\_HEX (0x02) - File type is intel hex

IpszProjectIni: name of the {project}.ini file, if protection settings from this file shall be used. If there should be no protection, replace IpszProjectIni by NULL.

Example: lFuncReturn = EraseFile("text.txt", long:0, NULL)

#### /FN0008/ EraseCheck

long int EraseCheck(long int wStart, long int wLength)

Performs an erase check of an area of the target's memory.

wStart: Start address of the memory area. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

wLength: Size of the area. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

The function EraseCheck() simply uses PatternCheck() with 0xFFFF as pattern.

EraseCheck(long int wStart, long int wLength)

{

return PatternCheck(wStart, wLength, 0xFFFF);

}

```

Example:

```

```

lFuncReturn = EraseCheck(long:0xF000, long:0x1000)

```

#### /FN0009/ EraseCheckFile

long int EraseCheckFile(char\* lpszFileName, long int iFileType)

This function checks if all memory addresses, which are in the file, are erased.

lpszFilName: Name of the file

iFileType:

| FILETYPE_AUTO<br>ti–text) | (0x00) | - autodetection of file type (intel-hex or |

|---------------------------|--------|--------------------------------------------|

| FILETYPE_TI_TXT           | (0x01) | – file type is TI txt                      |

| FILETYPE_INTEL_HEX        | (0x02) | - file type is intel hex                   |

| Example:                  |        |                                            |

lFuncReturn = EraseCheckFile("test.txt", long:0)

#### /FN00010/ PatternCheck

long int PatternCheck(long int wStart, long int wLength, long int wPattern)

Checks a memory range with word pattern passed.

wStart: Start address of the memory area. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

wLength: Size of the area. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

wPattern: Word pattern for check

Example: lFuncReturn = PatternCheck(long:0xF000, long:0x1000, long:0xFFFF)

#### /FN00011/ VerifyData

long int VerifyData(long int wStart, long int wLength, void\* lpData)

This function verifies the content of the device with the data stored at passed pointer to data.

wStart: Start address of memory area. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

wLength: Length of the memory area to be checked. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

IpData: Pointer to buffer with data bytes in it

Example: IFuncReturn = VerifyData(long:0xF000, long:0x1000, void\* lpData)

#### /FN00012/ VerifyFile

long int VerifyFile(char\* lpszFileName, long int iFileType)

This function checks if the memory contents of the target device are equal to the file contents.

IpszFileName: Name of the file

iFileType

| FILETYPE_AUTO<br>ti–text)                                        | (0x00) | -autodetection of file type (intel-hex or |  |

|------------------------------------------------------------------|--------|-------------------------------------------|--|

| FILETYPE_TI_TXT                                                  | (0x01) | <ul> <li>– file type is TI txt</li> </ul> |  |

| FILETYPE_INTEL_HEX                                               | (0x02) | - file type is intel hex                  |  |

| <pre>Example: lFuncReturn = VerifyFile("test.txt", long:0)</pre> |        |                                           |  |

#### /FN00013/ VerifyFileRange

long int VerifyFileRange(char\* lpszFileName, long int iFileType, long int wStart, long int wLength)

This function evaluates if the memory contents of the target device are equal to the file contents in a passed range.

IpszFileName: Name of the file

iFileType:

| FILETYPE_AUTO<br>ti–text) | (0x00) | - autodetection of file type (intel-hex or |

|---------------------------|--------|--------------------------------------------|

| FILETYPE_TI_TXT           | (0x01) | – file type is TI txt                      |

| FILETYPE_INTEL_HEX        | (0x02) | <ul> <li>file type is intel hex</li> </ul> |

wStart: Start address of memory area. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

wLength: Length of the memory area to be checked. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

Example: lFuncReturn = VerifyFileRange("test.txt", long:0, long:0xF000, long:0x1000)

#### /FN0014/ ProgramData

long int ProgramData(long int wStart, long int wLength, void\* lpData, long int Flags)

This function writes data into an MSP430 device. Protection of ranges of memory locations defined in the DEVICE.CFG file can be disabled by setting the DISABLE\_TI\_MEM\_PROTECT-Bit in Flags.

wStart: Start address of the range which is to be erased. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

wLength: Length of the range

Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device)

IpData: Pointer to the Data to be programmed

Flags: The bits in Flags control the operation of ProgramData()..

iFlags:

DISABLE\_TI\_MEMPROTECT (0x01)

PGM\_WITH\_ERASE (0x02)

PGM\_WITH\_ERASECHECK (0x04)

Example: lFuncReturn = ProgramData(long:0xF000, long:0x1000, void\* lpData, long:7)

#### /FN0015/ ProgramFile

long int ProgramFile(char\* lpszFileName, long int iFileType,

long int iFlags, char\* lpszProjectIni)

This function writes data from the file to the MSP430 device. The protection of ranges of memory locations defined in the DEVICE.CFG file can be disabled by setting the DISABLE\_TI\_MEM\_PROTECT-Bit in Flags.

IpszFileName: Name of the file to be written into the target

iFileType:

| FILETYPE_AUTO<br>text) | (0x00) - autodetection of file type (intel-hex or ti- |

|------------------------|-------------------------------------------------------|

| FILETYPE_TI_TXT        | (0x01) – file type is TI txt                          |

| FILETYPE_INTEL_HEX     | (0x02) - file type is intel hex                       |

iFlags:

| DISABLE_TI_MEMPROTECT | (0x01) |

|-----------------------|--------|

| PGM_WITH_ERASE        | (0x02) |

| PGM_WITH_ERASECHECK   | (0x04) |

#### IpszProjectIni

Name of the {project}.ini file, if protection settings from this file shall be used. If no protection is required, replace lpszProjectIni by NULL.

The added features do not need to be used – for ProgramFile according to older specification just call ProgramFile(FileName, FileType, 0, NULL); if no {project}.ini file or erase check, should be used just call:

Example: lFuncReturn = ProgramFile(FileName, 0, 0, NULL); // with

autodetect file type

Note: If an erase or erase-check function reports an error, the function ProgramFile() is aborted before programming is started.

#### /FN0016/ BlowFuse

long int BlowFuse(long int Flags)

This function blows the security fuse of the target device.

Flags:

Bitmap to control the operation of BlowFuse().

```

NO_INHIBIT 1

```

If this bit is set in Flags, BlowFuse() suppresses the inhibition from \*.ini files. This flag should always be set to ensure execution.

Example:lFuncReturn = BlowFuse(long:1)

#### /FN0017/ SetVcc

long int SetVcc(long int iVoltage)

This function sets the MSP\_Vcc voltage of the programming adapter to the given value.

iVoltage: Vcc in millivolts. (3000 -> 3V)

The correct MSP430 device should be selected before using this function.

The voltage range is limited to the voltage range allowed for the selected MSP430 device.

Example: lFuncReturn = SetVcc(Long: 3000)

#### /FN0018/ ReadOutData

long int ReadOutData(long int wStart, long int wLength, void\* lpBuffer)

Reads out data from the device and writes it to the buffer passed.

wStart: Start address of the area to be read out. Allowed values : 0x0000 – 0xFFFE (see memory map for the corresponding device).

wLength: Length of the area. Allowed values : 0x0000 - 0xFFFE (see memory map for the corresponding device).

IpBuffer: Pointer points to a buffer that receives the data. The buffer must be large enough to hold the entire data; otherwise, a fatal error of the operating system may occur!

Example:lFuncReturn = ReadOutData(long:0xF000, long:0x1000, void\* lpBuffer)

#### /FN0019/ ReadOutFile

long int ReadOutFile(long int wStart, long int wLength, char\* lpszFileName, long int iFileType)

Read out data from the device and writes it to a file.

wStart: Start address of the area to be read out. Allowed values : 0x0000 – 0xFFFE (see memory map of the corresponding device).

wLength: Length of the area. Allowed values : 0x0000 - 0xFFFE (see memory map of the corresponding device).

IpszFileName: Name of the file to receive data. If the file does not exist, it will be created; If the file already exists, it will be overwritten.

iFileType:

FILETYPE\_TI\_TXT(0x01)- file type is TI txtFILETYPE\_INTEL\_HEX(0x02)- file type is intel hex

Example: lFuncReturn = ReadOutFile(long:0xF000, long:0x1000, "test.out", long:1)

#### /FN0020/ Reset

long int Reset(long int Flags)

This function provides the reset functionality for the target.

Flags: Flags is a bitmap and determines the type of reset.

PUC 0x01

RST\_NMI 0x02

WITH\_RELEASE 0x04

Reset | PUC means that the Jtag sends the command to the MSP430.

Reset | RST\_NMI performs a reset via the RST/NMI pin of the MSP430. The JTAG will also be reset.

If the WITH\_RELEASE option is selected, the device will be released from the JTAG access after the reset.

Example: lFuncReturn = Reset(long:5)

#### /FN0022/ GetProgressInfo

long int GetProgressInfo(long int &iPercent, char\* lpszStatus,

long int iMaxLen)

This function can be polled (typically approximately 10 times per second or less) by the program software, and the progress bar can be updated while an operation is in progress.

iPercent: The state of the progress bar (0 to 100%) is written into this integer.

IpszStatus: Points to a buffer to receive the status string.

iMaxLen: The size of the buffer.

#### /FN0023/ GetDeviceCfgInfo

long int GetDeviceCfgInfo(long int InfoCmd, long int Infoldx, void\* lpBuf)

InfoType:

DEVICE\_COUNT (0x01) GetDeviceCfgInfo returns number of devices in Device.cfg; Infoldx and IpBuf are ignored.

SELECT\_DEVICE(0x02)Selects the given device for further commands (device number in InfoIndex,first device is number 0; IpBuf is ignored).

DEVICE\_NAME (0x03) Fills the name of the selected device into IpBuf; Infoldx is ignored.

DEVICE\_ID (0x04) Fills the DeviceID into IpBuf, Infoldx is ignored.

DEVICE\_DEFAULTOPTIONS (0x05) Fills the default options into lpBuf, Infoldx is ignored.

DEVICE\_MEMDEF\_COUNT (0x06) GetDeviceCfgInfo() returns the number of memory definitions for selected device; lpBuf and Infoldx are ignored.

DEVICE\_MEMDEF (0x07) Fills the definition of a memory definition (index passed by Infoldx) into IpBuf.

DEVICE\_MEMPROTECT\_COUNT(0x08) GetDeviceCfgInfo() returns the number of memory-protection definitions for the selected device; IpBuf and Infoldx are ignored.

DEVICE\_MEMPROTECT (0x09)

Fills the definition of a memory protection definition (index passed by Infoldx) into IpBuf.

DEVICE\_VCC

(0x0A)

GetDeviceCfgInfo() returns the Vcc setting for selected device in millivolts; lpBuf and Infoldx are ignored

DEVICE\_VPP

(0x0B) GetDeviceCfgInfo() returns the Vpp setting for selected device in millivolts; lpBuf and Infoldx are ignored.

DEVICE\_VFUSE

(0x0C) GetDeviceCfgInfo() returns the blow-fuse setting for the selected device; lpBuf and Infoldx are ignored.

#### 2.6.1 Return Values / Error Codes From the PRGS430.DLL

| Status                   | Return Value | Comment                                           |

|--------------------------|--------------|---------------------------------------------------|

| ОК                       | 0            |                                                   |

| SUCCESS                  | -1           | Operation ok                                      |

| ERR_COMMUNICATION        | -2           | Communication error (SSP)                         |

| ERR_TARGET_NOT_CONNECTED | -3           | No target connected                               |

| ERR_SPA430_NOT_CONNECTED | -4           | No SPA430 connected                               |

| ERR_WRONG_JTAG_VERSION   | -5           | JTAG version above 3                              |

| ERR_PUC_FAILED           | -6           | PUC did not succeed                               |

| ERR_SPA430_SYNC_FAILED   | -7           | Could not sync SPA430                             |

| ERR_NO_SPA430            | -8           | Adapter is not SPA430                             |

| ERR_UNKNOWN_TARGET       | -9           | Target type unknown                               |

| ERR_WRONG_TARGET         | -10          | Target type does not match                        |

| ERR_NO_TARGET_SELECTED   | -11          | No target selected (missing SetDeviceType() call) |

| ERR_TARGET_FUSE_BLOWN    | -12          | No target access because of blown fuse            |

| ERR_BLOW_FUSE_FAILED     | -13          | Blown-fuse command failed                         |

| ERR_VCC_NOT_SET          | -14          | No Vcc selected (missing SetVolt() call)          |

| ERR_WRONG_VCC            | -15          | Vcc out of allowed range                          |

| ERR_WRONG_BAUDRATE       | -16          | Invalid baud rate                                 |

| ERR_COMPORT              | -17          | Error accessing the communications port           |

| ERR_DEVICE_CFG           | -18          | Device.cfg corrupted                              |

| ERR_GENERAL              | -19          | General error (should not occur!)                 |

| ERR_RANGE                | -20          | Wrong range specified                             |

| ERR_ARGUMENT             | -21          | Wrong argument                                    |

| ERR_FILE_IO              | -22          | Error during file I/O                             |

| ERR_FILE_DETECT          | -23          | File type could not be detected                   |

| ERR_FILE_END             | -24          | Unexpected end of file                            |

| ERR_PROJECT_INI          | -25          | Error reading {project}.ini                       |

| ERR_VCC_BELOW_VCCMINPROG | -26          | Vcc to low for selected function                  |

| ERR_FUSE_NOT_RELEASED    | -27          | Fuse not release for this device                  |

| STATUS_CONNECTSPA        | 1            | Connecting to SPA430                              |

| STATUS_CONNECTTARGET     | 3            | Connecting to target                              |

| STATUS_RELEASETARGET     | 5            | Releasing target                                  |

| STATUS_RELEASESPA        | 7            | Releasing SPA430                                  |

| STATUS_RESETTARGET       | 9            | Resetting target                                  |

| STATUS_ERASE             | 11           | Erasing target                                    |

| STATUS_ERASECHECK        | 13           | Erase checking target                             |

| STATUS_PATTERNCHECK      | 15           | Pattern checking target                           |

| STATUS_VERIFY            | 17           | Verifying target                                  |

| STATUS_PROGRAM           | 19           | Programming target                                |

| STATUS_READOUT           | 21           | Reading out target                                |

| STATUS_BLOWFUSE          | 23           | Blowing fuse                                      |

### **Chapter 3**

## Hardware

Page

This chapter describes the hardware for the MSP430 family of microcontrollers, including specifications, components of the programming adapters, and connection of the programming adapter to the MSP430 device families.

#### Topic

#### 3.1 3.2 Basic Hints ...... 3-2 3.3 Programming Adapter Target Connector Signals ...... 3-3 3.4 Location of Components, MSP-PRGS430 ..... 3-5 3.5 Interconnection of MSP-PRGS430 to MSP430C313DL/ 3.6 430P313SDL, MSP430C311SDL/P315SDL or 'E313FZ ...... 3-6 3.7 Interconnection of MSP-PRGS430 to MSP430C325PG, Interconnection of MSP-PRGS430 to MSP430C336PJM/P337PJM 3.8 or MSP430E337CQFP ..... 3-12 Interconnection of MSP-PRGS430 to MSP430C111dW, 3.9 MSP430C112DW, MSP430P112DW or MSP430E112JL ...... 3-13 3.10 Interconnection of MSP-PRGS430 to the MSP430F13xPM, MSP430C13xPM, MSP430F14xPM or MSP430C14xPM ...... 3-14

#### 3.1 Specifications

The specifications for the MSP430 hardware are shown in Table 3–1.

Table 3–1. MSP430 Hardware Specifications

| Temperature range | 10°C–45°C                                        |

|-------------------|--------------------------------------------------|

| Humidity          | 40%–70%                                          |

| Power supply      | 14 V–20 V, 200 mA minimum                        |

| Dimensions        | 150 mm (W) $\times$ 30 mm (H) $\times$ 95 mm (D) |

#### 3.2 Basic Hints

These basic hints are useful for programming MSP430 devices or MSP430 devices on printed wire boards (PWB).

- All VCC pins of an MSP430 device are tied together and connected to the most positive terminal of the supply.

- All VSS pins of an MSP430 device are tied together and connected to the most negative terminal of the supply.

- The interface should supply the MSP430 with proper conditions according to the device data sheet in terms of current, voltage levels, and timing conditions.

- MSP430x3xx, MSP430x14x family: Six interconnections are needed as minimum:

TMS, TCK, TDI/VPP, TDO/TDI, VSS, and XOUT.

- MSP430x11x family: Seven interconnections are needed as minimum: TMS, TCK, TDI, TDO/TDI, VSS, Test/VPP, and XOUT.

- Short cables to interconnect the interface to the MSP430 device or PWB; less than 20 cm is recommended.

- Ensure low-impedance interconnections: Especially for the path of the programming and fuse blow voltage – TDI/VPP (MSP430x3xx family) or Test/VPP (MSP430x11x family, or TDI (MSP430x13x/14x family).

- When a device with a transparent window (MSP430E3xx family) is programmed, the window should be already covered with an opaque label while the device is programmed. Since ambient light contains the correct wavelength for erasure, keep the transparent window covered after the device is programmed.

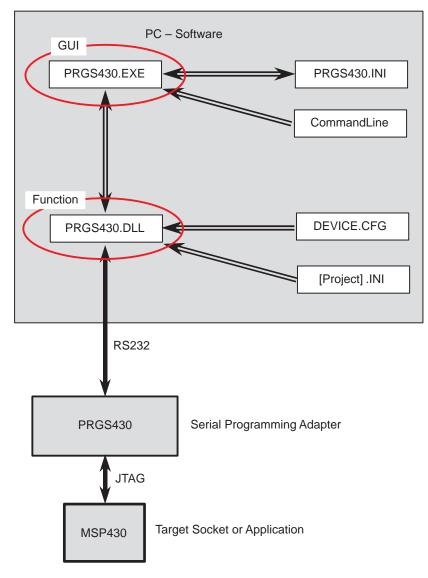

#### 3.3 Programming Adapter Target Connector Signals

The target connector signals for the programming adapter ensure communication between programming adapter and MSP430 devices and supply low energy to systems without extra supply sources.

Figure 3–1 and Figure 3–2 show the target connector signals for the programming adapter.

Figure 3–1. 25-Pin Sub-D at the Programming Adapter

Figure 3–2. 14-Pin Connector at the End of the Interconnect Cable

Table 3–2 lists the target connector signals and describes their requirement statuses and functions.

| Signal/Terminal Name | Required                           | Function/Comment                                                                                                                     |

|----------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| TMS                  | Mandatory                          | Test mode select functions according to IEE1149.1.                                                                                   |

| ТСК                  | Mandatory                          | Test clock functions according to IEE1149.1.                                                                                         |

| TDI/VPP              | Mandatory                          | Test data input functions according to IEE1149.1, but with additional programming voltage.                                           |

| TDO/TDI              | Mandatory                          | Test data output functions according to IEE1149.1, but additional data input is used when programming voltage is applied by TDI/VPP. |

| GND                  | Mandatory                          | GND is the most negative terminal.                                                                                                   |

| VCC_MSP              | Mandatory                          | Voltage source is used with MSP430 devices or PWBs.<br>The voltage level is set through by software.                                 |

| XOUT                 | Mandatory                          | Signal supplies the MSP430 system with clock signals.                                                                                |

| RST/NMI              | Optional                           | If not connected, RST/NMI pin must be held high                                                                                      |

| Test/VPP             | Mandatory<br>(depending on device) | Signal used with MSP430x11x devices to select pin or JTAG function or to apply VPP.                                                  |

#### Table 3–2. Target Connector Signal Functions

The output signal levels of the programming adapter are near GND or VCC\_NSP.

- ☐ The RST/NMI terminal of the device must be high; otherwise the access to the device via JTAG system may fail.

- ☐ The programming procedure (handling of the SW) is described in Chapters 1 and 2 of this manual.

- □ The connections from the MSP430 terminals must follow EMI rules; such as short lines and ground planes. If TMS line receives one negative pulse by EMI strike, the fuse current is activated (with fuse version 1.0). The fuse current flows from TDI(/VPP) pin to GND (or VSS).

Table 3–3. Programming Adapter Signal Levels

| Signal/Pin | Signal/Pin Levels     |

|------------|-----------------------|

| TMS        | VSS or VCC_MSP        |

| ТСК        | VSS or VCC_MSP        |

| TDI/VPP    | VSS or VCC_MSP or VPP |

| TDO/TDI    | VSS or VCC_MSP        |

| XOUT       | VSS or VCC_MSP        |

| RST/NM     | VSS or VCC_MSP        |

| Test/VPP   | VSS or VCC_MSP or VPP |

# 3.4 MSP-PRGS430 Circuit Diagrams

The MSP-PRGS430 circuit diagrams are found in Appendix A.

# 3.5 Location of Components, MSP-PRGS430

Figure 3–3. MSP-PRGS430 Components

Note: Do not use J2 Pin 9 as RST/NMI pullup.

# 3.6 Interconnection of MSP-PRGS430 to MSP430C313DL/430P313SDL, MSP430C311SDL/P315SDL, or 'E313FZ

The circuit diagrams in Figure 3–5 show the connections required to program the MSP430P313DL device with programming adapter MSP-PRGS430 in a separate socket.

Figure 3-4. MSP-PRGS430 Used to Program the MSP430P313DL Device

The  $\overline{\text{RST}}$ /NMI terminal on the MSP430 device has to be held high by an external resistor during access of the device through JTAG. In a noisy environment, consider using an additional capacitor from  $\overline{\text{RST}}$ /NMI to VSS.

Figure 3–5. MSP-PRGS430 Used to Program the MSP430P315SDL Device

The RST/NMI terminal on the MSP430 device has to be held high by an external resistor during access of the device through JTAG. In a noisy environment, consider using an additional capacitor from RST/NMI to VSS.

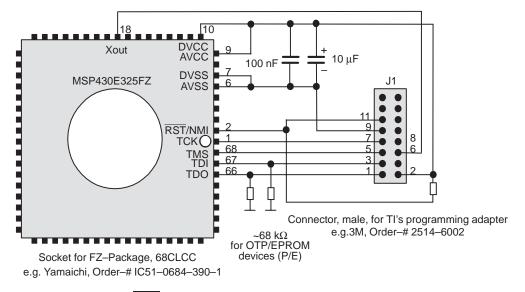

Figure 3–6. MSP-PRGS430 Used to Program the MSP430E313FZ Device

e.g. Yamaichi, Order-# IC51-0684-390-1

**Note:** The supply voltage is applied by TI's programming adapter. The MSP430 device is put into a socket without any additional application-specific components.

# 3.7 Interconnection of MSP-PRGS430 to MSP430C325PG, C325PM, MSP430P325PG, or 'P325PM

The circuit diagrams in Figure 3–19 show the connections required to program the MSP430C325PG, MSP430P325PG, or MSP430P325APG device with programming adapter PRGS430 in a separate socket.

Ensure that both positive terminals AVCC and DVCC are connected. In addition, ensure that both negative terminals AVSS and DVSS are connected.

Figure 3–9. MSP-PRGS430 Used to Program the MSP430E325FZ Device

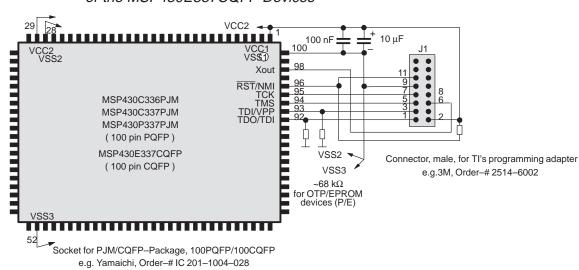

# 3.8 Interconnection of MSP-PRGS430 to MSP430C336PJM/337PJM or MSP430E337CQFP

The circuit diagram in Figure 3–10 show the connections required to program the MSP430C336PJM, MSP430P337PJM, or MSP430E337CQFP devices with programming adapter PRGS430 in a separate socket. Since the device is not connected to a power supply in this configuration, the necessary supply comes from the PRGS430.

Ensure that the two positive terminals, VCC1 and VCC2, as well as the three negative terminals, VSS1, VSS2, and VSS3, are connected.

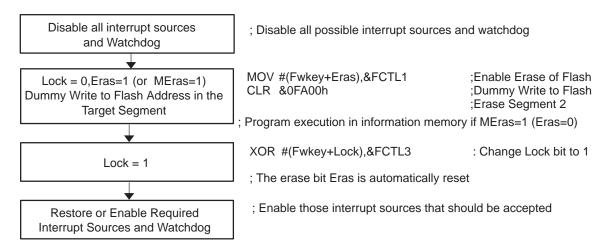

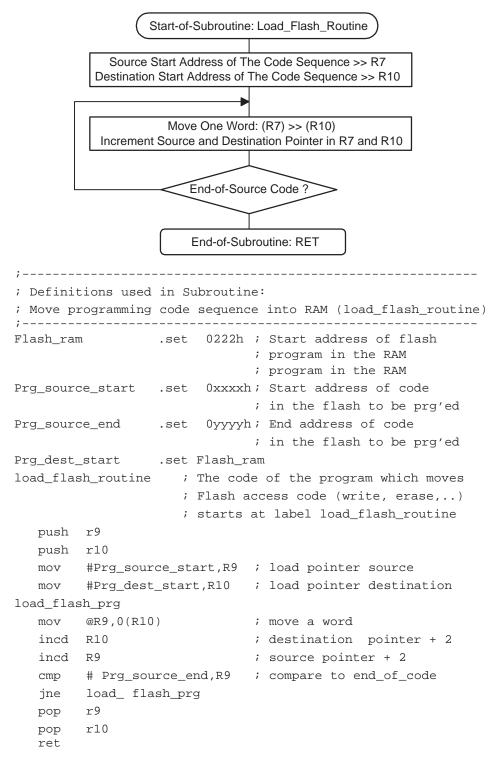

Figure 3–10. MSP-PRGS430 Used to Program the MSP430x33xPJM or the MSP430E337CQFP Devices