# MSM80C154S MSM83C154S MSM85C154HVS

**USER'S MANUAL**

| © Copyright 1988. | OKLELECTRIC | INDUSTRY | COMPANY LTD | ) |

|-------------------|-------------|----------|-------------|---|

|                   |             |          |             |   |

OKI makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

OKI retains the right to make changes to these specifications at any time, without notice.

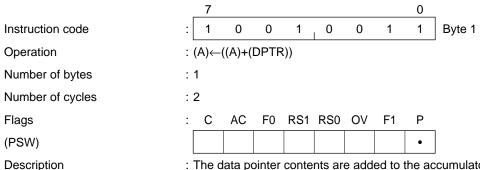

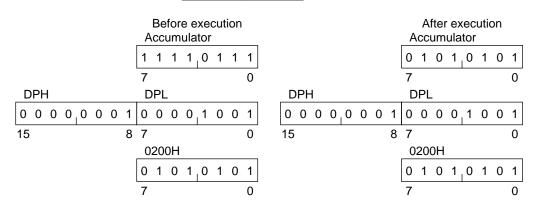

### **CONTENTS**

| 1. | INTRO    | DUCTION                                                                         |    |

|----|----------|---------------------------------------------------------------------------------|----|

|    | 1.1 MS   | M80C154S/MSM83C154S/MSM85C154HVS Outline                                        | 3  |

|    |          | M80C154S/MSM83C154S Features                                                    |    |

|    | 1.3 Add  | ditional Features in MSM80C154S/MSM83C154S/MSM85C154HVS                         | 7  |

|    |          |                                                                                 |    |

| 2. |          | M CONFIGURATION                                                                 |    |

|    |          | M80C154S/MSM83C154S/MSM85C154HVS Logic Symbols                                  |    |

|    |          | M80C154S/MSM83C154S Pin Layout                                                  |    |

|    | 2.2.1    | MSM80C154S/MSM83C154S external dimensions                                       |    |

|    | 2.2.2    | MSM85C154HVS pin layout and external dimensions                                 |    |

|    |          | M80C154S Block Diagram                                                          |    |

|    |          | M83C154S Block Diagram                                                          |    |

|    |          | M85C154HVS Block Diagram                                                        |    |

|    |          | ning and Control                                                                |    |

|    | 2.6.1    |                                                                                 |    |

|    | 2.6.2    | Major synchronizing signals                                                     | 23 |

|    |          | (1) ALE                                                                         |    |

|    |          | (2) PSEN                                                                        |    |

|    |          | (3) WR                                                                          |    |

|    | 0.00     | (4) RD                                                                          |    |

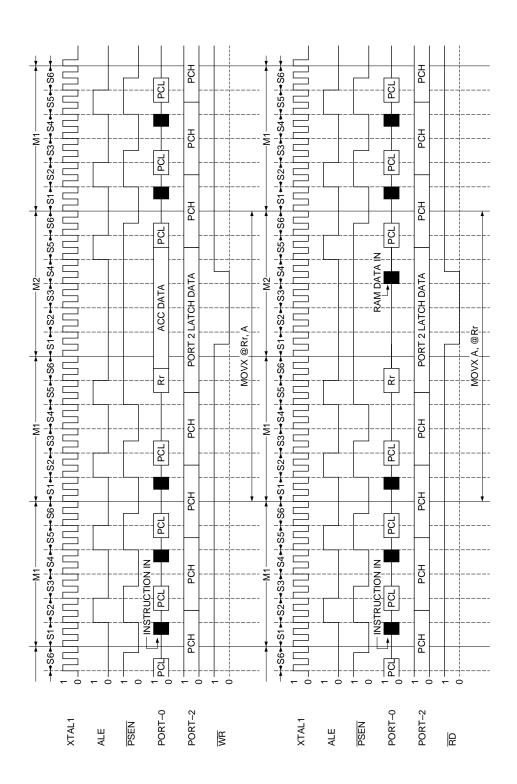

|    | 2.6.3    | MSM80C154S fundamental operation time charts                                    |    |

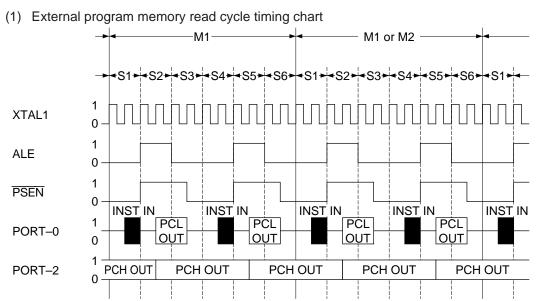

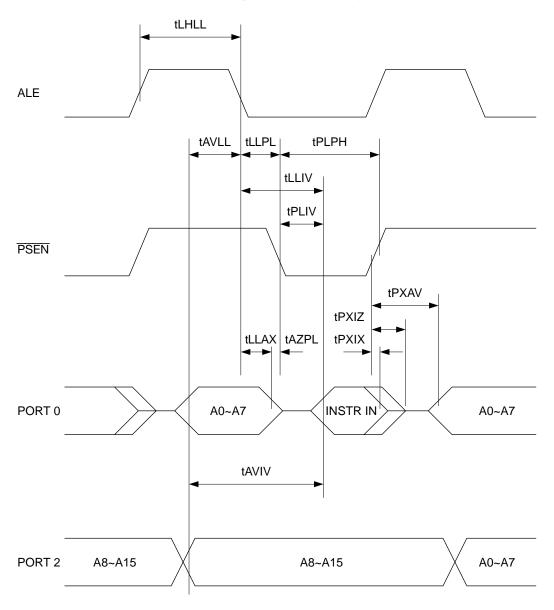

|    |          | (1) External program memory read cycle timing chart                             |    |

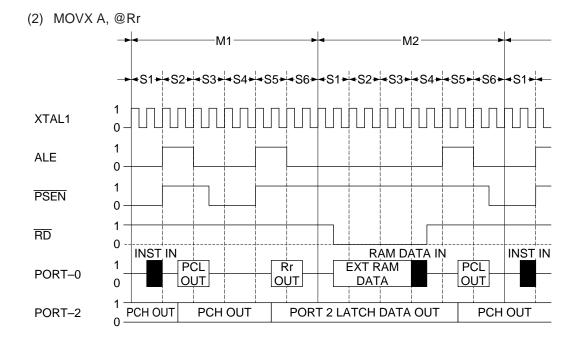

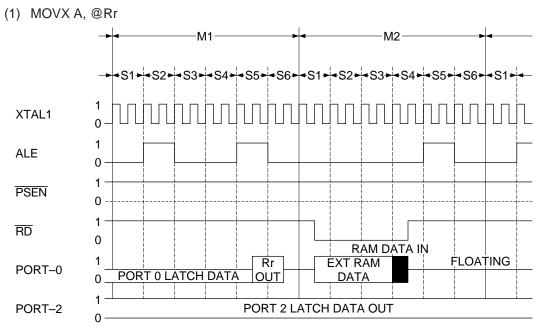

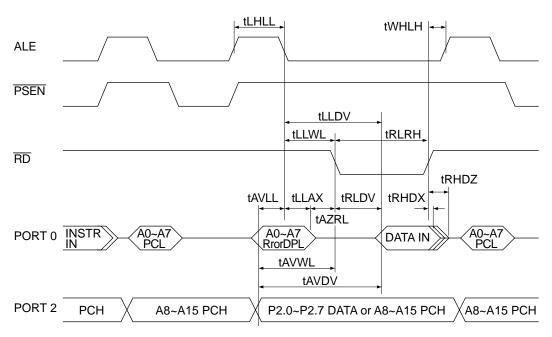

|    |          | (2) MOVX A, @Rr                                                                 |    |

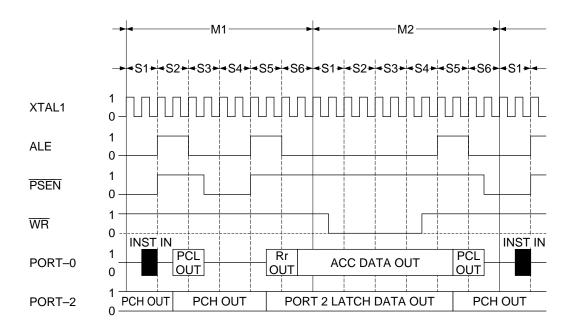

|    |          | (3) MOVX @Rr, A                                                                 |    |

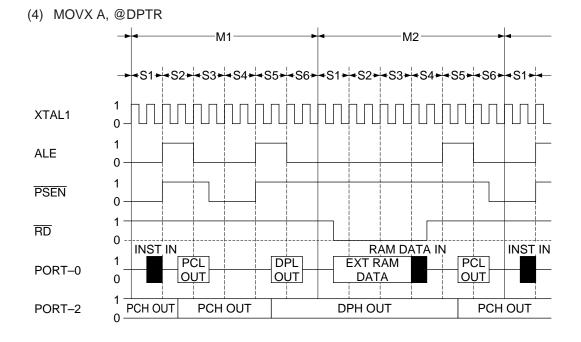

|    |          | (4) MOVX A, @DPTR                                                               |    |

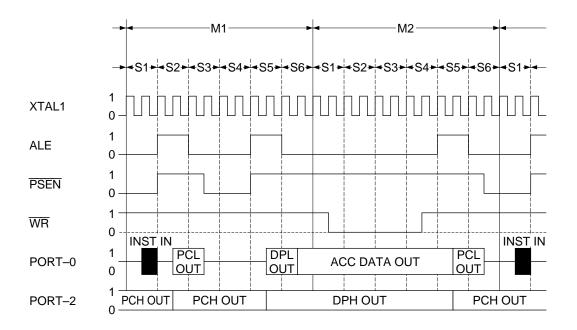

|    |          | (5) MOVX @DPTR, A                                                               |    |

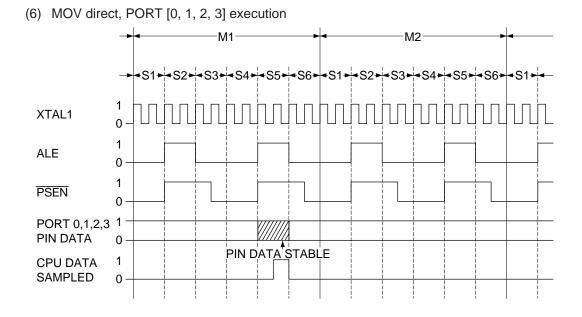

|    | 264      | (6) MOV direct, PORT[0, 1, 2, 3] execution                                      |    |

|    | 2.6.4    | MSM83C154S fundamental operation time charts                                    |    |

|    |          | (1) MOVX A, @Rr(2) MOVX @Rr, A                                                  |    |

|    |          | (2) MOVX @RI, A(3) MOVX A, @DPTR                                                |    |

|    |          | (4) MOVX @ DPTR, A                                                              |    |

|    |          | (5) MOV direct, PORT[0, 1, 2, 3] execution                                      |    |

|    | 2.7 Inst | truction Register (IR) and Instruction Decoder (PLA)                            |    |

|    |          | hmetic Operation Section                                                        |    |

|    | 2.0 AIII | (1) Outline                                                                     |    |

|    |          | (2) Arithmetic operation instruction decoder                                    |    |

|    |          | (3) Arithmetic and logic unit (ALU)                                             |    |

|    | 2.0 Pro  | gram Countergram Counter                                                        |    |

|    |          | gram Memory and External Data Memory                                            |    |

|    |          | MSM80C154S/MSM83C154S program area and                                          |    |

|    | ۷.۱۵.۱   | external ROM connections                                                        | 22 |

|    | 2 10 2   | Procedures and circuit connections used when external                           |    |

|    | ۷.۱۷.۷   | data memory (RAM) is accessed by data pointer (DPTR)                            | 35 |

|    | 2 10 3   | Procedures and circuit connections used when external                           |    |

|    | 2.10.0   | data memory (RAM) is accessed by registers R0 and R1                            | 32 |

|    |          | water morning (interpretation according by logicities into alle in immediations |    |

| 3. | CONTROL                                                              |    |

|----|----------------------------------------------------------------------|----|

|    | 3.1 Oscillators [XTAL1 .2]                                           | 43 |

|    | 3.2 CPU Resetting                                                    |    |

|    | 3.2.1 Outline                                                        | 45 |

|    | 3.2.2 Reset Schmitt trigger circuit                                  | 50 |

|    | 3.2.3 CPU internal status by reset                                   | 51 |

|    | 3.3 EA(CPU Memory Separate)                                          | 52 |

|    | 3.3.1 Outline                                                        | 52 |

|    | (1) Internal ROM mode                                                | 52 |

|    | (2) External ROM mode                                                |    |

| 4. | INTERNAL SPECIFICATIONS                                              |    |

|    | 4.1 Internal Data Memory (RAM) and Special Function Registers        | 55 |

|    | 4.1.1 Outline                                                        | 55 |

|    | 4.2 Internal Data Memory (RAM)                                       | 57 |

|    | 4.2.1 Internal data memory (RAM)                                     | 57 |

|    | 4.2.2 Internal data memory registers R0 thru R7                      | 59 |

|    | 4.2.3 Stack                                                          |    |

|    | 4.3 Internal Data Memory (RAM) Operating Procedures                  |    |

|    | 4.3.1 Internal data memory indirect addressing                       |    |

|    | 4.3.2 Internal data memory register R0 thru R7 designation           |    |

|    | 4.3.3 Internal data memory 1-bit data designation                    |    |

|    | 4.4 Special Function Registers(TCON, SCON,ACC, B)                    |    |

|    | 4.4.1 Outline                                                        |    |

|    | 4.4.2 Special function registers                                     |    |

|    | 4.4.2.1 Timer mode register (TMOD)                                   |    |

|    | 4.4.2.2 Power control register (PCON)                                |    |

|    | 4.4.2.3 Timer control register (TCON)                                |    |

|    | 4.4.2.4 Serial port control register (SCON)                          |    |

|    | 4.4.2.5 Interrupt enable register (IE)                               |    |

|    | 4.4.2.6 Interrupt priority register (IP)                             |    |

|    | 4.4.2.7 Program status word register (PSW)                           |    |

|    | 4.4.2.8 I/O control register (IOCON)                                 |    |

|    | 4.4.2.9 Timer 2 control register (T2CON)                             |    |

|    | 4.5 Timer/Counters 0, 1, and 2                                       |    |

|    | 4.5.1 Outline                                                        |    |

|    | 4.5.2 Timer/counters 0 and 1                                         |    |

|    | 4.5.2.1 Outline                                                      |    |

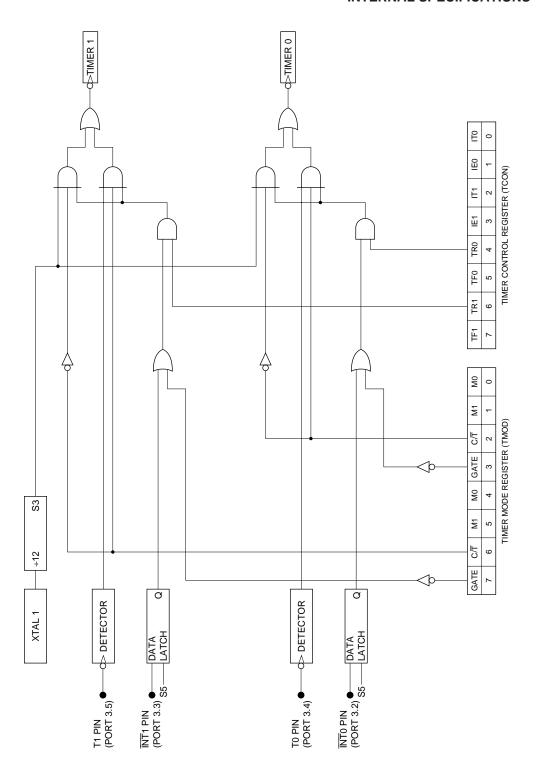

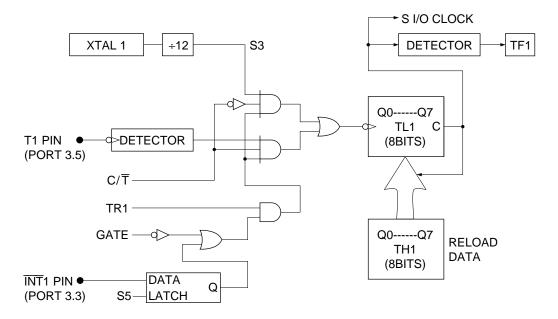

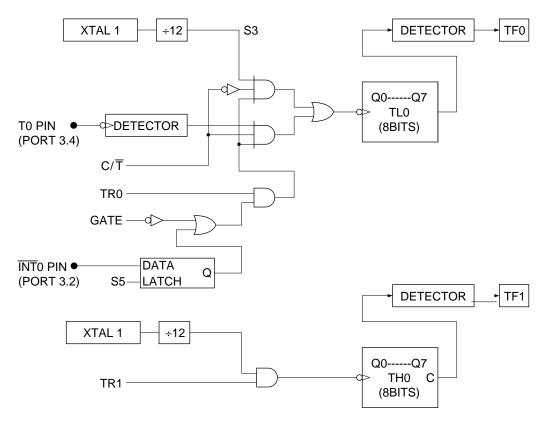

|    | 4.5.2.2 Timer/counter 0 and 1 counting control                       |    |

|    | 4.5.2.3 Timer/counter 0 and 1 count clock designation                |    |

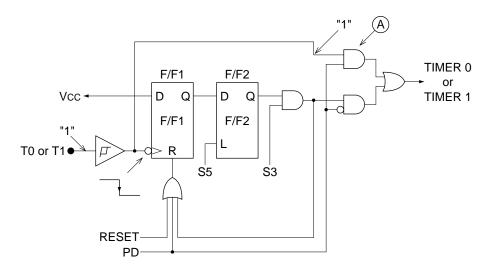

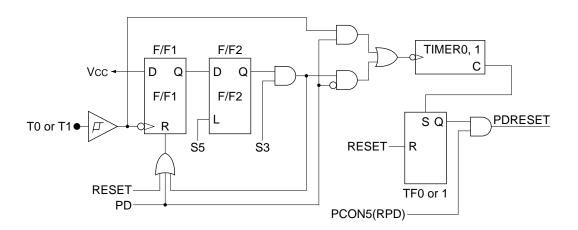

|    | 4.5.2.3.1 External clock detector circuit for timer/counters 0 and 1 |    |

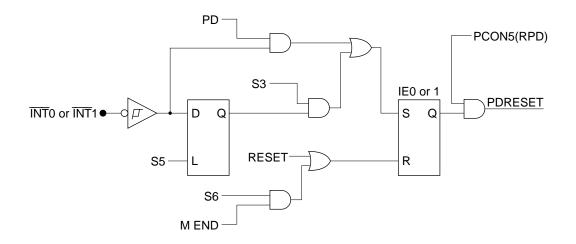

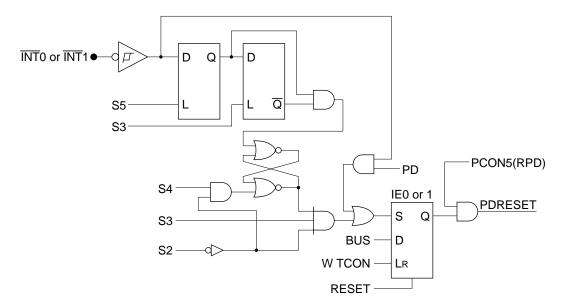

|    | 4.5.2.4 Counting control of timer/counters 0 and 1 by INT pin        |    |

|    | 4.5.2.5 Timer/counters 0/1 timer modes                               |    |

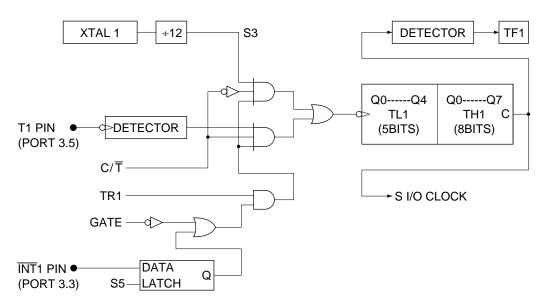

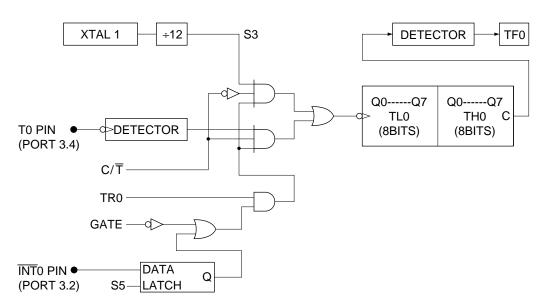

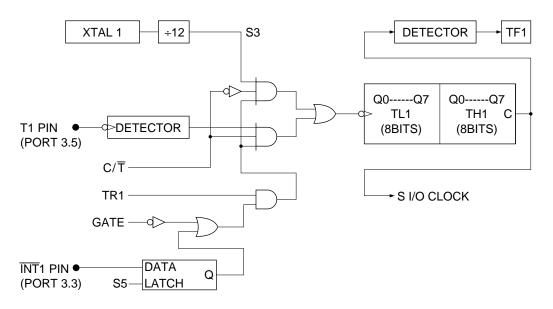

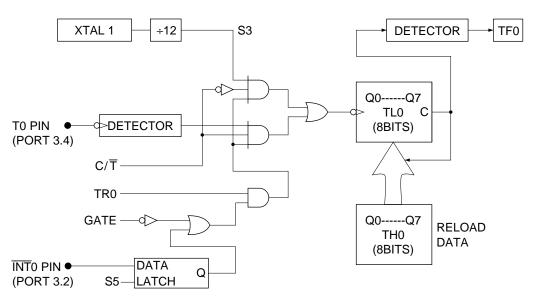

|    | 4.5.2.5.1 Outline                                                    | _  |

|    | 4.5.2.5.2 Mode 0                                                     | _  |

|    | 4.5.2.5.3 Mode 1                                                     |    |

|    | 4.5.2.5.4 Mode 2                                                     |    |

|    | 4.5.2.5.5 Mode 3                                                     |    |

|    | 4.0.2.0.0 32-DIL LITTEL THOUGE                                       | 09 |

| 4.5.2.5.7    | Caution about use of timer counters 0 and 1                  | 90                                    |

|--------------|--------------------------------------------------------------|---------------------------------------|

| 4.5.2.5.8    | Caution about use of timer counters 0 and 1 when setting sof | tware                                 |

|              | power down mode                                              | 91                                    |

| 4.5.3 Timer. | /counter 2                                                   | 92                                    |

| 4.5.3.1 Out  | tline                                                        | 92                                    |

| 4.5.3.2 Tim  | ner 2 control register (T2CON)                               | 92                                    |

|              | ner/counter 2 operation modes                                |                                       |

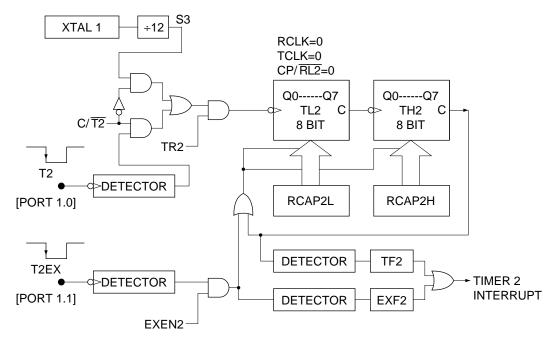

| 4.5.3.3.1    | 16-bit auto reload mode                                      | 93                                    |

| 4.5.3.3.2    | 16-bit capture mode                                          | 94                                    |

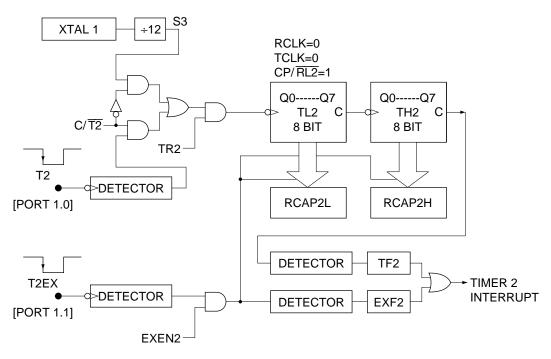

| 4.5.3.3.3    | 16-bit baud rate generator mode                              | 95                                    |

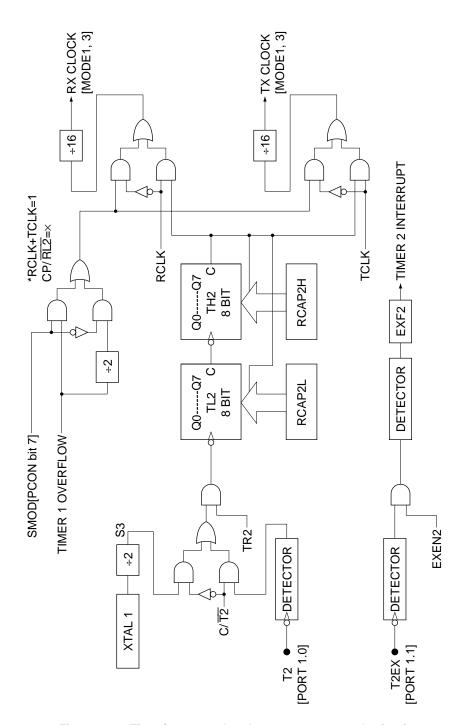

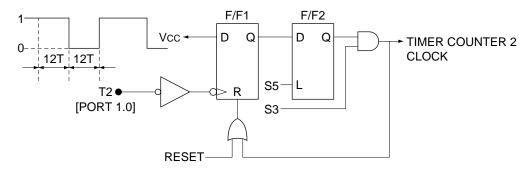

| 4.5.3.4 Tim  | ner/counter 2 detector circuit                               | 97                                    |

| 4.5.3.4.1    | T2(timer/counter 2 external clock detector)                  | 97                                    |

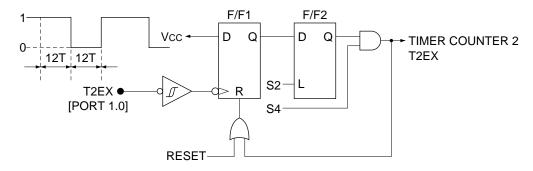

| 4.5.3.4.2    | T2EX(timer/counter 2 external flag input detector)           | 97                                    |

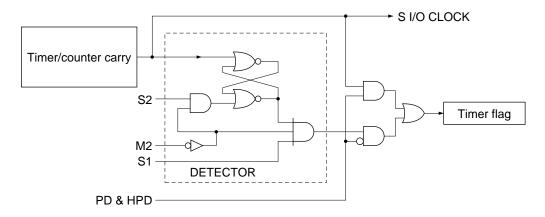

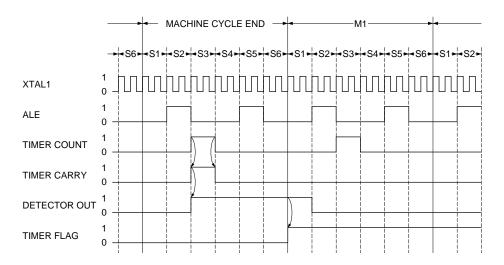

|              | ner/counter carry signal detector circuit                    |                                       |

|              |                                                              |                                       |

| 4.6.1 Outlin | e                                                            | 99                                    |

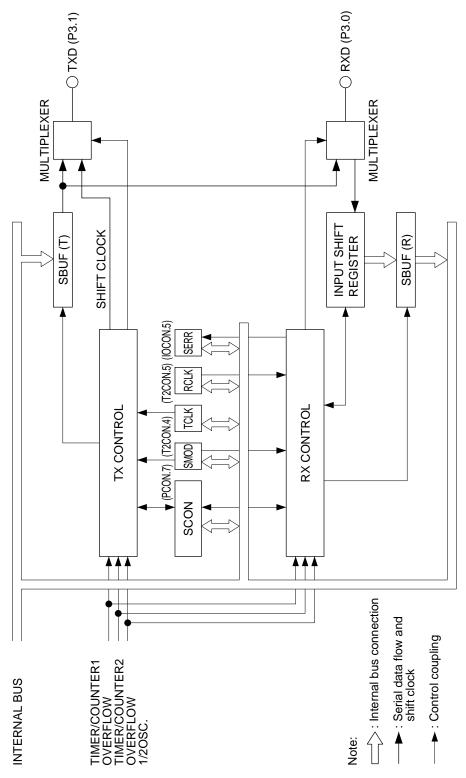

| 4.6.2 Specia | al function registers for serial port                        | 101                                   |

|              | ON                                                           |                                       |

|              | UF                                                           |                                       |

|              | LK                                                           |                                       |

| 4.6.2.4 RC   | LK                                                           | 103                                   |

|              | OD                                                           |                                       |

|              | RR                                                           |                                       |

|              | ating modes                                                  |                                       |

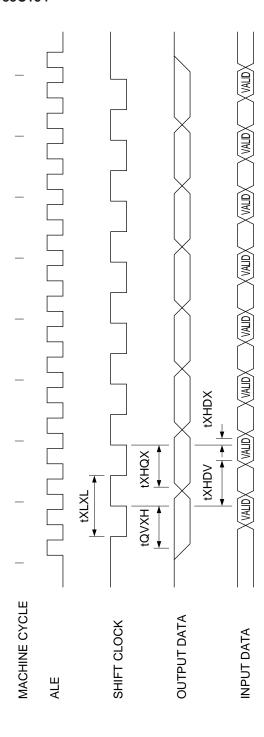

| •            | de 0                                                         |                                       |

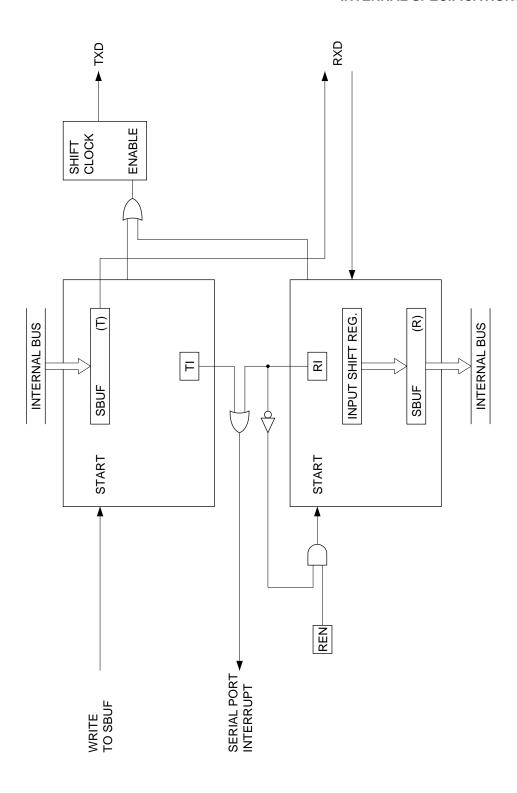

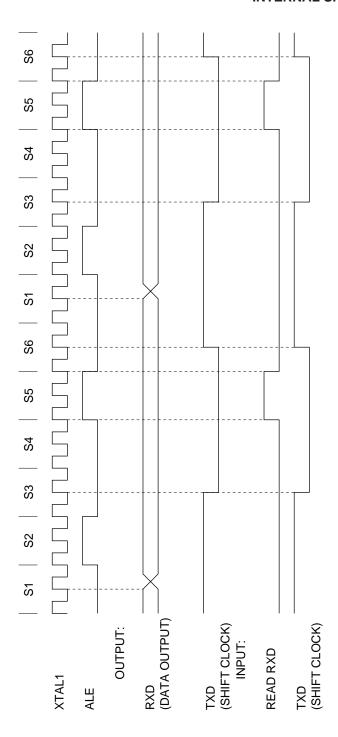

|              | Outline                                                      |                                       |

|              | Mode 0 baud rate                                             |                                       |

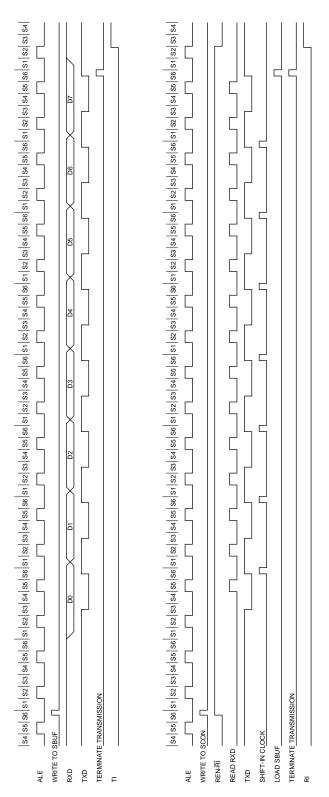

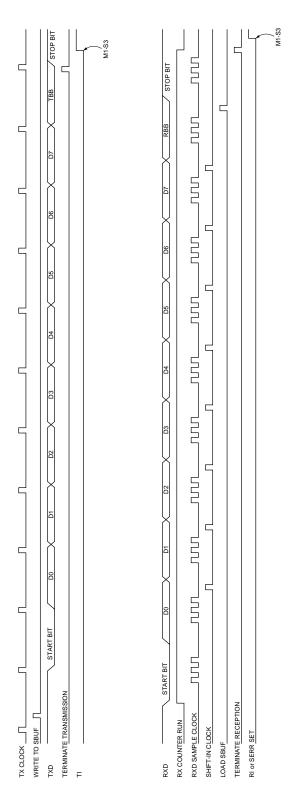

|              | Mode 0 transmit operation                                    |                                       |

|              | Mode 0 receive operation                                     |                                       |

|              | le 1                                                         |                                       |

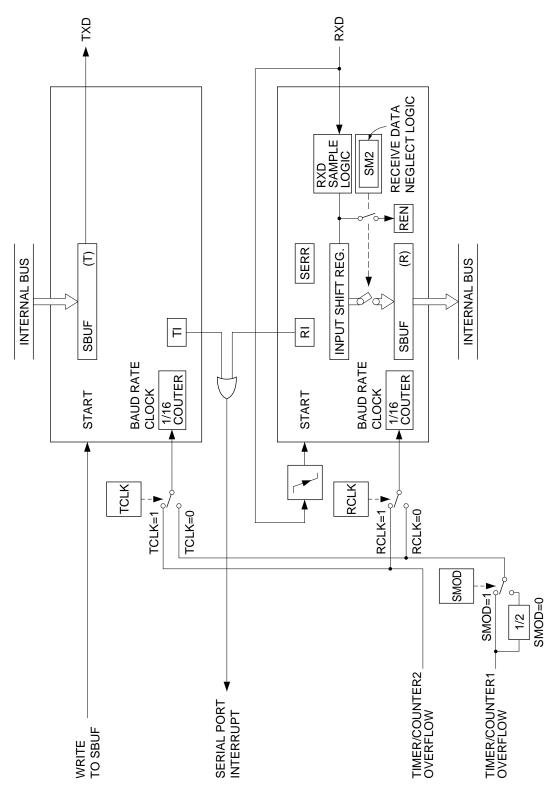

|              | Outline                                                      |                                       |

|              | Mode 1 baud rate                                             |                                       |

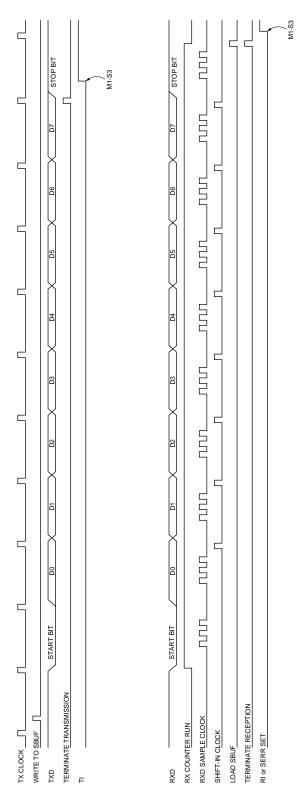

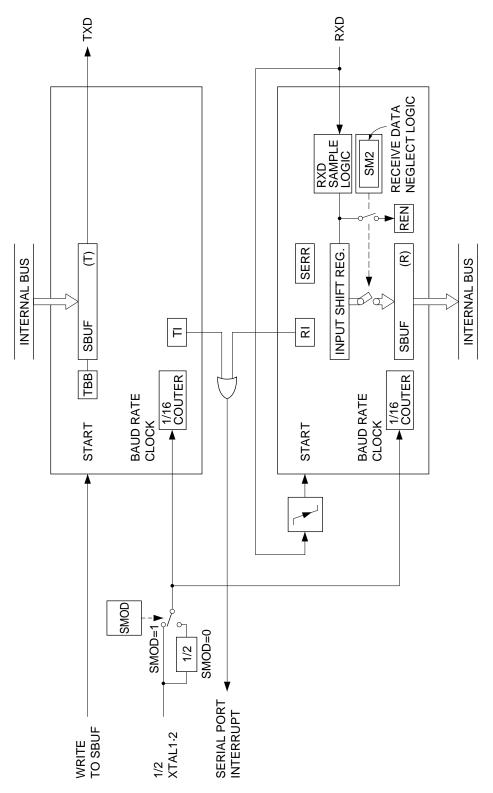

|              | Mode 1 transmit operation                                    |                                       |

|              | Mode 1 receive operation                                     |                                       |

|              | Mode 1 UART error detection                                  |                                       |

|              | de 2                                                         |                                       |

|              | Outline                                                      |                                       |

|              | Mode 2 baud rate                                             |                                       |

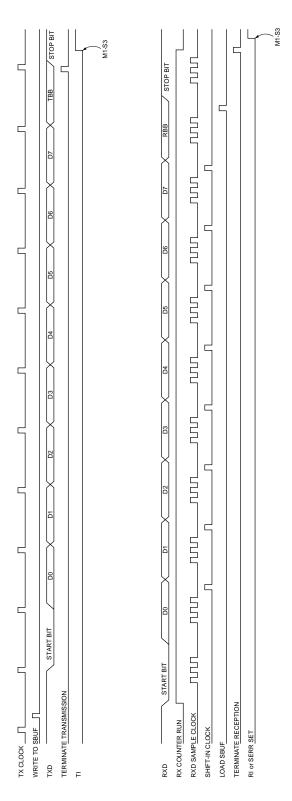

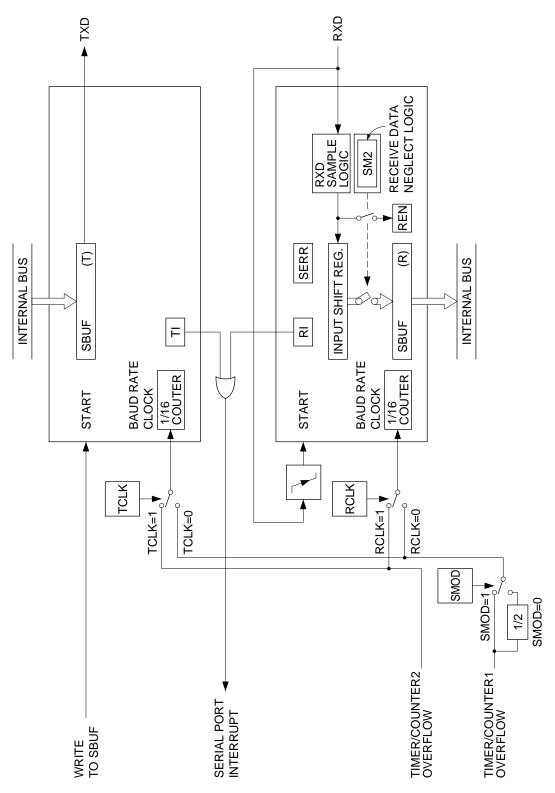

|              | Mode 2 transmit operation                                    |                                       |

|              | Mode 2 receive operation                                     |                                       |

|              | Mode 2 UART error detection                                  |                                       |

|              | de 3                                                         |                                       |

|              | Outline                                                      |                                       |

|              | Mode 3 baud rate                                             |                                       |

|              | Mode 3 transmit operation                                    |                                       |

|              | Mode 3 receive operation.                                    |                                       |

|              | Mode 3 UART error detection                                  |                                       |

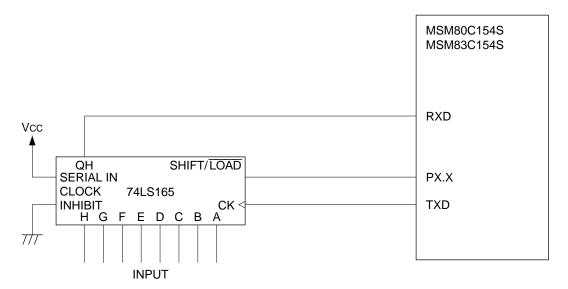

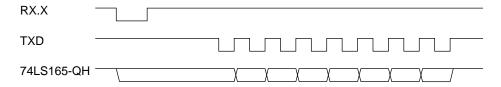

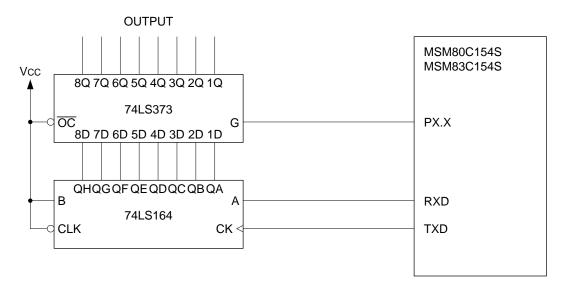

|              | port application examples                                    |                                       |

|              | extension                                                    |                                       |

|              |                                                              | · · · · · · · · · · · · · · · · · · · |

|    | 4.6.4.2 Multi-processor systems                                               | 128 |

|----|-------------------------------------------------------------------------------|-----|

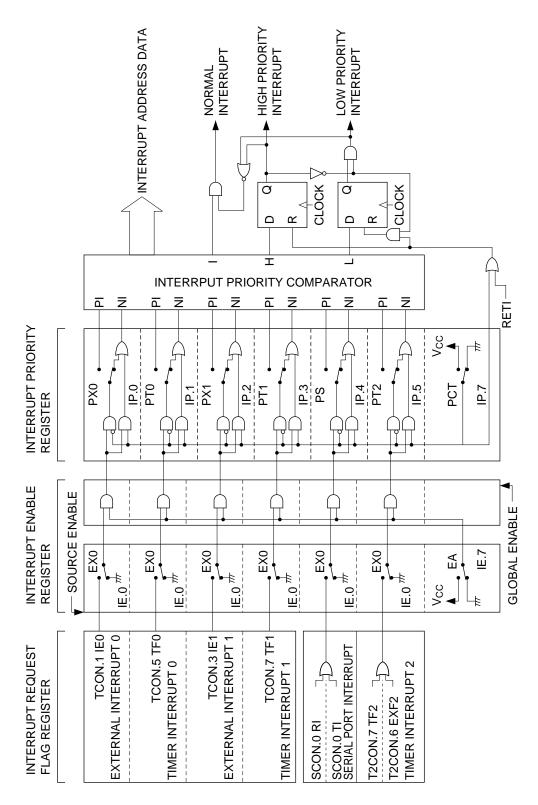

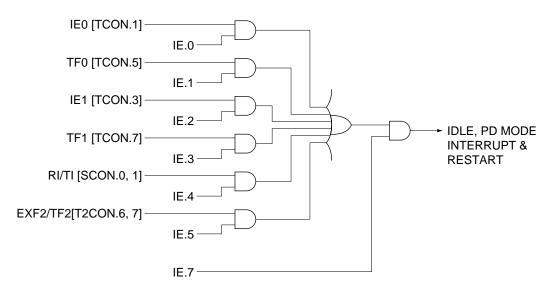

|    | 4.7 Interrupt                                                                 | 129 |

|    | 4.7.1 Outline                                                                 | 129 |

|    | 4.7.2 Interrupt enable register (IE)                                          | 131 |

|    | 4.7.3 Interrupt priority register (IP)                                        | 132 |

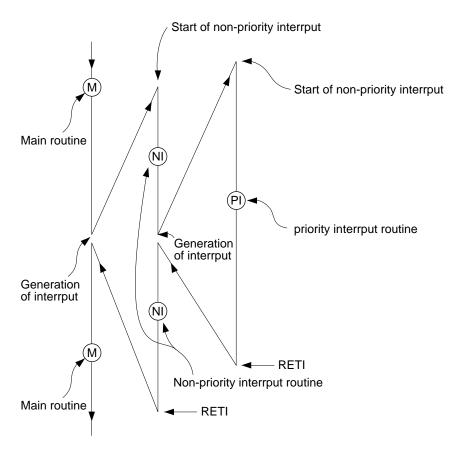

|    | 4.7.3.1 Priority interrupt routine flow                                       | 133 |

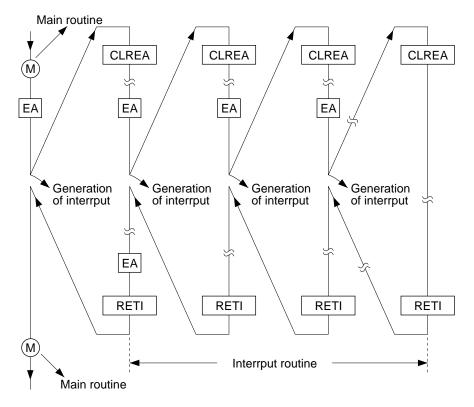

|    | 4.7.3.2 Interrupt routine flow when priority circuit is stopped               | 134 |

|    | 4.7.3.3 Interrupt priority when priority register (IP) contents are all "0"   | 135 |

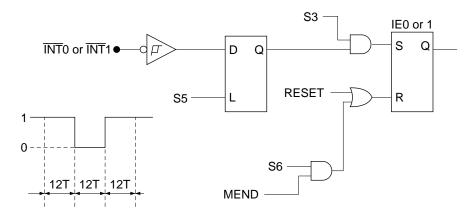

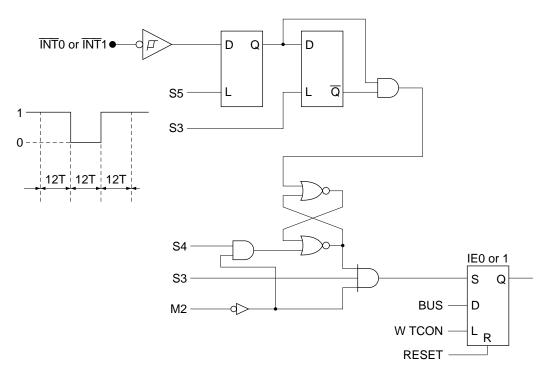

|    | 4.7.4 Detection of external interrupt signals INT0 and INT1                   | 136 |

|    | 4.7.4.1 Outline of INT signal detection                                       | 136 |

|    | 4.7.4.2 External interrupt signal 0 and 1 level detection                     | 136 |

|    | 4.7.4.3 External interrupt signal 0 and 1 trigger detection                   | 137 |

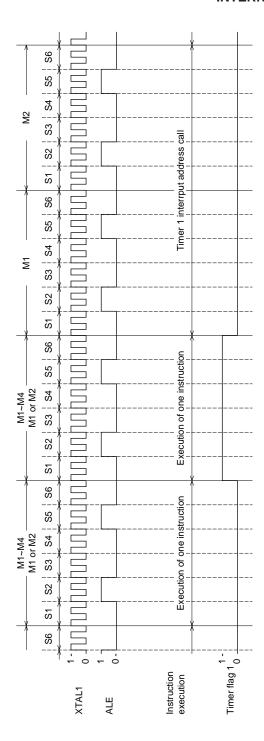

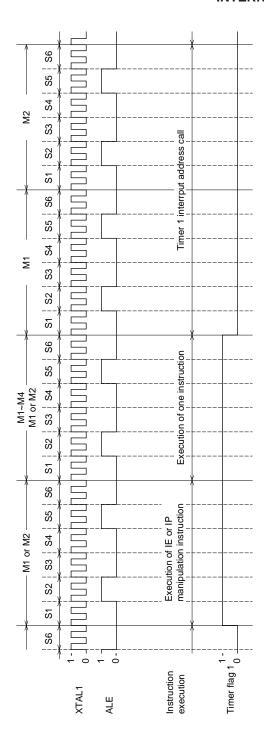

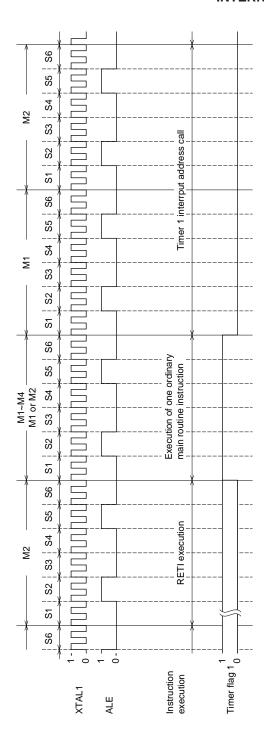

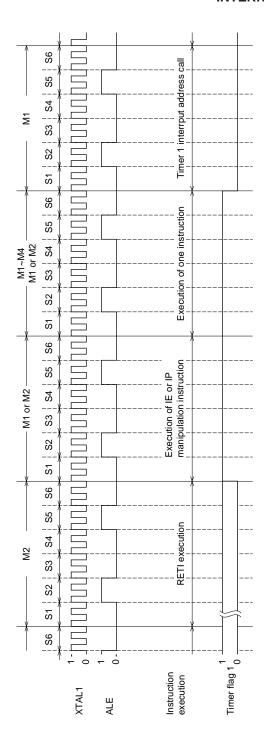

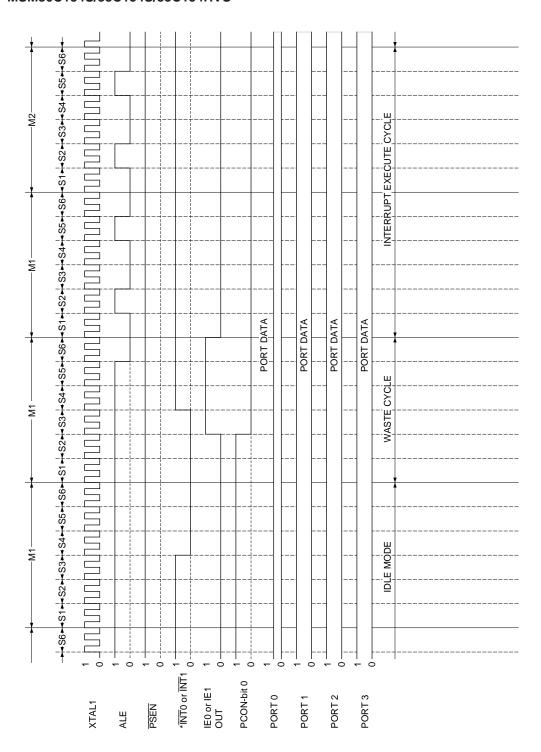

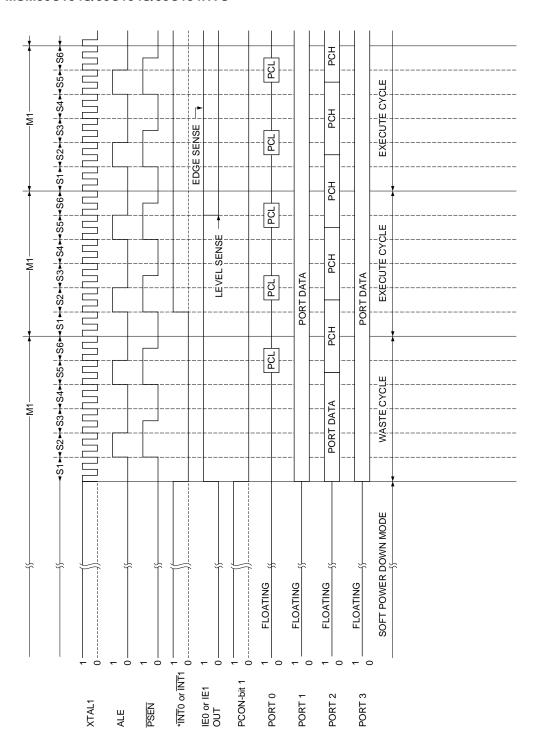

|    | 4.7.5 MSM80C154S/MSM83C154S interrupt response time charts                    | 138 |

|    | 4.7.5.1 Interrupt response time chart when interrupt conditions are satisfied |     |

|    | during execution of ordinary instruction in main routine                      | 138 |

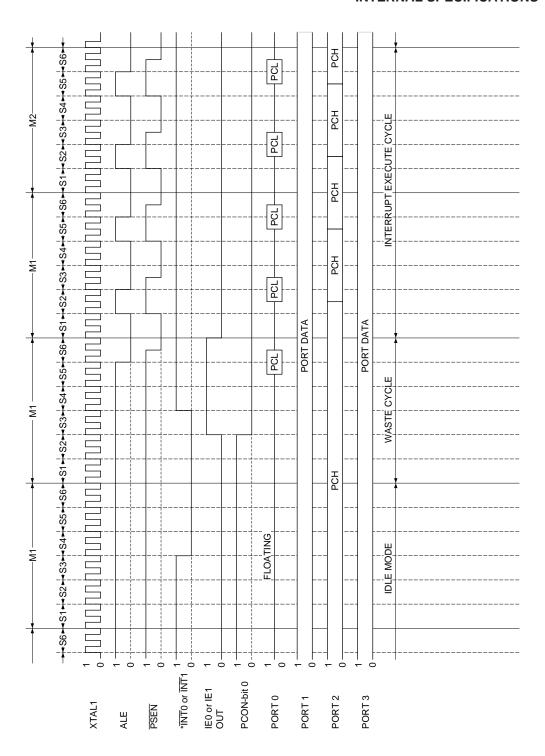

|    | 4.7.5.2 Interrupt response time chart when interrupt conditions are satisfied |     |

|    | during execution of IE or IP register operation instruction in main           |     |

|    | routine                                                                       | 140 |

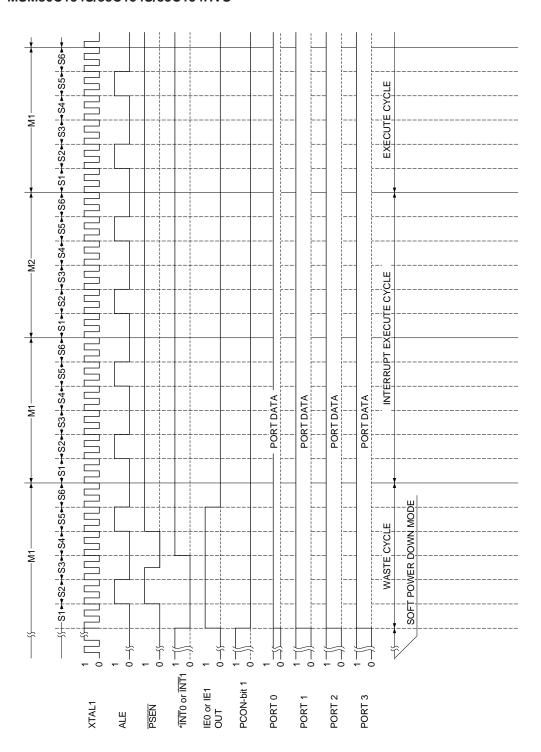

|    | 4.7.5.3 Interrupt response time chart when an ordinary instruction is         |     |

|    | executed after temporarily returning to the main routine from                 |     |

|    | continuous interrupt processing                                               | 142 |

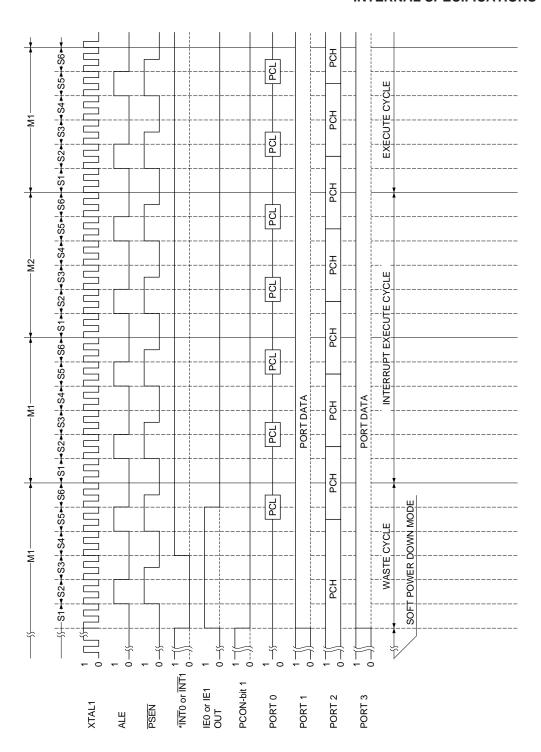

|    | 4.7.5.4 Interrupt response time chart when an IE or IP manipulating           |     |

|    | instruction is executed after temporarily returning to the main               |     |

|    | routine from continuous interrupt processing                                  | 144 |

|    | 4.8 CPU "Power Down"                                                          |     |

|    | 4.8.1 Outline                                                                 |     |

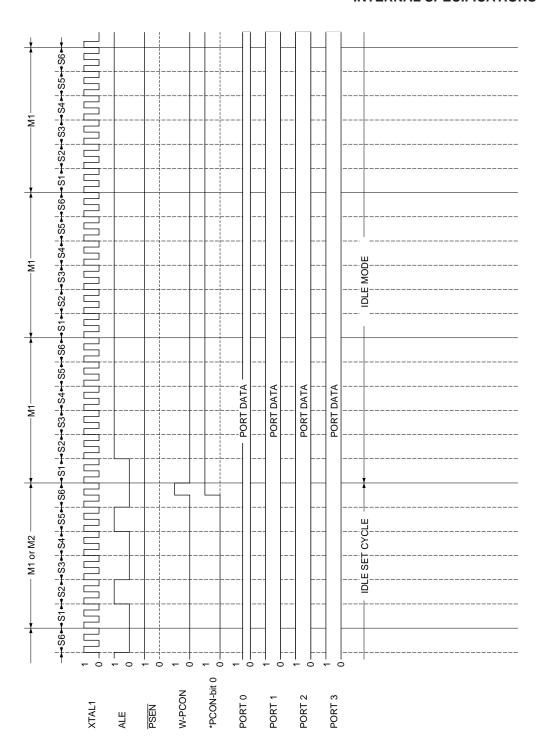

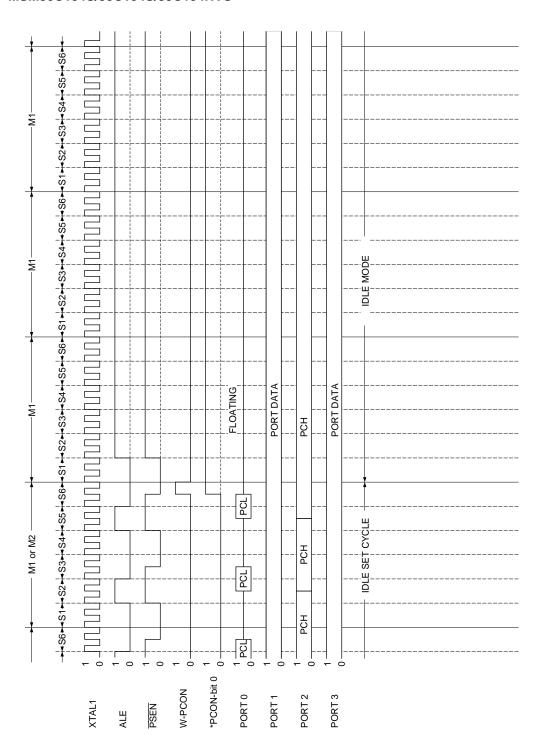

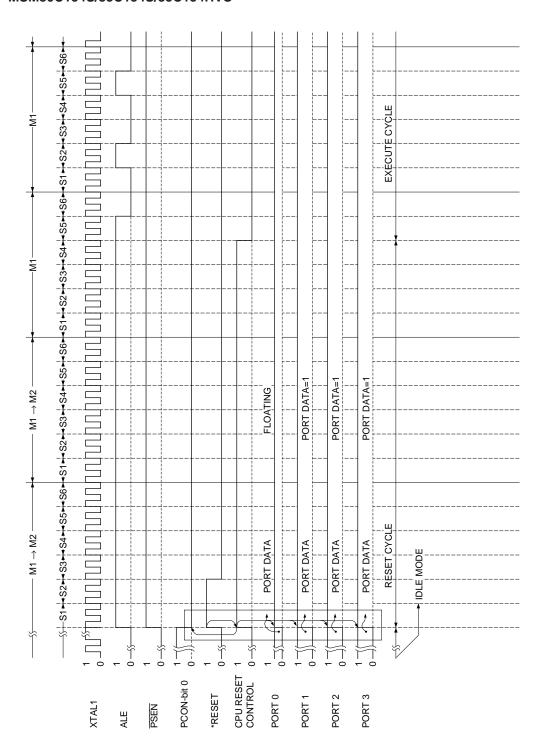

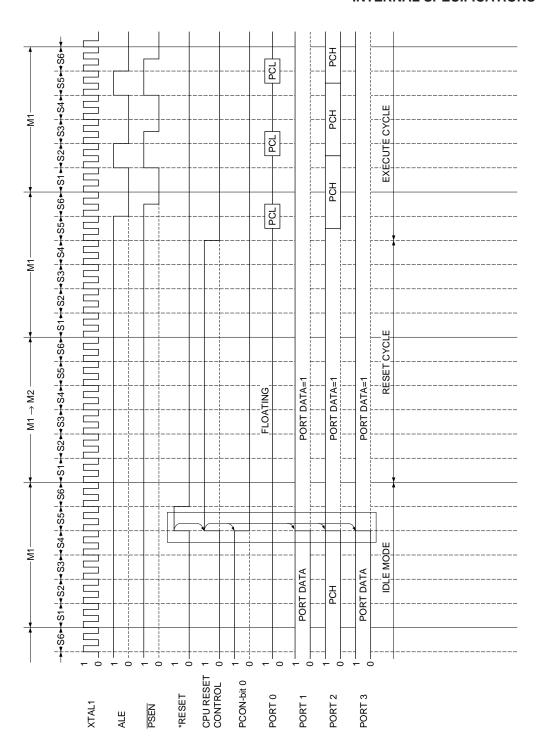

|    | 4.8.2 Idle mode (IDLE) setting                                                | 146 |

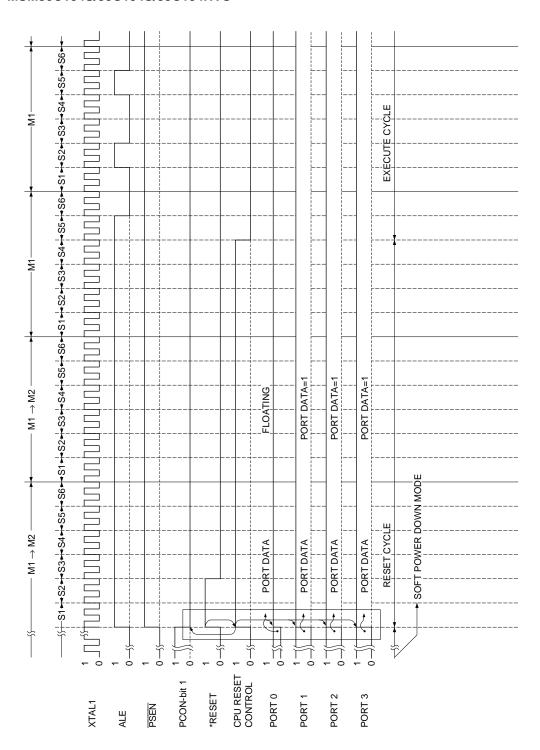

|    | 4.8.3 Soft power down mode (PD) setting                                       |     |

|    | 4.8.3.1 Caution about software power down mode setting                        |     |

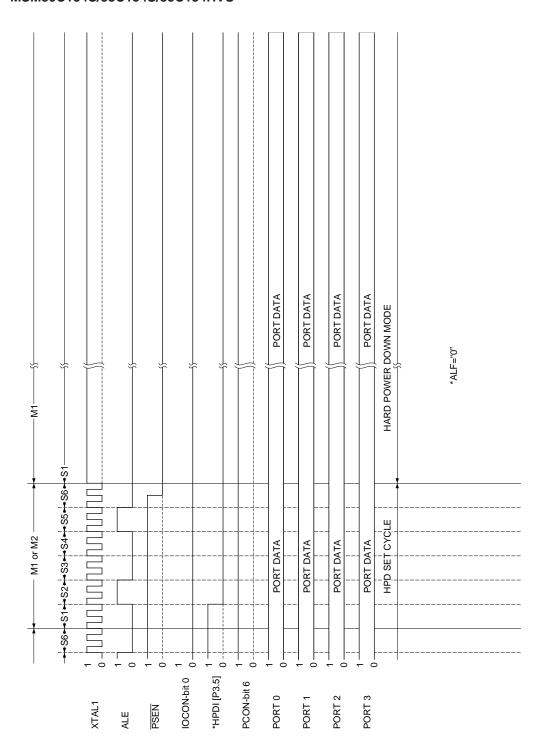

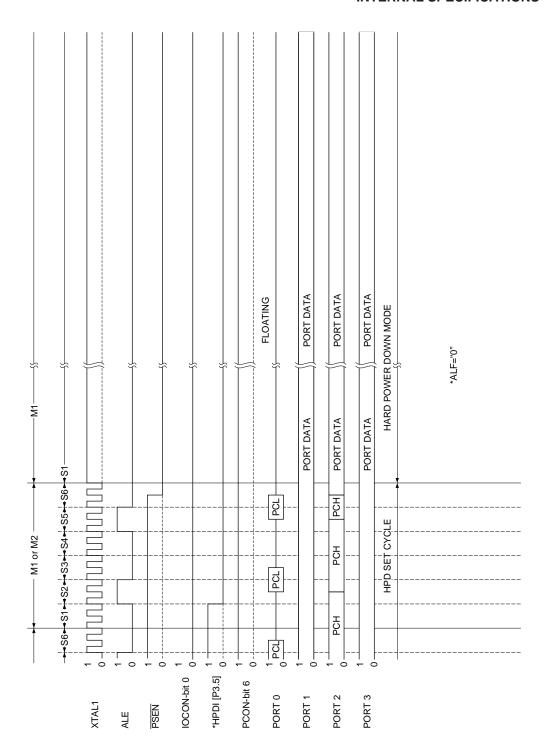

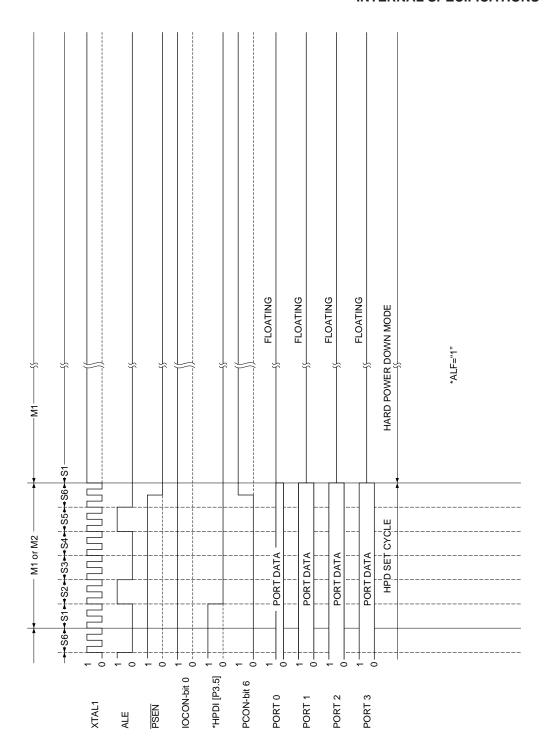

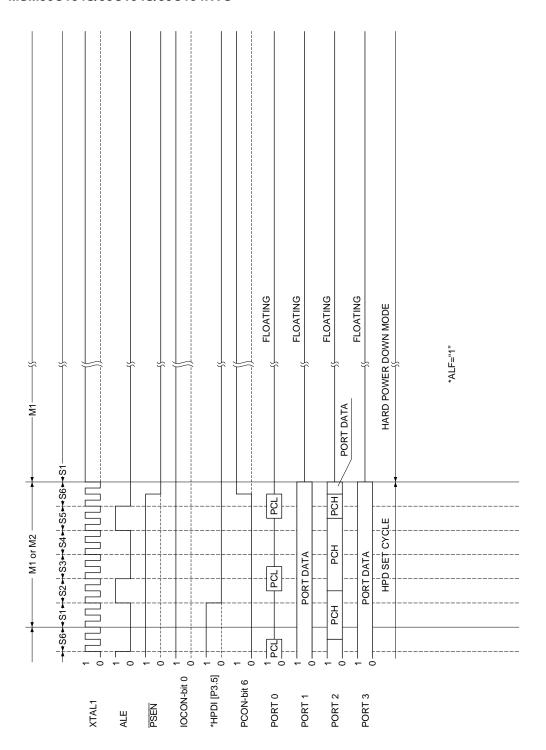

|    | 4.8.4 Hard power down mode (HPD) setting                                      |     |

|    | 4.9 CPU Power Down Mode (IDLE, PD, and HPD) Cancellation (CPU Activation)     |     |

|    | 4.9.1 Outline                                                                 |     |

|    | 4.9.2 Cancellation by CPU resetting (RESET pin)                               | 169 |

|    | 4.9.3 Cancellation of CPU power down mode(IDLE, PD)by interrupt signal        | 176 |

|    | 4.9.3.1 Cancellation of CPU power down mode (IDLE, PD) from interrupt         |     |

|    | address                                                                       | 176 |

|    | 4.9.3.2 Cancellation of CPU power down mode (IDLE, PD) by interrupt           |     |

|    | request signal and restart from next address of stop address                  | 182 |

|    | 4.10 MSM80C154S/83C154S Battery Backup with Hard Power Down Mode              | 187 |

|    |                                                                               |     |

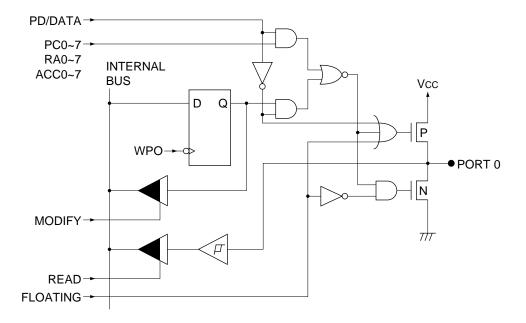

| 5. | INPUT/OUTPUT PORTS                                                            |     |

|    | 5.1 Outline                                                                   | 192 |

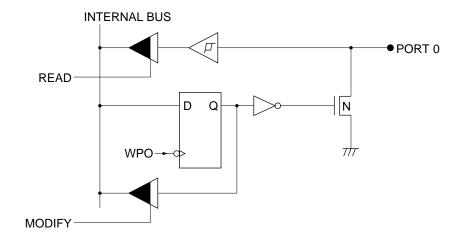

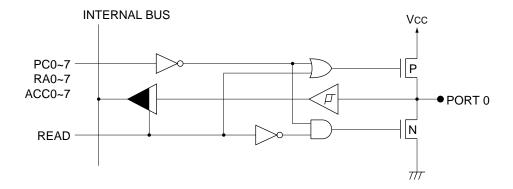

|    | 5.2 Port 0                                                                    | 192 |

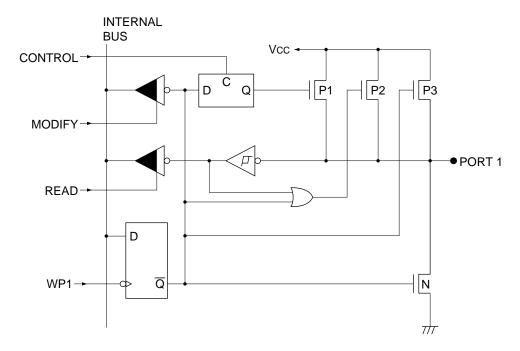

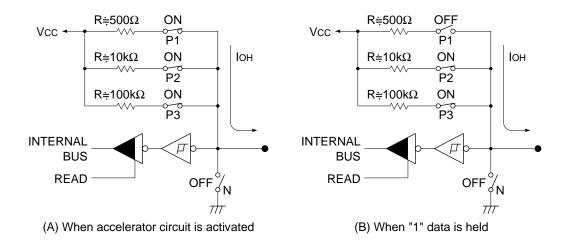

|    | 5.3 Port 1                                                                    |     |

|    | 5.4 Port 2                                                                    |     |

|    | 5.5 Port 3                                                                    | 203 |

|    | 5.6 Port 0, 1, 2, and 3 Output and Floating Status Settings in CPU Power Down |     |

|    | Mode (PD, HPD)                                                                | 205 |

|    |                                                                               |     |

|    | 5.7  | High Impedance Input Port Setting of Each Quasi-bidirectional Port 1, 2, and 3    | 207 |

|----|------|-----------------------------------------------------------------------------------|-----|

|    | 5.8  | 100 kΩ Pull-Up Resistance Setting for Quasi-bidirectional Input Ports 1, 2, and 3 |     |

|    | 5.9  | Precautions When Driving External Transistors by Quasi-bidirectional              |     |

|    |      | Port Output Signals                                                               |     |

|    | 5.10 | Port Output Timing                                                                |     |

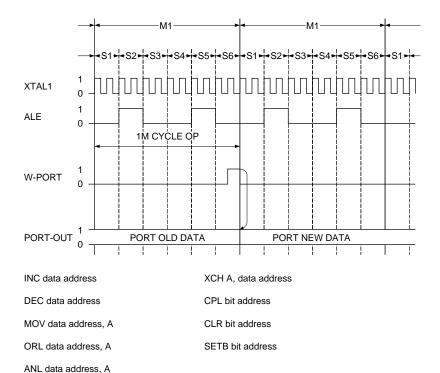

|    |      | 1) One machine cycle instruction output timing                                    |     |

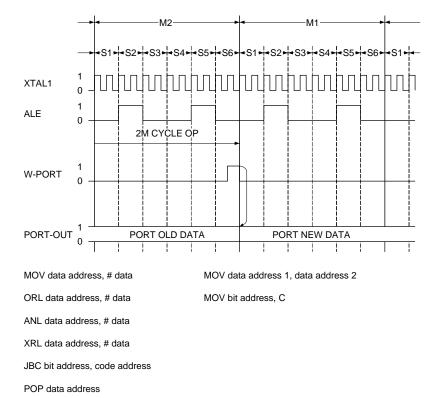

|    |      | 2) Two machine cycle instruction output timing                                    |     |

|    | 5.11 | Port Data Manipulating Instructions                                               | 212 |

| 6. | FLE  | CTRICAL CHARACTERISTICS                                                           |     |

| ٥. | 6.1  | Absolute Maximum Ratings                                                          | 216 |

|    | 6.2  | Operational Ranges.                                                               |     |

|    | 6.3  | DC Characteristics                                                                |     |

|    | 6.4  | External Program Memory Access AC Characteristics                                 |     |

|    | 6.5  | External Data Memory Access AC Characteristics                                    |     |

|    | 6.6  | Serial Port (I/O Extension Mode) AC Characteristics                               |     |

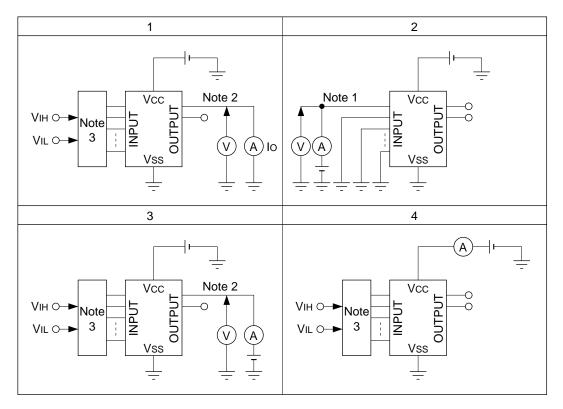

|    | 6.7  | AC Characteristics Measuring Conditions                                           |     |

|    |      | XTAL1 External Clock Input Waveform Conditions                                    |     |

| _  | 5-6  |                                                                                   |     |

| 7. |      | SCRIPTION OF INSTRUCTIONS                                                         |     |

|    | 7.1  | Outline                                                                           |     |

|    | 7.2  | Description of Instruction Symbols                                                |     |

|    |      | List of Instructions.                                                             |     |

|    | 7.4  | Simplified Description of Instructions                                            |     |

|    | 7.5  | Detailed Description of MSM80C154S/MSM83C154S Instructions                        | 246 |

# 1. INTRODUCTION

#### 1. INTRODUCTION

#### 1.1 MSM80C154S/MSM83C154S/MSM85C154HVS Outline

MSM80C154S/MSM83C154S/MSM85C154HVS are single-chip 8-bit fully static microcontrollers featuring high performance and low power consumption. All MSM80C31F/MSM80C51F instructions and functions have been retained.

Apart from being without the internal program memory (ROM), MSM80C154S is identical to MSM83C154S. And the difference between MSM85C154HVS and MSM83C154S is that the internal program memory (ROM) in MSM83C154S is replaced by an external ROM connected to MSM85C154HVS by using a piggy-back package.

While the MSM83C154S microcontroller integrates a 16384-word  $\times$  8-bit program memory (ROM) in a single chip, MSM80C154S/MSM83C154S/MSM85C154HVS all feature computer functions including a 256-word  $\times$  8-bit data memory (RAM), 32 input/ output ports, three 16-bit timer/counters, six interrupts, serial I/O, an 8-bit parallel processing circuit, and a clock generator.

The internal operation in these CPUs is based on an instruction code address method for greater efficiency. In this method, operations are specified in the instruction code (OP) section, and the objective registers are specified by part of that instruction code and the second or third byte following the code. A feature of this method is the ability to achieve several operations by simply changing the manipulation register designation in a single instruction code.

Inclusion of 8-bit multiplication and division instructions further increases the processing capacity of these CPUs.

In addition to expansion of the bit processing area, a comprehensive range of bit processing instructions has also been included. Processing operations include logical processing of the carry flag and specified bit within each register, transfer between the carry flag and specified bit in certain registers, transfer of specified bits between different registers, setting, resetting, and complement of the specified bit in each register, and execution of various bit tests within a wide area.

To make a relative jump after the execution of a bit test instruction, jumps can be made within a wide address range between –128 and +127 relative to the address of the instruction and there is no page field restriction.

The contents of specified registers can be saved in stack by using the PUSH instruction, and the saved contents can be returned from stack to a specified register by the POP instruction. Absolute interrupt priority can be allocated to any interrupt when in priority circuit operation mode. And by controlling only the interrupt enable register (IE) when in priority circuit stop mode, multi-level interrupt processing can be executed to make interrupt processing much easier than in conventional CPUs.

Employing the low-power consumption feature of C-MOS devices, these CPUs are designed to operate in a number of "CPU power down" modes. In idle mode the IDL bit in the power control register (PCON) is set to "1" to halt CPU operations while the oscillator continues to run. In soft power down mode the PD bit in the power control register is set to "1" to halt CPU operations as well as the oscillator. And in hard power down mode where the HPD bit in the power control register is set in advance to "1", CPU operations and the oscillator are stopped if the HPDI pin (P3.5) power failure detect signal level is changed from "1" to "0". CPU power down modes can be cancelled by resetting the CPU via reset pin and restarting execution from address 0, by restarting execution from the relevant interrupt address, or by resuming

execution from the next address after the stop address where CPU power down mode was activated.

Each of the quasi-bidirectional ports 1, 2, and 3 can be set independently as high impedance input ports. And the 10 k $\Omega$  pull-up resistance for these input ports can be isolated from the power supply (Vcc), leaving only the 100 k $\Omega$  pull-up resistance and thereby enabling the quasi-bidirectional ports to be driven by devices with low drive capacity. Furthermore, the outputs of ports, 0, 1, 2, and 3 can be switched to floating status during CPU power down modes (PD, HPD).

Three built-in 16-bit timer/counters capable of operating in a wide range of modes enable the CPUs to be used in many different ways. And since timer/counters 0 and 1 can be operated by external clock during CPU power down modes (PD, HPD) where the oscillator is stopped, these two counters can also be used in cancelling CPU power down modes.

UART based serial communication can be executed at any baud rate by carry signal from timer/counter 1 or timer/counter 2.

If an overrun or framing error is generated during data reception, the SERR bit in the I/O control register is set. And by testing this SERR bit, the accuracy of the data can be checked quite easily to ensure correct serial communication.

As can be seen, these CPUs are equipped with a very comprehensive range of functions. Also note that EASE80C51mkII is available for use as the program development support system for these CPUs.

Equipped with the MSM85C154E dedicated evachip, EASE80C51mkII is capable of program area mapping, realtime tracing, generating breaks according to accumulator contents, and various other functions designed for accurate and efficient support of program development of these CPUs.

With this great line-up of functions and with EASE80C51mkII capable of developing programs in a very short time, MSM80C154S/MSM83C154S/MSM85C154HVS give a highly integrated high performance solution.

#### 1.2 MSM80C154S/MSM83C154S Features

- Full static circuitry

- Internal program memory (ROM) 16384 words × 8 bits (MSM83C154S)

- External program memory (ROM)

Connectable up to 64K bytes

- Internal data memory (RAM)

256 words × 8 bits

- External data memory (RAM)

Connectable up to 64K bytes

- Four sets of working registers (R0 thru R7 × 4)

- Stack

Free use of 256-word × 8-bit internal data memory area

- Four input/output ports (8-bit × 4)

- Serial ports (UART operation)

- Six types of interrupts

- (1) Two external interrupts

- (2) Three timer interrupts

- (3) One serial port interrupt

- \* Priority allocated interrupt processing

- \* Multi-level interrupt processing by software management

- CPU power down function

- (1) Idle mode: CPU stopped while oscillation continued.

(Software setting)

(2) PD mode: CPU and oscillation all stopped.

(Software setting)

(Setting I/O ports to floating status possible)

(3) HPD mode: CPU and oscillation all stopped.

(Hardware setting)

(Setting I/O ports to floating status possible)

- CPU power down mode cancellation

- (1) Execution commenced from address 0 by CPU resetting.

(IDLE, PD, and HPD mode cancellation)

- \* RESET pin is used

- (2) Execution from interrupt address by interrupt request, or execution resumed from next address after the stop address. (IDLE and PD mode cancellation)

- \* External, timer, and serial port interrupts

- I/O control registers (0F8H)

- bo: Port 0, 1, 2, and 3 floating setting (PD, HPD)

- b1: Port 1 high impedance input port setting

- b2: Port 2 high impedance input port setting

- b3: Port 3 high impedance input port setting

- b4: Port 1, 2, and 3 pull-up resistance switching (10 k $\Omega$  pull-up resistance switch off to leave only 100 k $\Omega$ )

- b5: Serial port reception error detector bit

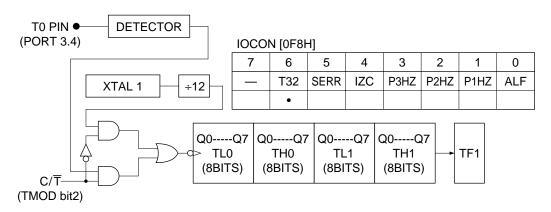

- b6: 32-bit timer mode setting (TL0+TH0+TL1+TH1)

- Timer/counters (three 16-bit timer/counters)

- (1) 8-bit timer with 5-bit prescalar

- (2) 16-bit timer

- (3) 8-bit timer with 8-bit auto-reloader

- (4) 8-bit separate timer

- (5) 16-bit timer with 16-bit auto-reloader

- (6) 16-bit capture timer

- (7) 16-bit baud rate generator timer

- (8) 32-bit timer

- Wide operating temperature range -40 to +85°C

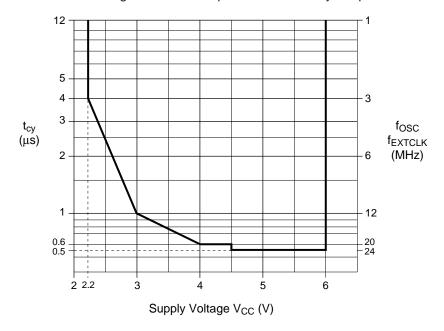

- Wide operating voltage range

- (1) When operating: VCC=+2.2 to 6V (varies according to frequency)

- (2) When stopped:

- VCC=+2 to +6V (PD or HPD mode)

- · Instruction execution cycle

- (1) 2-byte 1-machine cycle instructions

- (2) Multiplication/division instructions

- Direct initialization of ports 0, 1, 2, and 3 by input of reset signal even if oscillator have been stopped.

(All ports output "1".)

- High noise margin (with Schmitt trigger input for each I/O)

- 40-pin plastic DIP/44-pin plastic flat package/44-pin plastic PLCC/44/pin plastic TQFP

- Software compatibility with MSM80C31F and MSM80C51F

#### 1.3 Additional Features in MSM80C154S/MSM83C154S/MSM85C154HVS

In addition to the basic operations of MSM80C31F/MSM80C51F, the MSM80C154S/MSM83C154S/MSM85C154HVS devices also include the following functions.

- ROM capacity increased from 4K bytes to 16K bytes

- RAM capacity increased from 128 bytes to 256 bytes

- An additional timer counter 2

- An additional timer interrupt 2

- An additional 8-bit timer 2 control register (T2CON 0C8H)

- An additional 8-bit I/O control register (IOCON 0F8H)

- Addition of two bits (bit 5, PT2 and bit 7, PCT) to the priority register (IP 0B8H)

- Addition of one bit (bit 5, ET2) to the interrupt enable register (IE 0A8H)

- Addition of two bits (bit 5, RPD and bit 6, HPD) to the power control register (PCON 87H) Addition of these extra functions has further increased the performance and widen the range of application of these CPU devices.

# 2. SYSTEM CONFIGURATION

#### 2. SYSTEM CONFIGURATION

#### 2.1 MSM80C154S/MSM83C154S/MSM85C154HVS Logic Symbols

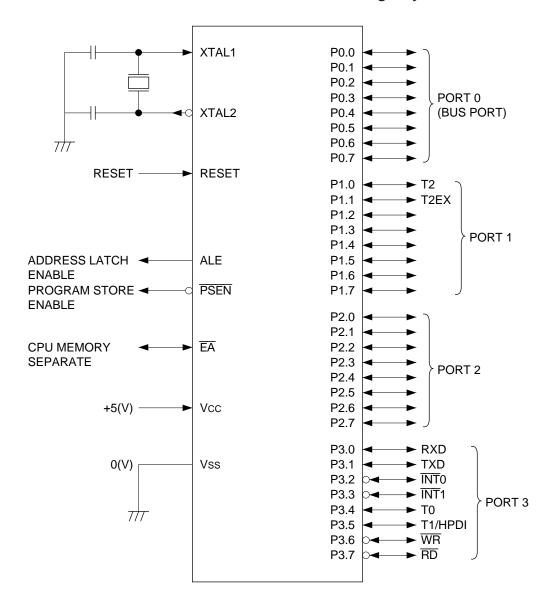

Figure 2-1 MSM80C154S/83C154S/85C154HVS logic symbols

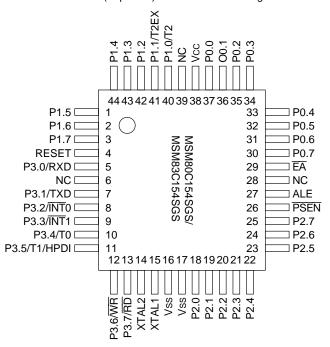

#### 2.2 MSM80C154S/MSM83C154S pin layouts

MSM80C154SRS/MSM83C154SRS (Top View) 40 Pin Plastic DIP

|                 |                           | h., .   |

|-----------------|---------------------------|---------|

| P1.0/T2 1       |                           | 40 Vcc  |

| P1.1/T2EX 2     |                           | 39 P0.0 |

| P1.2 3          |                           | 38 P0.1 |

| P1.3 4          | _                         | 37 P0.2 |

| P1.4 5          |                           | 36 P0.3 |

| P1.5 6          | Ž                         | 35 P0.4 |

| P1.6 7          | 306                       | 34 P0.5 |

| P1.7 8          | 21.                       | 33 P0.6 |

|                 | 54                        |         |

| RESET 9         | Ω<br>Z                    | 32 P0.7 |

| P3.0/RXD 10     | õ                         | 31 EA   |

| P3.1/TXD 11     | Ž.                        | 30 ALE  |

| P3.2/INT0 12    | Š                         | 29 PSEN |

| P3.3/INT1 13    | MSM80C154SRS/MSM83C154SRS | 28 P2.7 |

| P3.4/T0 14      | $\overline{\mathcal{C}}$  | 27 P2.6 |

| P3.5/T1/HPDI 15 | 54                        | 26 P2.5 |

| P3.6/WR 16      | S                         | 25 P2.4 |

| P3.7/RD 17      | õ                         | 24 P2.3 |

| XTAL2 18        |                           | 23 P2.2 |

|                 |                           |         |

| XTAL1 19        |                           | 22 P2.1 |

| Vss <u>20</u>   |                           | 21 P2.0 |

|                 |                           |         |

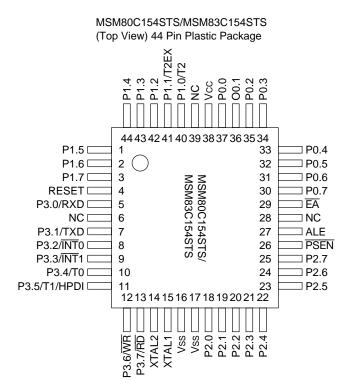

MSM80C154SGS/MSM83C154SGS (Top View) 44 Pin Plastic Package

#### SYSTEM CONFIGURATION

Figure 2-2 MSM80C154S/MSM83C154S pin layout (top view)

## **Applicable Packages**

| 40-Pin Plastic DIP (DIP40-P-600-2.54)         | MSM80C154S RS<br>MSM83C154S-XXX RS       |

|-----------------------------------------------|------------------------------------------|

| 44-Pin Plastic QFJ (QFJ44-P-S650-1.27)        | MSM80C154S JS<br>MSM83C154S-XXX JS       |

| 44-Pin Plastic QFP (DFP44-P-910-0.80-2K)      | MSM80C154S GS-2K<br>MSM83C154S-XXX GS-2K |

| 44-Pin Plastic TQFP (TQFP44-P-1010-0.80-K)    | MSM80C154S TS-K<br>MSM83C154S-XXX TS-K   |

| 40-Pin Ceramic Piggy Back (ADIP40-C-600-2.54) | MSM85C154HVS                             |

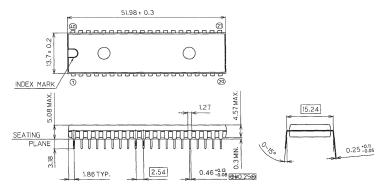

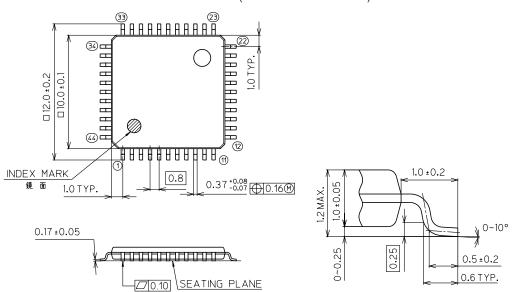

#### 2.2.1 MSM80C154S/MSM83C154S external dimensions

#### MSM80C154SRS/MSM83C154SRS

40-pin Plastic DIP (DIP40-P-600-2.54)

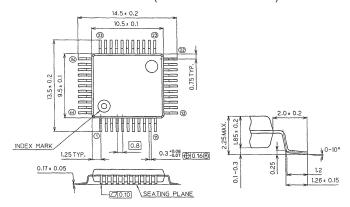

#### MSM80C154SGS/MSM83C154SGS

44-Pin Plastic QFP (QFP44-P-910-0.80-2K)

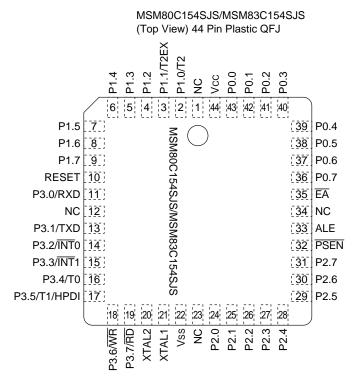

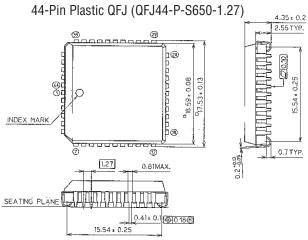

#### MSM80C154SJS/MSM83C154SJS

Figure 2-3 MSM80C154S/MSM83C154S external dimensions

#### MSM80C154STS/MSM83C154STS

44-Pin Plastic TQFP (TQFP44-P-1010-0.80-K)

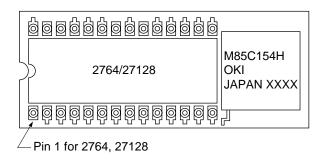

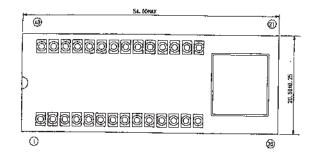

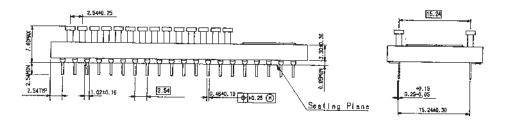

#### 2.2.2 MSM85C154HVS pin layout and external dimensions

- \* The MSM85C154HVS pin layout of bottom side is the same as the pin layout for MSM83C154SRS.

- \* The 27C64/128 device should be used for EPROM.

#### 40-Pin Ceramic Piggy Back (ADIP40-C-600-2.54)

Figure 2-4 MSM85C154HVS pin layout and external dimensions

#### W2W80C124S/83C124S/82C124HA2

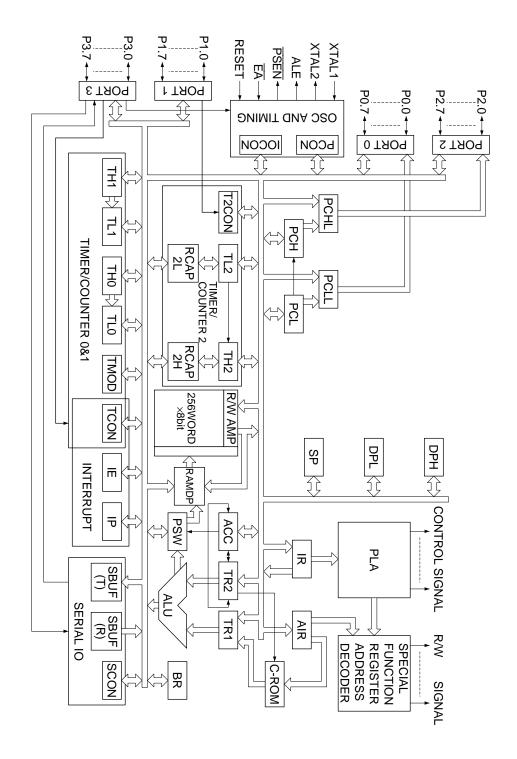

## 2.3 MSM80C1545 Block Diagram

Figure 2-5 MSM80C154S block diagram

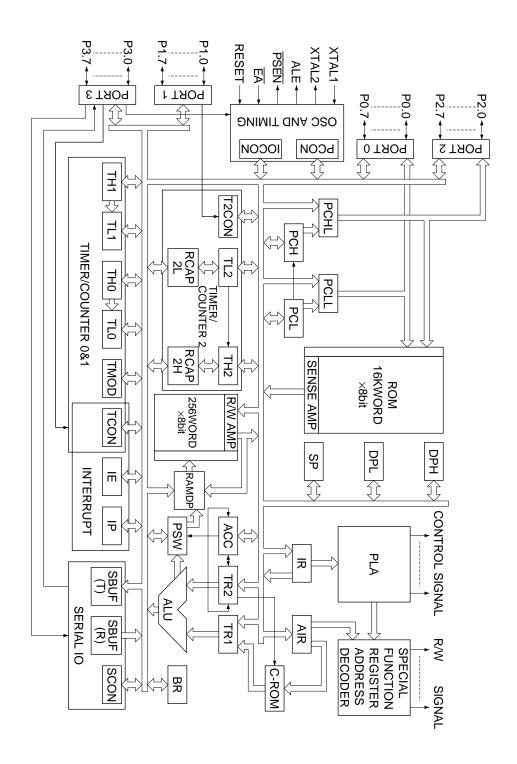

#### 2.4 MSM83C154S Block Diagram

Figure 2-6 MSM83C154S block diagram

#### W2W80C124S/83C124S/82C124HA2

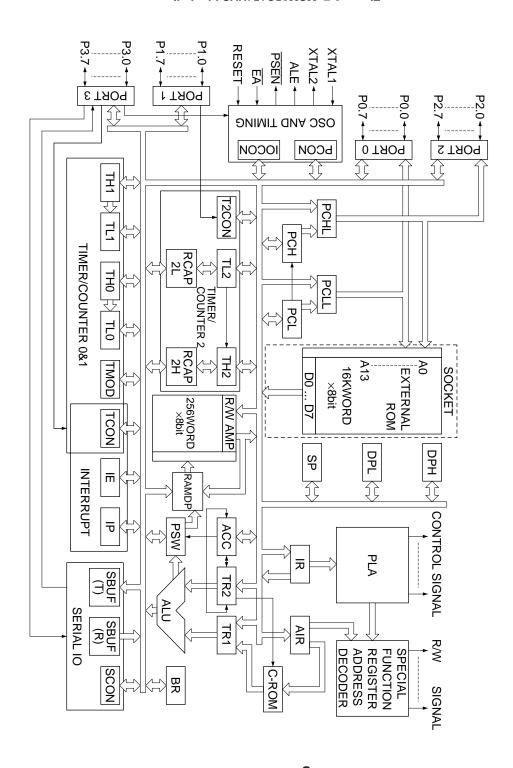

# 2.5 MSM85C154HVS Block Diagram

Figure 2-7 MSM85C154HVS block diagram

#### 2.6 Timing and Control

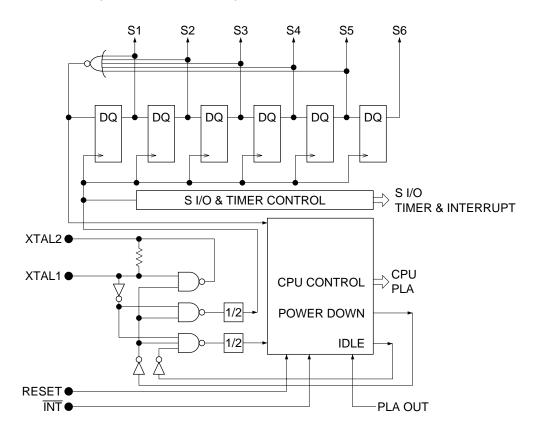

#### 2.6.1 Outline of MSM80C154S/MSM83C154S timing

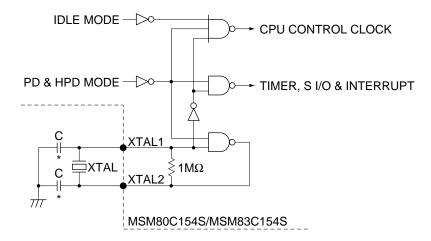

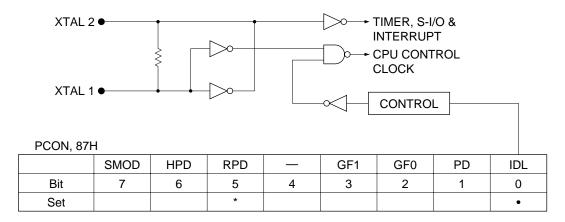

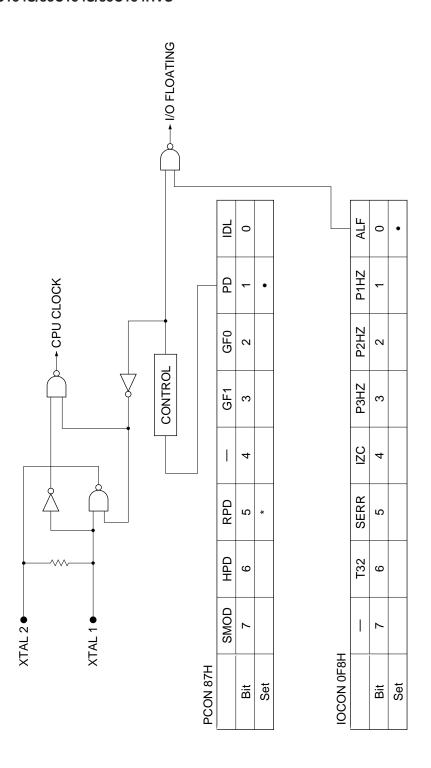

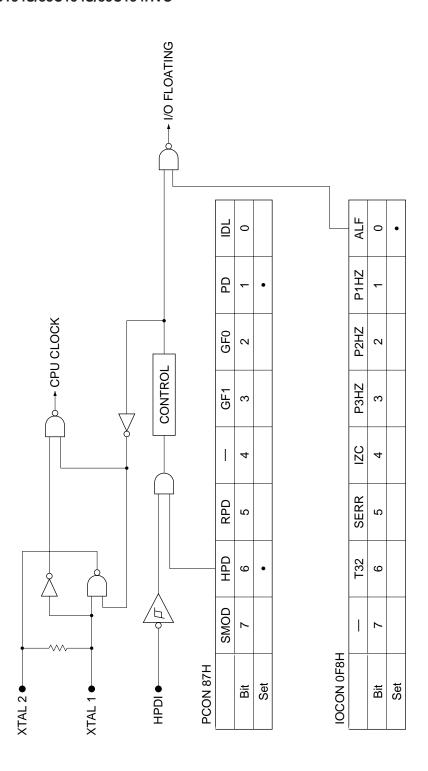

The MSM80C154S/MSM83C154S devices are both equipped with a built-in oscillation inverter (see Figure 2-8) for use in the generation of clock pulses by external crystal or ceramic resonator. These clock pulses are passed to the timing counter and control circuits where the basic timing and control signals required for internal control purposes are generated.

The basic timing consists of state 1 (S1) thru state 6 (S6) (see Figure 2-9) where each state cycle is based on two XTAL1·2 fundamental clock pulses. The interval from S1 thru S6 forms a single machine cycle with a total of 12 fundamental clock pulses. 1-byte 1-machine cycle and 2-byte 1-machine cycle instructions are fetched into the instruction register during M1·S1, decoded during M1·S2, and executed during M1·S3 thru M1·S6. The second byte is fetched during M1·S4. 1-byte 2-machine cycle, 2-byte 2-machine cycle, and 3-byte 2-machine cycle instructions are also fetched during M1·S1, decoded during M1·S2, and executed during M1·S3 thru M2·S6. The second and third bytes are fetched during M1·S4, M2·S1, or M2·S4. The number of clocks used is 24. 1-byte 4-machine cycle instructions are involved in multiplication and division operations where 48 clocks are used.

Figure 2-8 Oscillator, timing counter, and control stage block diagram

Figure 2-9 MSM80C154S/MSM83C154S fundamental timing

#### 2.6.2 Major synchronizing signals

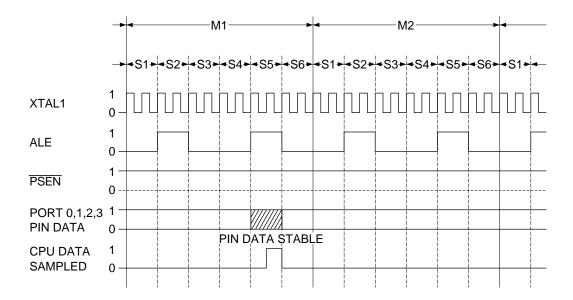

#### (1) ALE (Address Latch Enable)

The ALE signal is used as a clock signal where the address signals 0 thru 7 output from CPU port 0 can be latched externally when external program or external data memory (RAM) is used.

Although two ALE signal outputs are obtained in a single machine cycle during normal operations, no output is obtained during output of the RD/WR signal when an external memory instruction (MOVX......) is executed.

#### (2) PSEN (Program Store Enable)

The PSEN output signal is generated during execution of an external program. The output is obtained when an instruction or data is fetched.

The PSEN signal is valid when at "0" level, and external program data is enabled when in this valid state.

Although two PSEN signal outputs are obtained in a single machine cycle during normal operations, no output is obtained during output of the RD/WR signal when an external data memory instruction (MOVX......) is executed.

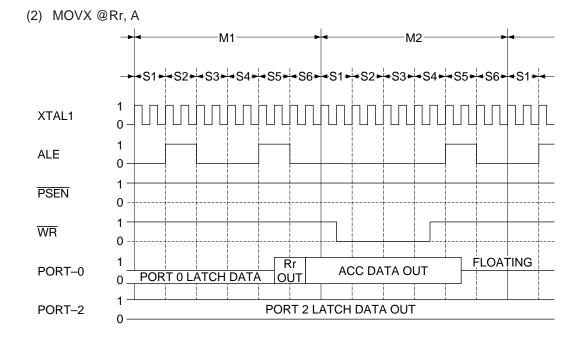

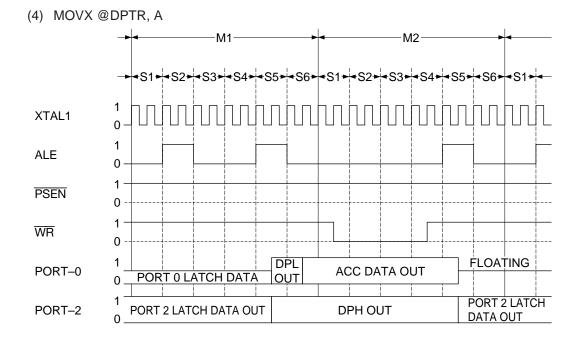

#### (3) WR (Write Strobe)

The WR output signal is obtained when an external data memory instruction (MOVX @Rr, A or MOVX @ DPTR, A) is executed.

CPU port 0 output data is written in the external RAM when the WR signal is at "0" level.

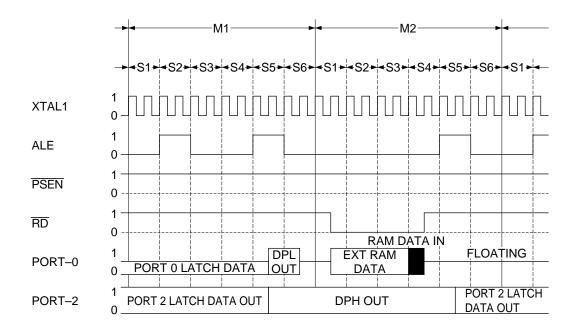

#### (4) RD (Read Strobe)

The  $\overline{\text{RD}}$  output signal is obtained when an external data memory instruction (MOVX A, @ Rr or MOVX A, @ DPTR) is executed.

The external RAM is enabled and output data is passed to CPU port 0 when the  $\overline{\text{RD}}$  signal is at "0" level.

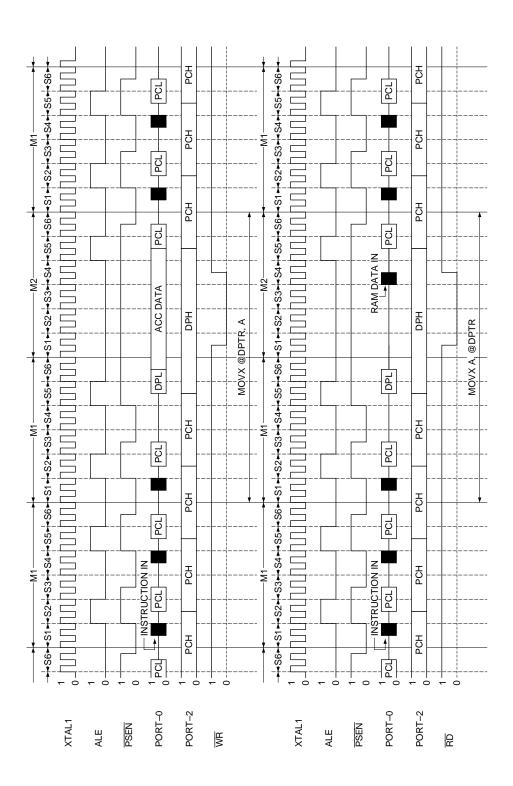

#### 2.6.3 MSM80C154S fundamental operation time charts

Figure 2-10 MSM80C154S external program memory read cycle timing chart

Figure 2-11 MSM80C154S MOVX A, @Rr execution

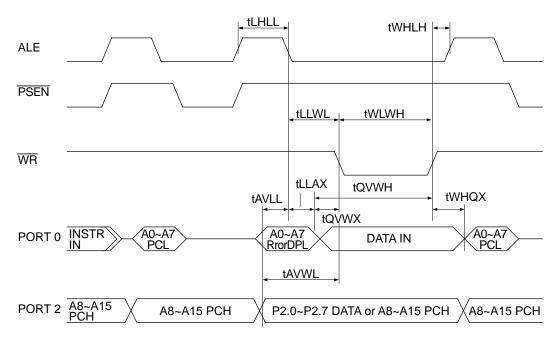

#### (3) MOVX @Rr, A

Figure 2-12 MSM80C154S MOVX @Rr, A execution

Figure 2-13 MSM80C154S MOVX A, @DPTR execution

#### (5) MOVX @DPTR, A

Figure 2-14 MSM80C154S MOVX @DPTR, A execution

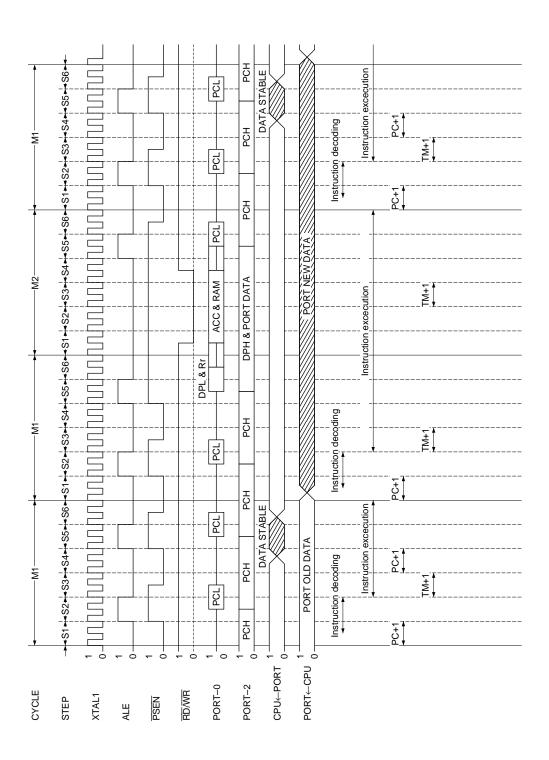

Figure 2-15 MSM80C154S MOV direct, PORT[0, 1, 2, 3] execution

#### 2.6.4 MSM83C154S fundamental operation time charts

Figure 2-16 MSM83C154S MOVX A, @Rr execution

Figure 2-17 MSM83C154S MOVX @Rr, A execution

#### (3) MOVX A, @DPTR

Figure 2-18 MSM83C154S MOVX A, @DPTR execution

Figure 2-19 MSM83C154S MOVX @DPTR, A execution

#### **SYSTEM CONFIGURATION**

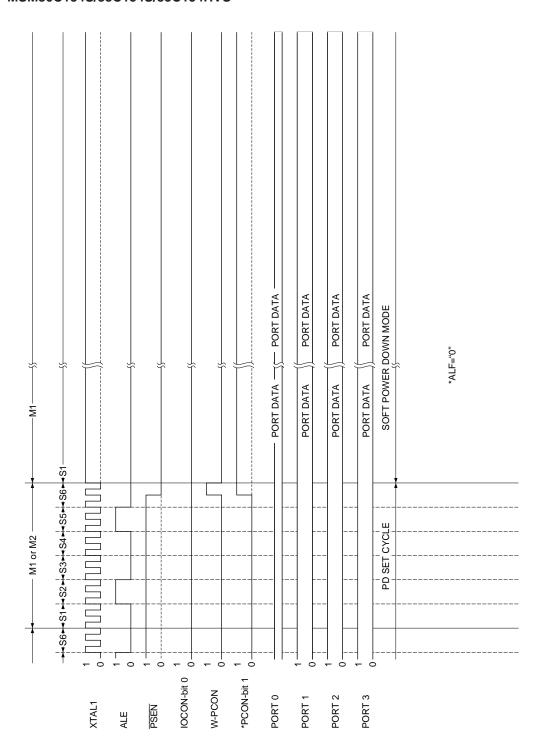

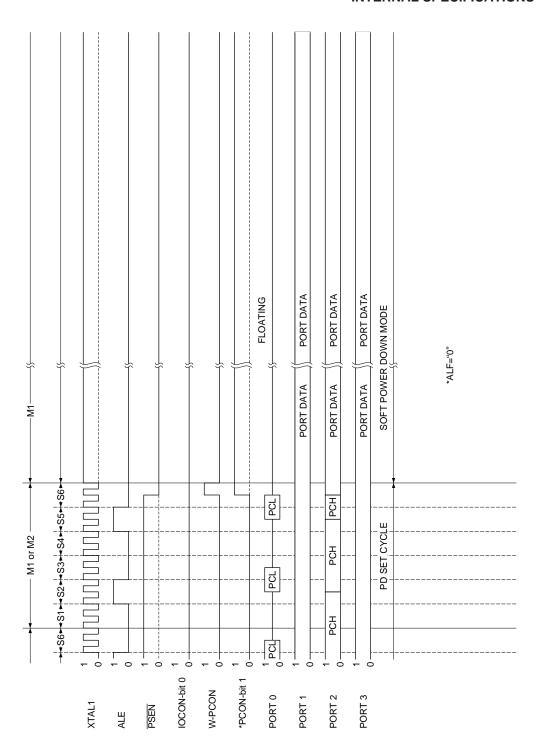

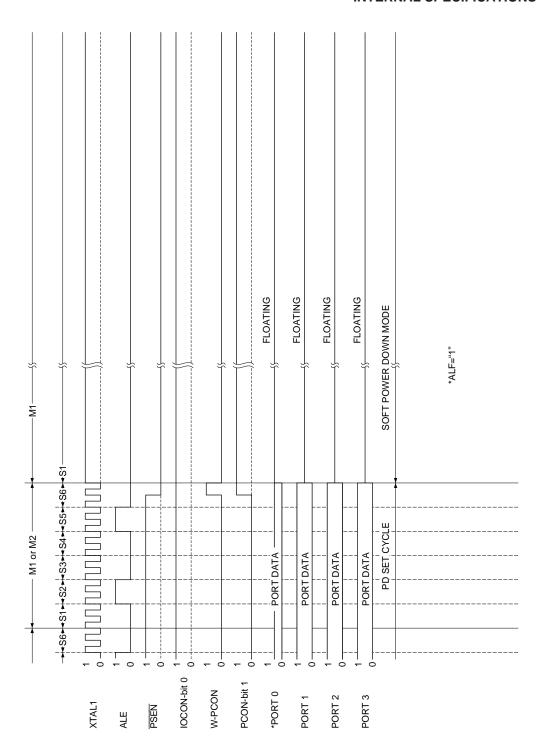

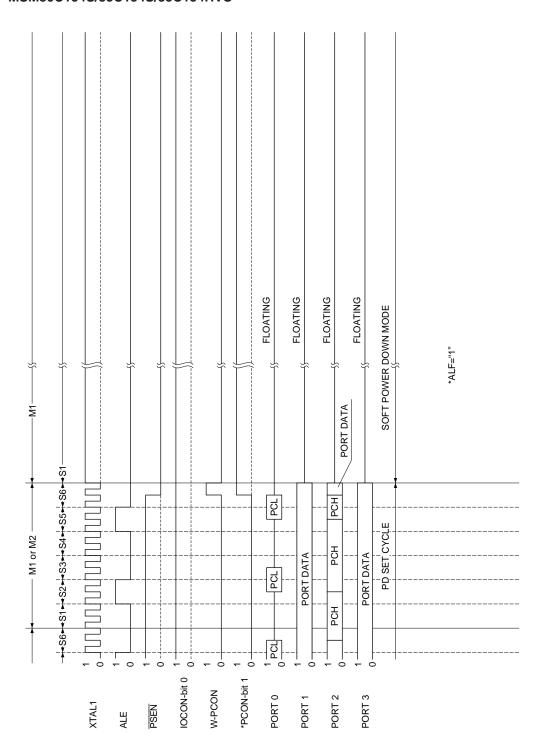

#### (5) MOV direct, PORT [0, 1, 2, 3] execution

Figure 2-20 MSM83C154S MOV direct, PORT[0, 1, 2, 3] execution

#### 2.7 Instruction Register (IR) and Instruction Decoder (PLA)

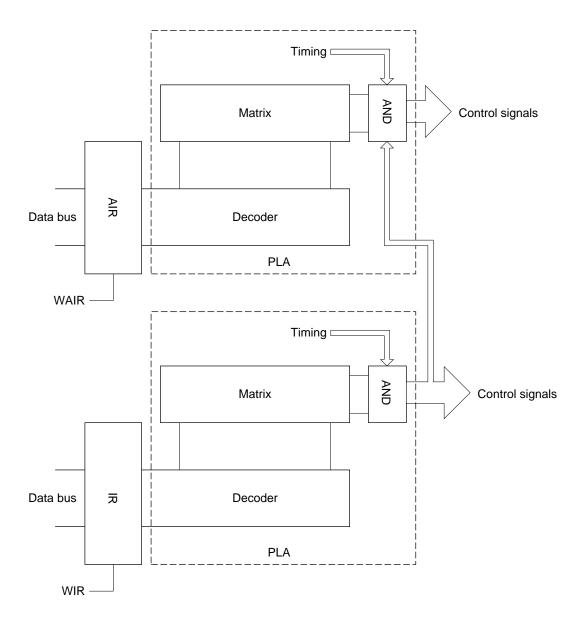

MSM80C154S/MSM83C154S operations are based on an instruction code address method. Hence, in addition to the instruction code instruction register (IR) and instruction decoder (PLA), these devices also include an instruction register (AIR) and register manipulation decoder (PLA) for data addresses and bit addresses.

Operation codes are passed to the IR, and data and bit addresses are passed to the AIR. CPU control signals are formed at the respective PLA for each instruction register, thereby activating the CPU. The block diagram is outlined in Figure 2-21.

Figure 2-21 IR and PLA block diagram

#### 2.8 Arithmetic Operation Section

#### (1) Outline

The MSM80C154S/MSM83C154S arithmetic operation section consists of

- (1) an arithmetic operation instruction decoder, and

- (2) an arithmetic and logic unit [ALU].

#### (2) Arithmetic operation instruction decoder:

Arithmetic operation instructions are passed to the instruction register (IR) and then to the PLA where they are converted into control signals.

The control signals from the PLA are used to control ALU peripheral circuits and ALU arithmetic operations (ADD, AND, OR, EOR).

#### (3) Arithmetic and logic unit [ALU]:

Upon reception of 8-bit data from one or two data sources the ALU processes that data in accordance with control signals from the PLA. The ALU is capable of executing the following processes:

- Additions and subtractions with and without carry

- Increments (+1) and decrements (-1)

- Bit complements

- Rotations (either direction with and without carry)

- BCD (decimal adjust)

- Carry, auxiliary carry, and overflow signal output

- Multiplications and divisions

- Bit detection

- · Exchange of low and high order nibbles

- · Logical AND, logical OR, and exclusive OR

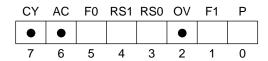

If a bit-3 auxiliary carry (AC), a bit-7 carry (CY), or an overflow (OV) is generated as a result of the arithmetic operation executed by the ALU, that result is set in the program status word (PSW 0D0H).

#### PSW(0D0H)

Figure 2-22 Program status word

#### 2.9 Program Counter

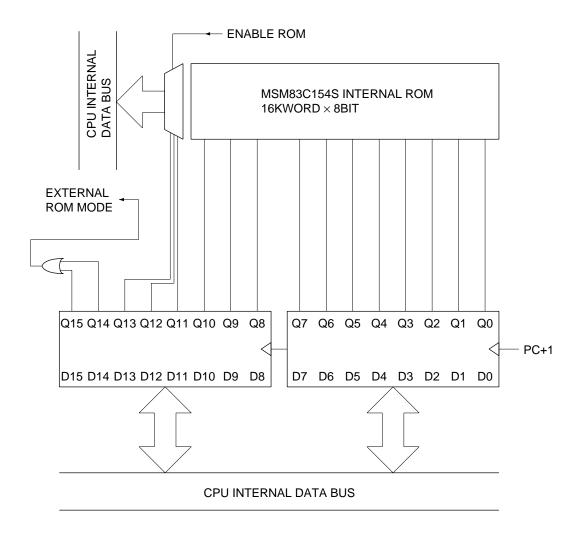

The MSM80C154S/MSM83C154S program counter has a 16-bit configuration PC0 thru PC15, as shown in Figure 2-23.

Figure 2-23 MSM80C154S/MSM83C154S program ounter

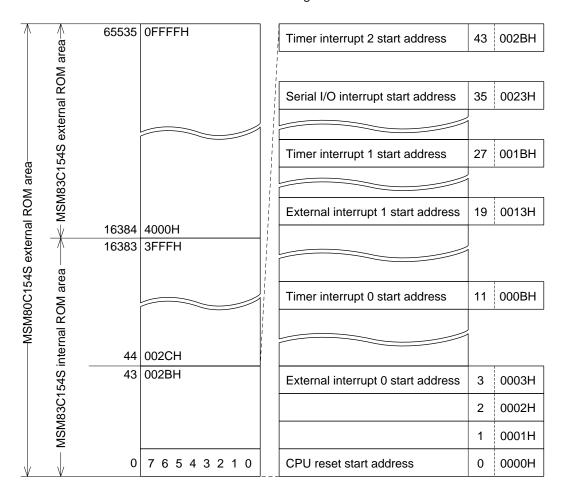

This program counter is a binary up-counter which is incremented by 1 each time one byte of instruction code is fetched. When the program counter is counted by 1 after counter contents have reached 0FFFFH, the counter is returned to 0000H. MSM83C154S is automatically switched to external ROM mode when the counter contents exceed 3FFFH.

#### 2.10 Program Memory and External Data Memory

#### 2.10.1 MSM80C154S/MSM83C154S program area and external ROM connections

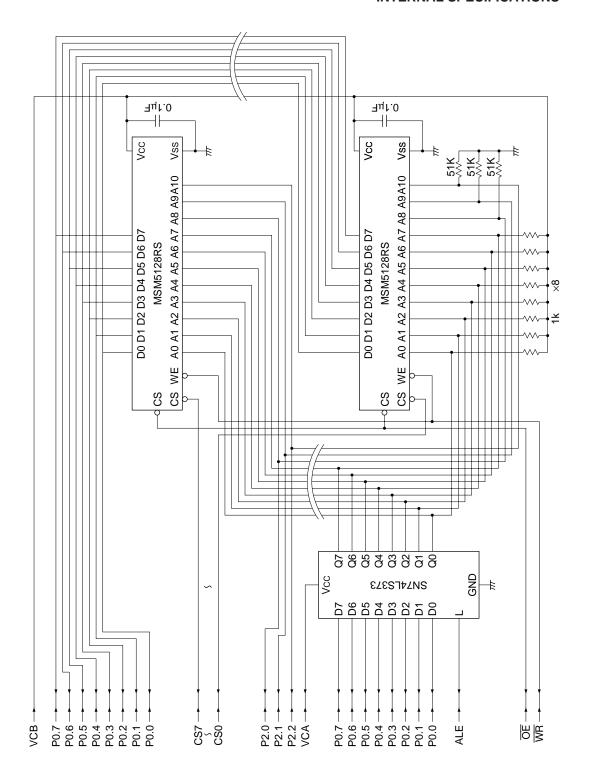

Since MSM80C154S/MSM83C154S are equipped with a 16-bit program counter, these devices can execute programs of up to 64K bytes (including both internal and external programs).

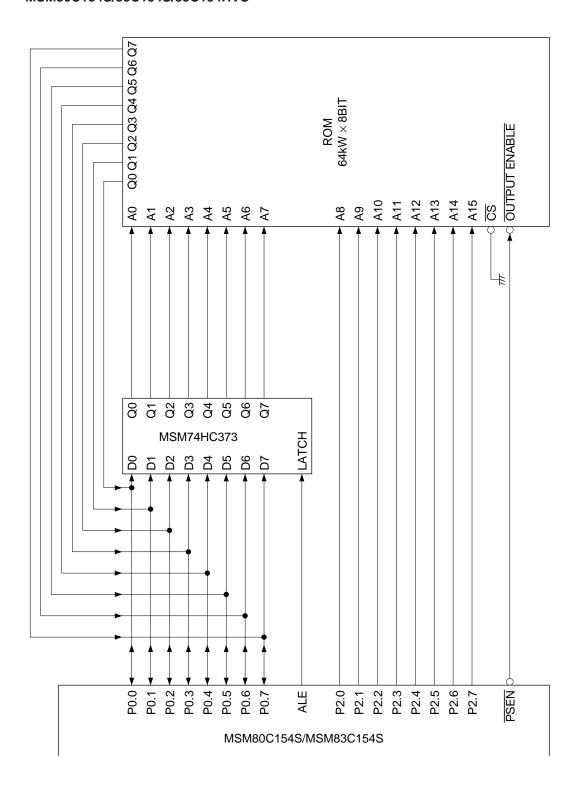

Since the MSM80C154S is not equipped with an internal program ROM, however, only external instructions are executed. MSM83C154S, on the other hand, is equipped with a 16K byte program ROM which enables it to execute internal instructions from address 0 thru address 16383. External instructions are executed when the address is greater than 16383. The program area is outlined in Figure 2-24, and a diagram of ROM connections made when external instructions are executed is shown in Figure 2-25.

Figure 2-24 MSM80C154S/MSM83C154S program area

Figure 2-25 MSM80C154S/MSM83C154S external ROM connection diagram

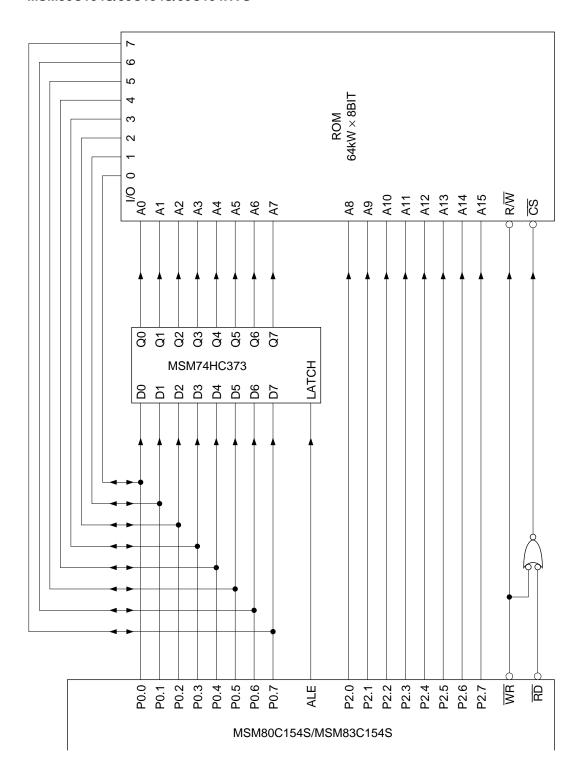

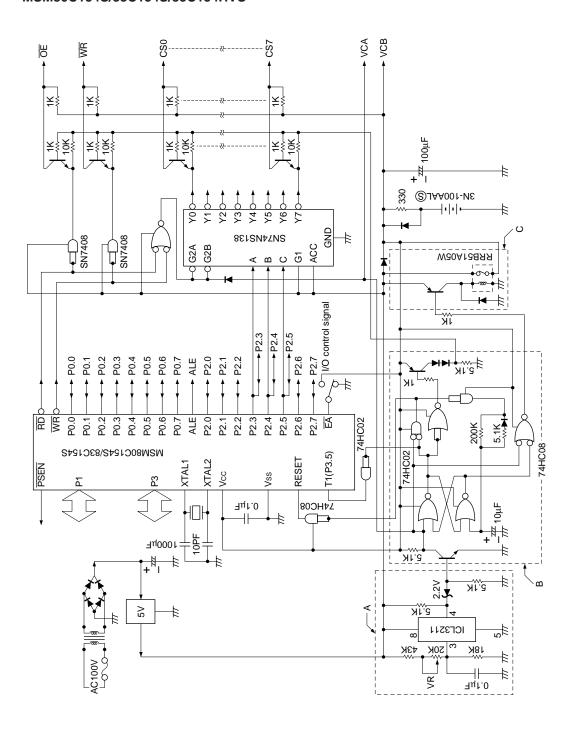

## 2.10.2 Procedures and circuit connections used when external data memory (RAM) is accessed by data pointer (DPTR)

The MSM80C154S/MSM83C154S can be connected to an external 64K word  $\times$  8-bit data memory (RAM) when accessing the memory by data pointer (DPTR).

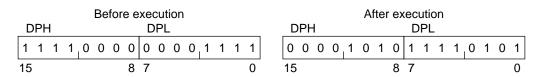

The data pointer (DPTR) consists of DPL and DPH registers. The DPL register contents serve as addresses 0 thru 7 of the external data memory, and the DPH register contents serve as addresses 8 thru 15.

The MOVX @DPTR, A instruction is used when accumulator contents are transferred to an external data memory, and the MOVX A, @DPTR instruction is used when external data memory contents are transferred to the accumulator. The external data memory connection diagram is shown in Figure 2-26 and the external data memory access time chart is shown in Figure 2-27.

When the data pointer indirect external memory instruction is executed, the CPU passes the DPL register contents to port 0, and the port 0 contents are latched externally by ALE signal. Data stored in the latch serves as the lower order addresses 0 thru 7 of the external data memory (RAM), and the DPH register contents passed to port 2 serve as the higher order addresses 8 thru 15 for addressing of the external data memory.

The WR or RD external data memory control signal is subsequently generated by the CPU to enable transfer of data between port 0 and the external data memory.

Figure 2-26 Connection circuit for external data memory addressed by DPTR

Figure 2-27 DPTR external data memory access timing

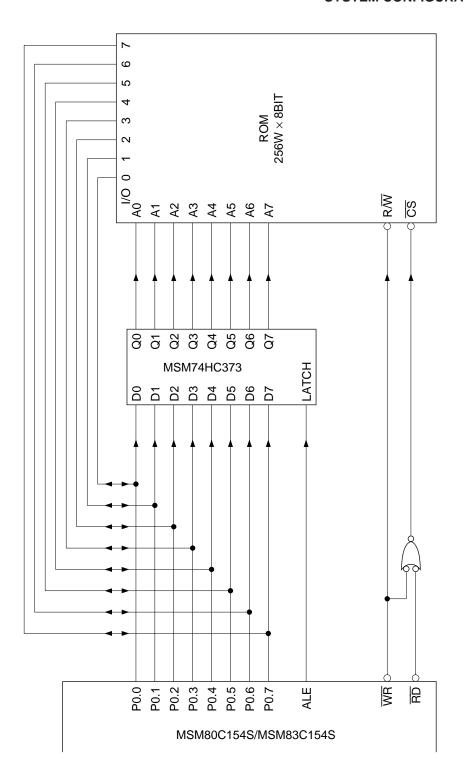

### 2.10.3 Procedures and circuit connections used when external data memory (RAM) is accessed by registers R0 and R1

The MSM80C154S/MSM83C154S can be connected to an external 256 word  $\times$  8-bit data memory (RAM) when addressing the memory according to the contents of registers R0 and R1 in the internal data memory (RAM).

The MOVX @Rr, A instruction is used when accumulator contents are transferred to an external data memory, and the MOVX A, @Rr instruction is used when external data memory contents are transferred to the accumulator. The external data memory connection diagram is shown in Figure 2-28 and the external data memory access time chart is shown in Figure 2-29.

When the indirect register external memory instruction is executed, the CPU passes the R0 or R1 register contents to port 0, and the port 0 contents are latched externally by the ALE signal. Data stored in the latch serves as the addresses 0 thru 7 of the external data memory. The  $\overline{\text{WR}}$  or  $\overline{\text{RD}}$  external data memory control signal is subsequently generated by the CPU to enable transfer of data between port 0 and the external data memory.

However, if the port 2 latched data is used in addresses 8 thru 15 of the external data memory, the circuit connections are the same as when the data pointer (DPTR) is used, thereby enabling a 64K byte  $\times$  8-bit data memory to be accessed.

Figure 2-28 Connection circuit for external data memory addressed by register R0 or R1

Figure 2-29 Register R0/R1 external data memory access timing

# 3. CONTROL

#### 3. CONTROL

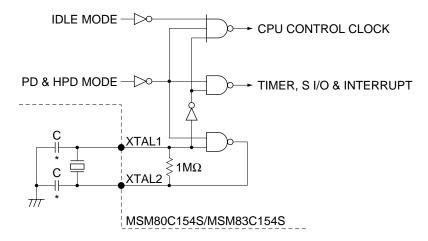

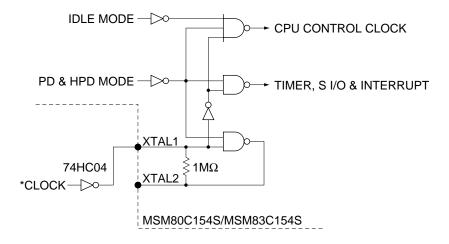

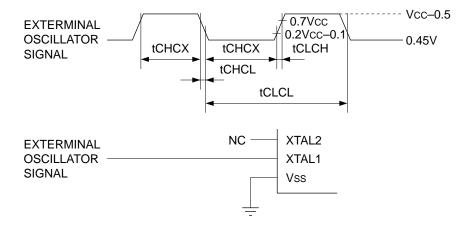

3.1 Oscillators: XTAL1 XTAL2

An oscillator is formed by connecting a crystal or ceramic resonator between the XTAL1 and XTAL2 pins of the MSM80C154S/MSM83C154S devices.

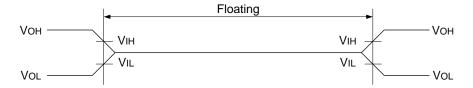

If an external clock is applied to XTAL1, the input should be at 50% duty and C-MOS level.

- \* The capacity of the compensating capacitor depends on the crystal resonator.

- \* The XTAL1-2 frequency depends on Vcc.

Figure 3-1 Crystal resonator connection diagram

- \* The capacity of the compensating capacitor depends on the ceramic resonator.

- \* The XTAL1.2 frequency depends on Vcc.

Figure 3-2 Ceramic resonator connection diagram

\* Supply of 50% duty clock

Figure 3-3 External clock supply circuit

#### 3.2 CPU Resetting

#### 3.2.1 Outline

If a reset signal (kept at "1" level for at least 1 $\mu$ sec) is applied to the RESET pin when the correct voltage (in respect to the various specifications) is applied to the MSM80C154S/MSM83C154S VCc pin, a reset signal is stored in the CPU even if the XTAL1·2 oscillators have been stopped.

The internally stored reset signal is used in direct initialization (setting to "1") of ports 0, 1, 2, and 3. All of the special function registers are then initialized (set to "0") two machine cycles after the XTAL1-2 oscillator commences regular operation.

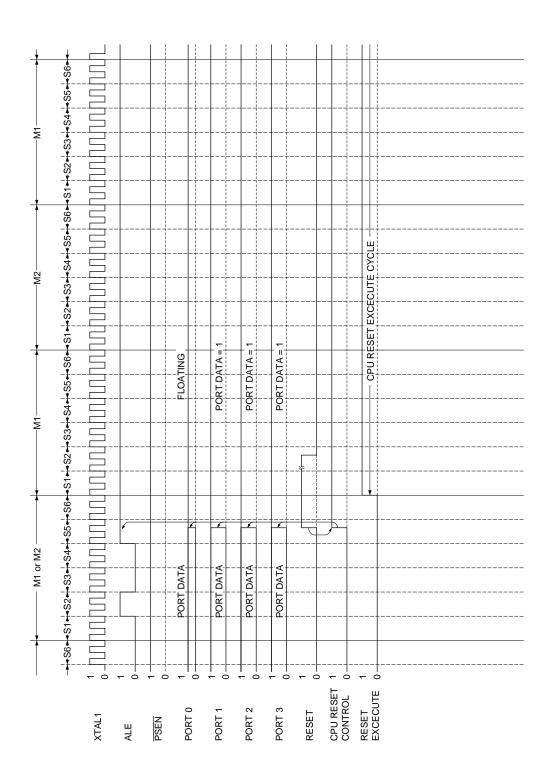

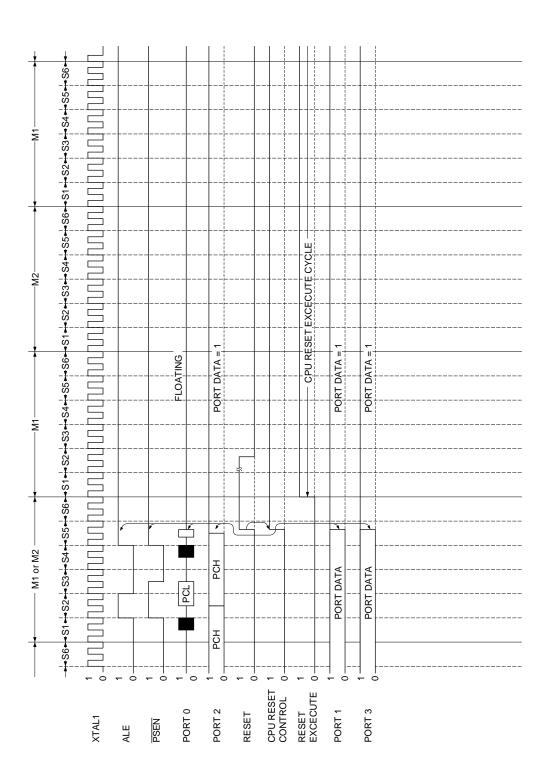

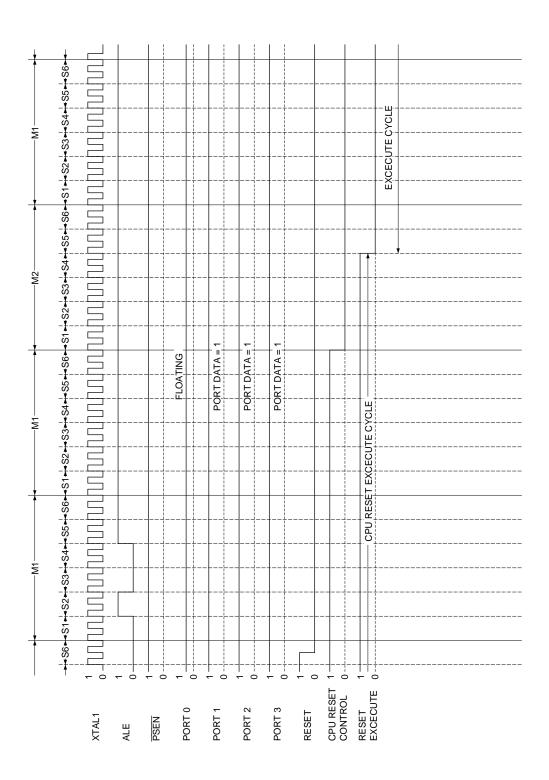

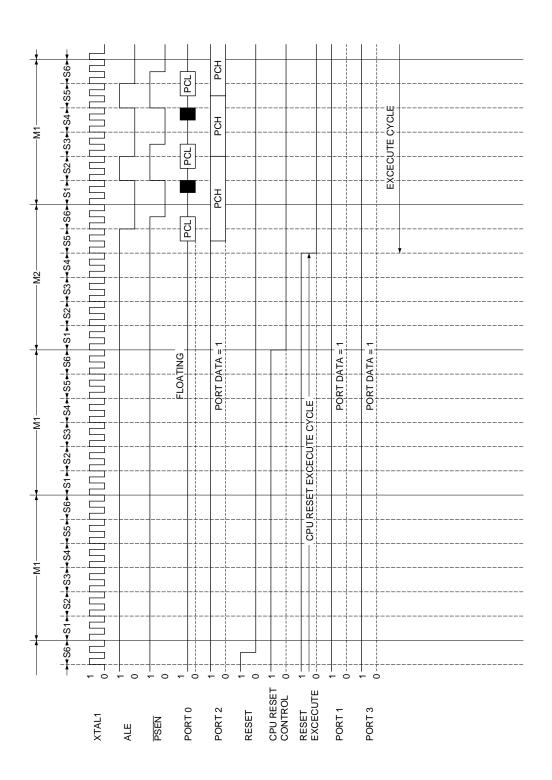

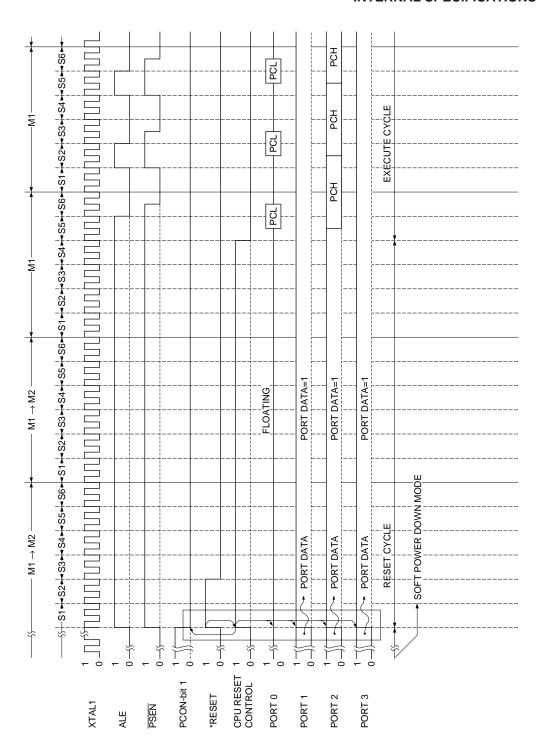

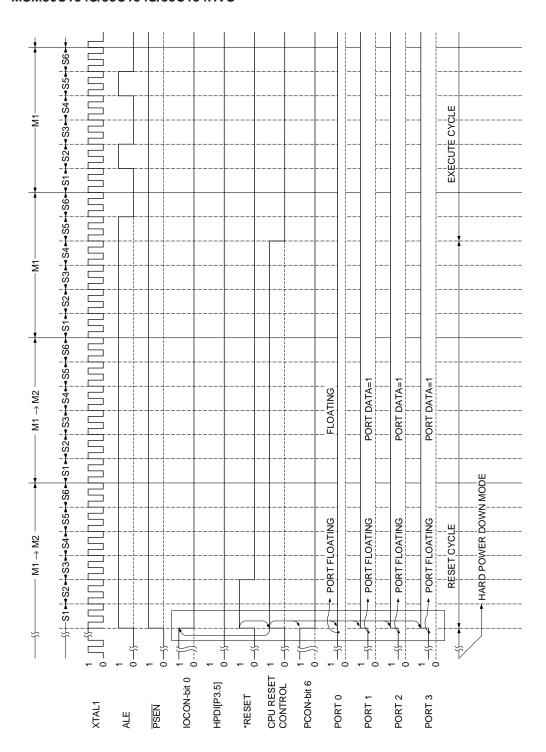

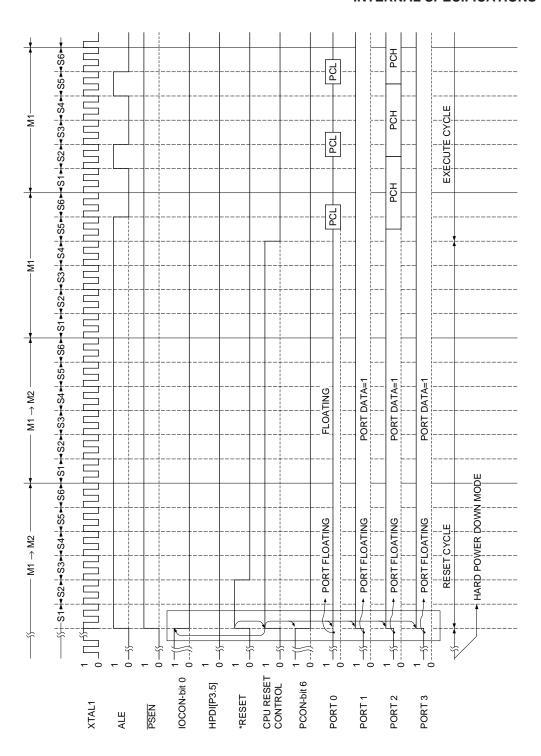

When the reset is released, instruction execution is started in the third machine cycle if the reset signal is changed from "1" level to "0" level before the M1-S1 signal leading edge, and in the fifth machine cycle if the reset signal is changed from "1" to "0" after the leading edge. The reset circuit block diagram is shown in Figure 3-4, the reset start time charts in Figures 3-5 and 3-6, and the reset release time charts in Figures 3-7 and 3-8.

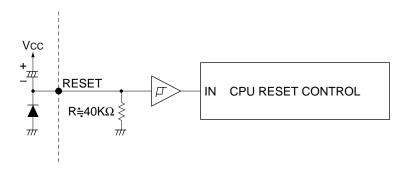

Figure 3-4 MSM80C154S/MSM83C154S reset circuit block diagram

Figure 3-5 Reset execution time chart (internal ROM mode)

Figure 3-6 Reset execution time chart (external ROM mode)

Figure 3-7 Reset release time chart (internal ROM mode)

Figure 3-8 Reset release time chart (external ROM mode)

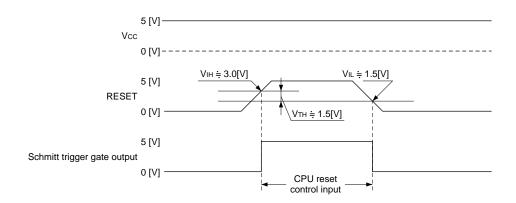

#### 3.2.2 Reset Schmitt trigger circuit

The Schmitt trigger circuit connected to the RESET pin shown in the MSM80C154S/ MSM-83C154S reset circuit block diagram in Figure 3-4 operates in the following way when the Vcc power supply voltage is +5V.

If the voltage of the reset signal applied to the RESET pin exceeds 3V when the level of that signal is changed from "0" to "1", the Schmitt trigger output level is changed from "0" to "1", and the reset signal is set in the CPU reset control circuit, resulting in the reset operation being started by the CPU.

The CPU reset state is released when the "1" level on the RESET pin is changed to "0". An input signal level below 1.5V is regarded as "0" level, and the Schmitt trigger output level is changed from "1" to "0". When the reset signal is changed to "0" level, the CPU reset control circuit is ready for reset release. The Schmitt trigger circuit operation time chart for changes in the reset input voltage is outlined in Figure 3-9.

Figure 3-9 Reset Schmitt trigger gate detector time chart

#### 3.2.3 CPU internal status by reset

When a reset signal is applied to the CPU with normal voltage applied to the MSM80C154S/MSM83C154S Vcc power supply pin, ports 0, 1, 2, and 3 are set to "1" (input mode) even if XTAL1·2 oscillation has been stopped. The output status of the ALE and PSEN pins also becomes "1". The CPU is then reset after normal XTAL1·2 oscillation has resumed. The internal CPU status when the CPU is reset is shown in Table 3-1.

Table 3-1 MSM80C154S/MSM83C154S reset internal status

| Register Name       | Register Reset Status |  |  |  |  |

|---------------------|-----------------------|--|--|--|--|

| PC                  | 0000H                 |  |  |  |  |

| SP                  | 07H                   |  |  |  |  |

| IP                  | 40H(0 × 000000)       |  |  |  |  |

| IE                  | 40H(0×000000)         |  |  |  |  |

| PCON                | 10H(000 × 0000)       |  |  |  |  |

| PSW, DPH, DPL, A, B |                       |  |  |  |  |

| SCON, TCON, TMOD    | 00Н                   |  |  |  |  |

| T2CON, IOCON, TL0   |                       |  |  |  |  |

| TL1, TL2, TH0, TH1  |                       |  |  |  |  |

| TH2, RCAP2L, RCAP2H |                       |  |  |  |  |

| P1, P2, P3          | *0FFH(input port)     |  |  |  |  |

| P0                  | *0FFH(floating)       |  |  |  |  |

| SBUF                | Undofined             |  |  |  |  |

| INTERNAL RAM        | Undefined             |  |  |  |  |

| ALE, PSEN           | *"1" OUT              |  |  |  |  |

<sup>\*</sup> Denotes direct resetting even if XTAL1.2 has stopped.

#### 3.3 EA (CPU Memory Separate)

#### 3.3.1 Outline

The function of the  $\overline{EA}$  pin is to determine whether a CPU internal program memory (ROM) instruction or an external program instruction is to be executed.

- (1) Internal ROM mode

If the EA pin is connected to Vcc and a "1" reset signal is applied to the RESET pin to reset the CPU, an internal program memory (ROM) is executed from address 0.

(MSM83C154S, MSM85C154HVS)

- (2) External ROM mode

If the EA pin is connected to Vss and a "1" reset signal is applied to the RESET pin to reset the CPU, an external program memory is executed from address 0.

# 4. INTERNAL SPECIFICATIONS

#### 4. INTERNAL SPECIFICATIONS

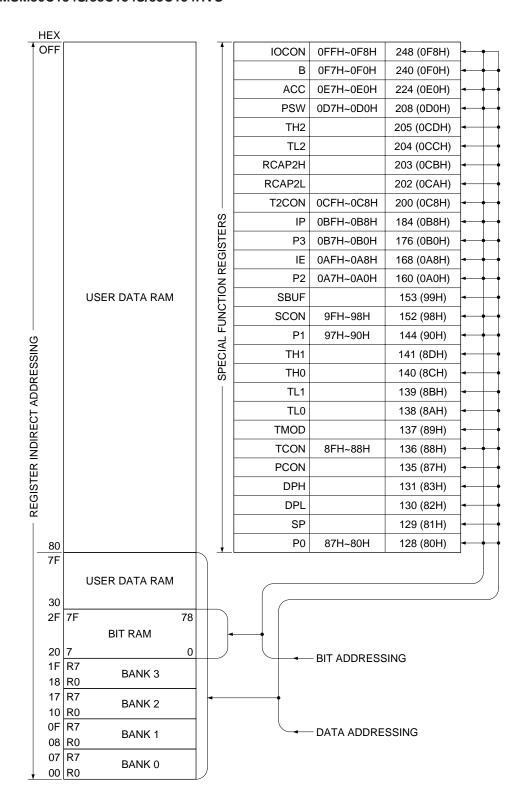

#### 4.1 Internal Data Memory (RAM) and Special Function Registers

#### 4.1.1 Outline

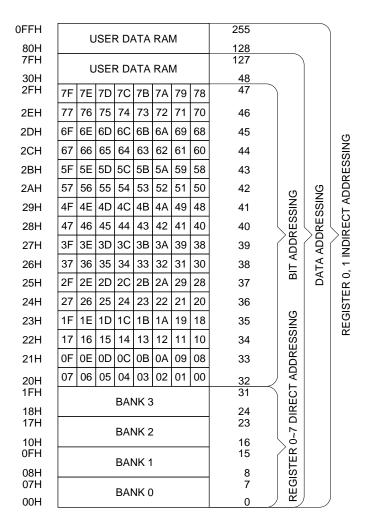

MSM80C154S/MSM83C154S operation is based on an instruction code address method where operations are specified in an instruction code (OP) section, and the data memory (RAM) and special function registers (ACC, B, TCON, P0........) are specified directly by part of the instruction code and the second or third byte of data following that instruction code. According to this instruction code address method, all eight bits of data in the data memory and special function register may be specified, or one bit of data memory and one bit of data in the special function register may be specified. Direct designation of all eight bits of data is called data addressing, and direct designation of one bit of data is called bit addressing. Since these CPU devices specify data memory (RAM) and special function register contents by the above method, specific addresses are assigned to the respective CPU data memory (RAM) and special function registers (ACC, B, TCON, P0, ....). Data addresses consist of eight bits, and range from 00 to 0FFH in binary (which correspond to 0 thru 255 in decimal). All data memory (RAM) and special function registers (ACC, B, TCON, P0, ....) exist in these 256 locations.

The data memory contains 256 bytes. The data memory between addresses 00 thru 7FH can be specified directly by data address, and the data memory from address 80H to 0FFH can be specified by indirect register instruction where R0 or R1 contents are set to 80H thru 0FFH. Note that the entire data memory (RAM) from 00 thru 0FFH can be specified by indirect register instruction.

Special function registers are located between addresses 80H thru 0FFH, and can also be specified directly by data address. Bit addresses consist of eight bits, the manipulation bits being specified by the three lower order bits and the data memory (RAM) or special function register (ACC, B, TCON, P0, ....) by the five higher order bits. Data memory between addresses 20 thru 2FH can be specified by bit addressing. Other areas cannot be specified by bit designation.

The special function registers which can be specified by bit address are P0, P1, P2, P3, TCON, SCON, IE, IP, T2CON, PSW, ACC, B, and IOCON, a total of 13 registers. The data memory (RAM) and special function register address space layout is shown in Figure 4-1.

Figure 4-1 Data memory and special function register layout

#### 4.2 Internal Data Memory (RAM)

#### 4.2.1 Internal data memory (RAM)

The storage capacity of the MSM80C154S/MSM83C154S data memory is 256 words  $\times$  8 bits. The layout diagram is shown in Figure 4-2.

The data memory can be accessed (R/W) in four different ways - direct register designation, indirect register designation, data addressing, and bit addressing.

Four banks of registers group (R0 thru  $R7 \times 4$ ) exist within the data memory address range from 00 to 1FH. Banks are specified by RS0 and RS1 data combinations within the PSW. The data memory address range from 20 to 2FH is an area where bit addressing is possible. One bit of data can be manipulated directly by bit manipulation instructions.

The data memory address range from 00 to 7FH is an area where data addressing is possible. 8-bit data manipulations can be handled directly by data address manipulation instructions. The data memory address range from 80H to 0FFH is an area where data addressing is not possible. To manipulate data in this data memory area, the contents of register R0 or R1 are set in 80H thru 0FFH, then an indirect register instruction is used. (Indirect register instructions can be used to specify the entire data memory from address 00 to 0FFH.) In addition to data storage in the CPU, the data memory is used as the place for saving stack data. This stack data storage area is addressed by a stack pointer (SP 81H).

Since the stack pointer can be set any desired value by software, the data memory can be used as stack from any data memory address. Note that 07H data is set automatically in the stack pointer when the CPU is reset.

Figure 4-2 RAM layout diagram

#### 4.2.2 Internal data memory registers R0 thru R7

Four banks of registers group exist in the data memory (RAM) between memory addresses 00 thru 1FH. Banks are specified by RS0 and RS1 bit combinations within the program status word (PSW). Note that the register area R0 thru R7 can also be used as normal data memory. The PSW table is shown in Table 4-1, and the data memory register bank layout in Figure 4-3.

Table 4-1 Program status word (PSW)

| Bit  | 7  | 6  | 5  | 4   | 3   | 2  | 1  | 0 |

|------|----|----|----|-----|-----|----|----|---|

| Flag | CY | AC | F0 | RS1 | RS0 | OV | F1 | Р |

| Set  |    |    |    | •   | •   |    |    |   |

| OFF                                    | 255                                  |                                              |                                        | D5<br>R D/                                   |                                              | D3<br>RAM                              | D2<br>1                                      | D1                                     | D0                                     | TA RAM                                       |        |     |     |

|----------------------------------------|--------------------------------------|----------------------------------------------|----------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------|----------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------------|--------|-----|-----|

| 30<br>2F                               | 48<br>47                             | D7<br>D7                                     | D6<br>D6                               | D5                                           | D4<br>D4                                     | D3<br>D3                               | D2<br>D2                                     | D1<br>D1                               | D0<br>D0                               | CK & DAT                                     |        |     |     |

| 20                                     | 32                                   | D7                                           | ВП <i>I</i>                            | ADDF<br>D5                                   | RESS<br>D4                                   | D3                                     | D2                                           | D1                                     | D0                                     | STACK                                        |        | RS1 | RS0 |

| 1F                                     | 31                                   | D7<br>D7                                     | D6                                     | D5                                           | D4<br>D4                                     | D3                                     | D2<br>D2                                     | D1                                     | D0<br>D0                               | R7                                           | BANK 3 | 1   | 1   |

| 18<br>17<br>10                         | 24<br>23<br>16                       | D7<br>D7                                     | D6<br>D6<br>D6                         | D5                                           | D4<br>D4<br>D4                               | D3<br>D3<br>D3                         | D2<br>D2<br>D2                               | D1<br>D1<br>D1                         | D0<br>D0                               | R0<br>R7<br>R0                               | BANK 2 | 1   | 0   |

| 0F<br>08                               | 15                                   | D7<br>D7                                     | D6<br>D6                               | D5<br>D5                                     | D4<br>D4                                     | D3<br>D3                               | D2<br>D2                                     | D1                                     | D0<br>D0                               | R7                                           | BANK 1 | 0   | 1   |

| 07<br>06<br>05<br>04<br>03<br>02<br>01 | 7<br>6<br>5<br>4<br>3<br>2<br>1<br>0 | D7<br>D7<br>D7<br>D7<br>D7<br>D7<br>D7<br>D7 | D6<br>D6<br>D6<br>D6<br>D6<br>D6<br>D6 | D5<br>D5<br>D5<br>D5<br>D5<br>D5<br>D5<br>D5 | D4<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4<br>D4 | D3<br>D3<br>D3<br>D3<br>D3<br>D3<br>D3 | D2<br>D2<br>D2<br>D2<br>D2<br>D2<br>D2<br>D2 | D1<br>D1<br>D1<br>D1<br>D1<br>D1<br>D1 | D0<br>D0<br>D0<br>D0<br>D0<br>D0<br>D0 | R7<br>R6<br>R5<br>R4<br>R3<br>R2<br>R1<br>R0 | BANK 0 | 0   | 0   |

Figure 4-3 Internal data memory register bank layout

#### 4.2.3 Stack

The stack data save (storage) area is in the internal data memory (RAM), and is specified by stack pointer (SP 81H).

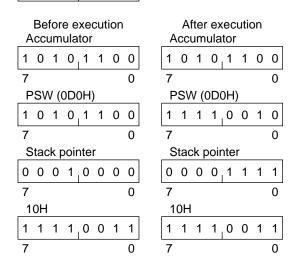

Although 07H data is automatically set in the stack pointer when the CPU is reset, any desired data can be set by software to enable the data memory to be used as stack from any address. Two bytes of data memory are used when the stack is used by interrupt or CALL instruction, and a single byte of data memory is used when the PUSH instruction is used. The status where an interrupt is generated and the program counter contents are saved in the stack when the stack pointer contents are 7FH, and the status where accumulator contents are pushed during interrupt routine and are subsequently saved in the stack are shown in Table 4-2. The stack status up to completion of interrupt processing upon execution of POP and RETI instructions is also included.

Table 4-2 Stack storage layout

| Ctook proposing       | Stack   | RAM data bit |      |      |      |      |      |     |     |  |  |

|-----------------------|---------|--------------|------|------|------|------|------|-----|-----|--|--|

| Stack processing      | pointer | 7            | 6    | 5    | 4    | 3    | 2    | 1   | 0   |  |  |

| Before execution      | 7FH     | D7           | D6   | D5   | D4   | D3   | D2   | D1  | D0  |  |  |

| Interrupt process     | 80H     | PC7          | PC6  | PC5  | PC4  | PC3  | PC2  | PC1 | PC0 |  |  |

| (push PC)             | 81H     | PC15         | PC14 | PC13 | PC12 | PC11 | PC10 | PC9 | PC8 |  |  |

| PUSH process (ACC)    | 82H     | A7           | A6   | A5   | A4   | A3   | A2   | A1  | A0  |  |  |

| POP process (ACC)     | 82H     | A7           | A6   | A5   | A4   | A3   | A2   | A1  | A0  |  |  |

| DETI process (per DC) | 81H     | PC15         | PC14 | PC13 | PC12 | PC11 | PC10 | PC9 | PC8 |  |  |

| RETI process (pop PC) | 80H     | PC7          | PC6  | PC5  | PC4  | PC3  | PC2  | PC1 | PC0 |  |  |

| After execution       | 7FH     | D7           | D6   | D5   | D4   | D3   | D2   | D1  | D0  |  |  |

#### 4.3 Internal Data Memory (RAM) Operating Procedures

#### 4.3.1 Internal data memory indirect addressing

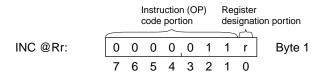

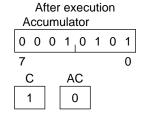

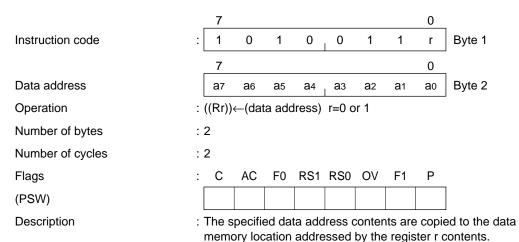

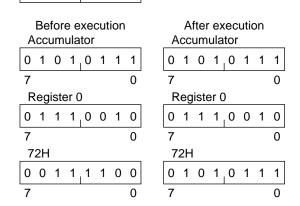

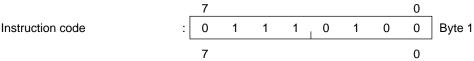

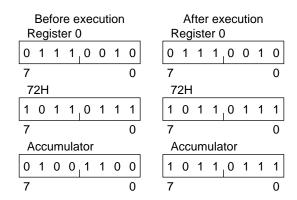

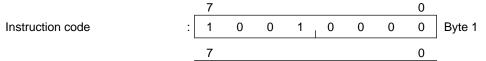

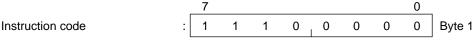

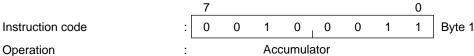

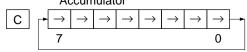

Operation of the internal data memory indirect increment instruction is described here as an example. This instruction (INC @Rr) is a 1-byte 1-machine cycle instruction (see Figure 4-4). The indirect address register is specified by instruction code bit 0 data r where r denotes either register 0 or 1 in the register group specified by PSW RS0 and RS1 bank data. Register 0 is specified when the r data is 0, and register 1 is specified when the data is 1. When this instruction is executed, register data is read from the specified register 0 or 1, and

the read out register data is written into the data pointer for the data memory.

The data memory contents specified by the data pointer are read by the CPU into a temporary register. Then a subsequent increment (+1) by the ALU is followed by a return to the data memory at the address where the data were read out. In this way, the contents of the data memory at the address specified by the contents of R0 or R1 are incremented.

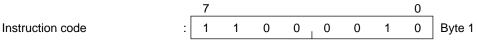

Figure 4-4 INC @Rr bit arrangement

#### 4.3.2 Internal data memory register R0 thru R7 designation

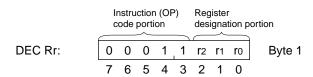

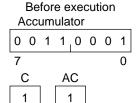

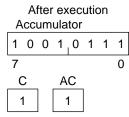

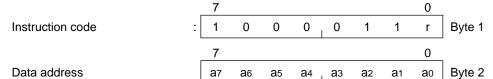

Operation of the internal data memory register decrement instruction is described here as an example. This instruction (DEC Rr) is a 1-byte 1-machine cycle instruction (see Figure 4-5). Register R0 thru R7 is specified by r0, r1, and r2 data of instruction code bit 0, 1, and 2. The r0, r1, and r2 data is represented in binary code, r0 being the LSB, and r2 the MSB. The code is weighted 1, 2, and 4 from the LSB. Any one of the eight registers can be specified by combinations of this code. See Table 4-3 for the register designation combinations. When this instruction is executed, one of the registers R0 thru R7 from the register group specified by the PSW RS0 and RS1 bank data is specified. The contents of the specified register is read by the CPU into a temporary register. Then a subsequent decrement (–1) by the ALU is followed by a return to the register where the data were read out. In this way, the register contents specified by r0, r1, and r2 are decremented.

Figure 4-5 DEC Rr bit arrangement

Table 4-3 Register designation table

| Register name | r2 | r1 | ro |

|---------------|----|----|----|

| Register 0    | 0  | 0  | 0  |

| Register 1    | 0  | 0  | 1  |

| Register 2    | 0  | 1  | 0  |

| Register 3    | 0  | 1  | 1  |

| Register 4    | 1  | 0  | 0  |

| Register 5    | 1  | 0  | 1  |

| Register 6    | 1  | 1  | 0  |

| Register 7    | 1  | 1  | 1  |

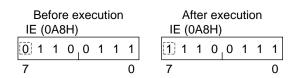

#### 4.3.3 Internal data memory 1-bit data designation

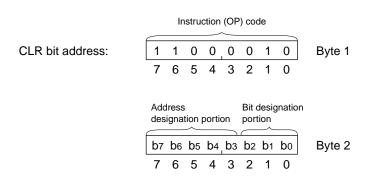

In the MSM80C154S/MSM83C154S, 1-bit data manipulations (test, reset, set, complement, transfer) can be executed directly between internal data memory addresses 20 thru 2FH by bit manipulation instructions. The operation of a bit reset instruction is described below as an example.

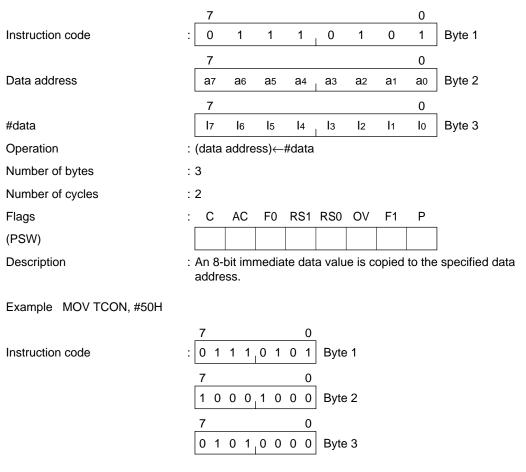

This instruction (CLR bit address) is a 2-byte 2-machine cycle instruction (see Figure 4-6). The instruction code is indicated in byte 1, and the data memory address and bit designation are indicated in byte 2. The manipulation bit is specified by the b0, b1, and b2 data in bits 0, 1, and 2 of byte 2. The b0, b1, and b2 portion is expressed in binary code which is weighted 1, 2, and 4. Combinations of this code enable any one of eight bits to be specified. The bit designation combinations are listed in able 4-4.

The data memory is addressed by bits b3, b4, b5, b6 and b7 of byte 2 with b7 being "0". These bits can be expressed in binary by 0 thru 0FH, and a total of 16 designations of the data memory are possible.

When data memory addresses are specified, the data memory bit manipulation start address 20H is added to the b3, b4, b5, and b6 binary data to obtain the data memory address.

The data memory contents specified by the above method are read by the CPU into a temporary register, the specified bit data is reset to "0" by the ALU, and the CPU returns the result to the data memory where the data were read. One bit of specified data memory is thus reset to "0".

Figure 4-6 CLR bit address bit arrangement

Table 4-4 Bit designation table

| Bit name | b2 | b1 | bo |

|----------|----|----|----|

| Bit 0    | 0  | 0  | 0  |

| Bit 1    | 0  | 0  | 1  |

| Bit 2    | 0  | 1  | 0  |

| Bit 3    | 0  | 1  | 1  |

| Bit 4    | 1  | 0  | 0  |

| Bit 5    | 1  | 0  | 1  |

| Bit 6    | 1  | 1  | 0  |

| Bit 7    | 1  | 1  | 1  |

Table 4-5 Addressing combination table

|   | b7 | b6 | b5 | b4 | рз | RAM address |    |

|---|----|----|----|----|----|-------------|----|

| 0 | 0  | 0  | 0  | 0  | 0  | 20H         | 32 |

| 1 | 0  | 0  | 0  | 0  | 1  | 21H         | 33 |

| 2 | 0  | 0  | 0  | 1  | 0  | 22H         | 34 |

| 3 | 0  | 0  | 0  | 1  | 1  | 23H         | 35 |

| 4 | 0  | 0  | 1  | 0  | 0  | 24H         | 36 |

| 5 | 0  | 0  | 1  | 0  | 1  | 25H         | 37 |

| 6 | 0  | 0  | 1  | 1  | 0  | 26H         | 38 |

| 7 | 0  | 0  | 1  | 1  | 1  | 27H         | 39 |

| 8 | 0  | 1  | 0  | 0  | 0  | 28H         | 40 |

| 9 | 0  | 1  | 0  | 0  | 1  | 29H         | 41 |

| Α | 0  | 1  | 0  | 1  | 0  | 2AH         | 42 |

| В | 0  | 1  | 0  | 1  | 1  | 2BH         | 43 |

| С | 0  | 1  | 1  | 0  | 0  | 2CH         | 44 |

| D | 0  | 1  | 1  | 0  | 1  | 2DH         | 45 |

| Е | 0  | 1  | 1  | 1  | 0  | 2EH         | 46 |

| F | 0  | 1  | 1  | 1  | 1  | 2FH         | 47 |

#### 4.4 Special Function Registers (TCON, SCON,.... ACC, B)

#### 4.4.1 Outline

As can be seen from the configuration shown in Table 4-6, the MSM80C154S/MSM83C154S special function registers consist of 27 8-bit registers.

Special function registers can be accessed (R/W) by either data addressing or bit addressing. All 27 registers can be specified by data addressing. 13 registers (P0, P1, P2, P3, TCON, T2CON, SCON, IE, IP, PSW, ACC, B, and IOCON) can be specified by bit addressing. If a register which does not exist at the data address is accessed when a special function register is used, the read data becomes 0FFH. And when data is written, none of the registers in the CPU are effected at all. Note, however, that since a jump is always executed when a bit test instruction which results in a relative jump at data condition "1" is executed, make sure that no instruction is executed for a register which does not exist.

Table 4-6 List of special function registers

| Register |    |    |    | Bit ad | ldress |    |    |    | Data address |

|----------|----|----|----|--------|--------|----|----|----|--------------|

| name     | b7 | b6 | b5 | b4     | bз     | b2 | b1 | bo | Data address |

| IOCON    | FF | FE | FD | FC     | FB     | FA | F9 | F8 | 0F8H(248)    |

| В        | F7 | F6 | F5 | F4     | F3     | F2 | F1 | F0 | 0F0H(240)    |

| ACC      | E7 | E6 | E5 | E4     | E3     | E2 | E1 | E0 | 0E0H(224)    |

| PSW      | D7 | D6 | D5 | D4     | D3     | D2 | D1 | D0 | 0D0H(208)    |

| TH2      |    |    |    |        |        |    |    |    | 0CDH(205)    |

| TL2      |    |    |    |        |        |    |    |    | 0CCH(204)    |

| RCAP2H   |    |    |    |        |        |    |    |    | 0CBH(203)    |

| RCAP2L   |    |    |    |        |        |    |    |    | 0CAH(202)    |

| T2CON    | CF | CE | CD | CC     | СВ     | CA | C9 | C8 | 0C8H(200)    |

| IP       | BF | BE | BD | ВС     | BB     | ВА | В9 | В8 | 0B8H(184)    |

| P3       | B7 | В6 | B5 | В4     | В3     | B2 | B1 | В0 | 0B0H(176)    |

| IE       | AF | AE | AD | AC     | AB     | AA | A9 | A8 | 0A8H(168)    |

| P2       | A7 | A6 | A5 | A4     | A3     | A2 | A1 | A0 | 0A0H(160)    |

| SBUF     |    |    |    |        |        |    |    |    | 99H(153)     |

| SCON     | 9F | 9E | 9D | 9C     | 9B     | 9A | 99 | 98 | 98H(152)     |

| P1       | 97 | 96 | 95 | 94     | 93     | 92 | 91 | 90 | 90H(144)     |

| TH1      |    |    |    |        |        |    |    |    | 8DH(141)     |

| TH0      |    |    |    |        |        |    |    |    | 8CH(140)     |

| TL1      |    |    |    |        |        |    |    |    | 8BH(139)     |

| TL0      |    |    |    |        |        |    |    |    | 8AH(138)     |

| TMOD     |    |    |    |        |        |    |    |    | 89H(137)     |

| TCON     | 8F | 8E | 8D | 8C     | 8B     | 8A | 89 | 88 | 88H(136)     |

| PCON     |    |    |    |        |        |    |    |    | 87H(135)     |

| DPH      |    |    |    |        |        |    |    |    | 83H(131)     |

| DPL      |    |    |    |        |        |    |    |    | 82H(130)     |

| SP       |    |    |    |        |        |    |    |    | 81H(129)     |

| P0       | 87 | 86 | 85 | 84     | 83     | 82 | 81 | 80 | 80H(128)     |

# 4.4.2 Special function registers

# 4.4.2.1 Timer mode register (TMOD)

| Name         | A al al u a a a | MSB                                                                                                                |                                                                     |           |            |                |            |           | LSB      |  |  |  |  |

|--------------|-----------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-----------|------------|----------------|------------|-----------|----------|--|--|--|--|

| Name         | Address         | 7                                                                                                                  | 6                                                                   | 5         | 4          | 3              | 2          | 1         | 0        |  |  |  |  |

| TMOD         | 89H             | GATE                                                                                                               | C/T                                                                 | M1        | MO         | GATE           | C/T        | M1        | MO       |  |  |  |  |

| Bit location | Flag            |                                                                                                                    |                                                                     |           | Fun        | ction          |            |           |          |  |  |  |  |

| TMOD.0       | MO              | M1 M0                                                                                                              | Timer/c                                                             | ounter 0  | mode se    | etting         |            |           |          |  |  |  |  |

|              |                 | 0 0                                                                                                                | 8-bit tim                                                           | ner/count | er with 5  | -bit preso     | calar      |           |          |  |  |  |  |

|              |                 | 0   1                                                                                                              | 16-bit ti                                                           | mer/cour  | nter       |                |            |           |          |  |  |  |  |

| TMOD.1       | M1              | 1 0                                                                                                                | 8-bit tim                                                           | ner/count | er with 8  | -bit auto      | reloadin   | g         |          |  |  |  |  |

|              |                 | 1   1                                                                                                              | Timer/c                                                             | ounter 0  | separate   | ed into Tl     | _0 (8-bit) | timer/co  | unter    |  |  |  |  |

|              |                 |                                                                                                                    | and TH0 (8-bit) timer/counter. TF0 is set by TL0 carry,             |           |            |                |            |           |          |  |  |  |  |

|              |                 | i                                                                                                                  | and TF1 is set by TH0 carry.                                        |           |            |                |            |           |          |  |  |  |  |

| TMOD.2       | C/T             |                                                                                                                    | Timer/counter 0 count clock designation control bit.                |           |            |                |            |           |          |  |  |  |  |

|              |                 |                                                                                                                    | XTAL1.2 divided by 12 clock is the input applied to timer/counter 0 |           |            |                |            |           |          |  |  |  |  |

|              |                 |                                                                                                                    | when $C/\overline{T}="0"$ .                                         |           |            |                |            |           |          |  |  |  |  |

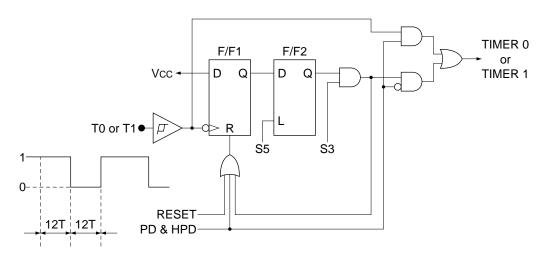

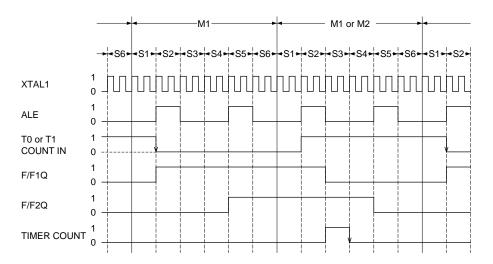

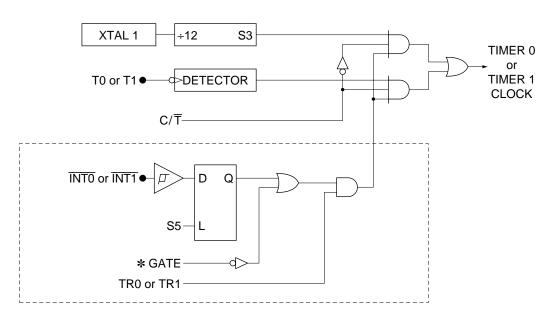

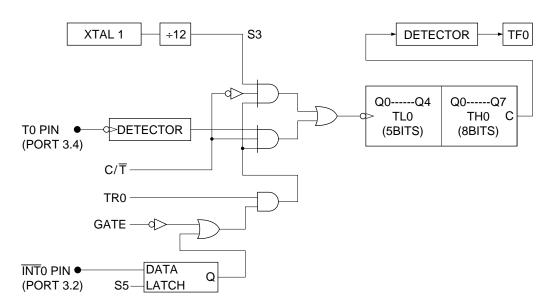

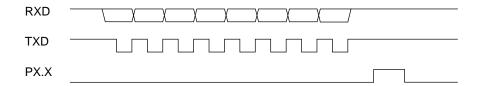

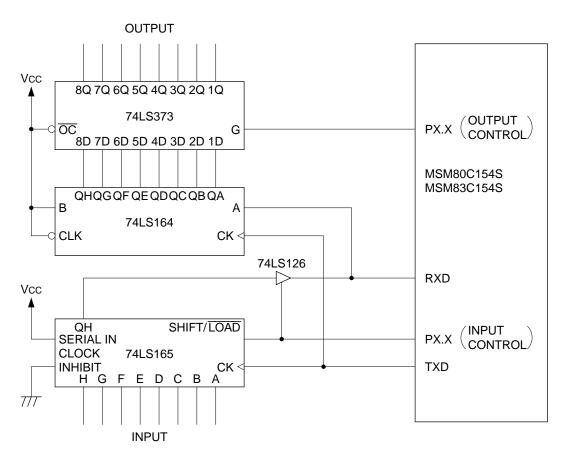

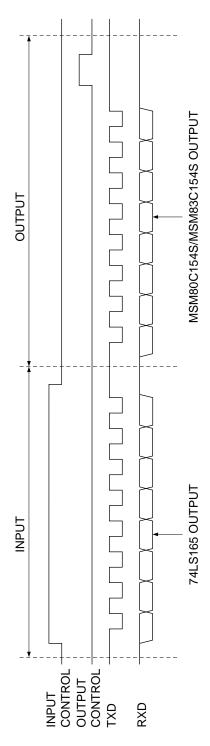

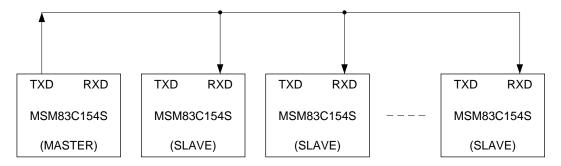

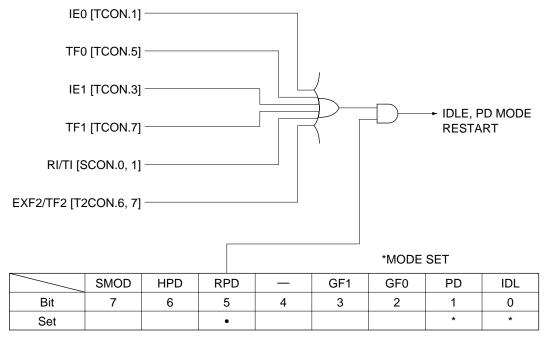

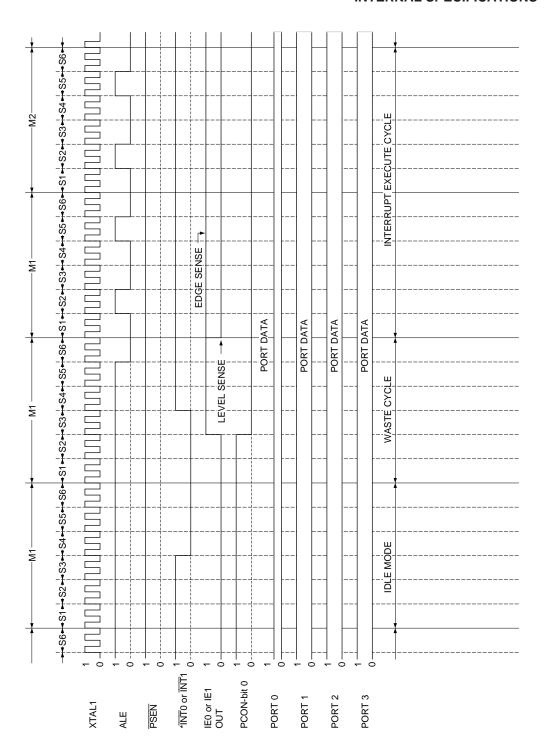

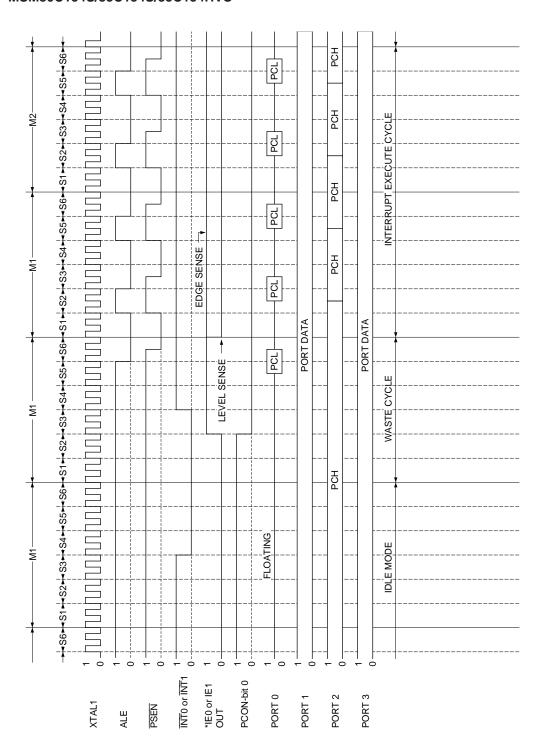

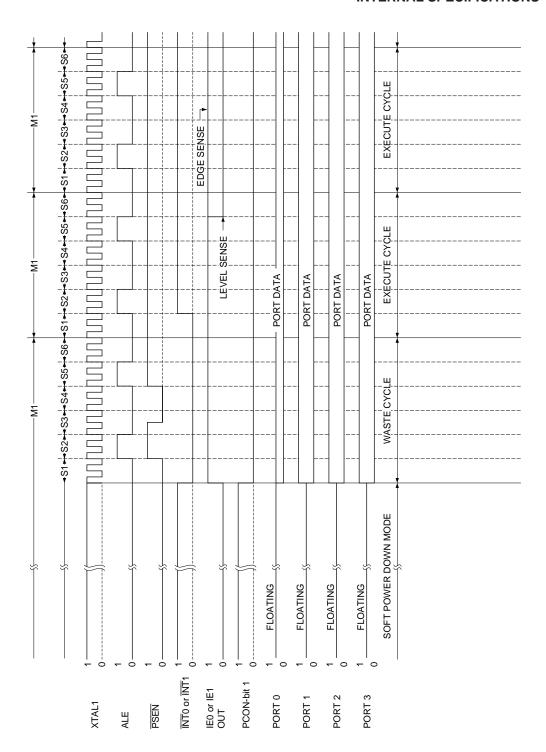

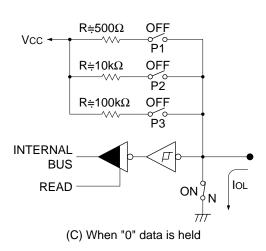

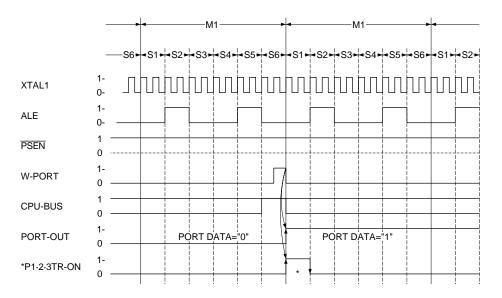

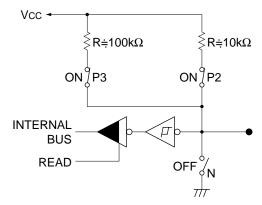

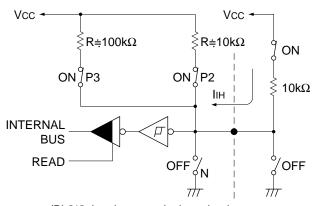

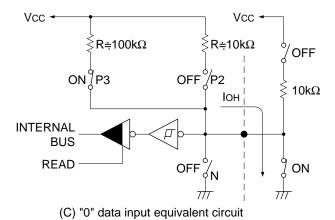

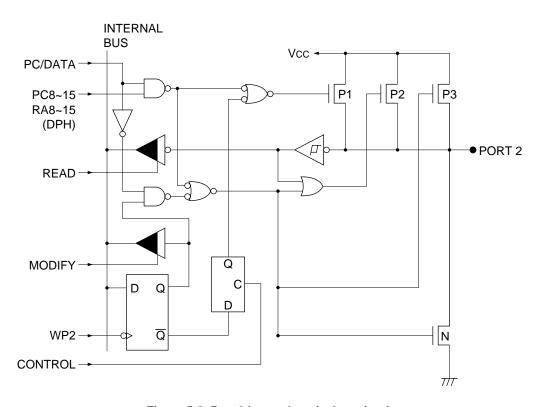

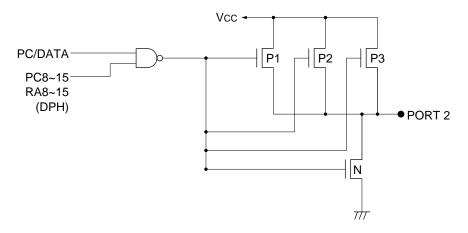

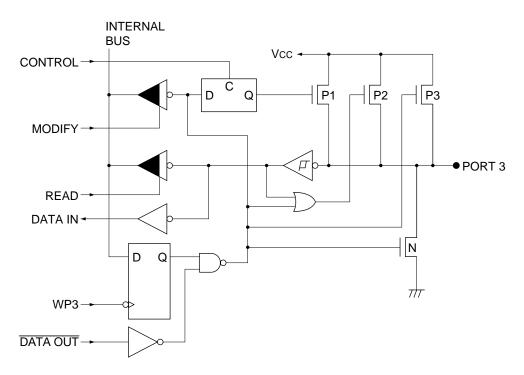

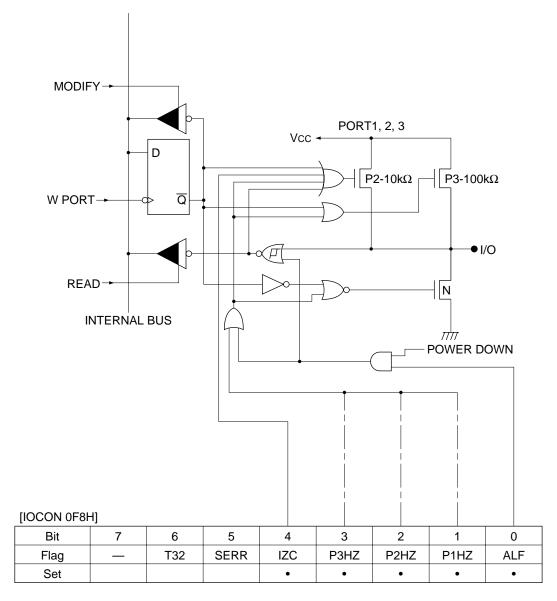

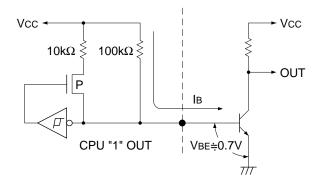

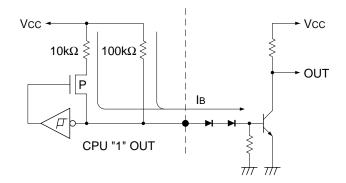

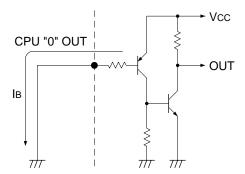

|              |                 |                                                                                                                    | The external clock applied to the T0 pin is the input applied to    |           |            |                |            |           |          |  |  |  |  |